Изобретение относится к вычислительной технике, в частности к области устройств, мо дифицирующих или вычисляющих адреса. Известно устройство, содержащее блок памяти, регистры операционную схему, оборудование, обеспечивающее косвенную адресацию в случае несовпадения содержимого блока памяти, вызванного по найденному адресу, с содержимым ключевого регистра 1). Известное устройство позволяет обрабатывать только одномерные массивы информации и быстродействиеего недостаточно. Наиболее близким по техническому решению к предлагаемому является устройство, содержащее регистры, при этом индексация адресов производится в арифметическом блоке центрального процессора 2 . Недостатками блока векторной работы являются аппаратная обработка только одномерных массивов, ограниченное количество обрабатывае мых массивов, использова1ше арифметического блока для индексации адресов и, как следстви этого, малое быстродействие.

is jBjjggs Цель изобретения - повьщ1ение быстродействия. Поставленная цель достигается тем, что в устройство для обработки адресной информации, содержащее выходной регистр адреса, блок контроля, блок индексации, входной регистр дескриптора, входной регистр индексов, выходной коммутатор, причем грутша выходов входного регистра индексов подключена к первой группе входов блока контроля и первой группе входов блока индексации, группа выходов входного регистра дескриптора подключена ко второй группе входов блока контроля и второй труппе входов блока индексации, группа выходов которого подключена к первой группе входов выходного коммутатора, выход которого соединен со входом выходного регистра, выход которого является выходом устройства, введены блок ассоциативной памяти адресов, блок регистровой памяти массивов, блок обращения в оперативную память, блок вычисления индекса массива, блок вычисления шага приращения, регистр адреса паспорта, формирователь переменных цикла, причем выход регистра адреса

паспорта подключен ко входу блока ассоциативной памяти адресов и ко второй группе входов вьЬсодного коммутатора, выходы входного регастра индексов подключены к первой группе входов блока вычисления индекса массива, первой группе входов формирователя переменных цикла и группе входов блока вычисления шага приращения, выходы входного регистра дескриптора подключены, ко второй rpynrte входов формирователя переменных цикла, выход которого подютючен ко второй группе входов блока вычисления индекса массива, выход которого подключен к третьей группе входов блока контроля и блока индексации, выход которого подключен к первой группе входов блока регистровой памяти массивов, вторая группа входов которого соединена с выходами блока вычисления шага приращения, первая группа выходов блока регистровой памяти массивов соединена с четвертой грзшпой входов блока индексации и третьей группой входов выходного коммутатора, а вторая труппа выходов - с пятой группой входов блока индексации, вход которого соединен с его выходом, группа выходов блока ассоциативной памяти адресов .соединена с третьей группой входов блока регистровой памяти массивов, четвертая группа входов которого соединена с группой выходов . блока обращения в оперативную память, входы регистра дескриптора, регистра индексов и регистра адреса являются соответствующими входами устройства.

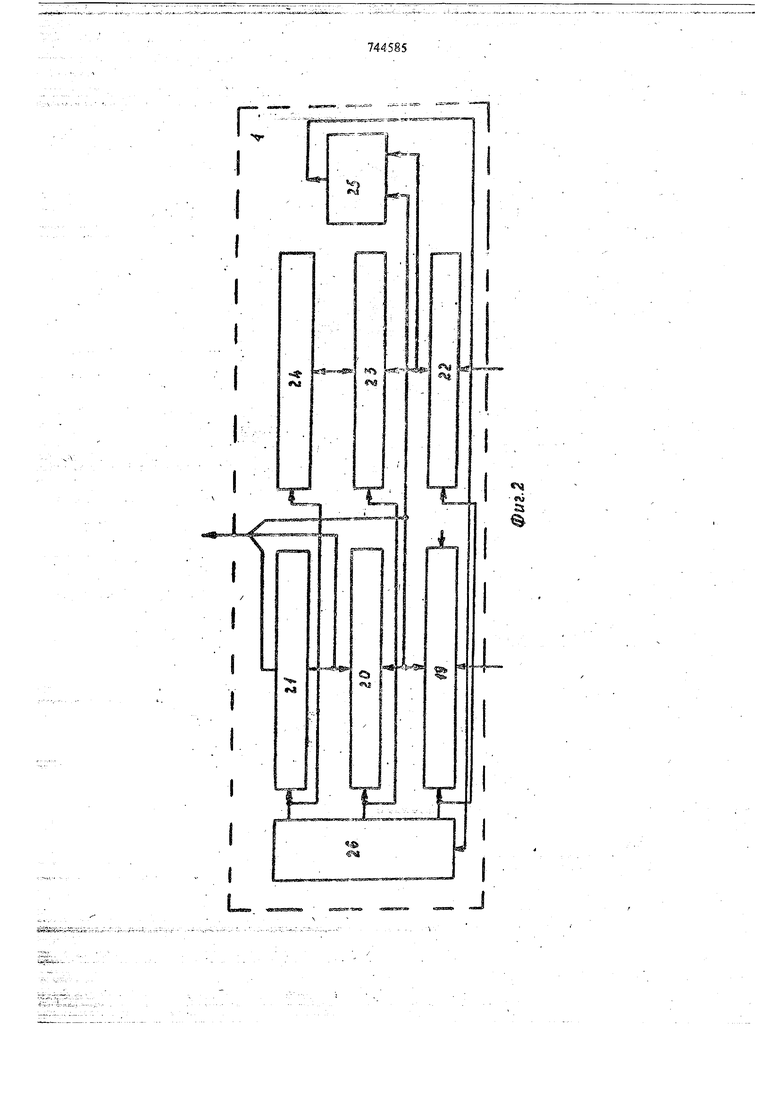

Причем формирователь переменных гдаклов содержит счетчик, пять регистров переменных цикла, схему сравнения и узел управления,

причем вход счетчика является первым входом формирователя, вход пятого регистра является вторым входом формирователя, выходы узла Зтяравления соединены с управляющими входами всех регистров переменных цикла и счетчика, а вход - с выходом схемы сравнения, первая группа входов которой соединена с выходами счетчика и третьего регистра, вторая группа входов схемы сравнения соединена с выходами пятого регистра и-входами четвертого регистра, соединенного двухсторонней связью с первым регистром, который связан двухсторонней связью с третьим регистром, выход которого, а также выход счетчика и выход первого регистра объединены и являются выходом формирователя.

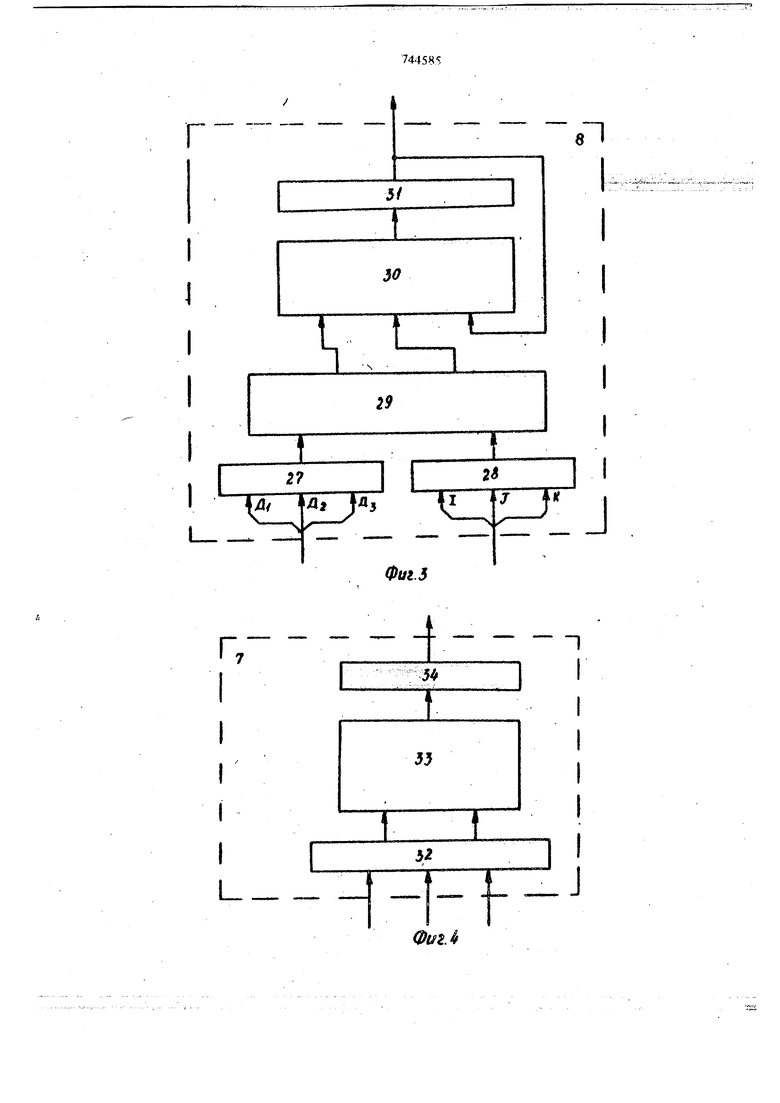

Кроме того, блок вычисления индекса массива содержит регистр, накапливающий сумматор, матричный умножитель и два входных коммутатора, выходы которых являются входами блока, а вЫХодьг - подключены ко входам матричного умножителя, первый и второй выходы соединены с соответствующими входами накапливающего сзтиматора, третий вход которого соединен с выходом регистра, вход которого соединен с выходом накапливающего сумматора, а выход - является выходом блок

При блок вычисления шага приращени содержит трехвходовой сумматор, сумматор с параллельным переносом и выходной регистр, причем входы трехвходового сумматора являются входами блока, а выходы - через сумматор с параллельным переносом соедюсены со входом выходного регистра, вьисод которого является выходом блока.

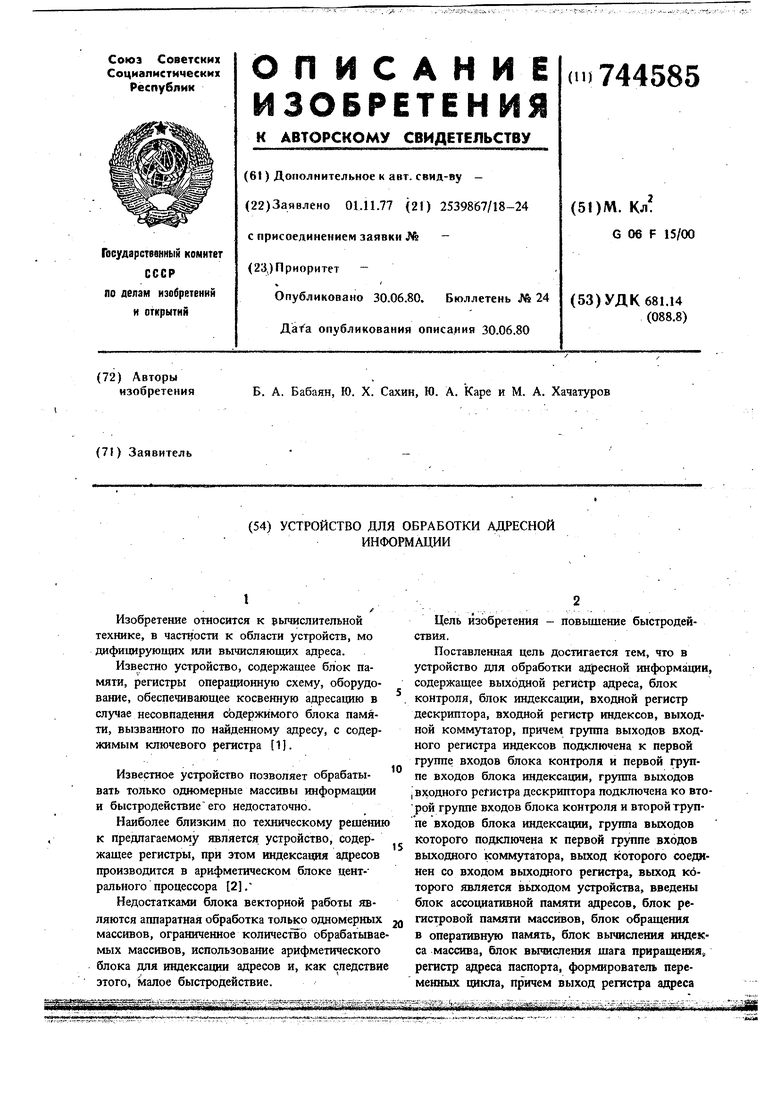

Кроме того блок обращения в оперативную память содержит счетчик массивов, дещифратор, триггеры занятости, группу элементов И, причем выходы счетчика массивов соединеньс со входами дешифратора, выходы которого соединены с первыми входами элементов И группы, вторые входы которых соединены с выходами триггеров занятости, выходы элементов И группы являются выходами блока.

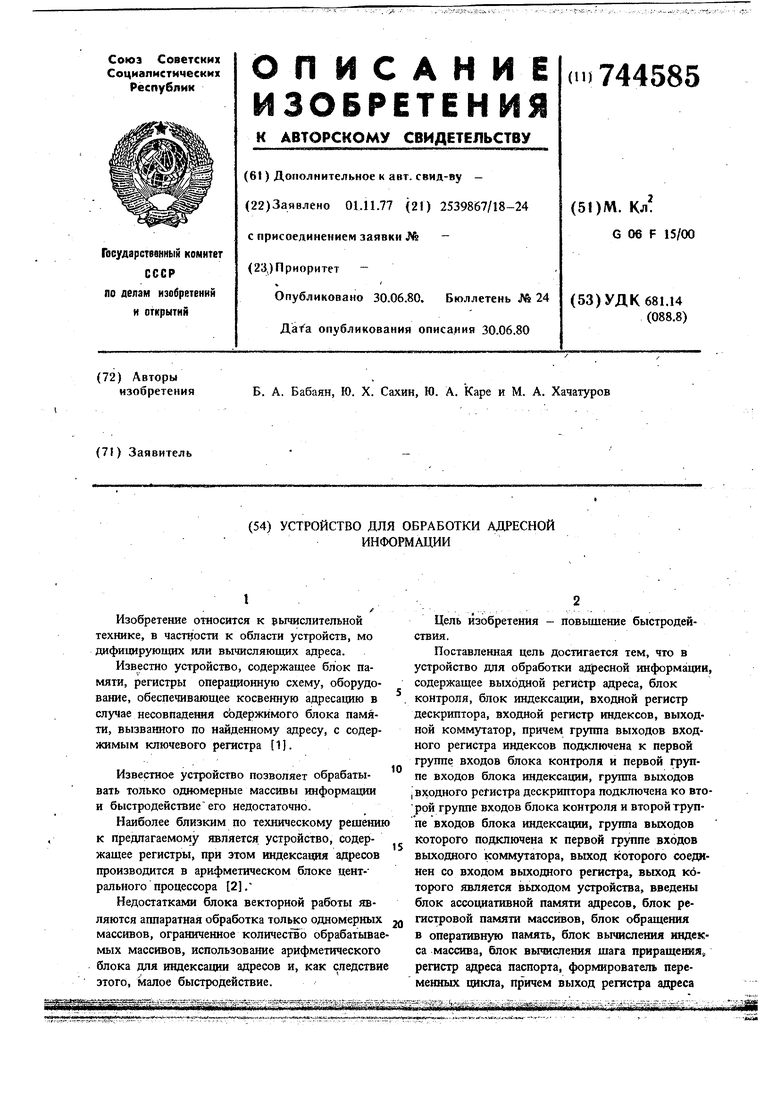

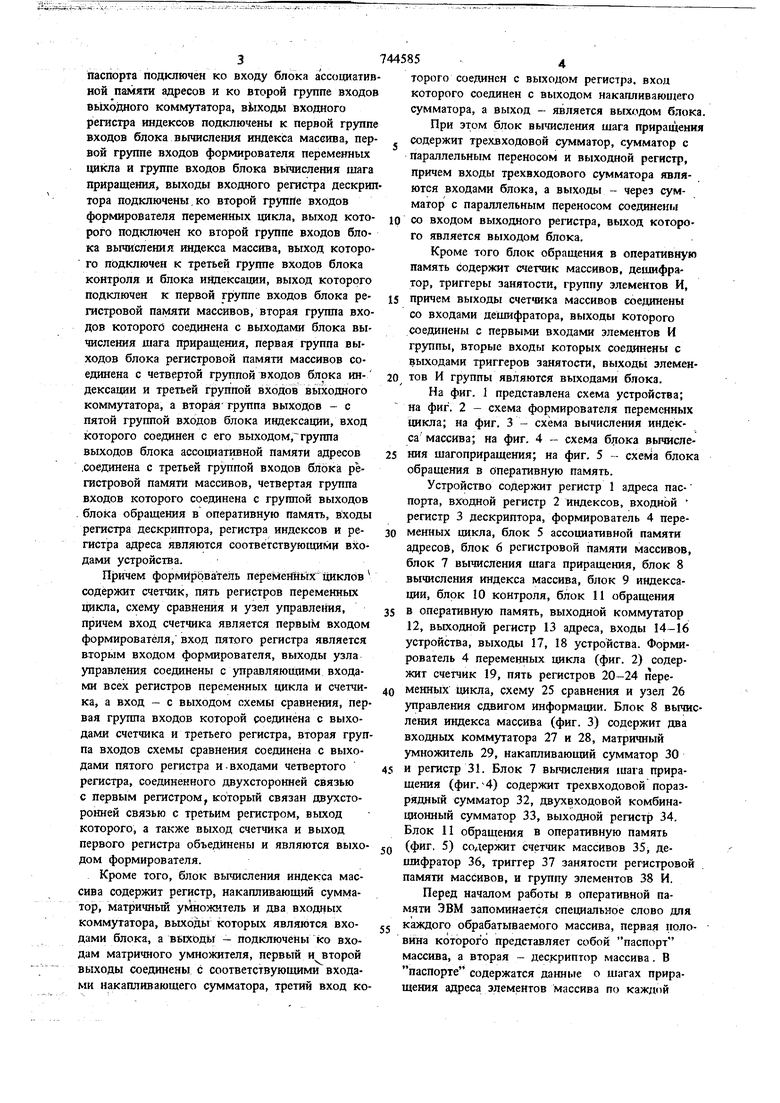

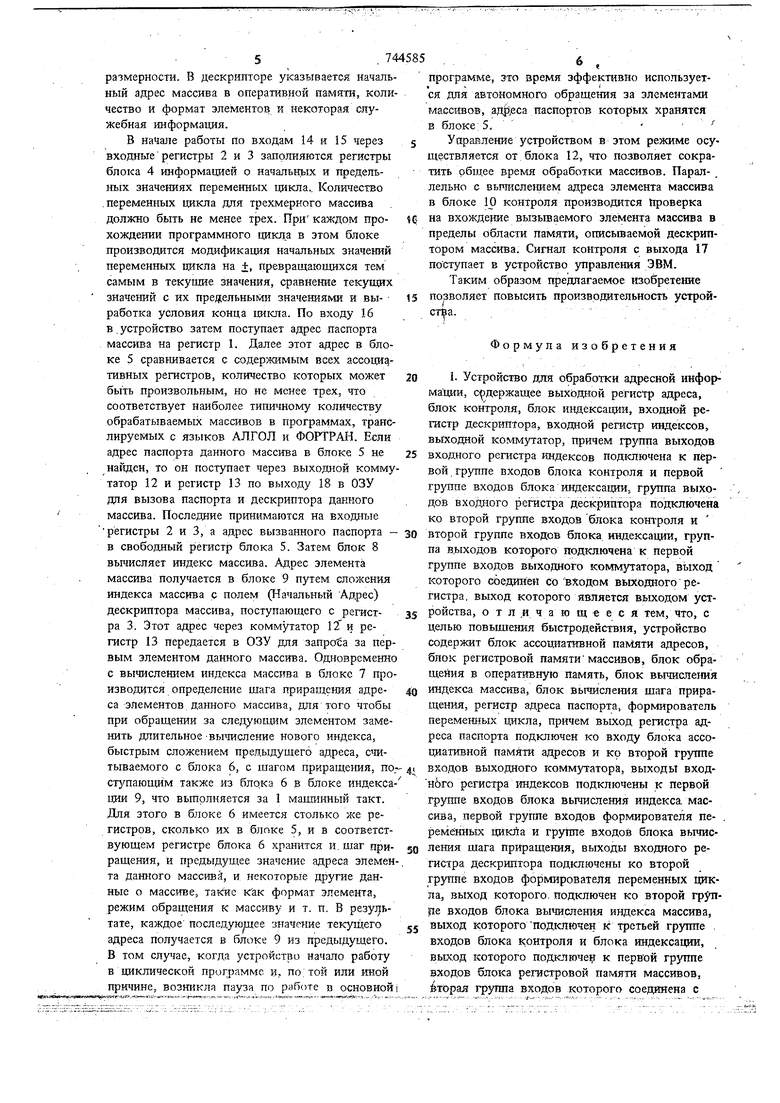

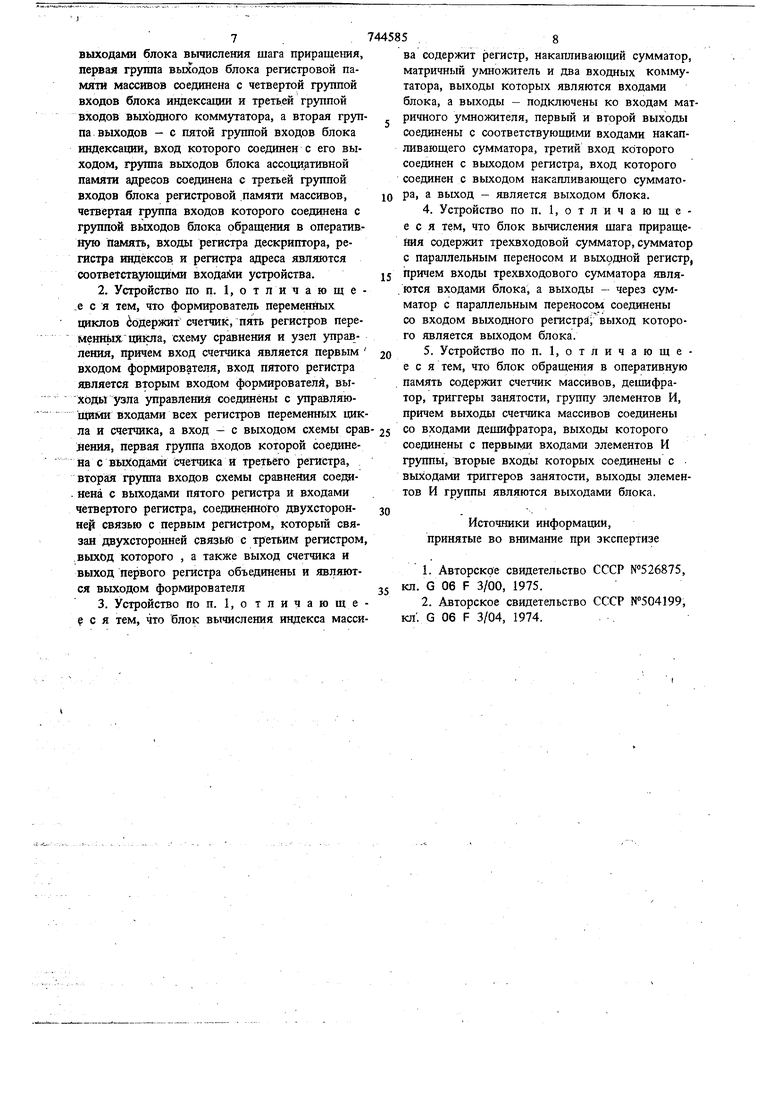

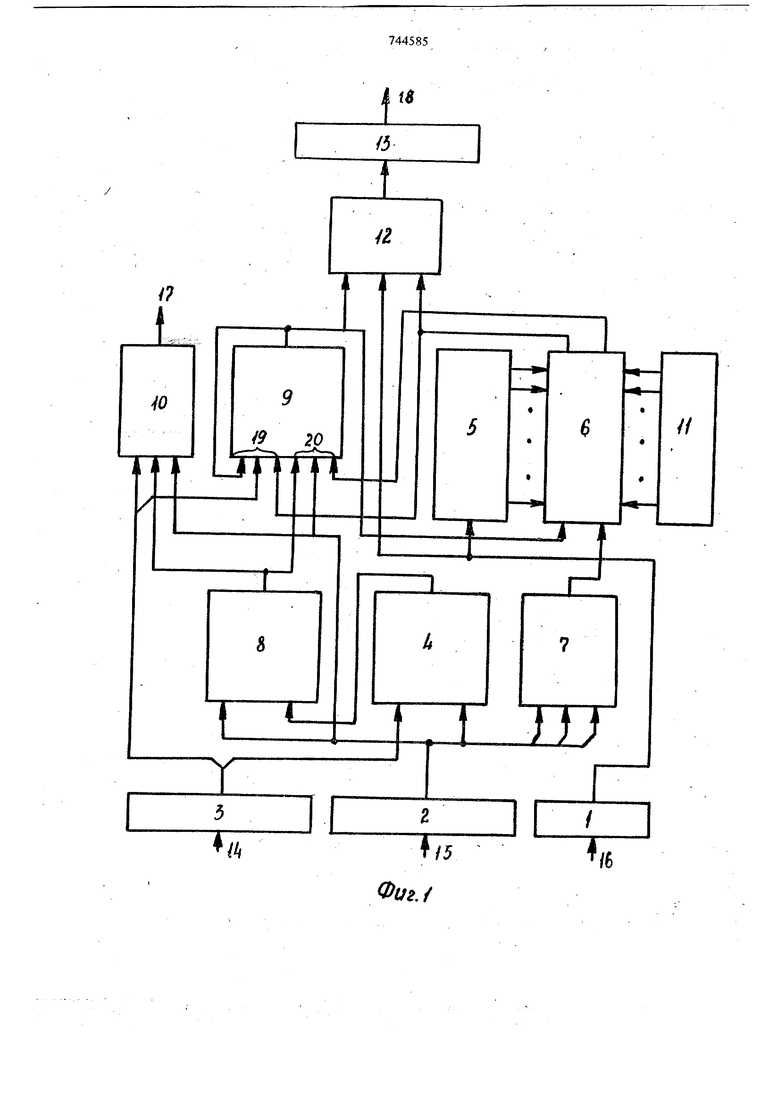

На фиг. 1 представлена схема устройства; на фиг . 2 - схема формирователя переменных цикла; на фиг. 3 - схема вычисления индекса массива; на фиг. 4 - схема блока вычисления щагоприращения; на фиг. 5 - схема блок обращения в оперативную память.

Устройство содержит регистр 1 адреса паспорта, входной регистр 2 Индексов, входной регистр 3 дескриптора, формирователь 4 переменных цикла, блок 5 ассоциативной памяти адресов, блок 6 регистровой памяти массивов, блок 7 выщ1сления шага приращения, блок 8 вычисления индекса массива, блок 9 индексации, блок 10 контроля, блок 11 обращения в оперативную память, выходной коммутатор 12, выходной регистр 13 адреса, входы 14-16 устройства, выходы 17, 18 устройства. Формирователь 4 переменных цикла (фиг. 2) содержит счетчик 19, пять регистров 20-24 переменных цикла, схему 25 сравнения и узел 26 управления сдвигом информации. Блок 8 вьршления индекса массива (фиг. 3) содержит два входных коммутатора 27 и 28, матричный умножитель 29, накапливающий сумматор 30 и регистр 31. Блок 7 вычисления шага приращения (фиг. Ч) содержит трехвходовой поразрядный сумматор 32, двухвходовой комбинационный сумматор 33, выходной регистр 34. Блок II обращения в оперативную память (фиг. 5) содержит счетчик массивов 35, дешифратор 36, триггер 37 занятости регистровой памяти массивов, и группу злементов 38 И.

Перед началом работы в оперативной памяти ЭВМ запоминается специальное слово для каждого обрабатываемого массива, первая половина которого представляет собой паспорт массива, а вторая - дескриптор массива. В паспорте содержатся данные о шагах приращения адреса элементов массива по каждой 5. 74 размерности. В дескрипторе указывается начальный адрес массива в оперативной памяти, количество и формат элементов к некоторая служебная информагщя. В начале работы по входам 14 и 15 через входные регистры 2 и 3 заполняются регистры блока 4 информацией о начальнъ1Х и предель1-гых значениях переменных цикла.. Количество .переменных цикла для трехмерного массива должно быть не менее трех. При каждом прохождении программного цикла в этом блоке производится модификация начальных значений переменных цикла на ±, превращающихся тем самым в текущие значения, сравнение текуидах значеьшй с их предельными значениями и выработка условия конца цикла. По входу 16 в. устройство затем поступает адрес паспорта , массива на регистр 1. Далее этот адрес в блоке 5 сравнивается с содержимым всех ассоци тивных регистров, количество которых может быть произвольным, но не менее трех, что соответствует наиболее тишгшому количеству обрабатываемых массивов в nporpaiviMax, транслируемых с языков АЛГОЛ и ФОРТРАН. Если адрес паспорта данного массива в блоке 5 не найден, то он поступает через выходной комму татор 12 и регистр 13 по выходу 18 в ОЗУ для вызова паспорта и дескриптора данного массива. Последние принимаются на входные регистры 2 и 3, а адрес вызванного паспорта - в свободный регистр блока 5. Затем блок 8 вычисляет индекс масс1ша. Адрес элемента массива получается в блоке 9 путем сложения индекса массива с полем (Начальный Адрес) дескриптора массива, поступающего с регистра 3. Этот адрес через коммутатор 12 и регистр 13 передается в ОЗУ для запроба за первым элементом данного массива. Одновременно с вычислением индекса массива в блоке 7 про изводится определение щага приращения адреса элементов, данного массива, для того чтобы при обращении за следующим элементом заменить длительное-вычисление нового индекса, быстрым сложением предыдущего адреса, считываемого с блока 6, с шагом прираще1шя, по ступающим также из блока 6 в блоке индекса 1ЩИ 9, что вьгарлняется за 1 машинный такт. Для этого в блоке 6 имеется столько же регистров, сколько их в блоке 5, и в соответствующем регистре блока 6 хранится и. шаг приращения, и предыдущее значение адреса элемен та данного массива, и некоторые другие данные о массиве, такие как формат элемента, режим обращения к массиву и т. п. В резул ьтате, каждое последующее значение текущего адреса получается в блоке 9 из предыдущего. В том случае, когда устройство начало работу в циклической программе и, по. той или иной причине, возникла пауза по работе в основной программе, это время эффективно используется для автономного обращения за элементами массшов, аД|);еса паспортов которых хранятся в блоке; 5. Управление устройством в этом режиме осуществляется от блока 12, что позволяет сократить общее время обработки массивов. Парал- . лельно с вычислением адреса элемента массива в блоке 10 контроля производится 1фоверка на вхождение вызьгааемого элемента массива в пределы области памяти, описьшаемой дескриптором массива. Сигнал контроля с выхода 17 поступает в устройство управления ЭВМ. Таким образом предлагаемое изобрете1ше позволяет повысить производительность устройФормула изобретения 1. Устройство для обработки адресной информации, содержащее выходной регистр адреса, блок контроля, блок индекса1щи, входной регистр дескриптора, входной регистр индексов, вьГходной коммутатор, причем группа выходов входного регастра индексов подключена к первой группе входов блока контроля и первой группе входов блока индексации, группа выходов входного регистра дескриптора подключена ко второй группе входов блока кош-роля и второй группе входов блока, индексации, группа в.ыходов которого подключена к первой группе входов выходного коммутатора, выход которого соединен совходом выходного регистра, выход которого является выходом устройства, о т л и ч а ю щ е е с Я тем, что, с целью повышения быстродействия, устройство содержит блок ассоциативной памяти адресов, блок регистровой памятимассивов, блок обращения в операт1;тную память, блок вычисления индекса массива, блок вычисления щага приращения, регистр адреса паспорта, формирователь переменных цикла, причем выход регистра адреса паспорта подключен ко входу блока ассоциативной памяти адресов и ко второй группе входов выходного коммутатора, выходы входнбго регистра индексов подключены к первой группе входов блока вычисления индекса массива, первой группе входов формирователя пе- . ремйшых цикйа и группе входов блока вычисле1шя щага приращения, выходы входного регистра дескриптора подютючены ко второй группе входов формирователя переменных цикла, выход которого, подключен ко второй rpjTiре входов блока вычисления индекса массива, выход которого подключен к третьей группе . входов блока контроля и блока индексации, ВЫХ.ОД которого подключен к первой группе входов блока регистровой памяти массивов, ёторал группа входов которого соединена с

выходами блока вычисления шага приращения, первая группа выходов блока регистровой памяти массивов соединена с четвертой группой входов блока индексации и третьей группой входов выходного комм)татора, а вторая группа выходов - с пятой группой входов блока ивдексации, вход которого соединен с его выходом, грзшпа выходов блока ассоциативной памяти адресов соединена с третьей группой входов блока регистровой памяти массивов, четвертая группа входов которого соединена с группой выходов блока обращения в оперативную память, входы регистра дескриптора, регистра индексов и регистра адреса являются соответствующими входа и устройства.

2.Устройство по п. 1, о т л и ч а ю щ е ,е с я тем, что формирователь переменйых циклов Содержит счетчик, пять регистров переменньК цикла, схему сравнения и узел управления, причем вход счетчика является первым входом формирователя, вход пятого регистра является вторым входом формирователи, выходы узла управления соединены с управляюи)( входами всех регистров переменных цикла и счетчика, а вход - с выходом схемы сравнения, первая группа входов которой соединена с выходами счетчика И третьего регистра, вторая группа входов схемы сравнения соеда. иена с выходами пятого регистра и входами четвертого регистра, соединенного двухсторонне{1 связью с первым регистром, который связан двзхсторонней связью с третьим регистром, выход которого , а также выход счетчика и выход первого регистра объединены и являются выходом формирователя

3.Устройство по п. 1, о тличающе с я тем, что блок вычисления индекса массива содержит регистр, накапливающий сумматор, матричный умножитель и два входных коммутатора, выходы которых являются входами блока, а выходы - подключены ко входам мат, ричного умножителя, первый и второй выходы соединены с соответствующими входами накапливающего сумматора, третий вход которого соединен с выходом регистра, вход которого соединен с выходом накапливающего сумматоQ ра, а выход - является выходом блока.

4. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок вычисления шага приращейия содержит трехвходовой сумматор, сумматор с параллельным переносом и выходной регистр,

5 причем входы трехвходового сумматора являются входами блока, а выходы - через сумматор с параллельным переносом соединены со входом выходного регистра выход которого является выходом блока.

0 5. Устройство по п. 1,отличающее с я тем, что блок обращения в оперативную . память содержит счетчик массивов, дешифратор, триггеры занятости, группу элементов И, причем выходы счетчика массивов соединены

5 со входами дешифратора, выходы которого соединены с первыми входами элементов И труппы, вторые входы которых соединены с . выходами триггеров занятости, выходы элементов И группы являются выходами блока.

Источники информащ1И,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР №526875, кл. G 06 F 3/00, 1975.

2.Авторское свидетельство СССР №504199, кл. G 06 F 3/04, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Устройство для выборки команд | 1978 |

|

SU726533A1 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для обработки информации | 1981 |

|

SU993262A1 |

| Устройство для адресации буферной памяти | 1978 |

|

SU717771A1 |

sS -«Ss

@

Г

г.

п

0Ut.5

I

Г 1

Г

И

Ui.J

Авторы

Даты

1980-06-30—Публикация

1977-11-01—Подача