Настоящее изобретение относится к способу регенерации ячеек памяти в динамическом запоминающем устройстве с произвольным доступом и, в частности, к способу, который уменьшает помехи регенерации на напряжении стока динамического запоминающего устройства с произвольным доступом, имеющего КМОП-структуру (комплементарную структуру метал-окисел-полупроводник).

Предпосылки создания настоящего изобретения

Как хорошо известно в этой области техники, динамические запоминающие устройства с произвольным доступом требуют периодической регенерации ячеек памяти в динамическом запоминающем устройстве с произвольным доступом так, чтобы данные, хранимые в каждой ячейке памяти, не разрушались или распадались за пределами установленного времени. Путем периодической регенерации каждой строки памяти в динамическом запоминающем устройстве с произвольным доступом к каждой ячейке емкостной памяти в строке энергию подают так, чтобы не разрушить данные, хранимые в ячейках памяти.

Таким образом, для энергозависимых запоминающих устройств регенерация является существенным элементом хранения запоминающего устройства.

Регенерация может быть выборкой адреса столбца перед регенерацией выборки адреса строки или только регенерацией выборки адреса строки. Выборка адреса столбца перед регенерацией выборки адреса строки включает в себя установление уровня сигнала выборки адреса столбца прежде, чем устанавливают сигнал выборки адреса строки для указания на то, что следующий цикл является циклом регенерации. В ответ на установление сигнала выборки адреса столбца перед установлением сигнала выборки адреса строки внутренний счетчик адреса в запоминающем устройстве сообщает адрес строки следующей строки, подлежащей регенерации. Регенерация только выборки адреса строки работает аналогичным образом для регенерации выбранных строк запоминающего устройства; за исключением того, что адрес строки, подлежащей регенерации, сообщается внешней схемой регенерации.

Однако всякий раз, когда осуществляется регенерация, выброс тока в регенерируемом динамическом запоминающем устройстве с произвольным доступом приводит к падению напряжения сети, подаваемого на динамическое запоминающее устройство с произвольным доступом. Помехи, вызванные падением напряжения сети, могут оказать воздействие на работу этого динамического запоминающего устройства с произвольным доступом или других динамических устройств с произвольным доступом, на которые оно подается. Это особенно относится к динамическим запоминающим устройствам с произвольным доступом, в которых использована КМОП-технология, поскольку внутренние схемы таких динамических запоминающих устройств с произвольным доступом особенно чувствительны к внезапным падениям напряжения или помехам.

Таким образом, для предотвращения больших всплесков помех в процессе цикла регенерации способы регенерации, соответствующие предшествующему уровню техники, обеспечивают предполагаемые регенерации в шахматном порядке, осуществляемые в смежных модулях памяти с однорядным расположением выводов так, чтобы регенерации осуществлялись, следуя одна за другой и были разделены по меньшей мере одним периодом повторения тактовых или синхронизирующих импульсов. Кроме того, для уменьшения величины падения напряжения, вызываемого доступами регенерации, предусматривают конденсаторы сглаживающего фильтра для каждого блока памяти для поддержания напряжения сети в процессе большого выброса тока. Хотя этот способ предназначен для распределения падения напряжения, возникающего в процессе регенерации, равномерно по множеству периодов повторения тактовых или синхронизирующих импульсов, уменьшение падения напряжения еще не оптимизировано. Это имеет место, поскольку иногда смежные блоки памяти совместно используют один или более конденсаторов сглаживающего фильтра, так что, если, например, первый и второй блоки памяти регенерируют последовательно, конденсаторы сглаживающего фильтра не имеют достаточного времени восстановления, чтобы вновь зарядиться до номинального напряжения сети. Таким образом, если блоки памяти, совместно использующие один конденсатор сглаживающего фильтра, регенерируются в течение последовательных периодов повторения тактовых или синхронизирующих импульсов, то имеется вероятность того, что на линии подвода электрического напряжения, соединенной с имеющими доступ блоками памяти, возникает большое падение напряжения, и того, что возникающие в результате этого падения напряжения, помехи повлияют на работу динамических запоминающих устройств с произвольной выборкой.

Известен способ регенерации блоков динамической памяти (SU авторское свидетельство 982081 G 11 C 11/401, 1982). Недостатки указанного способа приведены выше.

Целью настоящего изобретения является ликвидация указанных недостатков.

Указанная цель достигается использованием способа регенерации энергонезависимых блоков памяти, включающего инициирование регенерации блоков памяти, причем для сглаживания падений напряжения на линии подачи напряжения используют конденсатор сглаживающего фильтра общий для первого и второго блоков памяти, причем сначала инициируют регенерацию первого блока памяти, затем инициируют регенерацию третьего блока памяти, после чего инициируют регенерацию второго блока памяти. Предпочтительно первый, второй и третий блоки памяти являются блоками памяти, выполненными по КМОП-технологии. Преимущественно дополнительно предусматривают инициирование регенерации четвертого блока памяти, следующее за инициированием регенерации второго блока памяти, причем указанные третий и четвертый блоки памяти совместно используют другой конденсатор сглаживающего фильтра. Обычно каждая регенерация предусматривает выборку адреса столбца перед регенерацией выборки адреса строки.

Указанная цель достигается так же и тем, что используют способ уменьшения падения подаваемого напряжения при регенерации блоков памяти, включающий инициирование регенерации блоков памяти, причем инициируют регенерацию первого блока памяти совместно со вторым блоком памяти, использующего, по меньшей мере, один конденсатор сглаживающего фильтра, инициируют регенерацию указанного второго блока памяти после проведения достаточного количества циклов регенерации, инициированных на блоке памяти, не использующем указанный конденсатор, используемый первым и вторым блоками, причем указанную регенерацию второго блока памяти проводят таким образом, чтобы падение напряжения на указанных первом и втором блоках памяти было не выше, чем падение напряжения на первом и втором блоках при раздельном проведении регенерации на указанных блоках. Преимущественно указанное достаточное количество циклов регенерации является одним циклом регенерации. Предпочтительно каждая указанная регенерация предусматривает выборку адреса столбца, проводимую до регенерации выборки адреса строки.

Краткое описание чертежей

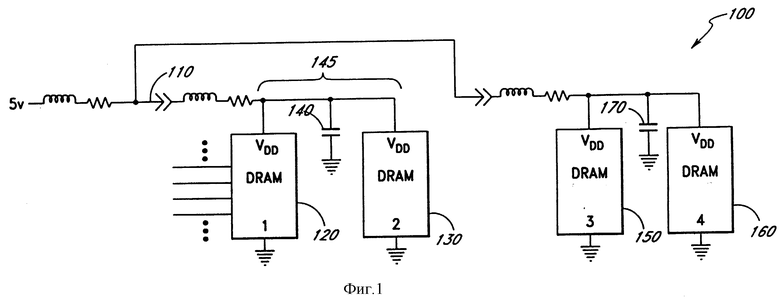

Фиг. 1 - принципиальная блок-схема, которая иллюстрирует две пары блоков памяти, каждая из которых совместно использует конденсатор сглаживающего фильтра.

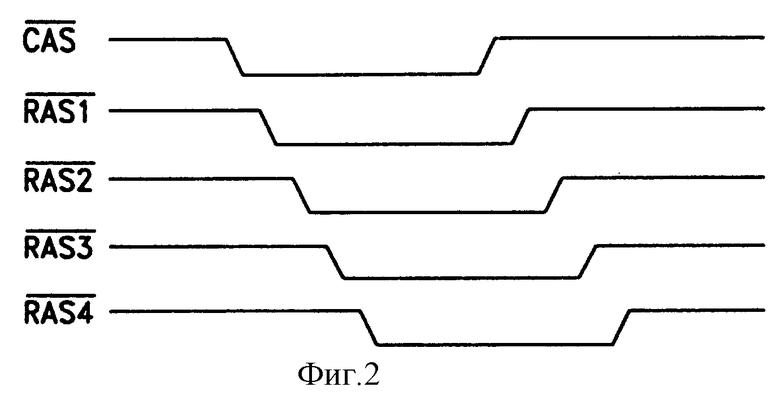

Фиг. 2 - временная диаграмма, которая иллюстрирует порядок доступов регенерации к каждому из блоков памяти в соответствии со способом предшествующего уровня техники.

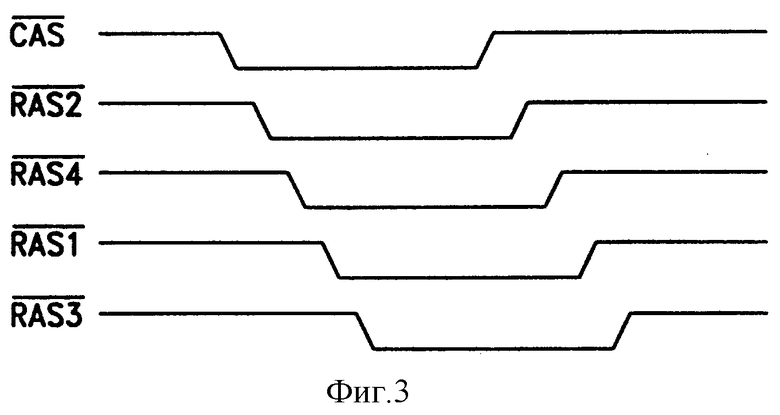

Фиг. 3 - временная диаграмма, которая иллюстрирует порядок доступов регенерации к каждому из блоков памяти, показанных на фиг. 1, в соответствии со способом настоящего изобретения.

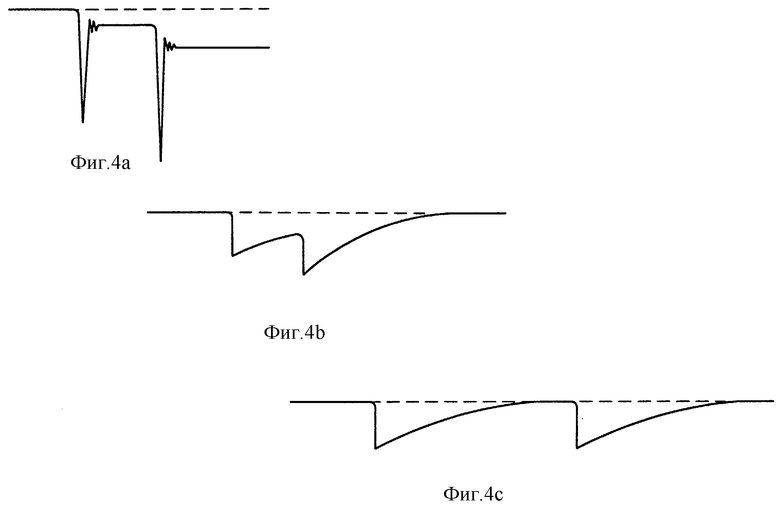

Фиг. 4a-4c- схемы прохождения сигнала, которые иллюстрируют падение напряжения, которые имеют место в процессе регенерации для того случая, где (a) - способ предшествующего уровня техники, используемый для доступа в шахматном порядке к смежным блокам памяти, в которых не используют конденсатор сглаживающего фильтра; (b) - способ предшествующего уровня техники, используемый для регенерации смежных блоков памяти, совместно использующих один и тот же конденсатор сглаживающего фильтра; и (c) - способ, соответствующий настоящему изобретению, используемый для доступа к смежным блокам памяти в разнесенных интервалах, где конденсатор сглаживающего фильтра используют совместно между блоками памяти.

Подробное описание предпочтительного варианта осуществления настоящего изобретения

Фиг. 1 - принципиальная блок-схема, которая иллюстрирует некоторое количество блоков 100 памяти динамического запоминающего устройства с произвольным доступом в связи с линией 110 подачи напряжения. Как показано на фиг. 1, первый блок 120 памяти динамического запоминающего устройства с произвольным доступом и второй блок 130 памяти динамического запоминающего устройства с произвольным доступом совместно используют батарею 140 конденсаторов сглаживающего фильтра. Такое исполнение характерно для тех случаев применения, где, например, модули памяти с двухрядным расположением выводов выполнены так, чтобы иметь динамические запоминающие устройства с произвольным доступом на обеих сторонах печатной платы. Как будет очевидно для обычных специалистов в этой области техники, батарея 140 конденсаторов может содержать некоторое количество конденсаторов, совместно используемых каждым из элементов динамического запоминающего устройства с произвольным доступом в блоках 120,130 памяти динамического запоминающего устройства с произвольным доступом. Аналогичным образом, как дополнительно показано на фиг. 1, третий блок 150 памяти динамического запоминающего устройства с произвольным доступом и четвертый блок 160 памяти динамического запоминающего устройства с произвольным доступом совместно используют батарею 170 конденсаторов.

В процессе работы, регенерации ячеек памяти в каждом из блоков 120, 130, 150 и 160 памяти динамического запоминающего устройства с произвольным доступом осуществляют в заданном порядке так, чтобы уменьшить мгновенное потребление тока по линии 110. Как хорошо известно квалифицированным в этой области техники специалистам, линия 110 подачи напряжения обладает некоторым импедансом, так что, если в некоторой точке на линии 110 имеет место внезапный выброс тока, то возникает вероятность того, что в этом месте линии 110 будет наблюдаться большое падение напряжения. По этой причине конденсаторы 140, 170 сглаживающего фильтра включены в нескольких местах по линии 110 источника напряжения для уменьшения эффектов такого падения напряжения. Кроме того, для уменьшения общего выброса тока в любом данном месте вдоль линии 110 доступы регенерации, которые часто являются ответственными за внезапные выбросы тока на линии 110, осуществляют в шахматном порядке.

Некоторые способы, соответствующие предшествующему уровню техники, уменьшения выброса тока в любом данном месте вдоль линии 110 предусматривали регенерации, осуществляемые в шахматном порядке, каждого из блоков памяти динамического запоминающего устройства с произвольным доступом так, чтобы селекторная линия адреса строки не устанавливалась в одно и то же время для любого из блоков 120, 130, 150, 160 памяти динамического запоминающего устройства с произвольным доступом. Как показано на фиг. 2, для инициирования операции регенерации, после селекторной линии адреса столбца последовательно устанавливают каждую из селекторных линий адреса строки (то есть линий, соответствующих каждому блоку 120, 130, 150, 160 памяти динамического запоминающего устройства с произвольным доступом) соответственно. Однако, если селекторные сигналы адреса строки установлены в быстрой последовательности для блоков памяти динамического запоминающего устройства с произвольным доступом, совместно использующих одни и те же конденсаторы сглаживающего фильтра, возникает вероятность того, что конденсаторы сглаживающего фильтра не будут иметь достаточно времени для восстановления после выброса тока, который следует за установкой выборки первой строки, так что дополнительный выброс тока, который следует за установкой селекторного сигнала адреса второй строки приводит к падению напряжения вдоль линии 110 от уровня напряжения, который уже ниже нормального уровня напряжения. Этот случай иллюстрируется на фиг. 4a и фиг. 4b. В частности, на фиг. 4a показано падение напряжения, которое бы имело место вдоль линии 110 в блоках 120, 130 памяти динамического запоминающего устройства с произвольным доступом, если сигнал выборки адреса строки второго блока памяти установлен непосредственно после сигнала выборки доступа строки первого блока памяти (как показано на фиг. 2) при отсутствии конденсатора 140 сглаживающего фильтра. Таким образом, на фиг. 4a иллюстрируется непосредственная близость падений напряжений, наблюдаемых на входах напряжения в блоки 120, 130 памяти динамического запоминающего устройства с произвольным доступом, когда эти смежные блоки памяти регенерируют в последовательных периодах повторения тактовых или синхронизирующих импульсов.

Поскольку конденсатор 140 сглаживающего фильтра представлен на линии 110 смежно блокам 120, 130 памяти динамического запоминающего устройства с произвольным доступом, наблюдаемое падение напряжения имеет вид, как показано на фиг. 4b. Хотя падение напряжения, наблюдаемое на входах напряжения в блоки 120, 130 памяти динамического запоминающего устройства с произвольным доступом не так велико, как падение напряжения, которое было бы, если бы не было конденсатора 140 при первом падении напряжения, когда имеет место второе падение напряжения, в то время как напряжение на линии 110 вблизи блоков 120, 130 памяти динамического запоминающего устройства с произвольным доступом еще не восстановилось до своего исходного значения, при установке второго селекторного сигнала адреса строки наблюдается большое падение. Таким образом очевидно, что в некоторых случаях способ, соответствующий предшествующему уровню техники, приводит к значительному падению напряжения на входах напряжения, смежных блокам памяти динамического запоминающего устройства с произвольным доступом, если регенерацию осуществляют в быстрой последовательности, так что конденсатор 140 сглаживающего фильтра не имеет времени для восстановления из первоначального падения напряжения. Эта проблема дополнительно усугубляется, если в блоках 120, 130 памяти динамического запоминающего устройства с произвольным доступом использована КМОП-технология, поскольку КМОП-технология особенно чувствительна к помехам при наличии таких падений напряжения.

Однако в соответствии с настоящим изобретением предлагается усовершенствованный способ доступа блоков памяти динамического запоминающего устройства с произвольным доступом в процессе регенерации, как показано на фиг. 3. Как показано на фиг. 3, последовательность регенераций динамического запоминающего устройства с произвольным доступом изменяют так, чтобы блоки памяти динамического запоминающего устройства с произвольным доступом, совместно использующие одни и те же конденсаторы сглаживающего фильтра, не имели доступа в последовательных периодах повторения тактовых или синхронизирующих импульсов. То есть, как показано на фиг. 3, выборку адреса строки, используемую для регенерации второго блока 130 памяти динамического запоминающего устройства с произвольным доступом, устанавливают перед селекторным сигналом адреса строки, используемым для регенерации четвертого блока 160 памяти динамического запоминающего устройства с произвольным доступом, следующего перед селекторным сигналом адреса строки, используемым для регенерации первого блока 120 памяти динамического запоминающего устройства с произвольным доступом, и наконец устанавливают селекторный сигнал адреса строки, используемый для регенерации третьего блока 150 памяти динамического запоминающего устройства с произвольным доступом. Таким образом, из фиг. 3 следует, что регенерации блоков памяти, совместно использующих один и тот же конденсатор сглаживающего фильтра, никогда не инициируют в последовательных периодах повторений тактовых или синхронизирующих импульсов.

Преимущества этой усовершенствованной последовательности регенерации показаны на фиг. 4c. Как показано на фиг. 4c, падения напряжения достаточно разнесены друг относительно друга так, чтобы конденсатор 140 имел достаточно времени для восстановления до исходной величины 5B прежде, чем на конденсаторе 140 наблюдается следующее падение напряжения. В этом случае на входах напряжения блоков 120, 130 памяти динамического запоминающего устройства с произвольным доступом имеют место только небольшие падения напряжения. Аналогичные эффекты наблюдаются также у блоков 150, 160 памяти динамического запоминающего устройства с произвольным доступом. Таким образом, усовершенствованный способ последовательности регенерации, соответствующий настоящему изобретению, гарантирует отсутствие значительного падения напряжения в любом из блоков 120, 130, 150 и 160 памяти динамического запоминающего устройства с произвольным доступом.

Хотя был подробно описан предпочтительный вариант осуществления настоящего изобретения, квалифицированному специалисту в этой области техники будут очевидны модификации, которые могут быть сделаны без отклонения от его объема или основных характеристик. Например, настоящее изобретение может быть использовано в системе, в которой вместо выборки доступа столбца перед регенерациями выборки адреса строки осуществляют регенерации только выборки доступа строки. По этой причине объем настоящего изобретения должен быть интерпретирован в свете прилагаемой формулы изобретения.

Изобретение относится к способу регенерации ячеек памяти в динамическом запоминающем устройстве с произвольным доступом и, в частности, к способу, который уменьшает помехи регенерации на напряжении стока динамического запоминающего устройства с произвольным доступом, имеющего КМОП-структуру. Техническим результатом является увеличение времени для восстановления подаваемого напряжения до его исходного уровня. Способы заключаются в том, что в процессе циклов регенерации осуществляют последовательный доступ к блокам памяти, которые не используют общие конденсаторы сглаживающего фильтра. 2 с. и 5 з.п.ф-лы, 4 ил.

| Способ управления регенерацией информации в блоках динамической памяти | 1980 |

|

SU982081A1 |

| JP 61050287 A, 12.03.1986 | |||

| US 5113372 A, 12.05.1992 | |||

| УНИВЕРСАЛЬНАЯ ПОТОЧНАЯ ЛИНИЯ ИЗОЛЯЦИИ ТРУБ | 2002 |

|

RU2199694C1 |

Авторы

Даты

2001-02-10—Публикация

1996-06-27—Подача