iCJ

о

4 IOO х4

Изобретение относится к импульсной технике и может быть использовано для фазовой автоподстройки генерируемой частоты относительно эталонной частоты в измерительных устройствах, а также в приемных и передающих устройствах.

Цель изобретения - упрощение устройства и повышение точности фазовой автоподстройки частоты.

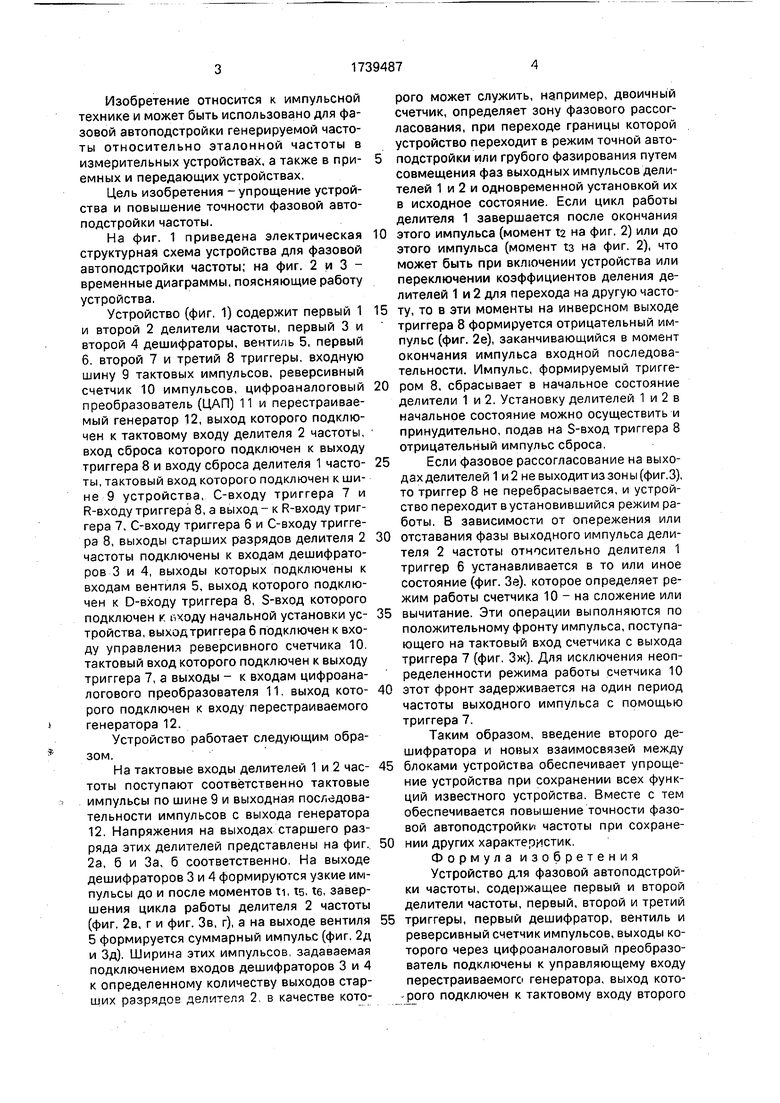

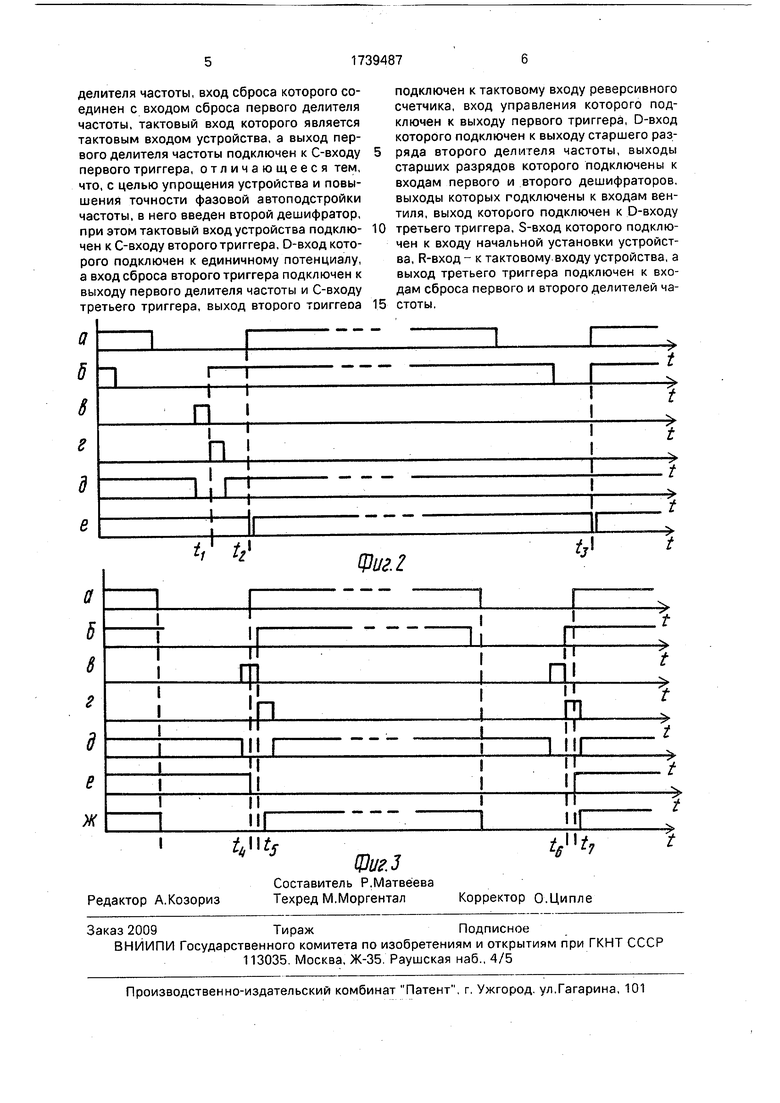

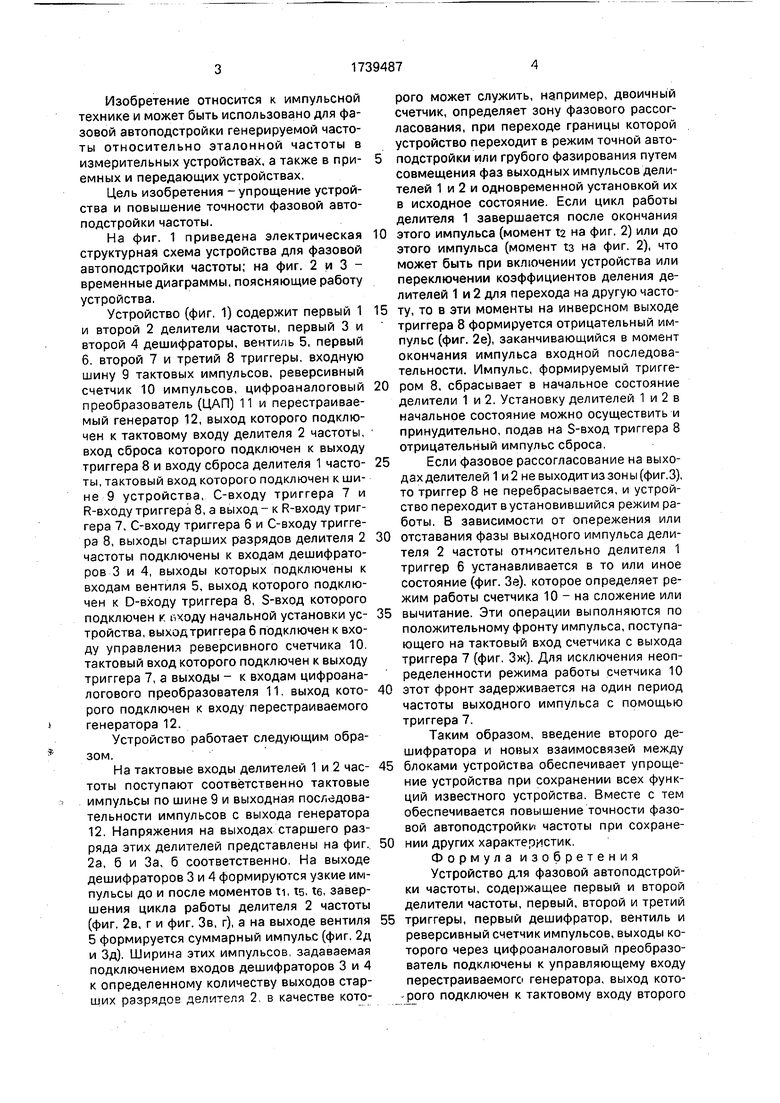

На фиг. 1 приведена электрическая структурная схема устройства для фазовой автоподстройки частоты; на фиг. 2 и 3 - временные диаграммы, поясняющие работу устройства.

Устройство (фиг. 1) содержит первый 1 и второй 2 делители частоты, первый 3 и второй 4 дешифраторы, вентиль 5, первый 6, второй 7 и третий 8 триггеры, входную шину 9 тактовых импульсов, реверсивный счетчик 10 импульсов, цифроаналоговый преобразователь (ЦАП) 11 и перестраиваемый генератор 12, выход которого подключен к тактовому входу делителя 2 частоты, вход сброса которого подключен к выходу триггера 8 и входу сброса делителя 1 частоты, тактовый вход которого подключен к шине 9 устройства, С-входу триггера 7 и R-входу триггера 8, а выход - к R-входу триггера 7, С-входу триггера 6 и С-входу триггера 8, выходы старших разрядов делителя 2 частоты подключены к входам дешифраторов 3 и 4, выходы которых подключены к входам вентиля 5, выход которого подключен к D-входу триггера 8, S-вход которого подключен к пходу начальной установки устройства, выход триггера б подключен к входу управления реверсивного счетчика 10. тактовый вход которого подключен к выходу триггера 7, а выходы - к входам цифроана- логового преобразователя 11. выход которого подключен к входу перестраиваемого генератора 12.

Устройство работает следующим образом.

На тактовые входы делителей 1 и 2 частоты поступают соответственно тактовые импульсы по шине 9 и выходная последовательности импульсов с выхода генератора 12. Напряжения на выходах старшего разряда этих делителей представлены на фиг. 2а, б и За, б соответственно. На выходе дешифраторов 3 и 4 формируются узкие импульсы до и после моментов ti, 15, te, завершения цикла работы делителя 2 частоты (фиг. 2в, г и фиг. Зв, г), а на выходе вентиля 5 формируется суммарный импульс (фиг, 2д и Зд). Ширина этих импульсов, задаваемая подключением входов дешифраторов 3 и 4 к определенному количеству выходов старших разрядов делителя 2. в качестве которого может служить, например, двоичный счетчик, определяет зону фазового рассогласования, при переходе границы которой устройство переходит в режим точной автоподстройки или грубого фазирования путем Совмещения фаз выходных импульсов делителей 1 и 2 и одновременной установкой их в исходное состояние. Если цикл работы делителя 1 завершается после окончания

0 этого импульса (момент iz на фиг. 2) или до этого импульса (момент ta на фиг. 2), что может быть при включении устройства или переключении коэффициентов деления делителей 1 и 2 для перехода на другую часто5 ту, то в эти моменты на инверсном выходе триггера 8 формируется отрицательный импульс (фиг. 2е), заканчивающийся в момент окончания импульса входной последовательности. Импульс, формируемый тригге0 ром 8, сбрасывает в начальное состояние делители 1 и 2. Установку делителей 1 и 2 в начальное состояние можно осуществить и принудительно, подав на S-вход триггера 8 отрицательный импульс сброса.

5 Если фазовое рассогласование на выходах делителей 1 и 2 не выходит из зон ы(фиг.З), то триггер 8 не перебрасывается, и устройство переходит в установившийся режим работы. В зависимости от опережения или

0 отставания фазы выходного импульса делителя 2 частоты относительно делителя 1 триггер 6 устанавливается в то или иное состояние (фиг. Зе), которое определяет режим работы счетчика 10 - на сложение или

5 вычитание. Эти операции выполняются по положительному фронту импульса, поступающего на тактовый вход счетчика с выхода триггера 7 (фиг. Зж). Для исключения неопределенности режима работы счетчика 10

0 этот фронт задерживается на один период частоты выходного импульса с помощью триггера 7.

Таким образом, введение второго дешифратора и новых взаимосвязей между

5 блоками устройства обеспечивает упрощение устройства при сохранении всех функций известного устройства. Вместе с тем обеспечивается повышение точности фазовой автоподстройки частоты при сохране0 нии других характеристик.

Формула изобретения Устройство для фазовой автоподстройки частоты, содержащее первый и второй делители частоты, первый, второй и третий

5 триггеры, первый дешифратор, вентиль и реверсивный счетчик импульсов, выходы которого через цифроаналоговый преобразователь подключены к управляющему входу перестраиваемого генератора, выход кото- -ррго подключен к тактовому входу второго

делителя частоты, вход сброса которого соединен с входом сброса первого делителя частоты, тактовый вход которого является тактовым входом устройства, а выход первого делителя частоты подключен к С-входу первого триггера, отличающееся тем, что, с целью упрощения устройства и повышения точности фазовой автоподстройки частоты, в него введен второй дешифратор, при этом тактовый вход устройства подключен к С-входу второго триггера, D-вход которого подключен к единичному потенциалу, а вход сброса второго триггера подключен к выходу первого делителя частоты и С-входу третьего триггера, выход второго тоиггеоа

0

5

подключен к тактовому входу реверсивного счетчика, вход управления которого подключен к выходу первого триггера, D-вход которого подключен к выходу старшего разряда второго делителя частоты, выходы старших разрядов которого подключены к входам первого и второго дешифраторов, выходы которых подключены к входам вентиля, выход которого подключен к D-входу третьего триггера, S-вход которого подключен к входу начальной установки устройства, R-вход - к тактовому входу устройства, а выход третьего триггера подключен к входам сброса первого и второго делителей частоты,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1987 |

|

SU1503070A1 |

| Цифровой синтезатор частоты | 1989 |

|

SU1637022A2 |

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

| Устройство для восстановления информации | 1990 |

|

SU1707620A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Частотный компаратор | 1981 |

|

SU1023630A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Устройство автоматической подстройки частоты | 1989 |

|

SU1698987A1 |

Изобретение относится к импульсной технике и может быть использовано для фазовой автоподстройки генерируемой частоты относительно эталонной частоты в измерительных, приемных и и передающих устройствах. Устройство содержит делители 1 и 2 частоты, дешифраторы 3, 4, триггеры 6-8. реверсивный счетчик 10, цифроанало- говый преобразователь 11, перестраиваемый генератор 12, вентиль 5. 3 ил.

а 5

| Авторское свидетельство СССР № 1500070, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-06-07—Публикация

1990-09-21—Подача