Изобретение относится к системам автоматики и может быть использовано в автоматизированных системах управления машинами, механизмами, поточными линиями и т.д.

Цель изобретения - уменьшение количества командных шин, повышение надежности работы блока синхронизации и упрощение конструкции вычислительного блока с сохранением его функциональных возможностей, а следовательно, повышение надежности работы и упрощение конструкции всего устройства.

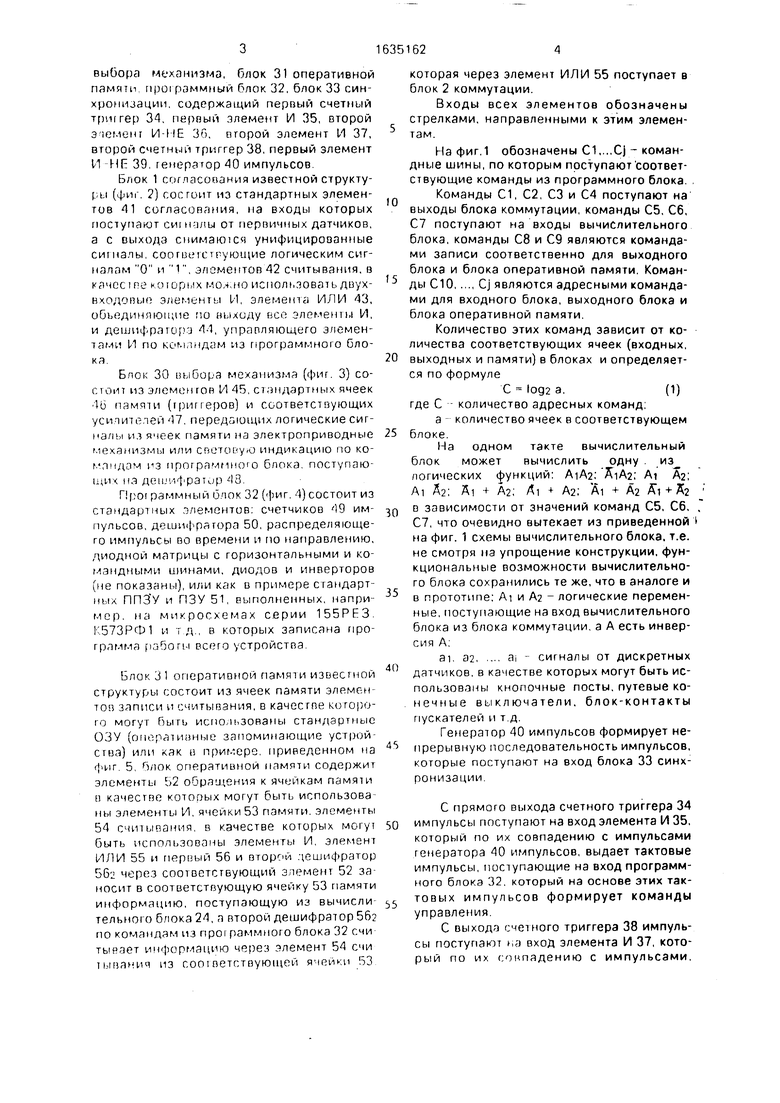

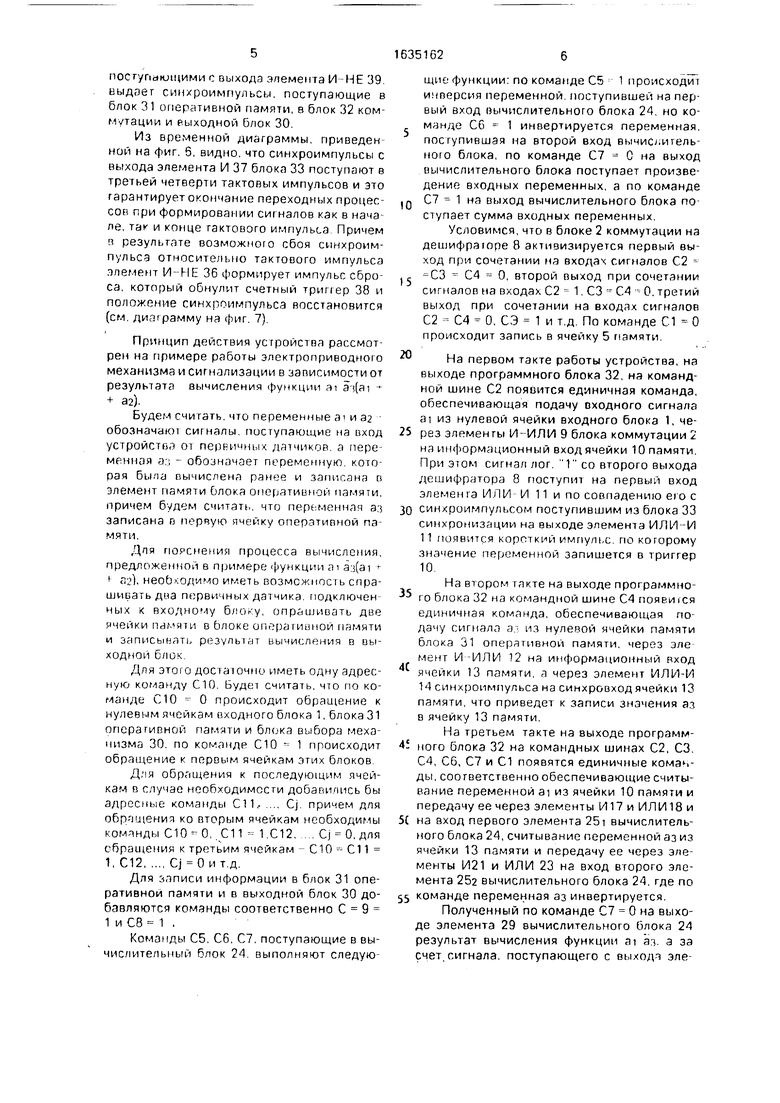

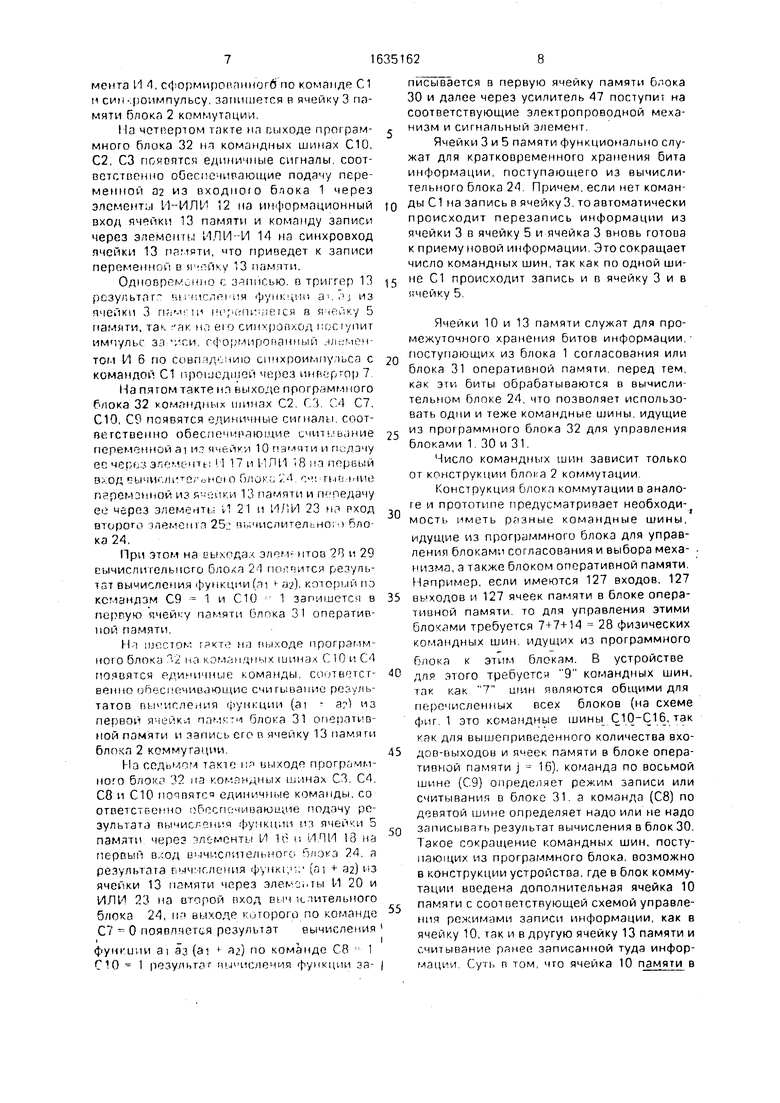

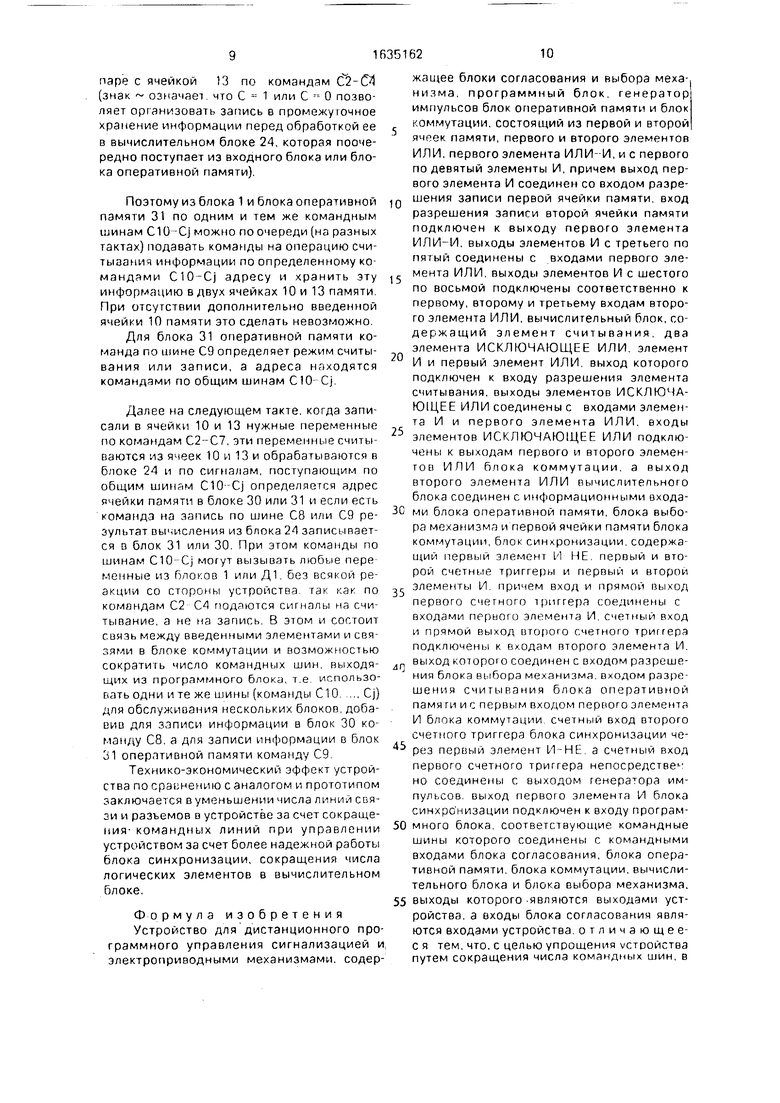

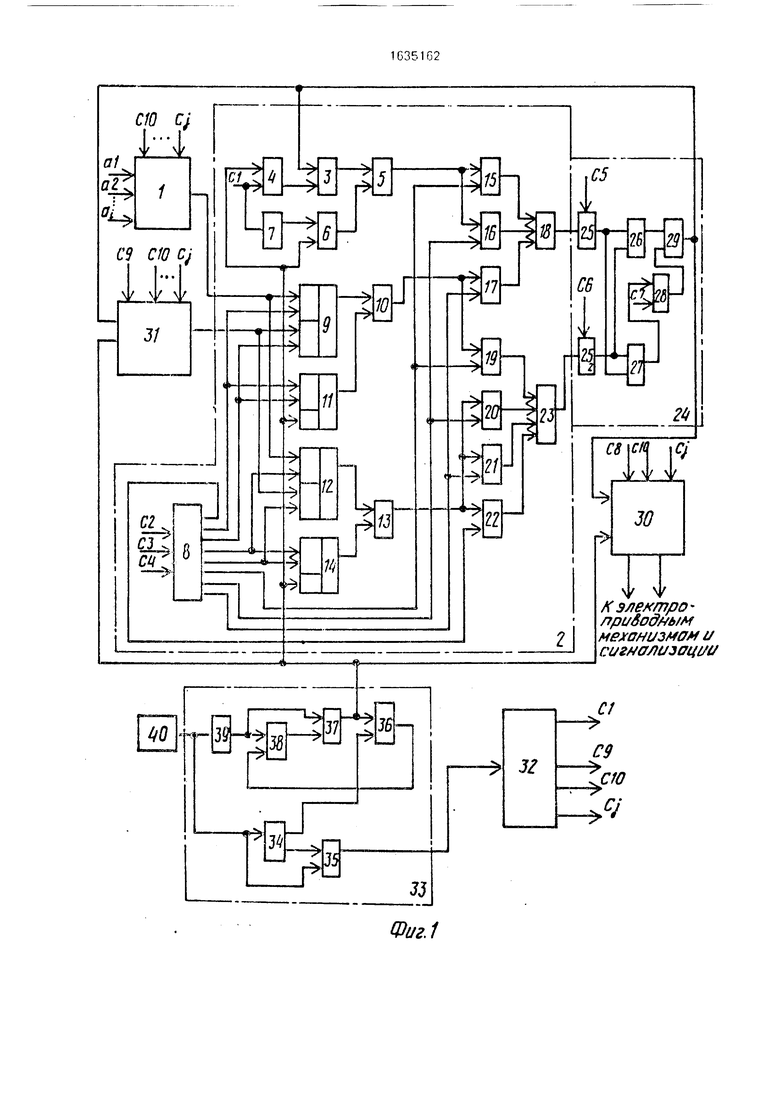

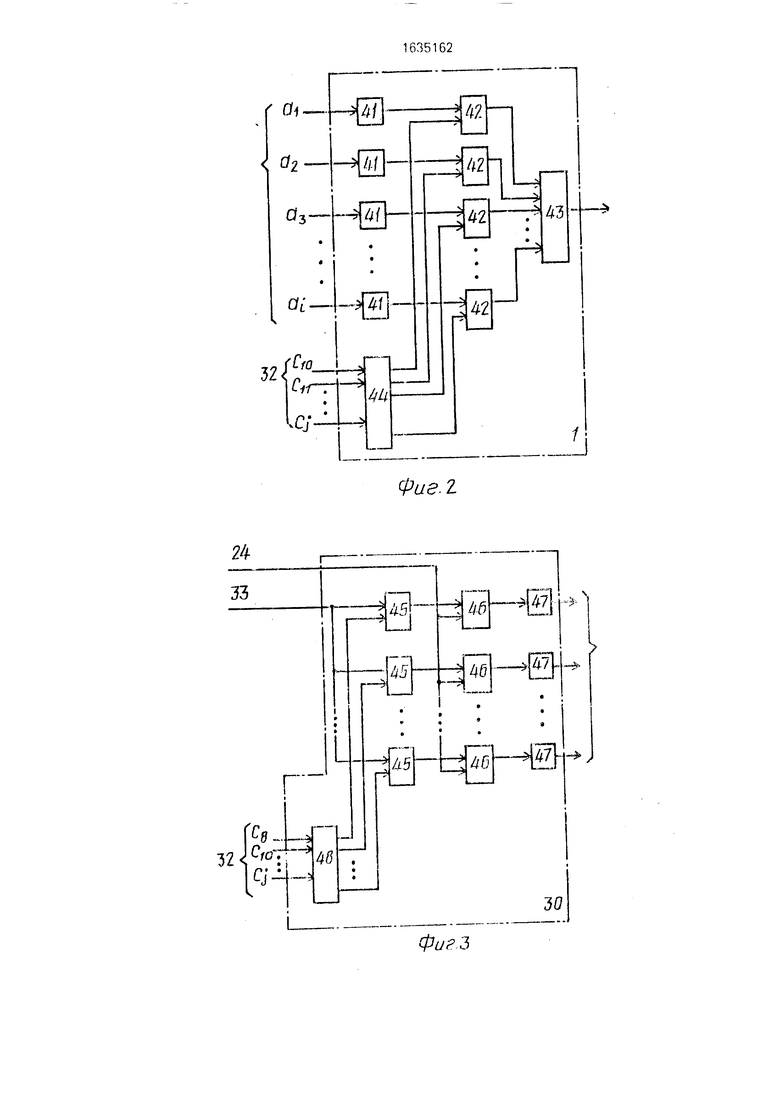

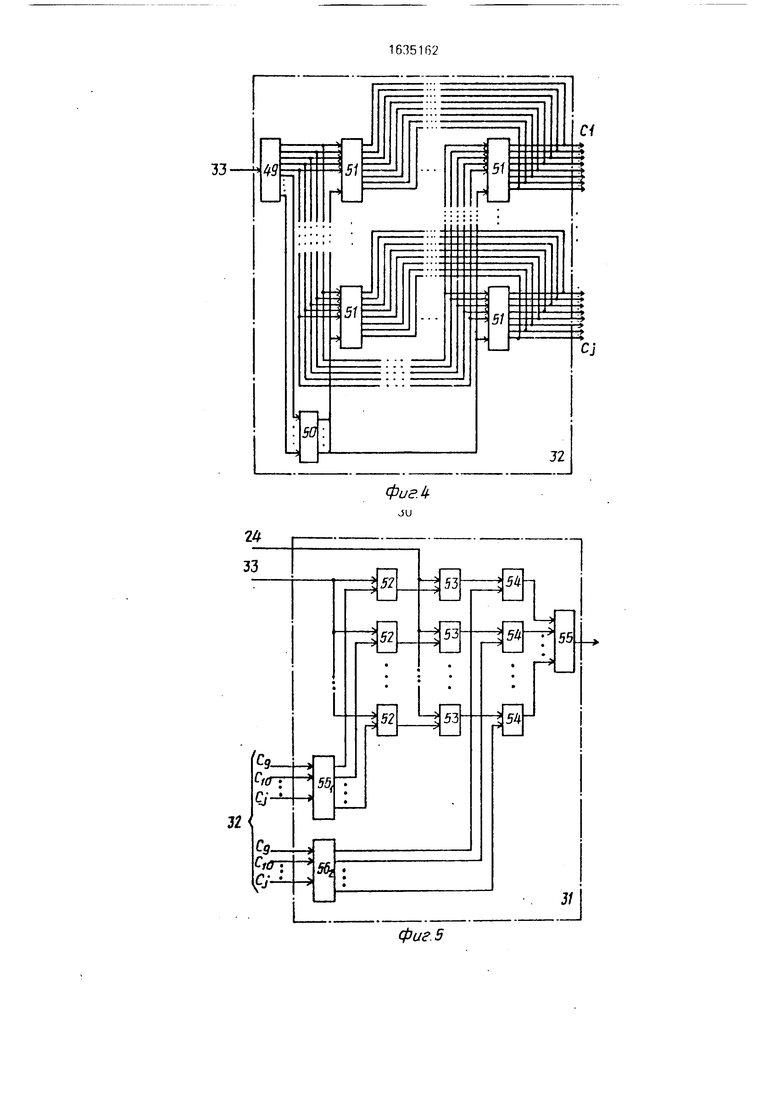

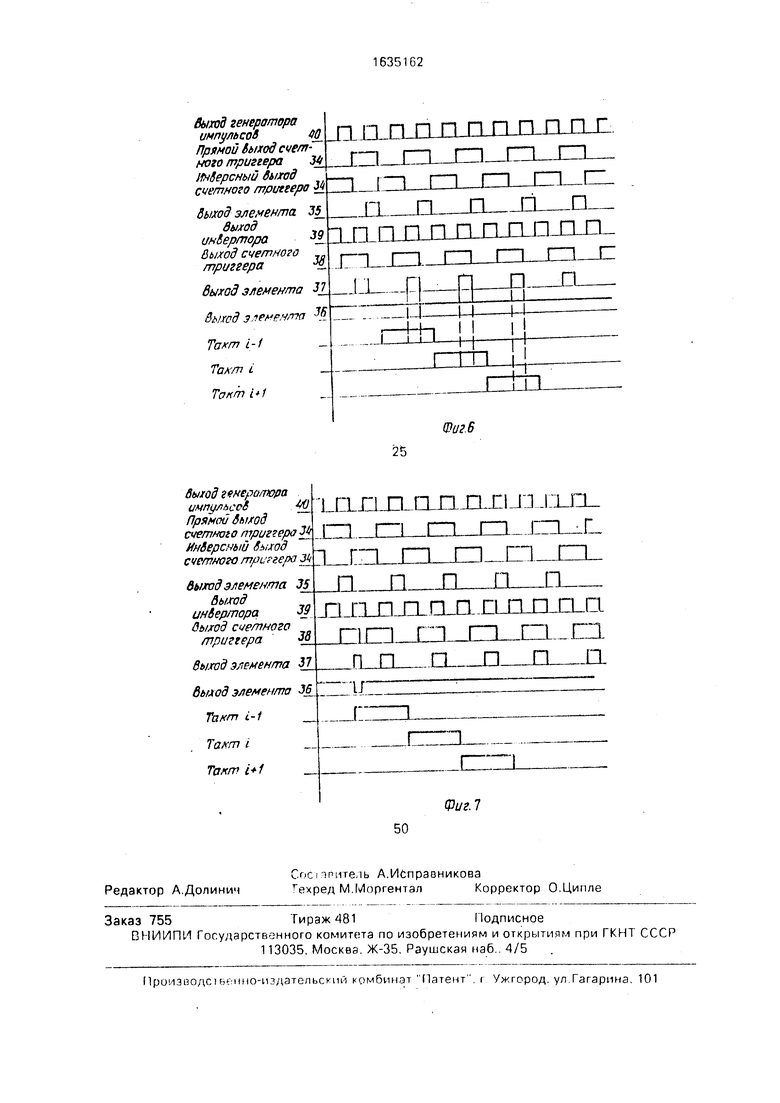

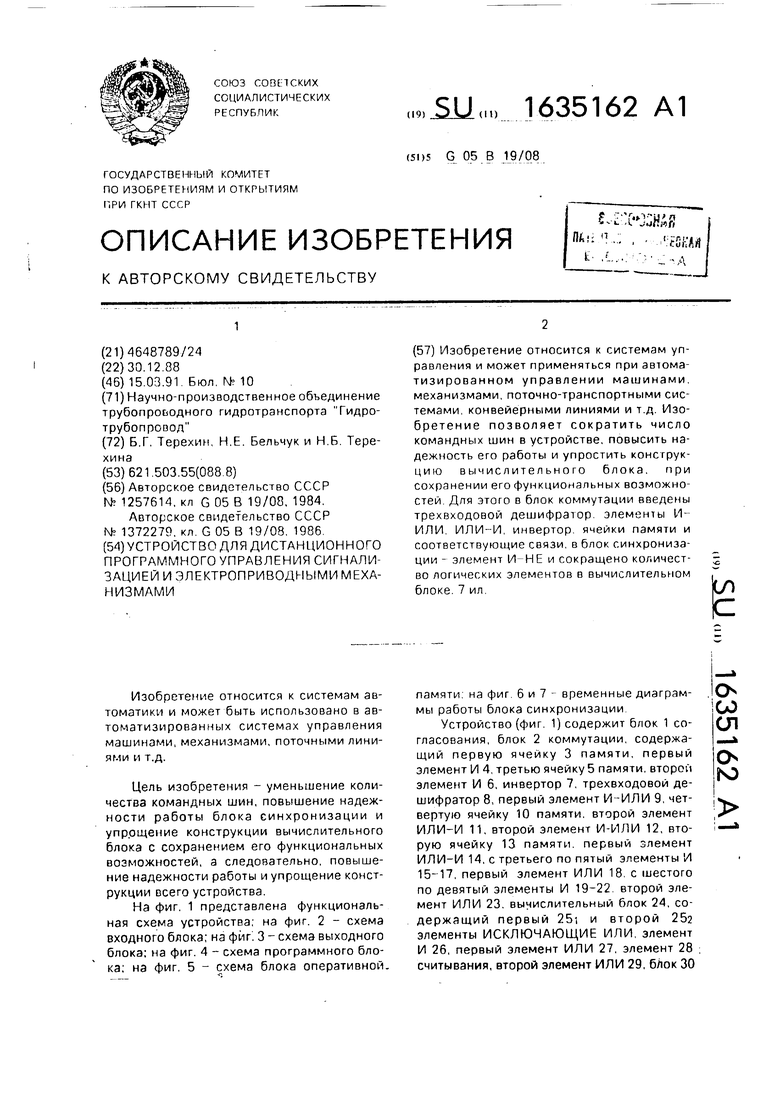

На фиг. 1 представлена функциональная схема устройства, на фиг. 2 - схема входного блока; на фиг. 3 - схема выходного блока; на фиг. 4 - схема программного блока; на фиг. 5 - схема блока оперативной.

памяти на фиг 6 и 7 - временные диаграммы работы блока синхронизации

Устройство(фиг 1)содержит блок 1 согласования, блок 2 коммутации, содержащий первую ячейку 3 памяти, первый элемент И 4 третью ячейку 5 памяти, второй элемент И 6, инвертор 7, трехвходовой дешифратор 8, первый элемент И-ИЛИ 9, четвертую ячейку 10 памяти, второй элемент ИЛИ-И 11, второй элемент И-ИЛИ 12, вторую ячейку 13 памяти первый элемент ИЛИ-И 14, с третьего по пятый элементы И 15-17, первый элемент ИЛИ 18 с шестого по девятый элементы И 19-22 второй элемент ИЛИ 23. вычислительный блок 24, содержащий первый 25т и второй 252 элементы ИСКЛЮЧАЮЩИЕ ИЛИ элемент И 26, первый элемент ИЛИ 27, элемент 28 считывания, второй элемент ИЛИ 29, блок 30

О

сх ел

ON N3

выбора механизма, блок 31 оперативной памяти npoi рэммиый блок 32, блок 33 синхронизации, содержащий первый счетный триггер 34, первый элемент И 35, второй эчеменг И-НЕ 30, второй элемент И 37, второй счетный триггер 38, первый элемент И -НЕ 39, генератор 40 импульсов

Б/юк 1 согласования известной структуры (фиг. 2) состоит из стандартных элементов 41 согласования, на входы которых поступают сигналы от первичных датчиков, а с выхода снимаю сч унифицированные сигналы, соогвсмстгующие логическим сигналам О и 1, элементов 42 считывания, в качесше которых мо,но использоватьдвух- входопыо элементы И, элемента ИЛИ 43, объединяющие по выходу ьсо элементы И, и дешифратора 4-1, управляющего элементами И по командам из программного блока

Блок 30 выбора механизма (фиг 3) со- стоит из эл ем о и го в И 45, стандартных ячеек Jb памяти (триггеров) и соответствующих усититетей 47. передающих логические сиг- малы из ячеек памяти на электроприводные механизмы или световую индикацию по ко- глндэм гз программное блока поступающих |)я дешифратор 43

Прог раммный ипок 32 (фиг. 4) состоит из стандартных элементов, счетчиков 49 импульсов, дешифратора 50, распределяющего импульсы во времени и по направлению, диодной матрицы с горизонтальными и командными шинами, диодов и инверторов (не показаны), или как в примере сгандарт- ныл ППЗ У и ПЗУ 51, выполненных, например, на микросхемах серии 155PF3 Г573РФ1 и гд, в которых записана программа работы всего устройства

Блок 31 оперативной памяти известной структуры состоит из ячеек памяти элементов записи и считывания, в качеств когори- ю могут быть испо 1ьзованы стандартные ОЗУ (оперативные запоминающие устройства) или как а примере приведенном на фиг 5 блок оперативной памяти содержит элементы Ь2 обращения к ячейкам памяти si качестве котооых могут быть использованы элементы И,ячейки 53 памяти, элементы 54 считывания, в качестве которых могут быть использованы элементы И, элемент ИЛИ 55 и первый 56 и второй дешифратор 562 через соответствующий элемент 52 за носит в соответствующую ячейку 53 памяти информацию, поступающую из вычисли тельного блока 24, а второй дешифратор562 по командам из программного блока 32 счи тырает информацию через элемент 54 счи тывги ия из соответствующей ямеиш 53

0

5

0

5

0

5

0

5

0

5

которая через элемент ИЛИ 55 поступает в блок 2 коммутации.

Входы всех элементов обозначены стрелками, направленными к этим элементам.

На фиг.1 обозначены C1....CJ - командные шины, по которым поступают соответствующие команды из программного блока.

Команды С1, С2, СЗ и С4 поступают на выходы блока коммутации, команды С5, С6, С7 поступают на входы вычислительного блока, команды С8 и С9 являются командами записи соответственно для выходного блока и блока оперативной памяти. Команды СЮCj являются адресными командами для входного блока, выходного блока и блока оперативной памяти.

Количество этих команд зависит от количества соответствующих ячеек (входных, выходных и памяти) в блоках и определяется по формуле

С toga а.(1)

где С - количество адресных команд.

а - количество ячеек в соответствующем блоке.

На одном такте вычислительный блок может вычислить одну из логических функций: AiA2. Ai A2i Ai A2i Ai + A2; Ai A2; Ai + A2 + в зависимости от значений команд С5, С6, , С7, что очевидно вытекает из приведенной на фиг. 1 схемы вычислительного блока, т.е. не смотря на упрощение конструкции, функциональные возможности вычислительного блока сохранились те же, что в аналоге и в прототипе: AI и AZ - логические переменные, поступающие на вход вычислительного блока из блока коммутации, а А есть инверсия А.

ai 32, ... а, - сигналы от дискретных датчиков, в качестве которых могут быть использованы кнопочные посты,путевые конечные выключатели, блок-контакты пускателей и т д.

Генератор 40 импульсов формирует непрерывную последовательность импульсов, которые поступают на вход блока 33 синхронизации

С прямого выхода счетного триггера 34 импульсы поступают на вход элемента И 35, который по их совпадению с импульсами генератора 40 импульсов, выдает тактовые импульсы, поступающие на вход программного блока 32. который на основе этих тактовых импульсов формирует команды управления

С выхода счетного триггера 38 импульсы поступают ,а вход элемента И 37, который по их совпадению с импульсами.

поступающими с выхода элемента И-НЕ 39 выдает синхроимпульсы, поступающие в блок 31 оперативной памяти, в блок 32 коммутации и РЫХОДНОЙ блок 30

Из временной диаграммы, приведен ной на фиг. 5, видно, что синхроимпульсы с выхода элемента И 37 блока 33 поступают в третьей четверти тактовых импульсов и это гарантирует окончание переходных процессов при формировании сигналов как в начале, так и конце тактового импульса Причем а результате возможного сбоя синхроимпульса относительно тактового импульса элемент И-НЕ 36 формирует импульс сброса, который обнулит счетный трип ер 38 и положение синхроимпульса восстановится (см диаграмму на фиг 7)

Принцип действия устройства рассмотрен на примере работы электроприводного механизма и сигнализации в зависимости от результата вычисления функции ai (ai - + 32).

Будем считать что переменные а и аз обозначают сигналы поступающие на вход устройств, от перричных датчиков а пере менная а , - обозначает переменную которая была вычислена ранее и записана в элемент памяти блока оперативной памяти, причем будем считать что переменная ai записана о первую лчейку оперативной памяти.

/Для пояснения процесса вычисления, предложенной в примере функции ai as(ai r ( йД необходимо иметь возможность спрашивать два первичных датчика подключен мых к входному блор у, опрашивать две ячейки памяти в блоке оперативной памяти и записывать результат вычисления в выходной блок

Для этого достаточно иметь одну адресную команду СЮ Будет считать, что по команде СЮ - 0 происходит обращение к нулевым ячейкам входного блока 1, блока 31 оперативной памяти и блока выбора механизма 30 по команде СЮ - 1 происходит обращение к первым ячейкам этих блоков

Для обращения к последующим ячейкам в случае необходимости добавились бы адресные команды С11,- . Cj причем для обращения ко вторым ячейкам необходимы команды СЮ-О, С11--1С12. Cj-О.для обращения к третьим ячейкам -С10--С11 1, С12Cj 0 и т д

Для записи информации в блок 31 оперативной памяти и в выходной блок 30 добавляются команды соответственно С 9 1 и С8 1 .

Команды С5, Сб. С7, поступающие в вычислительный блок 24 выполняют следую

5

5

0

5

С

(

5

щие функции по команде С5 1 происходит инверсия переменной поступившей на первый вход вычислительного блока 24, но команде С6 - 1 инвертируется переменная, поступившая на второй вход вычислительного блока, по команде С7 0 на выход вычислительного блока поступает произведение входных переменных, а по команде С7 1 на выход вычислительного блока по ступает сумма входных переменных

Условимся, что в блоке 2 коммутации на дешифраторе 8 активизируется первый выход при сочетании на входах сигналов С2 СЗ - С4 О, второй выход при сочетании сигналов на входах С2 1 СЗ С 4 - 0. третий выход при сочетании на входах сигналов С2 -- С4 О, СЭ 1 и т.д По команде С1 О происходит запись в ячейку 5 памяти

На первом такте работы устройства, на выходе программного блока 32, на командной шине С2 появится единичная команда, обеспечивающая подачу входного сигнала ai из нулевой ячейки входного блока 1, через элементы И-ИЛИ 9 блока коммутации 2 на информационный вход ячейки 10 памяти При этом сигнал лог 1 со второго выхода дешифратора 8 поступит на первый вход элемента ИЛИ И 11 и по совпадению eiо с синхроимпульсом поступившим из блока 33 синхронизации на выходе элемента ИЛИ-И 11 появится короткий импульс по которому значение переменной запишется в триггер 10

На втором такте на выходе программного блока 32 на командной шине С4 ПОЯРУИСЯ единичная команда, обеспечивающая подачу сигнала а из нулевой ячейки памяти блока 31 оперативной памяти, через эле мент И ИЛИ 12 на информационный вход ячейки 13 памяти, а через элемент ИЛИ-И 14 синхроимпульса на синхровход ячейки 13 памяти, что приведет к записи значения ат в ячейку 13 памяти.

На третьем такте на выходе программного блока 32 на командных шинах С2, СЗ, С4, С6, С7 и С1 появятся единичные команды, соответственно обеспечивающие считывание переменной ai из ячейки 10 памяти и передачу ее через элементы И17 и ИЛИ18 и на вход первого элемента 25i вычислительного блока 24, считывание переменной аз из ячейки 13 памяти и передачу ее через элементы И21 и ИЛИ 23 на вход второго элемента 25г вычислительного блока 24. где по команде переменная аз инвертируется.

Полученный по команде С7 0 на выходе элемента 29 вычислительного блока 24 результат вычисления функции ai аз а за счет, сигнала, поступающего с выхода элемента И 4, сформиросанногб по команде С1 и сим ропмпульсу запишется в ячейку 3 памяти блока 2 коммутации

На четвертом такте на выходе программного блока 32 на командных шинах СЮ, С2, СЗ появятся единичные сигналы соответственно обеспечивающие подачу переменной 32 из входного блока 1 через элемента 11-ИЛИ 12 на информационный вход ячейки 13 памяти и команду записи через элементы ИЛИ-И 14 на синхровход ячейки 13 памяти, что приведет к записи переменной в я -йку 13 пампти.

Одновременно с j-зпигью втршгер 13 результат чь M Mei ня функции а ,j из ячейки 3 14 ; :егся в я (Рйку 5 памяти, так ак н ею сишроиход поглупит импульс зт /си г формированный ии-меч том И 6 по совп лл 1ию оинхроимпу )ьса с командой С1 прошедшей через инвертор 7

На пятом такте нл выходе программного блока 32 командных шинах С2 Г } Г 4 С7 СЮ, СО появятся единичные сигналы соответственно обеспечивающие считывание переменной ai и-1 ячейки 10 памяти и гк дэчу ее чео. i эче очтt: 11 17 и ИЛИ 18 m первый 8,-од :ычИ они о Олс ... Л гнмыш1 п ремэнной из й - ;пки 13 памяти и п оедачу ее через элемент. И 21 и ИЛИ 23 на РХОД второго элемент 25п чь.числител1 но ) бло ка24.

При этом на еычгда эл м-нтов28 и 29 вычисли(ельнсго блоха 21 носится результат вычисления функции (гп - аД который иэ командам С9 - 1 и СЮ 1 запишстсч в первую ячей у памяти блока 31 оперативной памяти

Н Ш Ттог гркг-1 на вы-оде программно го блока Т2 н i комнм ны шинах С 10 и С 4 появятся единичные команды соответственно огк-снечивлощие считывание резуль- татов вычисления функции (ai - а) из первой я IUHK-I там ти блока 31 оперативной памяти и запись его в ячейку 13 памяти блоча 2 коммутации

На седьмом такте пя выходе программного блок 3 па УОМЛНДНЫХ шинах СЗ С4 С8 и СЮ появятся едииичп 1е команды, со ответственно бесшгчивающие подачу результата вычисления функции из ячейки 5 памяти через лсментп И 1о и И ПИ 13 ria псрвьч 1 в :од вччис/нпельно о бпокэ 24 а результата г ччгления Ф,нк1,|-. (oi + 32) 113 ячейки 13 памяти через элементы И 20 и ИЛИ 23 на второй вход выч и. тигельного блока 24, п- 1 выходе которого по команде

С7 - 0 появляется результат вычисления ii

Фунгиии ai аз (ai + ял) по команде С8 1 С10 1 резу/ ьтлг mi 4 слечия функции за- ,

0

5

0

писывается в первую ячейку памяти блока 30 и далее через усилитель 47 поступит на соответствующие электропроводной механизм и сигнальный элемент

Ячейки 3 и 5 памяти функционально служат для кратковременного хранения бита информации, поступающего из вычислительного блока 24 Причем если нет команQ ды С1 на запись в ячейку 3 тоавтоматически происходит перезапись информации из ячейки 3 в ячейку 5 и ячейка 3 вновь готова к приему новой информации Это сокращает число командных шин, так как по одной ши5 не С1 происходит запись и в ячейку 3 и в ячейку 5

Ячейки 10 и 13 памяти служат для промежуточного хранения битов информации поступающих из блока 1 согласования или блока 31 оперативной памяти перед тем как эти биты обрабатываются в вычислительном блоке 24 что позволяет использовать одни и теже командные шины идущие из программного блока 32 для управления блоками 1 30 и 31

Число командных шин зависит только от конструкции блока 2 коммутации

Конструкция блока коммутации в аналоге и прототипе предусматривает необходимость иметь разные командные шины, идущие из программною блока для управления блоками согласования и выбора меха- низма, а также блоком оперативной памяти Например, если имеются 127 входов. 127 5 выходов и 127 ячеек памяти в блоке оперативной памяти то для управления этими блоками требуется - 28 физических командных шин идущих из программного блока к этим блокам В устройстве 0 для этого требуется 9 командных шин, так как 7 шин являются общими для перечисленных всех блоков (на схеме фиг 1 это командные шинь С10-С16, так как для вышеприведенного количества вхо- 5 дов-выходов и памяти в блоке оперативной памяти j -- 16), команда по восьмой шине (С9) определяет режим записи или считывания в блоке 31 а команда (С8) по девятой шине определяет надо или не надо Q записывать результат вычисления в блок 30 Такое сокращение командных шин, поступающих из программного блока, возможно в конструкции устройства, где в блок коммутации введена дополнительная ячейка 10 5 памяти с соответствующей схемой управления режимами записи информации, как в ячейку 10, так и в другую ячейку 13 памяти и считывание ранее записанной туда информации Суть п том что ячейка 10 памяти в

паре с ячейкой 13 по командам С2-СА (знак означает что С 1 или С - 0 позволяет организовать запись в промежуточное хранение информации перед обработкой ее в вычислительном блоке 24, которая поочередно поступает из входного блока или блока оперативной памяти).

Поэтому из блока 1 и блока оперативной памяти 31 по одним и тем же командным шинам СЮ-Cj можно по очереди (на разных тактах) подавать команды на операцию считывания информации по определенному командами СЮ-Cj адресу и хранить эту информацию в двух ячейках 10 и 13 памяти. При отсутствии дополнительно введенной ячейки 10 памяти это сделать невозможно.

Для блока 31 оперативной памяти команда по шине С9 определяет режим считывания или записи, а адреса находятся командами по общим шинам СЮ-Cj.

Далее на следующем такте, когда записали в ячейки 10 и 13 нужные переменные по командам С2-С7, эти переменные считываются из ячеек 10 и 13 и обрабатываются в блоке 24 и по сигналам, поступающим по общим шинам СЮ-Cj определяется адрес ячейки памяти в блоке 30 или 31 и если есть команда на запись по шине С8 или С9 результат вычисления из блока 24 записывается в блок 31 или 30. При этом команды по шинам СЮ-Cj могут вызывать любые переменные из блоков 1 или Д1. без всякой реакции со стороны устройства гак как по командам С2 С4 подаются сигналы на считывание, а не на запись. В этом и состоит связь между введенными элементами и связями в блоке коммутации и возможностью сократить число командных шин. выходящих из программного блока, т.е использовать одни и те же шины (команды СЮ ... Cj) для обслуживания нескольких блоков, добавив для записи информации в блок 30 команду С8. а для записи информации в блок 31 оперативной памяти команду С9

Технико-экономический эффект устройства по сравнению с аналогом и прототипом заключается в уменьшении числа линий связи и разъемов в устройстве за счет сокращения- командных линий при управлении устройством за счет более надежной работы блока синхронизации, сокращения числа логических элементов в вычислительном блоке.

Формула изобретения Устройство для дистанционного программного управления сигнализацией и электроприводными механизмами, содер

5

0

5

С

5

г

5

0

5

жащее блоки согласования и выбора механизма, программный блок, генератор импульсов блок оперативной памяти и блок коммутации, состоящий из первой и второй ячеек памяти, первого и второго элементов ИЛИ, первого элемента ИЛИ-И, и с первого по девятый элементы И, причем выход первого элемента И соединен со входом разрешения записи первой ячейки памяти, вход разрешения записи второй ячейки памяти подключен к выходу первого элемента ИЛИ-И, выходы элементов И с третьего по пятый соединены с входами первого элемента ИЛИ, выходы элементов И с шестого по восьмой подключены соответственно к первому, второму и третьему входам второго элемента ИЛИ, вычислительный блок, содержащий элемент считывания, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. элемент И и первый элемент ИЛИ. выход которого подключен к входу разрешения элемента считывания, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с входами элемента И и первого элемента ИЛИ. входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходам первого и второго элементов ИЛИ б пока коммутации, а выход второго элемента ИЛИ вычислительного блока соединен с информационными входами блока оперативной памяти, блока выбора механизма и первой ячейки памяти блока коммутации, блок синхронизации,содержащий первый элемент И НЕ первый и второй счетные триггеры и первый и второй элементы И причем вход и прямой выход первого счетного триггера соединены с входами первою элемента И. счетный вход и прямой выход второго счетного триггера подключены к входам второго элемента И. выход которого соединен с входом разрешения блока выбора механизма, входом разрешения считывания блока оперативной памя ги и с первым входом первого элемента И блока коммутации счетный вход второго счетного триггера блока синхронизации через первый элемент И-НЕ а счетный вход первого счетного триггера непосредстве1 но соединены с выходом генератора импульсов выход первого элемента И блока синхро низации подключен к входу программного блока, соответствующие командные шины которого соединены с командными входами блока согласования, блока оперативной памяти, блока коммутации,вычислительного блока и блока выбора механизма, выходы которого -являются выходами устройства, а входы блока согласования являются входами устройства, отличающее- с я тем, что, с целью упрощения устройства путем сокращения числа командных шин, в

блок коммутации введены трехвходовой дешифратор, третья и четвертая ячейки памяти, инвертор, второй элемент ИЛИ-И и два элемента И-ИЛИ. причем первый выход трехвлодорого дешифраюра соединен с первым входом девятого элемента И, второй пыход грехвходового дешифратора подключен к первым входам третьего и шестого элементов И, третий выход трехвходового дешифратора соединен с первыми входами четвертого и седьмого элементов И, четвертый выход трехоходового дешифратора подключен к первым входам пятого и восьмого элементов И, пятый выход трехвходового дешифратора соединен с первыми входами первого элемента И-ИЛИ и второго элемента ИЛИ-И, вторые ьходы которых подключены к шестому выходу трехвходивого дешифратора, седьмой выход ко юрою соединен с первыми входами второго элемента И-ИЛИ и первого элемента ИЛИ-И. вторые пходы которых подключены к восьмому выходу трехоходового дешифратора, входы которого соединены с соответствующими командными шинами программного бпокэ пыход блока согласования подключен к третьим входам первого и второго злемеп тов И-ИЛИ блока коммутации, чгшертые входы которых соединены с выходом блока оперативной памяти, третьи входы первого и второго элементов ИЛИ-И блока коммутации подключены к первым входам первого и второго элементов И, второй вход первого элемента И соединен с соответствующей

командной шиной программного блока и через инвертор блока коммутации с вторым входом второго элемента И. выход когорсм о подключен к входу разрешения записи третьей ячейки памяти, информационный вход которой соединен с выходом первой ячейки памяти, информационные входы четвертой и второй ячеек памяти соединены с выходами первого и второго элементов И- ИЛИ, вход разрешения записи четвертой ячейки памяти подключен к выходу второго элемента ИЛИ-И, выходы второй, третьей и четвертой ячеек памяти соединены соответственно с вторыми входами седьмого, восьмого и девятого элементов И, третьего и четвертого элементов И. пятого и шестого элементов И. выход девятого элемента И подключен к четвертому входу второго элеQ мента И блока коммутации, в вычислительный блок введен второй элемент ИЛИ, входы которого подключены к выходам эче- мента И и элемента считывания, а выход является выходом вычислительного блока.

/ информационный вход элемента считывания соединен с соответствующей командной шиной программного блока а в бгок синхронизации дополнительно введен второй элемент И-НЕ, ирпчгм первый вход этого элемента связан с выходом второго элемента И, второй вход подключен к инверсному выходу первого счетного триггера, а выход элемента И-НЕ подключен к входу Сброс о нуль второго счетного тритгера.

0

I-.

i

.

-

Jtf

v v

Кэлехтро лрибоднь/м механизмами сигнолиэощ/U

Изобретение относится к системам управления и может применяться при автоматизированном управлении машинами механизмами, поточно-транспортными системами конвейерными линиями и т д Изобретение позволяет сократить число командных шин в устройстве, повысить надежность его работы и упростить конструкцию вычислительного блока, при сохранении его функциональных возможностей Для этого в блок коммутации введены трехвходовой дешифратор элементы И ИЛИ ИЛИ-И инвертор ячейки памяти и соответствующие связи в блок синхронизации - элемент И-НЕ и сокращено количество логических элементов в вычислительном блоке 7 ил fe

40

с

56

37

Г

J/

С

С9

СЮ

с;

JJ

7 глф

2919Ш

«- 4

LD Г

to

D °

IT)

s

0JJ

ПППППППППГ

П-П Г.

пп п

Г1П.

пппппппппп

1-II-L ГП |-| Г

U3.n nLCLnj3j:i j j

nJDJnjn-OJlJmiJlJCLQ JIlIIl XZLJIi ZL EZL - ri DПП П 11

СП-П Г.

пп п

Г1П.

ппппппппппп

1-II-L ГП |-| Г

| Устройство для дистанционного программного управления электроприводными механизмами | 1984 |

|

SU1257614A1 |

| Устройство для дистанционного программного управления электроприводными механизмами | 1986 |

|

SU1372279A1 |

Авторы

Даты

1991-03-15—Публикация

1988-12-30—Подача