Изобретение относится к электронным схемам общего назначения, в частности к схемам кодирования, декодирования и преобразования данных при их передаче между удаленными друг от друга абонентами.

Известно устройство [1], содержащее подключенные к противоположным сторонам линии связи блоки передачи и приема данных, входы блоков передачи и выходы блоков приема данных являются входами и выходами устройства, линия связи содержит группу витых пар проводов по числу входов устройства. По одной из витых пар проводов линии передается сигнал синхронизации, по остальным витым парам - биты данных.

Недостатком устройства [1] является низкая эффективность использования линии связи. Для передачи n-разрядных слов линия должна содержать n+1 витую пару проводов, одна из которых используется для трансляции синхросигнала, а остальные - для пересылки битов данных.

Известно устройство [2] для кодирования - декодирования данных, содержащее подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, выход генератора синхросигналов соединен с входом шифратора и является первым выходом синхронизации первого канала устройства, группа входов блока передачи данных является группой входов данных первого канала устройства, группа выходов шифратора соединена с входами группы выходных усилителей, выходы которых соединены с витыми парами проводов линии связи, блок приема данных содержит группу входных усилителей, дешифратор, регистр, первый элемент задержки и инвертор, входы группы входных усилителей соединены с витыми парами проводов линии связи, а их выходы - с входами дешифратора, выходы которого соединены с входами данных регистра и, через первый элемент задержки, с входом инвертора, выход которого соединен с входом синхронизации регистра и является вторым выходом синхронизации первого канала устройства, группа выходов регистра является группой выходов данных первого канала устройства.

Устройство [2] преобразует параллельный двоичный код данных и синхросигнал в группу троичных сигналов, которая передается по линии связи, состоящей из группы витых пар проводов. На приемной стороне устройства группа троичных сигналов преобразуется в исходный двоичный код, сопровождаемый восстановленным синхросигналом.

Устройство [2] имеет недостаточно высокую скорость передачи данных. Это связано с тем, что при шифрации данных для их передачи по линии связи использованы не все потенциально возможные кодовые комбинации трехуровневых сигналов. Это, в свою очередь, приводит к тому, что дешифратор кодовых комбинаций оперирует не полным диапазоном кодов и поэтому не реализует потенциальные возможности восстановления кодированных данных. В результате скорость передаваемого потока данных снижена.

Цель изобретения - повышение скорости передачи данных.

Цель достигается тем, что в устройстве для кодирования - декодирования данных, содержащем подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, выход генератора синхросигналов соединен с входом шифратора и является первым выходом синхронизации первого канала устройства, группа входов блока передачи данных является группой входов данных первого канала устройства, группа выходов шифратора соединена с входами группы выходных усилителей, выходы которых соединены с витыми парами проводов линии связи, блок приема данных содержит группу входных усилителей, дешифратор, регистр, первый элемент задержки и инвертор, входы группы входных усилителей соединены с витыми парами проводов линии связи, а их выходы - с входами дешифратора, выходы которого соединены с входами данных регистра и, через первый элемент задержки, с входом инвертора, выход которого соединен с входом синхронизации регистра и является вторым выходом синхронизации первого канала устройства, группа выходов регистра является группой выходов данных первого канала устройства, блок передачи данных дополнительно содержит регистр, дешифратор, инвертор, триггер и элемент И, группа входов данных первого канала устройства соединена с входами дешифратора и с входами данных регистра, выходы которого соединены с входами шифратора, а вход синхронизации - с выходом генератора синхросигналов, с первым входом элемента И и с входом инвертора, выход которого соединен с входом синхронизации триггера, выход которого соединен с вторым входом элемента И, выход которого является первым выходом синхронизации второго канала устройства, вход данных второго канала устройства соединен с входом шифратора, выход дешифратора соединен с входом данных триггера, блок приема данных дополнительно содержит второй элемент задержки и элемент И, вход второго элемента задержки соединен с выходом инвертора, а его выход - с первым входом элемента И, второй вход которого соединен с выходом регистра, выход элемента И является вторым выходом синхронизации второго канала данных устройства, выход данных второго канала устройства соединен с выходом регистра.

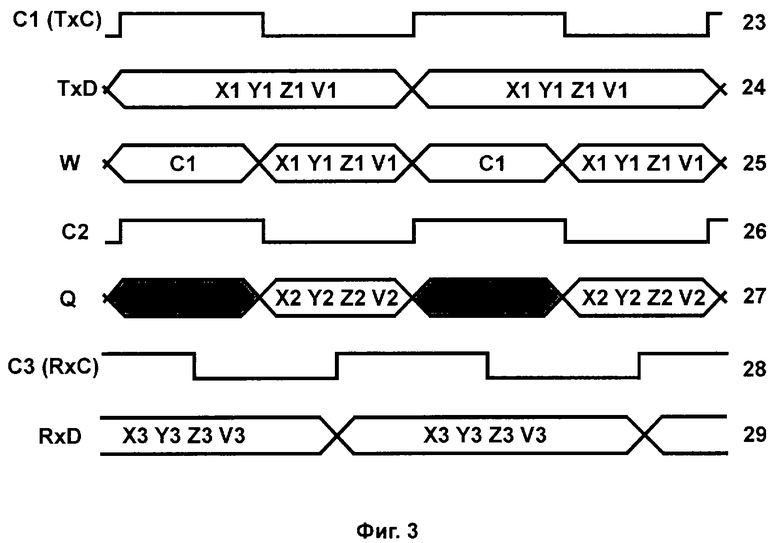

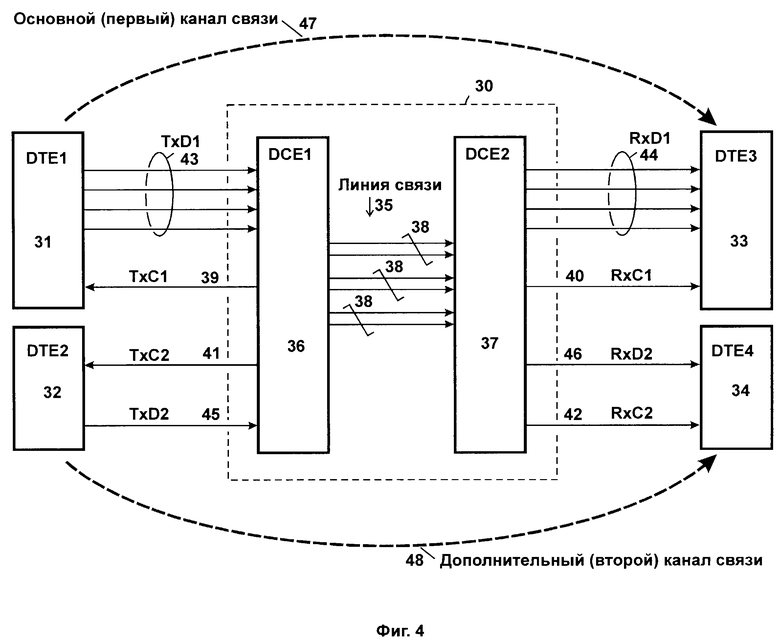

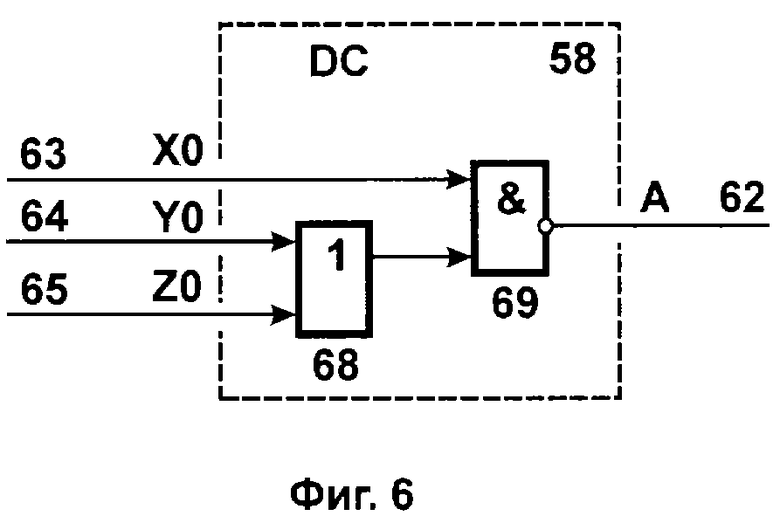

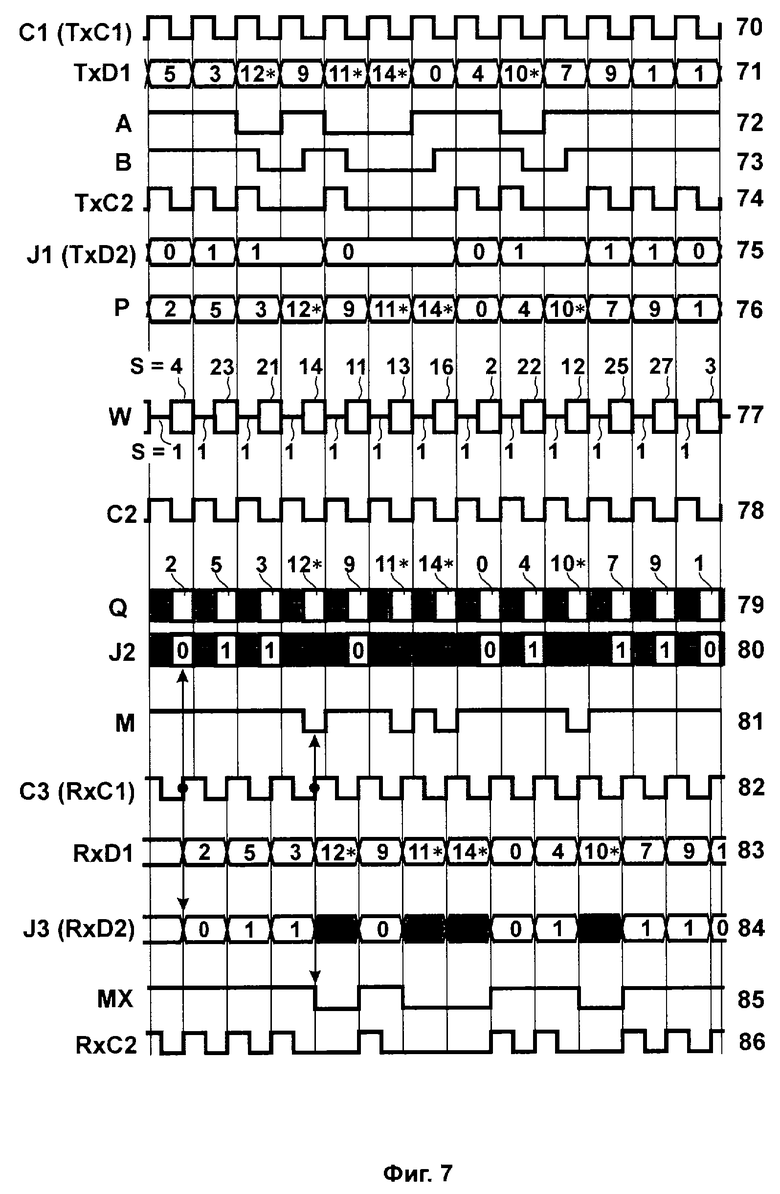

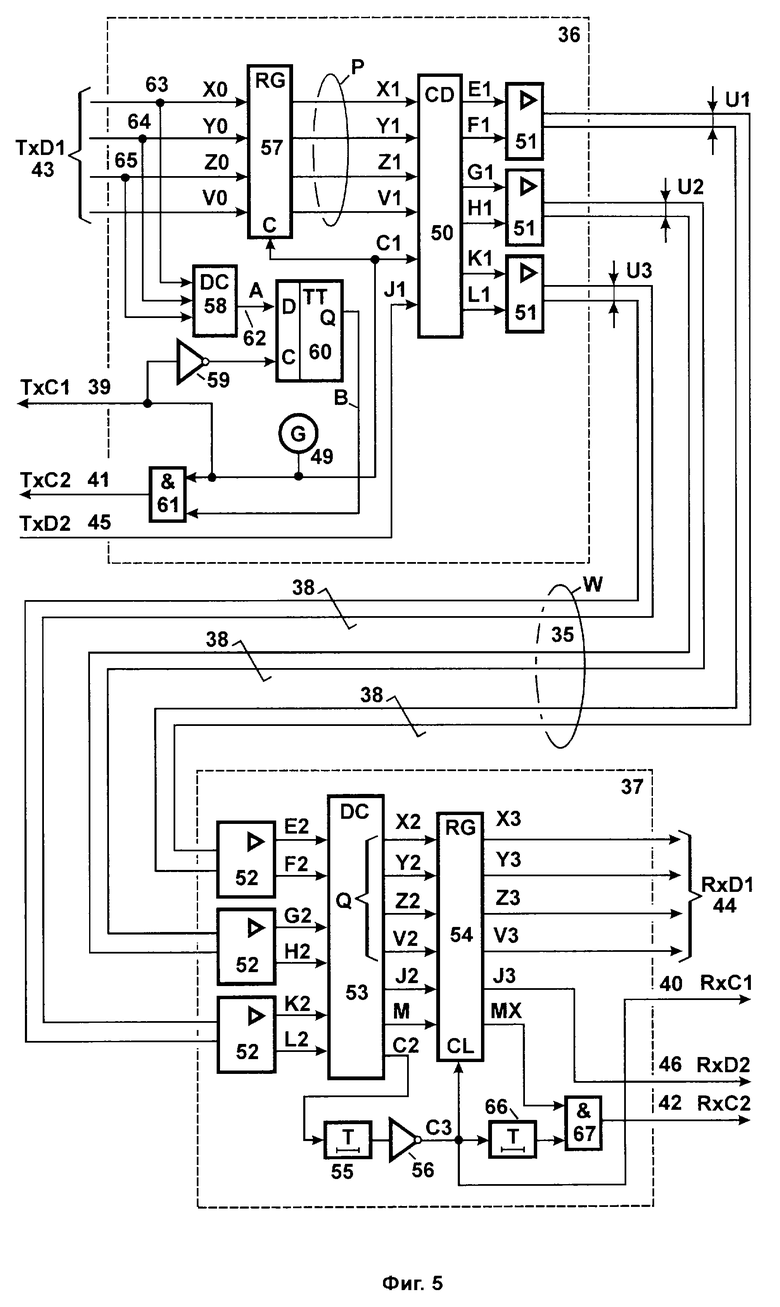

На фиг. 1 и 2 представлены схемы известных устройств [1] и [2]; на фиг. 3 - временные диаграммы передачи данных устройством [2]; на фиг. 4 - пример схемы включения предлагаемого устройства в телекоммуникационную систему, на фиг. 5 - пример функциональной схемы предлагаемого устройства, на фиг. 6 - пример схемы дешифратора блока передачи данных, на фиг. 7 - временные диаграммы передачи данных предлагаемым устройством.

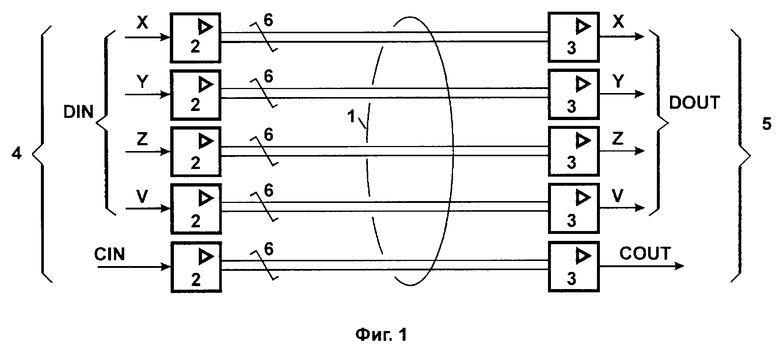

Устройство [1] (фиг. 1) содержит подключенные к противоположным сторонам линии связи 1 блоки 2 передачи и 3 приема данных, входы 4 блоков передачи и выходы 5 блоков приема данных являются входами и выходами устройства, линия связи 1 содержит группу витых пар 6 проводов по числу входов устройства.

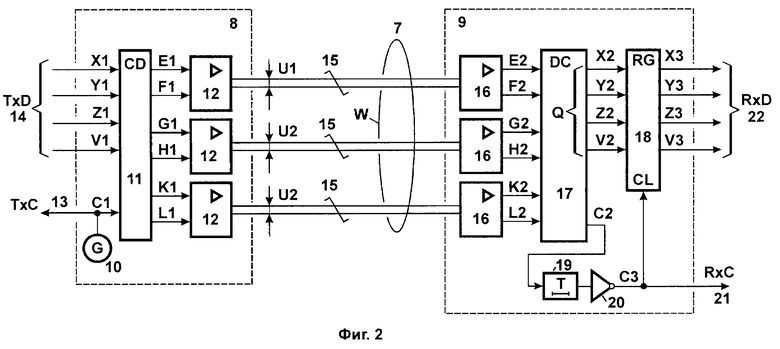

Устройство [2] (фиг. 2) содержит подключенные к противоположным сторонам линии связи 7 блок 8 передачи данных и блок 9 приема данных, блок передачи данных содержит генератор 10 синхросигналов, шифратор 11, группу выходных усилителей 12, выход генератора 10 синхросигналов соединен с входом шифратора 11 и является первым выходом 13 синхронизации устройства, группа входов 14 блока 8 является группой входов данных устройства, группа выходов шифратора 11 соединена с входами группы выходных усилителей 12, выходы которых соединены с витыми парами 15 проводов линии связи 7, блок 9 приема данных содержит группу входных усилителей 16, дешифратор 17, регистр 18, элемент 19 задержки и инвертор 20, входы группы входных усилителей 16 соединены с витыми парами 15 проводов линии связи, а их выходы - с входами дешифратора 17, выходы которого соединены с входами данных регистра 18. Один из выходов дешифратора 17 через элемент задержки 19 соединен с входом инвертора 20, выход которого соединен с входом синхронизации регистра 18 и является вторым выходом 21 синхронизации устройства, группа 22 выходов регистра 18 является группой выходов данных устройства.

Временные диаграммы 23 и 24 (фиг. 3) соответствуют сигналам на выходе 13 и входах 14 блока 8 (см. фиг. 2); диаграмма 25 отображает сигналы в линии 7; диаграммы 26 и 27 соответствуют сигналам на выходах дешифратора 17, диаграммы 28 и 29 - сигналам на выходах 21 и 22 блока 9.

Телекоммуникационная система (фиг. 4) содержит предлагаемое устройство 30 для кодирования - декодирования данных и подключенные к нему первое-четвертое 31-34 оконечные устройства DTE1-DTE4. Устройство 30 содержит подключенные к противоположным сторонам линии связи 35 блок 36 передачи данных (DCE1) и блок 37 приема данных (DCE2). Линия связи 35 содержит витые пары 38 проводов. Выходы 39 и 40 блоков 36 и 37 являются первым и вторым выходами синхронизации первого канала устройства 30. Выходы 41 и 42 блоков 36 и 37 являются первым и вторым выходами синхронизации второго канала устройства 30. Группа входов 43 блока 36 передачи данных является группой входов данных первого канала устройства 30. Группа выходов 44 блока 37 приема данных является группой выходов данных первого канала устройства 30. Вход 45 блока 36 является входом данных второго канала устройства 30. Выход 46 блока 37 является выходом данных второго канала устройства 30. Указатели 47 и 48 показывают направления передачи данных по первому и второму каналам связи.

Блок 36 передачи данных (фиг.5) содержит генератор 49 синхросигналов, шифратор 50, группу выходных усилителей 51, выход генератора 49 синхросигналов соединен с входом шифратора 50 и является первым выходом 39 синхронизации первого канала устройства 30, группа выходов шифратора 50 соединена с входами группы выходных усилителей 51, выходы которых соединены с витыми парами 38 проводов линии связи 35. Блок 37 приема данных содержит группу входных усилителей 52, дешифратор 53, регистр 54, первый элемент 55 задержки и инвертор 56, входы группы входных усилителей 52 соединены с витыми парами 38 проводов линии связи 35, а их выходы - с входами дешифратора 53, выходы которого соединены с входами данных регистра 54 и, через первый элемент 55 задержки, с входом инвертора 56, выход которого соединен с входом синхронизации регистра 54 и является вторым выходом 40 синхронизации первого канала устройства 30, группа выходов регистра 54 является группой 44 выходов данных первого канала устройства 30.

Блок 36 передачи данных дополнительно содержит регистр 57, дешифратор 58, инвертор 59, триггер 60 и элемент И 61, группа входов 43 блока 36 соединена с входами данных регистра 57, выходы которого соединены с входами шифратора 50, а вход синхронизации - с выходом генератора 49 синхросигналов, с первым входом элемента И 61 и с входом инвертора 59, выход которого соединен с входом синхронизации триггера 60, выход которого соединен с вторым входом элемента И 61, выход которого является первым выходом 41 синхронизации второго канала устройства, вход 45 данных второго канала устройства соединен с входом шифратора 50, выход 62 дешифратора 58 соединен с входом данных триггера 60, входы дешифратора 58 соединены с входами 63, 64 и 65 группы 43 входов блока 36. Блок 37 приема данных дополнительно содержит второй элемент 66 задержки и элемент И 67, вход второго элемента 66 задержки соединен с выходом инвертора 56, а его выход - с первым входом элемента И 67, второй вход которого соединен с выходом регистра 54, выход элемента И 67 является вторым выходом 42 синхронизации второго канала данных устройства 30, выход 46 данных второго канала устройства соединен с выходом регистра 54.

В примере, приведенном на фиг. 6, дешифратор 58 блока 36 содержит элементы ИЛИ 68 и И-НЕ 69. Входы 64 и 65 дешифратора 58 соединены с входами элемента ИЛИ 68, вход 63 соединен с первым входом элемента И-НЕ 69, второй вход которого соединен с выходом элемента ИЛИ 68, выход элемента И-НЕ 69 является выходом 62 дешифратора 58.

Временные диаграммы 70 и 71 (фиг. 7) отображают сигналы на выходе 39 и входах 43 блока 36; диаграммы 72 и 73 - сигналы на входе 62 и выходе триггера 60; диаграммы 74 и 75 - сигналы на выходе 41 и входе 45 блока 36; диаграммы 76 и 77 - сигналы на выходах регистра 57 и в линии связи 35; диаграммы 78, 79, 80 и 81 - сигналы на выходах дешифратора 53 блока 37; диаграммы 82 и 83 - сигналы на выходе инвертора 56 и на выходах 44 блока 37; диаграммы 84 и 85 - сигналы на выходе 46 блока 37 и на входе элемента И 67, соединенном с регистром 54; диаграмма 86 - сигнал на выходе 42 блока 37.

В схеме, приведенной на фиг. 1, четырехразрядный параллельный код данных DIN (X Y Z V) и сопровождающий его синхросигнал CIN передаются по витым парам 6 проводов линии связи 1 к удаленному абоненту. Напряжение между проводами витой пары 6 может быть отрицательным или положительным в зависимости от значения передаваемого бита (лог. "0" или "1"). Выходной код данных DOUT (X Y Z V) и принятый синхросигнал COUT совпадают с входными с точностью до задержек передачи.

Пересылка четырехразрядного параллельного кода и синхросигнала может быть выполнена по меньшему числу витых пар проводов с использованием схемы [2], показанной на фиг. 2.

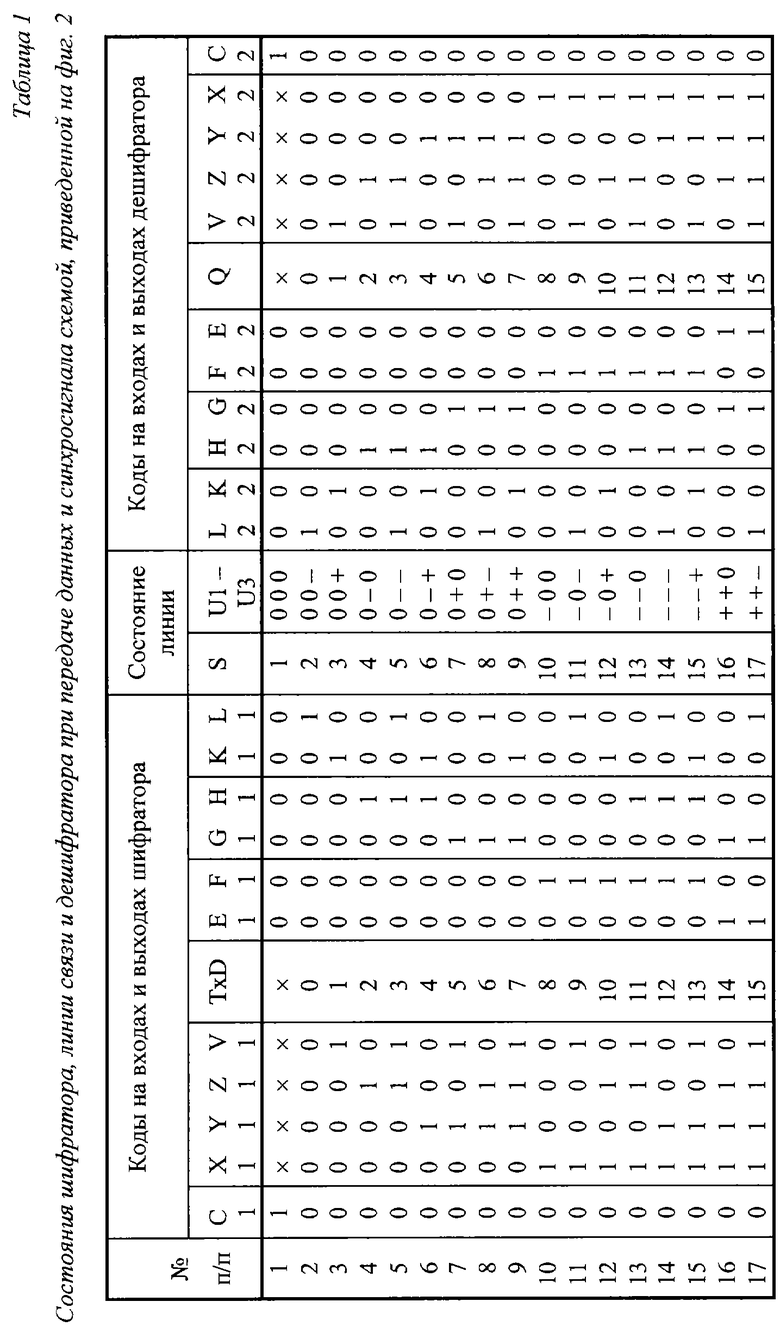

В этой схеме применено трехуровневое кодирование сигналов в линии связи 7. Напряжение U1 (U2, U3) между проводами витой пары 15 может быть отрицательным, нулевым или положительным (сокращенно: -, 0, +). Это напряжение формируется усилителем 12 в зависимости от сочетания битов E1 F1 (G1 H1, K1 L1) на его входах следующим образом. При Е1=F1=0 (G1=H1=0, K1=L1=0) напряжение U1 (U2, U3) нулевое, при Е1=0, F1=1 (G1=0, H1=1; K1=0, L1=1) - отрицательное, при E1=1, F1=0 (G1=1, H1=0; K1=1, L1=0) - положительное. Код E1 F1 G1 H1 K1 L1 формируется шифратором 11 из входного кода X1 Y1 Z1 V1 С1 (данные, синхросигнал), например, как показано в левой части табл. 1.

Входные усилители 16 и дешифратор 17 осуществляют обратное преобразование сигналов, представленных напряжениями U1, U2 и U3 в витых парах проводов линии связи. В этом можно убедиться сопоставлением левой и правой частей табл. 1 - они симметричны. В центральной части таблицы показаны 17 (из 33=27 возможных) комбинаций S сигналов в линии связи. Первая (S=1) комбинация (0 0 0) произвольно выбрана для отображения единичного состояния синхросигнала С1. Символы "х" в левой части таблицы означают, что при С1=1 входные сигналы TхD не воспринимаются шифратором. Эти же символы в правой части таблицы показывают, что при выдаче восстановленного синхросигнала С2 выходные данные Х2 Y2 Z2 V2 не определены и не могут использоваться для выдачи абоненту. Остальные 16 комбинаций сигналов в линии связи произвольно распределены для отображения 16 состояний четырехразрядного кода X1 Y1 Z1 VI при условии, что С1= 0. Шифратор и дешифратор могут быть выполнены на основе ПЗУ, программируемой логики или построены из обычных логических элементов.

Из временных диаграмм, показанных на фиг. 3, следует, что сигналы W, передаваемые по линии связи 7, поочередно отображают синхросигнал С1 и данные (группу битов X1, Y1, Z1, V1). Как отмечалось, группа выходных сигналов дешифратора 17 не определена при наличии синхросигнала. Этот факт отмечен затененными областями на временной диаграмме 27 группы Q сигналов Х2, Y2, Z2, V2. Для устранения неопределенности этих сигналов применен параллельный регистр 18. Данные принимаются в него по положительному фронту сигнала С3, который формируется из сигнала С2 после его задержки на четверть периода синхросигнала и последующего инвертирования. В результате сигналы RхD и RхC с некоторой задержкой повторяют сигналы TхD и ТхС.

Данный способ уменьшения числа витых пар проводов канала связи применим к схемам с различной разрядностью. При трехуровневом кодировании число состояний линии, содержащей N витых пар проводов, равно 3N. Одно из этих состояний следует выделить для кодирования единичного значения синхросигнала. С помощью оставшихся 3N - 1 состояний можно отобразить М-разрядный двоичный код TxD, где М = [log2(3N - 1)], прямые скобки здесь обозначают целую часть заключенного в них числа. Так, при N=2, 3, 4,..., 10 разрядность М передаваемого кода составляет 3, 4, 6, 7, 9, 11, 12, 14, 15.

Принцип действия предлагаемого устройства (см. фиг. 4 - фиг. 7) близок рассмотренному, но по линии связи 35 передается большее число кодовых комбинаций (в рассмотренном далее примере использованы все возможные комбинации). Совокупность этих комбинаций несет более высокую информационную нагрузку. Это позволяет при том же числе проводов линии связи, что и в устройстве-прототипе, построить дополнительный (второй) канал связи, который работает параллельно с основным (первым) каналом, не ухудшая его характеристик. Скорость передачи данных предлагаемым устройством складывается из скоростей передачи данных по обоим каналам и, следовательно, она более высокая по сравнению со скоростью передачи данных одноканальным прототипом.

Предлагаемое устройство 30 (фиг. 4) подключено к четырем оконечным устройствам DTE1 (31) - DTE4 (34), например к четырем компьютерам. В процессе работы системы данные передаются из устройства 31 в устройство 33 по основному (первому) каналу. Одновременно с этим по дополнительному (второму) каналу данные передаются из устройства 32 в устройство 34. (Для передачи данных в обратном направлении необходимо второе устройство 30, включенное встречно.)

Сигнал ТхС1 обеспечивает синхронную передачу данных TхD1 первого канала из устройства 31 в блок 36. Сигнал ТхС2 обеспечивает синхронную передачу данных TxD2 второго канала из устройства 32 в блок 36. Положительные фронты сигнала ТхС1 задают границы битовых интервалов для каждого входного сигнала из группы 43. Положительные фронты сигнала ТхС2 задают границы битовых интервалов сигнала TxD2. Отрицательные фронты сигналов ТхС1 и ТхС2 гарантируют истинность соответствующих данных TхD1 и TхD2. Аналогичные функции выполняют синхросигналы RхC1 и RхC2 сопровождения данных RхD1 и RхD2. Как будет показано, поток данных по первому каналу связи имеет постоянную скорость, в отличие от потока данных по второму каналу. Скорость передачи битов по второму каналу зависит от кодов в первом канале и при случайном равномерном распределении последних составляет 62,5% скорости передачи четырехразрядных слов данных по первому каналу.

Все процессы, протекающие при передаче данных предлагаемым устройством, синхронизируются от генератора 49 (см. фиг 5). По положительному фронту сигнала ТхС1 на входы 43 устройства поступает очередной четырехразрядный двоичный код Х0 Y0 Z0 V0 данных TхD1 (Х0 - старший разряд). В примере, приведенном на временных диаграммах 70 и 71 (см. фиг. 7), от источника данных под управлением сигнала ТхС1 поступает такая последовательность кодов TхD1: 01012= 5, 00112= 3, 11002=12,...,00012=1. При этом коды, помеченные символами "x", препятствуют распространению данных по дополнительному каналу в соответствующих битовых интервалах.

Регистр 57 принимает данные по положительному фронту сигнала ТхС1, поэтому в этом регистре фиксируется "старый" код TхD1, прежде чем на его входы поступит "новый" код. (По аналогичной схеме построены обычные сдвиговые регистры с общей цепью синхронизации. ) В результате данные Р на выходах регистра 57 формируются с задержкой на один такт по сравнению с данными TхD1 на его входах (см. диаграмму 76, повторяющую диаграмму 71 со сдвигом вправо на один период сигнала ТхС1).

Данные TхD1 анализируются дешифратором 58. Если данные принадлежат диапазону 0, 1, 2,..., 9, то на выходе 62 дешифратора формируется сигнал А=1. Если данные принадлежат диапазону 10, 11, 12,..., 15, то на выходе 62 дешифратора формируется сигнал А=0 (см. временную диаграмму 72). Как показано на фиг. 6, дешифратор может быть выполнен на двух логических элементах 68 и 69. Сигнал А с выхода дешифратора 58 принимается в триггер 60 по отрицательному фронту сигнала ТхС1 (см. временную диаграмму 73). Сигнал В=0 с выхода триггера 60 закрывает элемент И 61 и препятствует формированию сигнала ТхС2 в тех ситуациях, когда необходимо приостановить передачу данных по второму каналу (см. временную диаграмму 74). Поэтому данные TхD2 запрашиваются и поступают с переменным темпом по мере возможности их передачи по второму каналу (см. временную диаграмму 75).

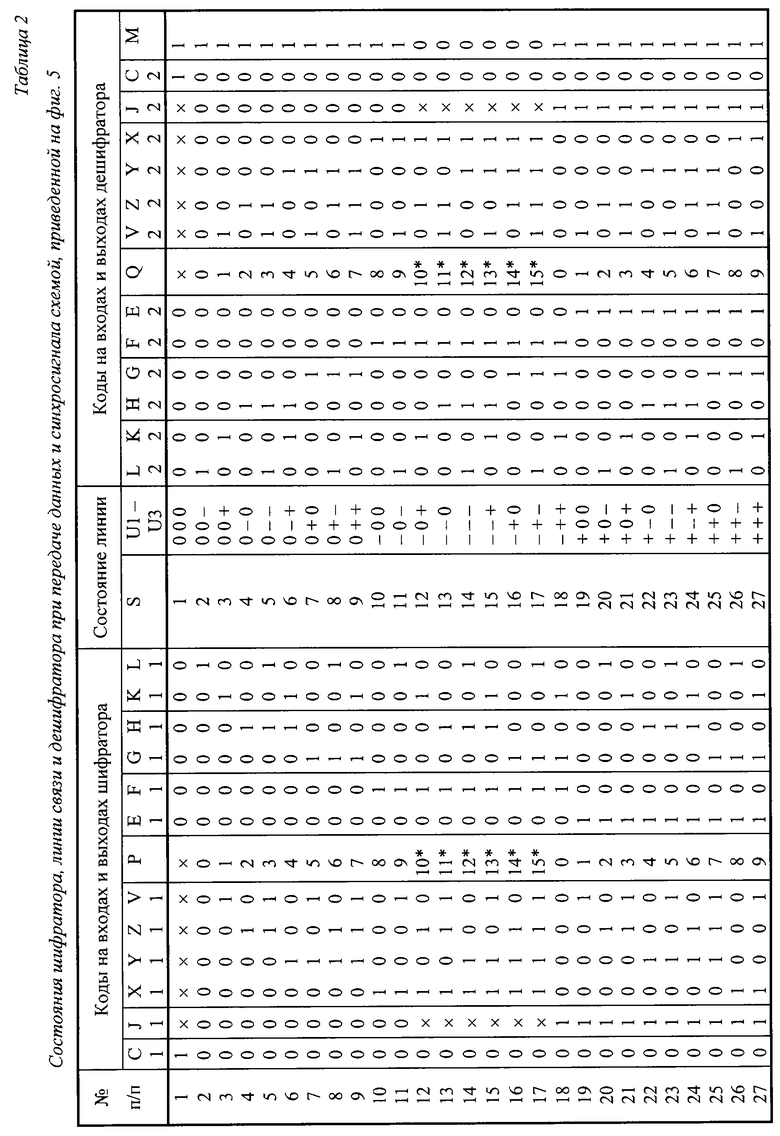

Сигналы Р, С1 и J1 (TхD2) поступают на входы шифратора 50. Шифратор 50, усилители 51, 52 и дешифратор 53 выполняют преобразование кодов в соответствии с табл. 2.

В предлагаемом устройстве, так же как и в прототипе, применено трехуровневое кодирование сигналов в линии связи 35. Напряжение U1 (U2, U3) между проводами витой пары 38 может быть отрицательным, нулевым или положительным (сокращенно: -, 0, +). Это напряжение формируется усилителем 51 в зависимости от сочетания битов E1 F1 (G1 H1, K1 L1) на его входах следующим образом. При Е1=F1=0 (G1=H1=0, K1=L1=0) напряжение Ul (U2, U3) нулевое, при Е1= 0, F1=1 (G1=0, H1=1; K1=0, L1=1) - отрицательное, при E1=1, F1=0 (G=1, H1=0; K1=1, L1=0) - положительное. Код E1 F1 G1 H1 K1 L1 формируется шифратором 50 из входного кода X1 Y1 Z1 V1 С1 J1 (данные Р, синхросигнал, данные TxD2), как показано в левой части табл. 2.

Входные усилители 52 и дешифратор 53 осуществляют обратное преобразование сигналов, представленных напряжениями U1, U2 и U3 в витых парах проводов линии связи. В графе S табл. 2 перечислены 33 = 27 возможных состояний трехуровневых сигналов U1-U3 в линии связи. Первое состояние (S=1) соответствует нулевым напряжениям в линии: (U1 U2 U3)=(0 0 0). Это состояние выбрано для отображения единичного значения синхросигнала С1. Символы "х" в левой части первой строки таблицы означают, что при С1=1 входной код X1 Y1 Z1 V1 J1 не воспринимается шифратором. Эти же символы в правой части первой строки таблицы показывают, что при выдаче восстановленного синхросигнала С2=1 выходные данные Х2 Y2 Z2 V2 J2 также не определены. При этом сигнал М принимает значение лог. "1".

Состояния 2, 3,.... 27, соответствующие условию С1=0, используются для отображения данных первого и, в дополнение к этому, по возможности, второго каналов. Как следует из табл. 2, коды Р, принадлежащие диапазону 0-9, представлены двумя равноценными копиями. Первая копия размещена в строках с номерами 2-11 и сопровождается нулевым значением сигнала J1. Вторая копия размещена в строках с номерами 18-27 и сопровождается единичным значением сигнала J1. Передача первой или второй копии кода по первому каналу сопровождается передачей одного бита данных (TхD2=J1) по второму каналу. Коды Р, принадлежащие диапазону 10-15, представлены в единственном экземпляре и размещены в строках 12-17. При передаче этих кодов состояние сигнала J1 не учитывается (что отражено символами "х" в столбце "J1" таблицы). Это означает, что параллельная передача данных по второму каналу невозможна.

Как показано на временной диаграмме 77 сигналов W линии, в первых половинах тактов состояние линии S=1, так как С1=1 (см. табл. 2). Во второй половине первого такта С1=0, Р=2, J=0. Этому сочетанию сигналов соответствует четвертая строка таблицы. Из нее следует, что состояние линии S = 4. Аналогично, во второй половине второго такта С1=0, Р=5, J=1, в результате в линии формируется состояние S=23 (+ - -) и т. д.

Дешифратор 53 восстанавливает синхросигнал С2 (совпадающий с синхросигналом С1 с точностью до задержки передачи) и формирует сигналы Q, J2 и М (см. временные диаграммы 78-81). Сигналы Q и J2 содержат области неопределенности, выделенные на диаграммах затененными участками.

Для устранения неопределенности сигналов Q применен параллельный регистр 54. Данные принимаются в него по положительному фронту сигнала С3 (см. диаграмму 82), который формируется из сигнала С2 после его задержки на четверть периода и последующего инвертирования. В результате сигналы RхD1 (диаграмма 83) и RхC1 с некоторой задержкой повторяют сигналы TхD1 и ТхС1.

Сигнал С3 задерживается элементом 66 для исключения "гонок". При наличии единичного сигнала MX (диаграмма 85) элемент И 67 формирует периодический сигнал RхC2 (диаграмма 86). При MX=0 из сигнала RхC2 исключаются положительные импульсы, соответствующие областям неопределенности сигнала J3 (диаграмма 84). Таким образом регулируется поток данных по дополнительному каналу.

При равномерном случайном распределении кодов TхD1 вероятность их попадания в диапазон 0-9 равна 10/16=0,625. Каждое попадание в этот диапазон сопровождается передачей одного бита данных по дополнительному каналу. Поэтому скорость передачи битов по дополнительному каналу составляет 62,5 % скорости передачи четырехразрядных кодов TхD1 по основному каналу. Протокол передачи данных может предусматривать передачу нулевых кодов TхD1 в незанятом состоянии первого канала. Тогда дополнительный канал используется в каждом такте синхросигнала, т. е. в нем полностью исключаются приостановки передачи данных.

Для исключения неблагоприятных ситуаций, при которых в течение длительных промежутков времени коды попадают в диапазон 10-15, можно применить скремблирование одного или двух старших разрядов данных TхD1 перед их подачей на входы 43.

Предлагаемое устройство позволяет повысить скорость передачи данных за счет использования дополнительного канала (параллельно с основным) без увеличения числа витых пар проводов линии.

Источники информации

1. Патент США 5160929, Fig 1.

2. Патент США 5160929, Fig 2 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2206181C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214046C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214044C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2205445C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2214061C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2271612C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2262205C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2272360C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2004 |

|

RU2260251C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЛИНЫ ДВУХПРОВОДНОЙ ЛИНИИ ПЕРЕДАЧИ ДАННЫХ | 2002 |

|

RU2233554C1 |

Изобретение относится к устройствам для кодирования - декодирования данных и может быть использовано в синхронных телекоммуникационных системах. Технический результат, достигаемый при реализации, - повышение скорости передачи данных. Устройство содержит подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, регистр, дешифратор, инвертор, триггер и элемент И, блок приема данных содержит группу входных усилителей, дешифратор, регистр, два элемента задержки, элемент И и инвертор. Повышение скорости передачи данных достигнуто благодаря использованию дополнительного канала связи (параллельно с основным) без увеличения числа витых пар проводов линии. 7 ил., 2 табл.

Устройство для кодирования-декодирования данных, содержащее подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, выход генератора синхросигналов соединен с входом шифратора и является первым выходом синхронизации первого канала устройства, группа входов блока передачи данных является группой входов данных первого канала устройства, группа выходов шифратора соединена с входами группы выходных усилителей, выходы которых соединены с витыми парами проводов линии связи, блок приема данных содержит группу входных усилителей, дешифратор, регистр, первый элемент задержки и инвертор, входы группы входных усилителей соединены с витыми парами проводов линии связи, а их выходы - с входами дешифратора, выходы которого соединены с входами данных регистра и, через первый элемент задержки, с входом инвертора, выход которого соединен с входом синхронизации регистра и является вторым выходом синхронизации первого канала устройства, группа выходов регистра является группой выходов данных первого канала устройства, отличающееся тем, что блок передачи данных дополнительно содержит регистр, дешифратор, инвертор, триггер и элемент И, группа входов данных первого канала устройства соединена с входами дешифратора и с входами данных регистра, выходы которого соединены с входами шифратора, а вход синхронизации - с выходом генератора синхросигналов, с первым входом элемента И и с входом инвертора, выход которого соединен с входом синхронизации триггера, выход которого соединен с вторым входом элемента И, выход которого является первым выходом синхронизации второго канала устройства, вход данных второго канала устройства соединен с входом шифратора, выход дешифратора соединен с входом данных триггера, блок приема данных дополнительно содержит второй элемент задержки и элемент И, вход второго элемента задержки соединен с выходом инвертора, а его выход - с первым входом элемента И, второй вход которого соединен с выходом регистра, выход элемента И является вторым выходом синхронизации второго канала данных устройства, выход данных второго канала устройства соединен с выходом регистра.

| US 5160929 A, 03.11.1992 | |||

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2168270C2 |

| RU 2004973 C1, 15.12.1993 | |||

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА ВО МНОГОЗНАЧНЫЙ КОД (ВАРИАНТЫ) | 1997 |

|

RU2109400C1 |

| БИБЛИОТЕКА IК. И. Умрихин и А. А. Шахназаров'~°°~~~~~~~~—• .. ~=»J | 0 |

|

SU299639A1 |

Авторы

Даты

2003-10-10—Публикация

2002-01-31—Подача