Изобретение относится к области вычислительной техники и может быть использовано в МДП интегральных схемах при реализации арифметических и логических каскадных устройств.

Известен парафазный логический элемент с запоминающим триггером на выходе (Патент США № 6331791, Н 03 К 19/096, НКИ 326/98 от 18.12.2001). В нем используются парафазные входные и выходные сигналы, что расширяет функциональные возможности элемента и триггер-фиксатор для запоминания результата. Недостатком элемента является его сложность, что усложняет синхронизацию, увеличивает длительность цикла и снижает быстродействие.

Наиболее близким техническим решением к предлагаемому является парафазный логический элемент на МДП транзисторах (Патент РФ № 2107387, Н 03 К 19/01 от 26.12.1995). Это устройство, принятое за прототип, предназначено для реализации логических функций с однофазным тактированием и с запоминанием результата в R-S триггере на полутакте при наличии парафазных входных и выходных сигналов. Логический блок элемента реализован па ключевых цепях только из транзисторов n-типа, а исходное состояние элемента обеспечивается предзарядовыми транзисторами p-типа. Недостаток этого устройства - избыточное потребление мощности, что обусловлено тем, что каждый такт функционирования элемента сопровождается перезарядом внутренних межэлектродных емкостей элемента независимо от того, изменяется логическое состояние выходов элемента или подтверждается их предыдущее состояние.

Технической задачей, решаемой в изобретении, является уменьшение потребляемой мощности.

Поставленная цель достигается тем, что парафазный логический элемент на КМДП транзисторах, содержащий R-S триггер, тактовый транзистор n-типа, два предзарядовых транзистора p-типа и логический блок, содержащий прямые и инверсные ключевые цепи, которые состоят из последовательно соединенных транзисторов n-типа, затворы которых подключены к соответствующим входам элемента, на которые подаются парафазные сигналы входных переменных так, что только одна из ключевых цепей является замкнутой, первые выводы прямых и инверсных ключевых цепей объединены и через тактовый транзистор n-типа соединены с общей шиной, вторые выводы прямых и инверсных ключевых цепей подключены соответственно к прямому и инверсному выходам логического блока. R-S триггер выполнен на двух элементах 2И-НЕ, первые входы которых являются входами обратной связи и одновременно выходами элемента, а вторые входы первого и второго элементов 2И-НЕ соответственно через первый и второй предзарядовые транзисторы p-типа, затворы которых подключены к затвору тактового транзистора n-типа и к тактовой шине, соединены с шиной питания, устройство содержит два проходных транзистора n-типа, причем первый из них включен между прямым выходом логического блока и вторым входом первого элемента 2И-НЕ, а второй - между инверсным выходом логического блока и вторым входом второго элемента 2И-НЕ, затворы первого и второго проходных транзисторов n-типа подключены к первым входам соответственно второго и первого элементов 2И-НЕ.

Существенными отличительными признаками в указанной совокупности признаков является введение двух проходных транзисторов n-типа н включение каждого из них между соответствующим выходом логического блока и входом одноименного элемента 2И-НЕ R-S триггера и подключение затворов указанных транзисторов к соответствующим выходам устройства.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - уменьшение потребляемой мощности. При любом наборе входных сигналов в рабочем полутакте благодаря введению проходных транзисторов перезаряд внутренних емкостей элемента, что определяет потребление мощности при переключении, происходит только в том случае, когда состояние выходов элемента в соответствии с данными входными сигналами должно измениться. Если набор входных сигналов ведет только к подтверждению предыдущего состояния элемента, проходной транзистор, управляемый по затвору с соответствующего выхода R-S триггера, блокирует цепь разряда емкости, предварительно заряжаемой до напряжения питания. Во время предзаряда цепи предзарядовых транзисторов потребляют ток от источника питания только в том случае, если состояние выходов элемента изменилось на противоположное. Причем внутренние емкости логического блока при этом не перезаряжаются. В устройстве-прототипе каждый цикл работы элемента сопровождается полным перезарядом внутренних емкостей элемента независимо от конкретного набора входных сигналов. Поскольку вероятность перехода элемента в новое - противоположное логическое состояние в двоичной системе равно одной второй, при использовании данных элементов потребление мощности уменьшается в два раза.

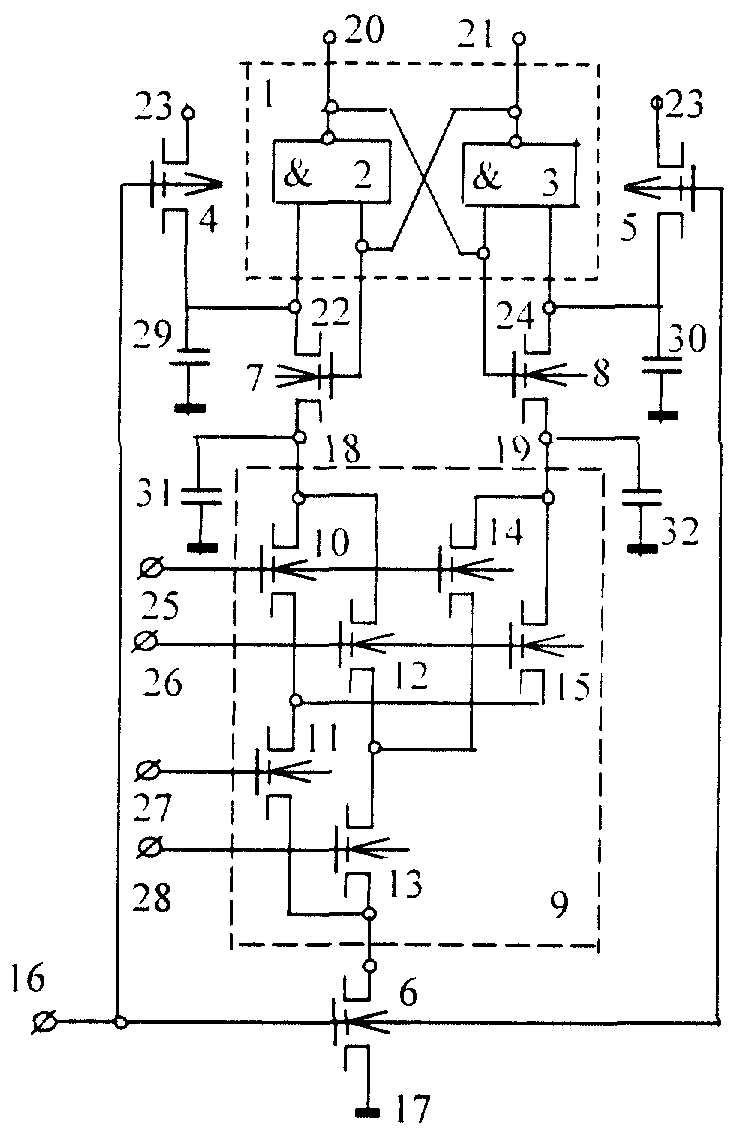

На чертеже приведена принципиальная схема заявляемого парафазного логического элемента на примере одноразрядного полусумматора арифметических устройств с ускоренным переносом.

Парафазный логический элемент на КМДП транзисторах содержит R-S триггер 1. состоящий из первого 2 и второго 3 элементов 2И-НЕ, первый 4 и второй 5 предзарядовые транзисторы p-типа, тактовый транзистор 6 n-типа, первый 7 и второй 8 проходные транзисторы n-типа и логический блок 9, который выполнен на 6 транзисторах 10-15 n-типа. Прямые ключевые цепи составляют пары первого 10 и второго 11, третьего 12 и четвертого 13 последовательно соединенных транзисторов n-типа. Инверсные ключевые цепи составляют пары четвертого 13 и пятого 14, второго 11 и шестого 15 последовательно соединенных транзисторов n-типа.

Затворы предзарядовых транзисторов 4, 5 p-типа и тактового транзистора 6 n-типа подключены к тактовой шине 16. Первые выводы прямых и инверсных ключевых цепей объединены и через тактовый транзистор 6 n-типа соединены с общей шиной 17. Вторые выводы прямых и инверсных ключевых цепей подключены соответственно к прямому 18 и инверсному 19 выходам логического блока 9. Первые входы элементов 2И-НЕ являются входами обратной связи R-S триггера и одновременно выходами 20, 21 устройства. Второй вход 22 первого 2 элемента 2И-НЕ через первый предзарядовый транзистор 4 p-типа соединен с шиной питания 23, а через первый проходной транзистор 7 n-типа - с прямым выходом 18 логического блока 9. Второй вход 24 второго 3 элемента 2И-НЕ через второй предзарядовый транзистор 5 p-типа соединен с шиной питания 23 и через второй проходной транзистор 8 n-типа - с инверсным выходом 19 логического блока 9. Затворы первого 7 и второго 8 проходных транзисторов подключены к выходам 21 и 20 устройства, которые соединены обратными связями с первыми входами соответственно второго 3 и первого 2 элементов 2И-НЕ R-S триггера 1.

Затворы транзисторов 10-15 n-типа, составляющих ключевые цепи логического блока 9, подключены к входам 25-28 элемента, на которые подаются парафазные сигналы входных переменных таким образом, что только одна ключевая цепь является замкнутой. В логическом блоке 9 одноразрядного полусумматора на первый 25 и второй 26 входы, которые подключены к затворам первого 10, пятого 14 и соответственно третьего 12, шестого 15 транзисторов, подаются парафазные сигналы, соответствующие прямому и логически дополняющему значениям первой переменной. На третий 27 и четвертый 28 входы, которые подключены к затворам второго 11 и соответственно четвертого 13 транзисторов, подаются парафазные сигналы, соответствующие прямому и логически дополняющему значениям второй переменной. Двоичному значению логической 1 соответствует высокий уровень напряжения шины питания, а значению логического 0 - низкий уровень напряжения общей шины. Открытому или замкнутому состоянию транзистора n-типа соответствует сигнал логической 1, поданный на затвор транзистора.

Каждая ключевая цепь реализует единичное множество состояний входных переменных (состояние замкнутости цепи), которые не должны логически пересекаться, т.е. при любом наборе входных переменных замкнутой может быть только одна из ключевых цепей. Ключевые цепи строятся из последовательно соединенных транзисторов по таблицам истинности соответствующих функций. Причем каждому набору входных переменных соответствует одна прямая ключевая цепь (если логическое значение реализуемой функции равно 1) либо одна инверсная ключевая цепь (если логическое значение реализуемой функции равно 0).

Элементы 2И-НЕ 2 и 3 включены по питанию между шиной питания 23 и общей шиной 17.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при нулевом сигнале на тактовой шине 16 тактовый транзистор 6 n-типа закрыт, а предзарядовые транзисторы 4 и 5 p-типа - открыты. От шины питания 23 через указанные транзисторы p-типа происходит процесс предзаряда узловых емкостей 29 и 30, связанных с первыми логическими входами 12 и 13 первого 2 и второго 3 элементов 2И-НЕ до уровня логической 1, равного напряжению питания. На первом полутакте на входах 25-28 элемента устанавливаются соответствующие парафазные сигналы, благодаря которым одна из ключевых цепей, например, прямая ключевая цепь, состоящая из первого 10 и второго 11 транзисторов n-типа оказывается замкнутой. В этом случае логические значения первой и второй переменных равны 1 (на входах 25 и 27 - сигнал логической 1, а на входах 26 и 28 - соответственно логического 0). R-S триггер 1 при этом находится в предыдущем логическом состоянии, например, на выходе 20 - сигнал логического 0, а на выходе 21 - сигнал логической 1, что соответствует результату суммирования на предыдущем этапе, равному 1.

На втором полутакте после подачи положительного сигнала на тактовую шину 16 тактовый транзистор 6 n-типа открывается, а предзарядовые транзисторы p-типа 4 и 5 закрываются. Поскольку первый проходной транзистор 7 n-типа открыт, узловая емкость 29 и внутренняя приведенная емкость 31 логического блока 9 разряжаются через первую ключевую цепь, находящуюся в замкнутом состоянии, и тактовый транзистор 6. На втором входе 22 первого элемента 3И-НЕ 3 появляется сигнал логического 0. На выходе 20 при этом формируется сигнал логической 1, а на выходе 21 за счет обратной связи R-S триггера - сигнал логического 0. Данное состояние триггера 1 соответствует результату суммирования, равному 0 (сумма двух 1). При этом первый проходной транзистор 7 n-типа закрыт, а второй проходной транзистор 8 n-типа открыт.

На втором цикле работы устройства повторяется этап предзаряда и емкость 29 через предзарядовый транзистор 4 p-типа заряжается до напряжения питания, а внутренняя приведенная емкость 32 логического блока 9 дополнительно через второй проходной транзистор 8 n-типа подзаряжается до уровня напряжения питания минус пороговое напряжение транзисторов n-типа. Другая внутренняя приведенная емкость 31 логического блока 9 при этом не заряжается, т.к. первый проходной транзистор 7 закрыт. Если на втором цикле производится сложение двух переменных равных 0 (на входах 26 и 28 - сигналы логической 1), то результат суммирования так же, как и в рассмотренном случае, равен 0. При этом замкнутой является вторая ключевая цепь, состоящая из третьего 12 и четвертого 13 транзисторов n-типа. При подаче сигнала на тактовую шину 16 разряда емкости 29 на входе первого 2 элемента 2И-НЕ не происходит, поскольку первый проходной транзистор 7 закрыт. Состояние R-S триггера при этом не изменяется и вообще никаких процессов, связанных с протеканием токов и потреблением мощности, не происходит. На очередном полутакте предзаряда узловые емкости 29 и 30 сохраняют свое исходное состояние и не потребуют дополнительную мощность от источника питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2014 |

|

RU2542660C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| ТАКТИРУЕМЫЙ ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2382490C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ НА КМДП ТРАНЗИСТОРАХ | 2008 |

|

RU2368072C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2012 |

|

RU2515702C1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

Изобретение относится к вычислительной технике и может использоваться в МДП интегральных схемах для арифметических и логических устройств. Технический результат заключается в уменьшении потребляемой мощности. Устройство содержит R-S триггер (1), предзарядовые транзисторы (Т) (4) и (5) р-типа, тактовый Т (6) n-типа, проходные Т (7) и (8) n-типа и логический блок (9), содержащий прямые и инверсные ключевые цепи на Т (10-15) n-типа. Затворы предзарядовых Т (4, 5) и тактового Т (6) подключены к тактовой шине (16). Первые выводы прямых и инверсных ключевых цепей через тактовый Т (6) соединены с общей шиной (17). Вторые выводы прямых и инверсных ключевых цепей подключены соответственно к прямому (18) и инверсному (19) выходам блока (9). Первые входы элементов 2И-НЕ (2, 3) являются входами обратной связи R-S триггера (1) и одновременно выходами (20, 21) устройства. Вторые входы (22, 24) через одноименные предзарядовые Т (4) или (5) соединены с шиной питания (23), а через одноименные проходные Т (7) или (8) - соответственно с прямым (18) или инверсным (19) выходами блока (9). Затворы проходных Т (7) и (8) подключены к выходам (21) и (20) устройства. На входы 25-28 подаются парафазные сигналы переменных так, что только одна ключевая цепь логического блока (9) является замкнутой. 1 ил.

Парафазный логический элемент на КМДП транзисторах, содержащий RS-триггер, тактовый транзистор n-типа, два предзарядовых транзистора р-типа и логический блок, содержащий прямые и инверсные ключевые цепи, которые состоят из последовательно соединенных транзисторов n-типа, затворы которых подключены к соответствующим входам элемента, на которые подаются парафазные сигналы входных переменных так, что только одна из ключевых цепей является замкнутой, первые выводы прямых и инверсных ключевых цепей объединены и через тактовый транзистор n-типа соединены с общей шиной, вторые выводы прямых и инверсных ключевых цепей подключены соответственно к прямому и инверсному выходам логического блока, RS-триггер выполнен на двух элементах 2И-НЕ, первые входы которых являются входами обратной связи и одновременно выходами элемента, а вторые входы первого и второго элементов 2И-НЕ соответственно через первый и второй предзарядовые транзисторы р-типа, затворы которых подключены к затвору тактового транзистора n-типа и к тактовой шине, соединены с шиной питания, отличающийся тем, что устройство содержит два проходных транзистора n-типа, причем первый из них включен между прямым выходом логического блока и вторым входом первого элемента 2И-НЕ, а второй - между инверсным выходом логического блока и вторым входом второго элемента 2И-НЕ, затворы первого и второго проходных транзисторов n-типа подключены к первым входам соответственно второго и первого элементов 2И-НЕ.

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| US 6331791 B1, 18.12.2001 | |||

| US 6204697 B1, 20.03.2001 | |||

| US 4570084, 11.02.1986 | |||

| Маховик | 1972 |

|

SU440514A1 |

Авторы

Даты

2005-08-10—Публикация

2003-12-15—Подача