Изобретение относится к области электросвязи, преимущественно к дуплексной передаче сигналов по каналам связи.

Известно устройство для разделения сигналов двух направлений [1], состоящее из передающего устройства, вычитателя и приемного устройства. Принцип действия таких устройств основан на искусственном вырабатывании сигналов эха в формирующем адаптивном фильтре и в дальнейшем компенсации эхо-сигналов, проникающих на вход приемного устройства. Операция компенсации эхо-сигналов осуществляется с помощью вычитания из суммарного принимаемого сигнала и сигналов эха дополнительно сформированной копии сигналов эха.

Недостатками подобных устройств являются низкая помехоустойчивость принимаемых сообщений, большой уровень нескомпенсированного эхо-сигнала, большая критичность к корреляционным связям сигналов передачи и приема. Даже при частичной коррелированности сигналов двух направлений устройство начинает компенсировать принимаемый сигнал, делая дуплексный обмен сигналов невозможным.

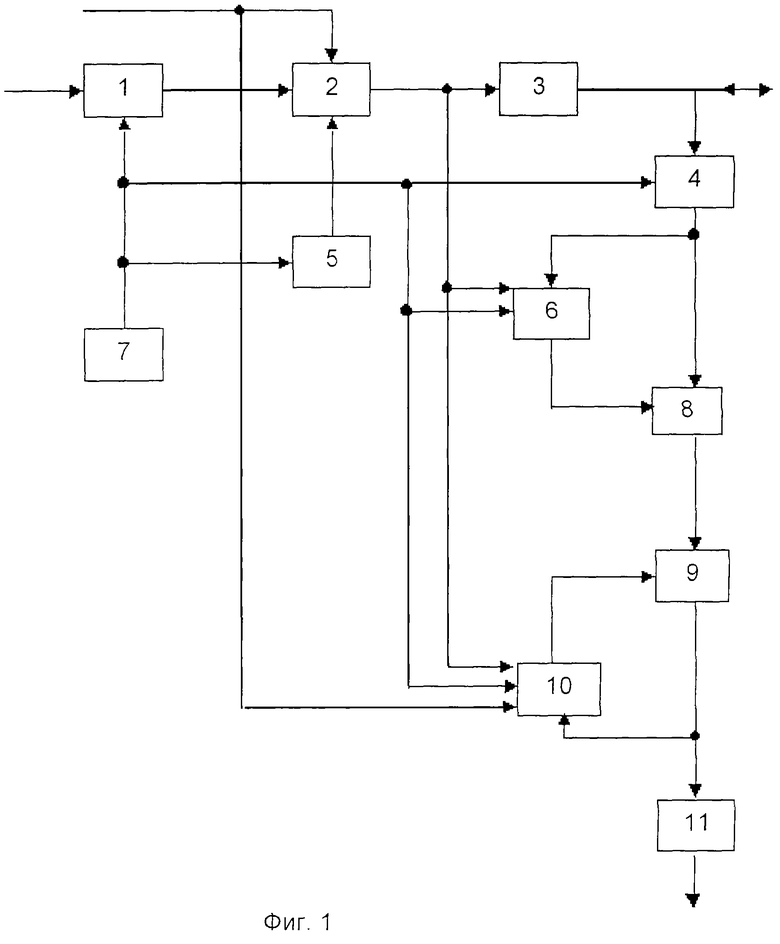

Этот недостаток устранен в прототипе [2], содержащем последовательно соединенные (Фиг.1) входной блок 1, коммутатор 2, первый цифроаналоговый преобразователь 3, аналого-цифровой преобразователь 4, первый блок 6 памяти, вычитатель 8, вторым входом соединенный с выходом первого блока 6 памяти, сумматор 9, второй блок 10 памяти, выход которого соединен со вторым входом сумматора 9, а также последовательно соединенные генератор 7 и формирователь 5 обучающих сигналов, выходом соединенный со вторым входом коммутатора 2, управляющий вход которого объединен со входом обнуления второго блока 10 памяти, при этом выход генератора 7 соединен со вторыми входами соответственно входного блока 1, АЦП 4, первого 6 и второго 10 блоков памяти, а выход коммутатора соединен с третьим входами первого 6 и второго 10 блоков памяти.

Работа прототипа состоит из двух частей: предварительного обучения и дуплексного обмена сигналами. При предварительном обучении устройства под параметры канала связи блок обучения 5 выдает в цифровой форме все использованные цифровые комбинации, отклики от которых записываются в первом блоке 6 памяти. На период адаптации второй блок 10 памяти обнуляется. При обучении принимаемые сигналы должны отсутствовать.

По окончании предварительной адаптации начинается дуплексный обмен сигналами. Включаются оба блока памяти.

Используемая структура нерекурсивной и рекурсивной частей компенсатора зеркально симметричны. В нерекурсивной части производится компенсация сигналов передачи и модуляция сигналов приема. Рекурсивная часть полностью восстанавливает форму принимаемых сигналов.

Однако прототип может работать только на каналах с постоянными параметрами. При переходе параметров канала связи из одного состояния в другое во втором блоке 10 памяти накапливается сигнал надокомпенсации, который дополнительно не компенсируется. Это явление может привести к срыву дуплексного обмена и потребует нового переобучения. Если параметры канала связи изменяются с большой скоростью, то в таких условиях работа прототипа становится невозможной. При этом помехоустойчивость принимаемых сообщений будет достаточно низкой.

Целью настоящего изобретения является повышение помехоустойчивости принимаемых сообщений.

Поставленная цель достигается тем, что в устройстве для разделения направлений передачи в дуплексных системах связи, содержащем последовательно соединенные входной блок, коммутатор, первый цифроаналоговый преобразователь, выходом соединенный с двухпроводным каналом связи, аналого-цифровой преобразователь, вычитатель, сумматор и второй цифроаналоговый преобразователь, а также первый и второй блоки памяти и последовательно соединенные генератор и блок обучения, выходом соединенный со вторым входом коммутатора, третий вход которого является управляющим, при этом выход генератора соединен со вторыми входами соответственно входного блока, аналого-цифрового преобразователя, первого и второго блоков памяти, третьи входы первого и второго блоков памяти подсоединены к выходу коммутатора, а первые входы первого и второго блоков памяти подсоединены соответственно к выходу аналого-цифрового преобразователя и выходу сумматора, введены первый и второй блоки адаптации, первый и второй аттенюаторы и одновибратор, при этом выход первого блока памяти подсоединен ко входу первого аттенюатора и первому входу первого блока адаптации, выходы которых соединены со вторым и третьим входами вычитателя соответственно, выход второго блока памяти соединен со входом второго аттенюатора и первым входом второго блока адаптации, выходы которых соединены со вторым и третьим блоками сумматора соответственно, при этом вторые и третьи входы первого и второго блоков адаптации соединены с одноименными входами первого и второго блоков памяти, выход одновибратора соединен с четвертым входом первого блока памяти, а также с четвертым входом первого блока адаптации, а вход одновибратора объединен со входом управления коммутатора и четвертыми входами второго блока памяти и второго блока адаптации соответственно.

Докажем соответствие предлагаемого решения критерию "Существенные отличия".

1. Отличительным конструктивным признаком предлагаемого решения является введение двух блоков адаптации, двух аттенюаторов и одновибратора. При этом блоки адаптации содержат 2•(М-1) дополнительных блоков памяти, сумматоры и три аттенюатора.

При этом введенные блоки представляют собой единую совокупность конструктивных признаков, так как элементы предложенной конструкции взаимосвязаны, соединены в единую систему, действие одного из них непосредственно влияет на другие, замена какого-либо блока на другие нарушает работу всего устройства в целом. Такая новая совокупность конструктивных признаков обеспечивает положительный эффект (повышение помехоустойчивости принимаемых сообщений), который соответствует всему устройству, а не отдельным его элементам.

Кроме того, предложена конструкция первого и второго блоков адаптации.

2. Заявителем просмотрена техническая документация по классификации МКИ H 04 L 27/19 и УДК 621.393.3, относящаяся ко всему устройству в целом. В результате анализа вышеуказанной литературы, который изложен в тексте описания и в справке о патентных исследованиях, заявителем не обнаружено технических решений, аналогичных предлагаемому.

Также можно доказать появление у объекта изобретения новых свойств, не присущих его частям. Каждый из введенных блоков выполняет в отдельности те же функции, что и в известных устройствах. Например, блоки памяти считывают и записывают сигналы, сумматоры суммируют, аттенюаторы уменьшают в М раз сигнал и т.д. Однако введение новых блоков и связей между ними, а также новые электрические связи между введенными узлами и узлами прототипа создают новый механизм взаимодействия, который обеспечивает разделение сигналов двух направлений при изменении параметров канала связи и автоматически ведут подстройку устройства.

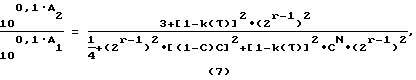

Устройство содержит /Фиг. 2/: 1 - входной блок, 2 - коммутатор, 3 - первый цифроаналоговый преобразователь, 4 - аналого-цифровой преобразователь, 5 - блок обучения, 6 и 10 - соответственно первый и второй блоки памяти, 7 - генератор, 8 - вычитатель, 9 - первый сумматор, 11 - второй цифроаналоговый преобразователь, 12 - первый блок адаптации, 13 - второй блок адаптации, 14 - одновибратор, 15 и 16 - соответственно первый и второй аттенюаторы.

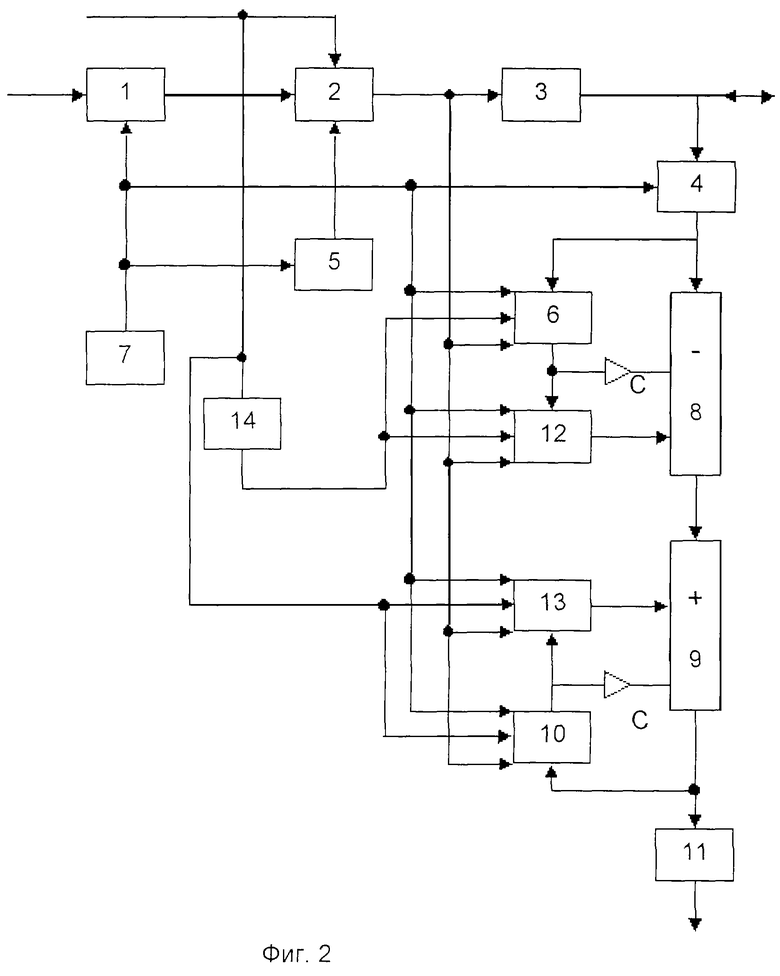

Первый блок 12 адаптации /Фиг.3/ содержит первый 17-1, второй 17-2,..., 17-(М-1) дополнительные блоки памяти, второй сумматор 18, третий аттенюатор 19.

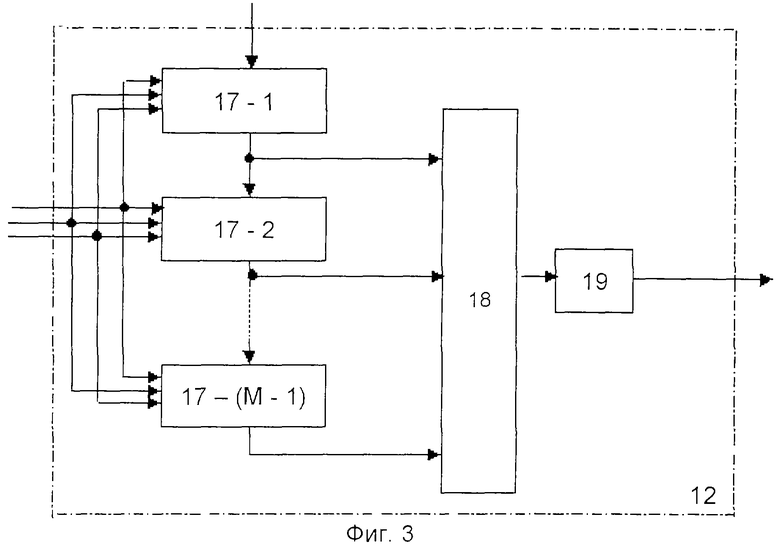

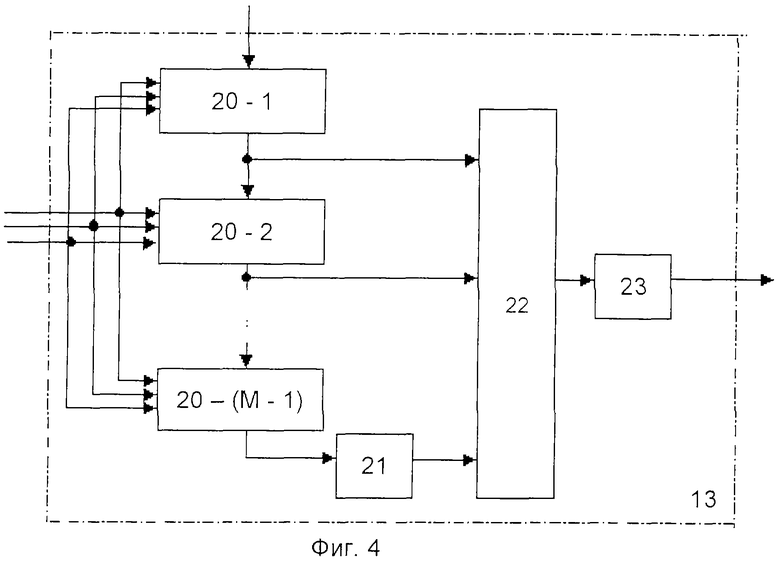

Второй блок 13 адаптации /Фиг.4/ содержит первый 20-1, второй 20-2,..., 20-(М-1) дополнительные блоки памяти, пятый аттенюатор 21, третий сумматор 22, четвертый аттенюатор 23.

Коэффициенты передачи первого 15, второго 16, третьего 19 и четвертого 23 аттенюаторов одинаковы и равны 1/М, где М - порядок сложности эхо-компенсатора. Для уменьшения сложности вычислительных затрат значение М выбирается кратным 2, т.е. М=1, 2, 4, 8,.... В этом случае операции умножения заменяются сдвигами вправо. В общем случае значение М может быть любым целым числом.

Конструктивное выполнение одновибраторов известно. Конструктивное выполнение блоков памяти (блоки 6, 10, 17, 20) известно. Это, к примеру, м/схема 1002ИР1. Вычитатель 8, сумматоры 9, 18, 22 строятся на многоразрядных м/схемах, к примеру 564ИМ1, 155ИМ1, 155ИМ3 и т.д.

Аналого-цифровые преобразователи 4 - стандартные узлы. Аналогично цифроаналоговые преобразователи конструктивно также представлены соответствующими м/схемами. Конструктивное выполнение остальных узлов также известно.

Предлагаемое устройство работает следующим образом.

Работу можно условно разбить на период предварительной адаптации к параметрам канала связи и рабочий цикл. Отметим, что в рабочем цикле производится автоматическая настройка под изменяющиеся параметры канала связи.

При предварительном обучении устройства на вход управления коммутатора 2 от оконечного оборудования данных ООД (на Фиг.2 не показан) поступает логический нуль. По данному сигналу коммутатор 2 подключает выход блока обучения 5 ко входу первого цифроаналогового преобразователя (ЦАП) 3. Сигнал управления ООД обнуляет второй блок 10 памяти и все дополнительные блоки 20 памяти во втором блоке 13 адаптации.

Помимо этого появление логического нуля на входе управления приводит к срабатыванию одновибратора 14, который вырабатывает кратковременный обнуляющий сигнал для первого блока 6 памяти и для дополнительных блоков 17 памяти в первом блоке 12 адаптации. После этих операций устройство готово к предварительной адаптации.

При предварительной адаптации сигналы противоположной стороны могут отсутствовать либо присутствовать, от этого работоспособность устройства, в целом, не изменится. Однако для лучшего понимания процесса предварительной адаптации будем полагать, что принимаемые сигналы отсутствуют.

Блок обучения 5 циклически выдает все используемые цифровые комбинации Ui(nT). Здесь подстрочный индекс означает квантованный по уровню сигнал, а значение n - дискретное время.

Комбинации Ui(nT) превращаются в отсчеты аналогового сигнала.

На выходе аналого-цифрового преобразователя 4 наблюдаем отсчеты сигнала, определяемые свойствами подключения канала, которые равны

Li(nT) = Ui(nT)*Gэхо(nT), (1)

где Gэхо(nT) - отсчеты импульсной реакции эхо-тракта;

* - означает операцию свертки.

Структура предлагаемого устройства такова, что двоичная цифровая комбинация Ui(nT) является адресом для первого 6 и второго 10 блоков памяти и дополнительных блоков 17 и 20 памяти в первом 12 и втором 13 блоках адаптации. Перечисленные выше блоки памяти работают синхронно. Порядок работы блоков памяти следующий: вначале по адресу Ui(nT) считывается прежнее содержимое, а затем по тому же адресу записывается входной сигнал соответствующего блока памяти. Так как во время начала адаптации все блоки памяти были обнулены, то считываются нули.

В первый блок 6 памяти записывается отклик канала связи с выхода АЦП 4. Дополнительные блоки 17 памяти первого блока 12 адаптации представляют собой многоразрядовые регистровые запоминающие устройства, следовательно, в первый дополнительный блок 17-1 памяти переписывается сигнал с выхода первого блока 6 памяти.

В последний дополнительный блок 17-(М-1) памяти переписывается сигнал с выхода дополнительного блока 17-(М-2) памяти.

Второй блок 10 памяти и все дополнительные блоки 20 памяти второго блока 13 адаптации обнулены и в начальный период и в работе не участвуют.

Все обучающие сигналы должны повторятся М раз. Таким образом, в момент времени от n=0 до n=N-1 первый обучающий сигнал U1(nT) дополняет часть памяти первого блока 6 памяти. Если используется V обучающих сигналов, то спустя промежуток времени, равный N•V, первый блок 6 памяти полностью заполнится образцами эхо-сигналов. По окончании временного интервала, равного M•N•V, первый блок 6 памяти и все дополнительные блоки памяти 17 в первом блоке 12 адаптации заполняются образцами эхо-сигналов. При этом наблюдается связь между передаваемыми обучающими сигналами Ui(nТ) и записываемыми откликами. Так, в ячейку с адресом U1(nT) записывается отклик канала связи L1(nТ). При этом в дополнительном блоке 17-(М-1) памяти первого блока 12 адаптации записывается значение эхо-сигнала, равное L1(1T). Соответственно по данному адресу в дополнительных блоках 17-2 и 17-1 памяти будут хранится образцы эхо-сигналов, равные L1[N•V•(M-2)•T] и L1[N•V•(M-1)•T]. В первом блоке 6 памяти будет хранится отклик, равный L1[N•V•M•T]. Следует отметить, что по закону относительности значения откликов канала связи отличаются на малую величину На этом процесс адаптации заканчивается. С выхода ООД снимается управляющий сигнал, коммутатор 2 подключает выход входного блока 1 ко входу первого ЦАП 3. Помимо этого снимается обнуляющий сигнал со второго блока 10 памяти и всех дополнительных блоков 20 памяти второго блока 13 адаптации.

Начинается рабочий цикл. Входной блок 1 представляет собой либо аналого-цифровой преобразователь при аналоговой передаче, либо универсальный последовательно/параллельный регистр сдвига при цифровом обмене сигналов. В том и другом случае на входе первого ЦАП 3 будут двоичные комбинации Ui(nТ), которые использованы при обучении устройства под параметры канала связи.

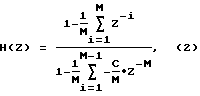

Совокупность вычитателя 8, первого блока 6 памяти, первого аттенюатора 15 и первого блока 12 адаптации в дальнейшем будем называть прямой структурой (ПС). Совокупность первого сумматора 9, второго блока 10 памяти, второго аттенюатора 16 и второго блока 13 адаптации будем называть взаимно-обратной структурой (ВОС). Характеристики ПС и ВОС зеркально симметричны. Передаточная характеристика каскадного соединения ПС и ВОС определяется следующим соотношением:

где1/М - коэффициенты передачи первого 15, второго 16, третьего 9 и четвертого 23 аттенюаторов;

М - порядок эхо-компенсатора;

С - коэффициент передачи пятого аттенюатора 21, 0,1<C≤1.

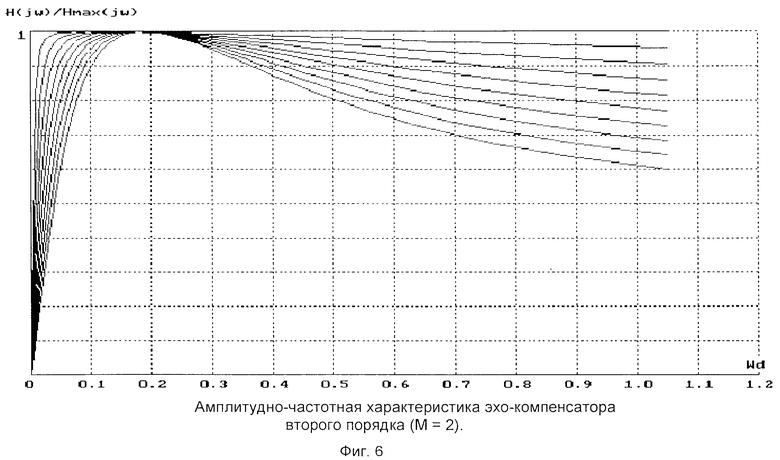

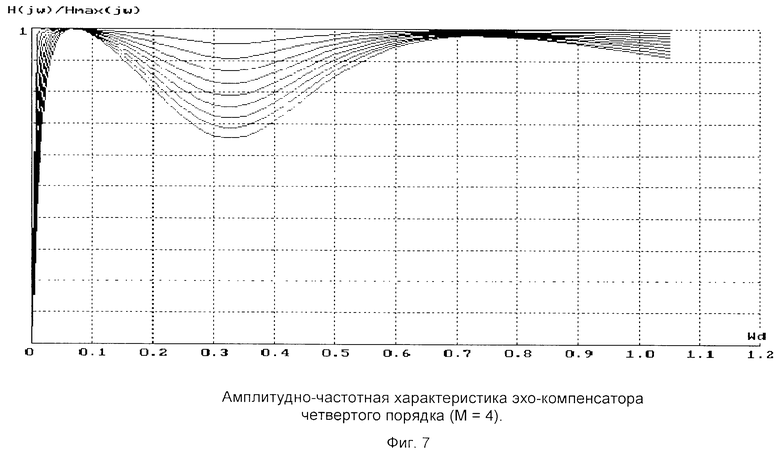

Передаточная характеристика, представленная выражением (2), представляет собой высокодобротный фильтр верхних частот.

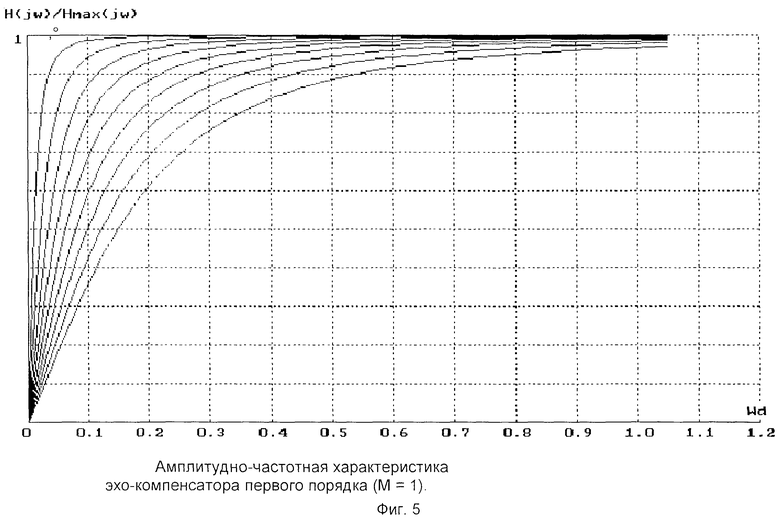

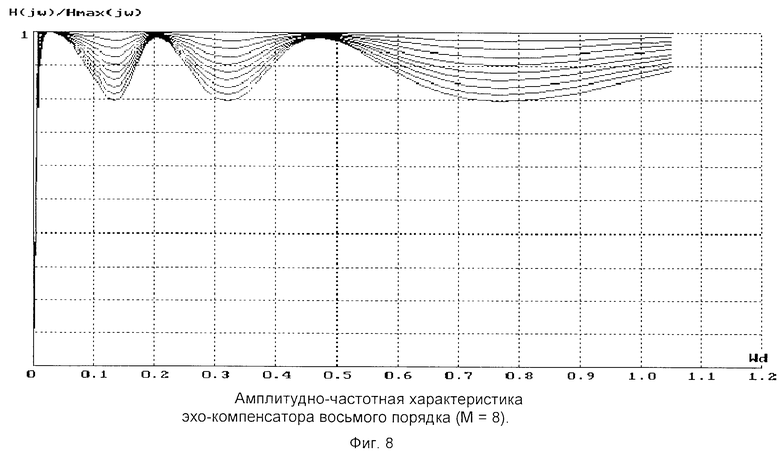

На Фиг. 5÷Фиг. 8 представлены амплитудно-частотные характеристики каскадного соединения ПС и ВОС при изменении коэффициента передачи пятого аттенюатора 21 в пределах от 0,1 до 1. При М=1 и С=1 предлагаемое устройство вырождается в структуру прототипа. Для этих параметров амплитудно-частотная характеристика частотно независима и устройство работоспособно на каналах с постоянными параметрами.

Как указывалось выше, в ячейки памяти первого блока 6 памяти и дополнительные блоки памяти 17 в первом блоке адаптации записываются отклики канала связи на соответствующие цифровые комбинации. Таким образом, на цифровую комбинацию U1(nT) во всех перечисленных блоках памяти хранятся отклики L1(nТ). Величины L1(nТ) во всех блоках памяти ПС отличаются на малую величину. Следовательно, значение L1(nТ) - это постоянная величина "в первом приближении". Аналогично по адресу U2(nT) хранится сигнал L2(nT) и т.д.

Следует заметить еще раз, что каскадное соединение ПС и ВОС - это фильтр верхних частот, который с большой точностью компенсирует постоянную составляющую.

На выходе АЦП 4 наблюдаем сумму двух составляющих - эхо-сигналов и принимаемых сигналов. В АЦП 4 аналоговый сигнал преобразуется в цифровой эквивалент. Так как работа предлагаемого устройства предполагает преобразование сигналов передачи в тракте приема в отчеты постоянной составляющей, то в ПС и перечисленных выше блоках памяти будет храниться значение постоянной составляющей совместно с отчетами принимаемых сигналов. На выходе ПС эхо-сигналы компенсируются, а принимаемые сигналы модулируются по закону сигналов передачи. В ВОС эта модуляция устраняется.

Для сигналов передачи (эхо-сигналов) каскадное соединение ПС и ВОС представляет собой высокодобротный фильтр - пробку.

Для принимаемых сигналов каскадное соединение ПС и ВОС в идеальном случае (при С=1) - это прямой провод с коэффициентом передачи, равным единице.

Однако в принимаемый сигнал вносятся амплитудно-частотные искажения, значения которых уменьшаются с увеличением коэффициента передачи пятого аттенюатора 21. При этом увеличение коэффициента передачи пятого аттенюатора 21 уменьшает скорость сходимости процесса настройки.

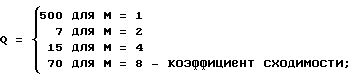

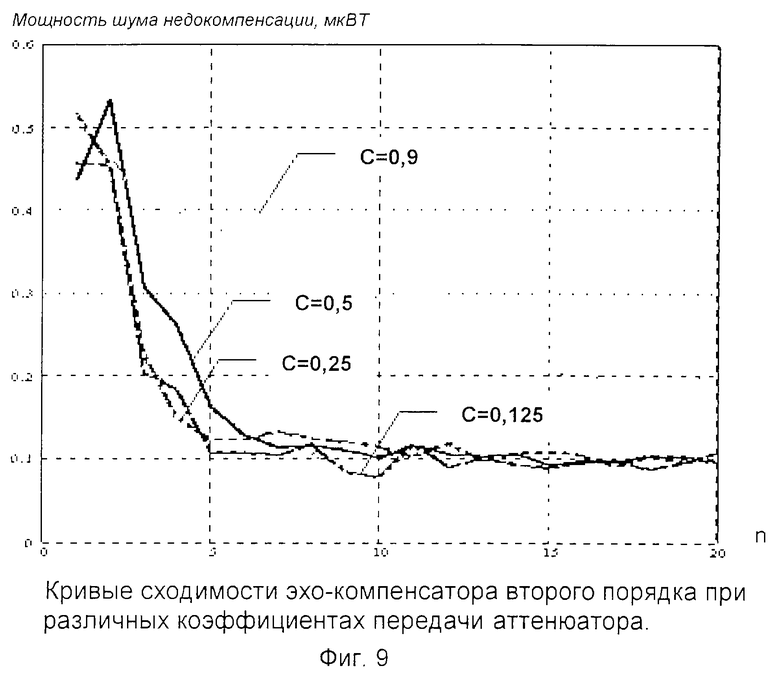

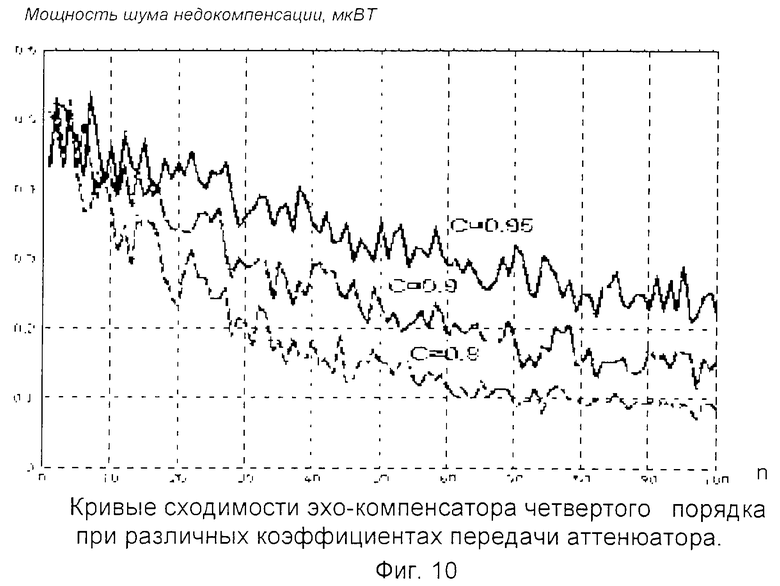

В качестве примера на Фиг.9 - Фиг.10 приведены кривые сходимости процесса настройки для эхо-компенсатора второго и четвертого порядков. Как видно из этих фигур, время сходимости заканчивается к 7 тактовому интервалу у компенсатора второго порядка.

С помощью моделирования на ЭВМ получены характеристики процесса сходимости, которые представлены в виде

Tсход≥Q•N•Zr•Tдискрет, (3)

где

Тдискрет - период дискретизации;

r - разрядность обработки;

N - количество отсчетов импульсной реакции.

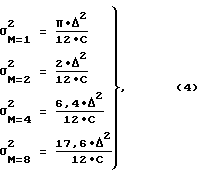

Полной компенсации сигналов передачи не будет. Величина остаточного шума недокомпенсации определяется следующими значениями:

где Δ - шаг квантования;

С - коэффициент передачи пятого аттенюатора 21.

Устройство является адаптивным. При изменении параметров канала связи изменяются образцы эхо-сигналов, которые записываются в блоки памяти ПС и спустя M•N•V тактовых интервалов произойдет самонастройка предлагаемого устройства под новые условия передачи.

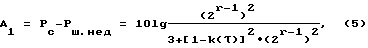

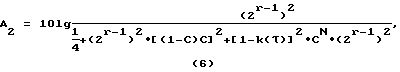

Оценим преимущества предлагаемого технического решения с прототипом, взятым за базовый объект. Величина защищенности у прототипа при изменении параметров канала связи определится следующим выражением:

где r - разрядность обработки;

k(τ) - коэффициент корреляции изменения параметров канала связи;

Рc - уровень сигнала приема;

Рш.нед. - величина шума недокомпенсации эхо-сигнала.

Величина защищенности у предлагаемого устройства равна

где С - коэффициент передачи пятого аттенюатора 21;

N - количество циклов обращения к заданной ячейки памяти.

Взяв отношение

окончательно получим

При С < 1 и N > 100 данное выражение всегда больше единицы.

При k(τ)=0,9; С=0,9; N=100; r=10 выигрыш составит 12,4 раза.

Таким образом, качество работы предлагаемого устройства превосходит качественные показатели прототипа.

Устройство прошло предварительные испытания и его предлагается внедрить на радиосети стандарта GSM для борьбы с явлением электрического эха.

Литература

1. Адаптивные фильтры под редакцией К.Ф.Н. Коуэна и П.М. Гранта. - М.: Мир, 1988. - 298 с. (аналог).

2. АС 1133675. Устройство для разделения направлений передачи в дуплексных системах связи. / Малинкин В.Б., Лебедянцев В.В., опубл. в БИ 1, 07.01.85 г. - прототип.

3. Тарабрин В.Г. Справочник по микросхемам.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2001 |

|

RU2233553C2 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2003 |

|

RU2255421C2 |

| Устройство для разделения сигналов двух направлений | 1989 |

|

SU1658393A1 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1987 |

|

SU1483647A2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| Адаптивное дуплексное устройство для передачи и приема фазоманипулированных сигналов | 1985 |

|

SU1256238A2 |

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1983 |

|

SU1133675A1 |

Изобретение относится к области электросвязи и может быть использовано в дуплексной передаче сигналов по каналам связи. Устройство содержит вычитатель, первый блок памяти, первый аттенюатор и первые (М-1) дополнительные блоки памяти, второй сумматор и третий аттенюатор, образующие прямую структуру (ПС), первый сумматор, второй блок памяти, второй аттенюатор, вторые (М-1) дополнительные блоки памяти, третий сумматор, четвертый и пятый аттенюаторы, образующие взаимообратную структуру ВОС. Каскадное соединение ПС и ВОС для эхо-сигналов образует фильтр-пробку, а для принимаемых сигналов - прямой провод с коэффициентом передачи, равным единице. Технический результат заключается в повышении помехоустойчивости принимаемых сообщений. 10 ил.

Устройство для разделения сигналов передачи и приема в дуплексных системах связи, содержащее последовательно соединенные входной блок, коммутатор, первый цифроаналоговый преобразователь, выходом соединенный с двухпроводным каналом связи, аналого-цифровой преобразователь, вычитатель, сумматор и второй цифроаналоговый преобразователь, а также первый и второй блоки памяти и последовательно соединенные генератор и блок обучения, выходом соединенный с вторым входом коммутатора, третий вход которого является управляющим, при этом выход генератора соединен со вторыми входами соответственно входного блока, аналого-цифрового преобразователя, первого и второго блоков памяти, третьи входы первого и второго блоков памяти, являющиеся адресными входами, соединены с выходом коммутатора, первые входы первого и второго блоков памяти, являющиеся сигнальными входами, соединены соответственно с выходом аналого-цифрового преобразователя и выходом сумматора, отличающееся тем, что введены первый аттенюатор, выход которого подключен к второму входу вычитателя, последовательно соединенные первые (М-1) дополнительных блоков памяти, выходы которых соединены со входами второго сумматора, выход которого через третий аттенюатор соединен с третьим входом вычитателя, при этом входы первого аттенюатора и первого из первых дополнительных блоков памяти подключены к выходу первого блока памяти, а также последовательно соединенные вторые (М-1) дополнительных блоков памяти, вход первого из которых подключен к выходу второго блока памяти и входу второго аттенюатора, подключенного к второму входу сумматора, выход последнего из которых подключен к входу пятого аттенюатора, выход которого, а также выходы остальных вторых (М-1) дополнительных блоков памяти подключены к входам третьего сумматора, выход которого через четвертый аттенюатор подключен к третьему входу первого сумматора, управляющий вход коммутатора подключен к входу одновибратора и четвертым входам второго блока памяти и вторых (М-1) дополнительных блоков памяти, а выход одновибратора подключен к четвертым входам первого блока памяти и первых (М-1) дополнительных блоков памяти, при этом управляющий сигнал коммутатора обнуляет второй блок памяти и вторые дополнительные (М-1) блоки памяти и приводит к срабатыванию одновибратора, который вырабатывает обнуляющий сигнал для первого блока памяти и первых (М-1) дополнительных блоков памяти.

| Устройство для разделения направлений передачи в дуплексных системах связи | 1983 |

|

SU1133675A1 |

| Адаптивный эхокомпенсатор | 1989 |

|

SU1665520A1 |

| Адаптивный эхокомпенсатор | 1987 |

|

SU1436277A1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1993 |

|

RU2039415C1 |

| РЕГУЛЯТОР ПОДАЧИ ВОЗДУХА | 0 |

|

SU231854A1 |

| US 5570423 А, 29.10.1996. | |||

Авторы

Даты

2004-02-10—Публикация

2001-05-22—Подача