Изобретение относится к технике связи и может быть использовано в системах дуплексной передачи сигналов.

Целью изобретения является повышение помехоустойчивости.

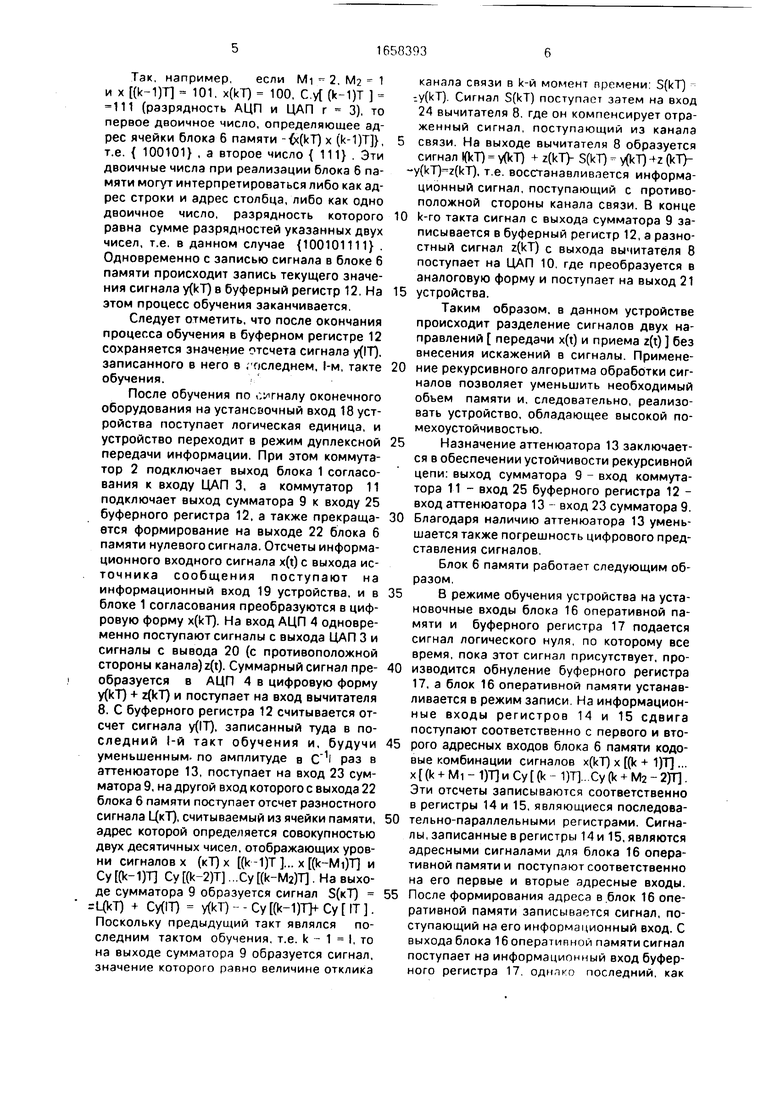

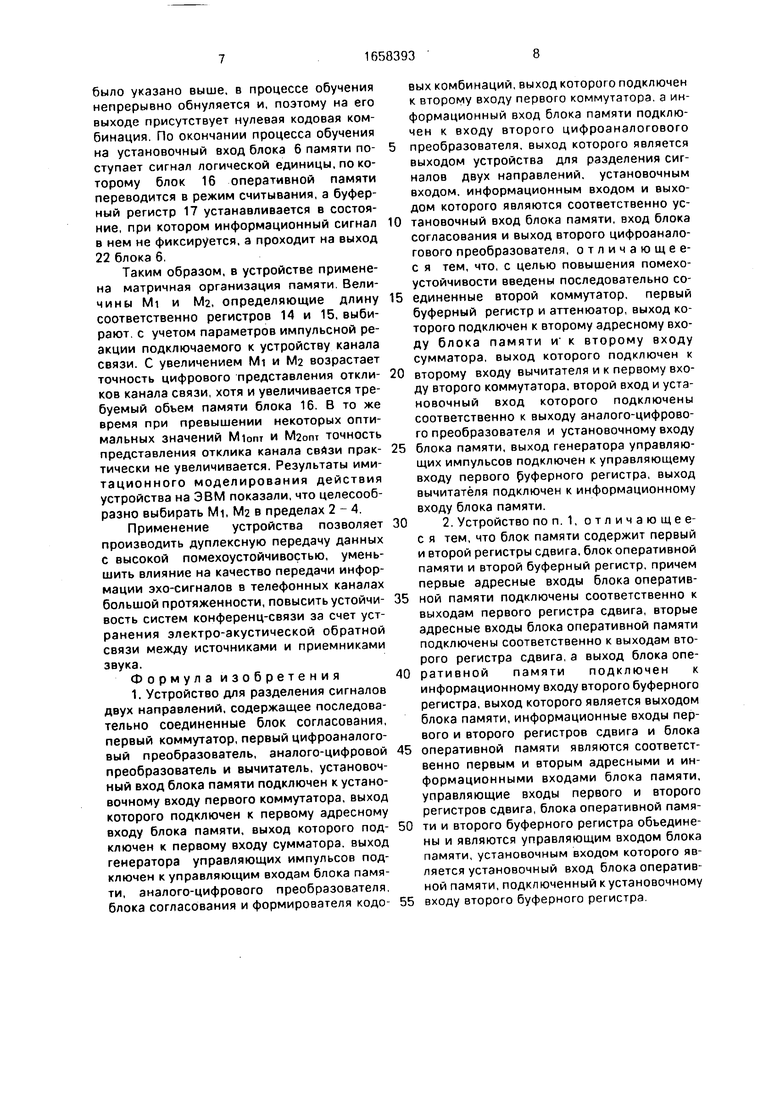

На фиг. 1 показана структурная схема устройства для разделения сигналов двух направлений; на фиг. 2 - структурная схема блока памяти устройства для разделения сигналов двух направлений.

Устройство для разделения сигналов двух направлений содержит блок 1 согласования, первый коммутатор 2, первый цифроаналоговый преобразователь 3, аналого-цифровой преобразователь 4, формирователь 5 кодог х комбинаций, блок 6 памяти, генератор 7 управляющих импульсов, вычитатель 8, сумматор 9, второй цифроаналоговый преобразователь 10, второй коммутатор 11, первый буферный регистр 12, аттенюатор 13, первый регистр 14 сдвига, второй регистр 15 сдвига, блок 16 оперативной памяти, второй буферный регистр 17, установочный вход 18, информационный вход 19, вывод 20 и выход 21 устройства для разделения сигналов двух направлений, выход 22 блока 6, вход 23 сумматора 9, вход 24 вычитателя 8, вход 25 буферного регистра 12.

Устройство для разделения сигналов двух направлений работает следующим образом.

К выводу 20 подключается канал связи. Процесс работы можно разбить на два этапа: процесс предварительной адаптации устройства к параметрам канала связи (процесс обучения) и процесс дуплексной передачи информации. Процесс обучения заключается в следующем. Сразу же после включения устройства все блоки, которые могут запоминать информацию (блок 6 памяти и буферный регистр 12), обнуляются. Затем по сигналу оконечного оборудования на установочный вход 18 поступает логический нуль. По данному сигналу коммутатор 2 подключает выход формирователя 5 к входу цифроаналогового преобразователя (ЦАП) 3; коммутатор 11 подключает выход аналого-цифрового преобразователя (АЦП) 4 к входу 25 буферного регистра 12; блок 6

памяти переводится в положение, при котором с его выхода 22 на вход сумматора 9 поступает кодовая комбинация, соответствующая нулевому сигналу. Формирователь

5 поочередно (в соответствии с поступающими на его вход сигналами от генератора 7) выдает в двоичной форме кодовые комбинации, соответствующие значениям (отсчетам) всех используемых для представления

сигнала источника сообщений уровней: х0,

XL X2 xiхп, х0.., которые циклически

повторяются. Эти отсчеты поступают на вход ЦАП 3, в котором преобразуются в аналоговую форму, и затем аналоговый сигнал

поступает на вход АЦП 4 и в канал связи. Кроме того, на вход АЦП 4 поступает также из канала связи отраженный сигнал, значение которого определяется импульсной реакцией канала связи. С выхода АЦП 4

цифровой сигнал у (kT) поступает на вход вычитателя 8 и через коммутатор 11 на вход 25 буферного регистра 12, с выхода которого считывается цифровой сигнал y(k-1)T, записанный в него в течение предыдущего

(k-1)-ro такта обучения. Этот сигнал в аттенюаторе 13 с коэффициентом передачи С уменьшается по амплитуде в раз и поступает на вход 23 сумматора 9. Поскольку на другой вход сумматора 9 поступаете выхода

22 блока 6 кодовая комбинация, соответствующая нулевому сигналу, то сигнал с входа 23, не изменяя своего значения, поступает на вход 24 вычитателя 8.

На выходе вычитателя 8 образуется сигнал разности текущего и предыдущего значений отклика канала связи ЦкТ) у(кТ) - -Су (k-1)T . который записывается в блок 6 памяти по адресу, определяемому совокупностью двух двоичных чисел, из которых первое представляет собой совокупность цифровых отсчетов сигнала на входе ЦАП 3 { х(кТ) х (k-1)T.,x (k-Mi) , а второе - совокупность цифровых отсчетов сигнала на выходе аттенюатора 13 { C.y(k-1)T С.у (k-2)T ...C.y (k-M2)T } , где ML M2 - количество отсчетов сигналов соответственно на входе ЦАП 3 и выходе аттенюатора 13. учитываемых при формировании адреса.

Так, например, если Mi - 2, Мг 1 х (k-1)T| - 101. x(kT) 100, С.у (k-1)T 111 (разрядность АЦП и ЦАП г 3), то ервое двоичное число, определяющее адес ячейки блока 6 памяти -&(kT) x (k-1), .е. { 100101} , а второе число { 111} . Эти воичные числа при реализации блока 6 паяти могут интерпретироваться либо как адрес строки и адрес столбца, либо как одно воичное число, разрядность которого равна сумме разрядностей указанных двух чисел, т.е. в данном случае {100101111} . Одновременно с записью сигнала в блоке 6 памяти происходит запись текущего значения сигнала у(кТ) в буферный регистр 12. На том процесс обучения заканчивается.

Следует отметить, что после окончания процесса обучения в буферном регистре 12 сохраняется значение отсчета сигнала y(IT). записанного в него в .оследнем. 1-м, такте обучения.

После обучения по сигналу оконечного оборудования на установочный вход 18 устройства поступает логическая единица, и устройство переходит в режим дуплексной передачи информации. При этом коммутатор 2 подключает выход блока 1 согласования к входу ЦАП 3, а коммутатор 11 подключает выход сумматора 9 к входу 25 буферного регистра 12, а также прекращается формирование на выходе 22 блока 6 памяти нулевого сигнала. Отсчеты информационного входного сигнала x(t) с выхода источника сообщения поступают на информационный вход 19 устройства, и в блохе 1 согласования преобразуются в цифровую форму х(кТ). На вход АЦП 4 одновременно поступают сигналы с выхода ЦАП 3 и сигналы с вывода 20 (с противоположной стороны канала) z(t). Суммарный сигнал преобразуется в АЦП 4 в цифровую форму у(кТ) + z(kT) и поступает на вход вычитателя 8. С буферного регистра 12 считывается отсчет сигнала y(IT), записанный туда в последний 1-й такт обучения и, будучи уменьшенным, по амплитуде в раз в аттенюаторе 13, поступает на вход 23 сумматора 9, на другой вход которого с выхода 22 блока 6 памяти поступает отсчет разностного сигнала ЦкТ), считываемый из ячейки памяти, адрес которой определяется совокупностью двух десятичных чисел, отображающих уровни сигналов х (к Т) х (k-1)T ... х (k-Mi)T и Су (k-1)T Су (k-2)T ...Су (k-Mz)T. На выходе сумматора 9 образуется сигнал 5(кТ) L(kT) + Су(ГП y(kT)--Cy(k-1). Поскольку предыдущий такт являлся последним тактом обучения, т.е. к - 1 I, то на выходе сумматора 9 образуется сигнал, значение которого равно величине отклика

канала связи в k-й момент премени: S(kT) - cy(kT). Сигнал S(kT) поступает затем на вход 24 вычитателя 8. где он компенсирует отраженный сигнал, поступающий из канала

связи. На выходе вычитателя 8 образуется сигнал KkT) y(kT) + z( S(kT) - y(kT) +z ( y(kT)-z(kT), т.е. восстанавливается информационный сигнал, поступающий с противоположной стороны канала связи. В конце

0 k-ro такта сигнал с выхода сумматора 9 записывается в буферный регистр 12, а разностный сигнал z(kT) с выхода вычитателя 8 поступает на ЦАП 10, где преобразуется в аналоговую форму и поступает на выход 21

5 устройства.

Таким образом, в данном устройстве происходит разделение сигналов двух направлений передачи x(t) и приема z(t) без внесения искажений в сигналы. Примене0 ние рекурсивного алгоритма обработки сигналов позволяет уменьшить необходимый объем памяти и, следовательно, реализовать устройство, обладающее высокой помехоустойчивостью.

5 Назначение аттенюатора 13 заключается в обеспечении устойчивости рекурсивной цепи: выход сумматора 9 - вход коммутатора 11 - вход 25 буферного регистра 12 - вход аттенюатора 13 - вход 23 сумматора 9.

0 Благодаря наличию аттенюатора 13 уменьшается также погрешность цифрового представления сигналов.

Блок 6 памяти работает следующим образом.

5 В режиме обучения устройства на установочные входы блока 16 оперативной памяти и буферного регистра 17 подается сигнал логического нуля, по которому все время, пока этот сигнал присутствует, про0 изводится обнуление буферного регистра 17, а блок 16 оперативной памяти устанавливается в режим записи, На информационные входы регистров 14 и 15 сдвига поступают соответственно с первого и вто5 рого адресных входов блока 6 памяти кодовые комбинации сигналов x(kT) х (k + 1)T... x(k + Mi-1))Т. Cy(k + M2-2)T. Эти отсчеты записываются соответственно в регистры 14 и 15, являющиеся последова0 тельно-параллельными регистрами. Сигналы, записанные в регистры 14 и 15, являются адресными сигналами для блока 16 оперативной памяти и поступают соответственно на его первые и вторые адресные входы.

5 После формирования адреса в блок 16 оперативной памяти записывается сигнал, поступающий на его информационный вход. С выхода блока 16 оперативной памяти сигнал поступает на информационный вход буферного регистра 17. однако последний, как

было указано выше, в процессе обучения непрерывно обнуляется и, поэтому на его выходе присутствует нулевая кодовая комбинация. По окончании процесса обучения на установочный вход блока 6 памяти поступает сигнал логической единицы, по которому блок 16 оперативной памяти переводится в режим считывания, а буферный регистр 17 устанавливается в состояние, при котором информационный сигнал в нем не фиксируется, а проходит на выход 22 блока б,

Таким образом, в устройстве применена матричная организация памяти Величины Mi и Мг, определяющие длину соответственно регистров 14 и 15. выбирают с учетом параметров импульсной реакции подключаемого к устройству канала связи. С увеличением Mi и М2 возрастает точность цифрового представления откликов канала связи, хотя и увеличивается требуемый объем памяти блока 16. В то же время при превышении некоторых оптимальных значений Mionr и М2опт точность представления отклика канала связи практически не увеличивается. Результаты имитационного моделирования действия устройства на ЭВМ показали, что целесообразно выбирать Mi, M2 в пределах 2-4.

Применение устройства позволяет производить дуплексную передачу данных с высокой помехоустойчивостью, уменьшить влияние на качество передачи информации эхо-сигналов в телефонных каналах большой протяженности, повысить устойчивость систем конференц-связи за счет устранения электро-акустической обратной связи между источниками и приемниками звука.

Формула изобретения

1. Устройство для разделения сигналов двух направлений, содержащее последовательно соединенные блок согласования, первый коммутатор, первый цифроаналого- вый преобразователь, аналого-цифровой преобразователь и вычитатель, установочный вход блока памяти подключен к установочному входу первого коммутатора, выход которого подключен к первому адресному входу блока памяти, выход которого подключен к первому входу сумматора, выход генератора управляющих импульсов подключен к управляющим входам блока памяти, аналого-цифрового преобразователя, блока согласования и формирователя кодовых комбинаций, выход которого подключен к второму входу первого коммутатора, а информационный вход блока памяти подключен к входу второго цифроаналогового

преобразователя, выход которого является выходом устройства для разделения сигналов двух направлений, установочным входом, информационным входом и выходом которого являются соответственно установочный вход блока памяти, вход блока согласования и выход второго цифроаналогового преобразователя, отличающее- с я тем, что, с целью повышения помехоустойчивости введены последовательно соединенные второй коммутатор, первый буферный регистр и аттенюатор, выход которого подключен к второму адресному входу блока памяти и к второму входу сумматора, выход которого подключен к

второму входу вычитателя и к первому входу второго коммутатора, второй вход и установочный вход которого подключены соответственно к выходу аналого-цифрового преобразователя и установочному входу

блока памяти, выход генератора управляющих импульсов подключен к управляющему входу первого буферного регистра, выход вычитателя подключен к информационному входу блока памяти.

2. Устройство поп.1, отличающее- с я тем, что блок памяти содержит первый и второй регистры сдвига, блок оперативной памяти и второй буферный регистр, причем первые адресные входы блока оперативной памяти подключены соответственно к выходам первого регистра сдвига, вторые адресные входы блока оперативной памяти подключены соответственно к выходам второго регистра сдвига, а выход блока оперативной памяти подключен к информационному входу второго буферного регистра, выход которого является выходом блока памяти, информационные входы первого и второго регистров сдвига и блока

оперативной памяти являются соответственно первым и вторым адресными и информационными входами блока памяти, управляющие входы первого и второго регистров сдвига, блока оперативной памяти и второго буферного регистра обьедине- ны и являются управляющим входом блока памяти, установочным входом которого является установочный вход блока оперативной памяти, подключенный к установочному

входу второго буферного регистра

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения направлений передачи в дуплексных системах связи | 1989 |

|

SU1672575A2 |

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1332542A2 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1992 |

|

RU2038702C1 |

| Устройство для кодирования аналоговых сигналов | 1985 |

|

SU1316091A1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2001 |

|

RU2223599C2 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1987 |

|

SU1483647A2 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНАЛОВ ПЕРЕДАЧИ В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 2001 |

|

RU2233553C2 |

| Устройство разделения направлений передачи в дуплексных системах связи | 1988 |

|

SU1570001A1 |

Изобретение относится к технике связи и может быть использовано в системах дуплексной передачи сигналов. Целью изобретения является повышение помехоустойчивости устройства. Устройство содержит блок 1 согласования, коммутатор 2, цифроаналоговый преобразователь (ЦАП)

| Устройство для разделения направлений передачи в дуплексных системах связи | 1983 |

|

SU1133675A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-06-23—Публикация

1989-07-11—Подача