Изобретение относится к области импульсной техники и может быть использовано в устройствах вычислительной техники и систем управления.

Известна ячейка памяти (см. а. с. СССР 1706362 от 02.04.90, МКИ Н 03 К 3/037, "Триггерное устройство", Еремин А.Н., Шишкин Г.И., опубл. 28.08.97, Бюл. 24), содержащая D-триггер, первый, второй и третий элементы ИЛИ-НЕ, элемент И-НЕ, двунаправленный ключ, резистор и конденсатор. Один из выводов резистора через конденсатор подключен к общей шине. Первый и второй входы первого элемента ИЛИ-НЕ соединены соответственно с первым установочным входом устройства и выходом второго элемента ИЛИ-НЕ. Первый и второй входы второго элемента ИЛИ-НЕ соединены соответственно со вторым установочным входом устройства и прямым выходом D-триггера. Тактовый вход D-триггера соединен с выходом третьего элемента ИЛИ-НЕ, первый и второй входы которого соединены с первыми входами соответственно первого и второго элементов ИЛИ-НЕ. Выход двунаправленного ключа соединен с информационным входом D-триггера и другим выводом резистора, вход - с выходом первого элемента ИЛИ-НЕ, а управляющий вход - с выходом элемента И-НЕ. Первый и второй входы элемента И-НЕ соединены соответственно с выходом третьего элемента ИЛИ-НЕ и с дополнительным входом устройства.

Недостатком указанной ячейки памяти является малый объем хранимой информации.

Известна ячейка памяти (см. патент РФ 2042268 от 28.06.91, МКИ Н 03 К 23/64, "Счетчик импульсов в коде Грея", Дикарев И.И., Шишкин Г.И., опубл. 20.08.95, Бюл. 23), содержащая разряды с нулевого по N-ый, последовательные RC-цепи по числу разрядов, демультиплексор, два коммутатора и в каждом разряде - асинхронный D-триггер и мультиплексор, содержащий два двунаправленных ключа и элемент ИЛИ-НЕ, входы которого являются адресными входами мультиплексора. В каждом разряде выходы двунаправленных ключей соединены с входом триггера и с соответствующим входом первого коммутатора, выход которого соединен с выходом второго коммутатора, входы которого соединены с первыми выводами соответствующих RC-цепей, вторые выводы которых соединены с общей шиной. Вход демультиплексора соединен с первой входной шиной, адресные входы - со второй входной шиной и с соответствующими адресными входами коммутаторов, а выходы - с первыми входами элементов ИЛИ-НЕ соответствующих разрядов, второй вход элемента ИЛИ-НЕ каждого разряда соединен с управляющим входом первого двунаправленного ключа и является входом разрешения записи информации, а выход соединен с управляющим входом второго двунаправленного ключа, вход которого соединен с прямым выходом триггера. Информация на второй входной шине изменяется при поступлении сигнала по первой входной шине. Вход первого двунаправленного ключа является информационным входом разряда ячейки памяти.

Ячейка памяти является наиболее близкой по технической сущности к заявленному устройству и взята в качестве прототипа.

Недостатком прототипа является сложность устройства.

Задачей, решаемой предлагаемым изобретением, является создание ячейки памяти с более простой схемной реализацией при увеличении надежности в режиме хранения памяти.

Технический результат достигается тем, что в ячейку памяти содержащую коммутатор, N последовательных RC-цепей, первые выводы которых соединены с соответствующими входами коммутатора, а вторые выводы - с общей шиной, асинхронный D-триггер, два двунаправленных ключа, выход первого из которых соединен со входом второго двунаправленного ключа и входом асинхронного D-триггера, прямой вход которого соединен с выходом второго двунаправленного ключа, управляющий вход которого соединен с выходом первого логического элемента ИЛИ-рого соединен с выходом первого логического элемента ИЛИ-НЕ. Новым является то, что дополнительно введены мультиплексор, счетчик импульсов, два синхронных D-триггера, два логических элемента ИЛИ-НЕ, выход второго логического элемента ИЛИ-НЕ является выходом данных ячейки памяти, а первый вход соединен с инверсным выходом асинхронного D-триггера, вход которого соединен с выходом коммутатора, управляющие входы которого соединены с соответствующими выходами мультиплексора, первые два входа которого соединены с соответствующими выходами счетчика импульсов, а два других входа мультиплексора являются адресными входами ячейки памяти, вход счетчика импульсов соединен с первым входом первого логического элемента ИЛИ-НЕ, С-входами первого и второго синхронных D-триггеров, прямые выходы которых соединены соответственно с первым и вторым входами третьего логического элемента ИЛИ-НЕ, выход которого соединен с управляющим входом мультиплексора и является стробирующим выходом ячейки памяти, инверсный выход второго из синхронных D-триггера соединен со вторым входом второго логического элемента ИЛИ-НЕ, прямой выход первого из синхронных D-триггеров соединен с вторым входом первого логического элемента ИЛИ-НЕ и управляющим входом первого двунаправленного ключа, вход которого является входом данных ячейки памяти, информационные входы первого и второго синхронных D-триггеров являются соответственно входами записи и считывания.

Указанная совокупность признаков позволяет упростить ячейку памяти при увеличении надежности в режиме хранения данных путем введения счетчика импульсов и мультиплексора.

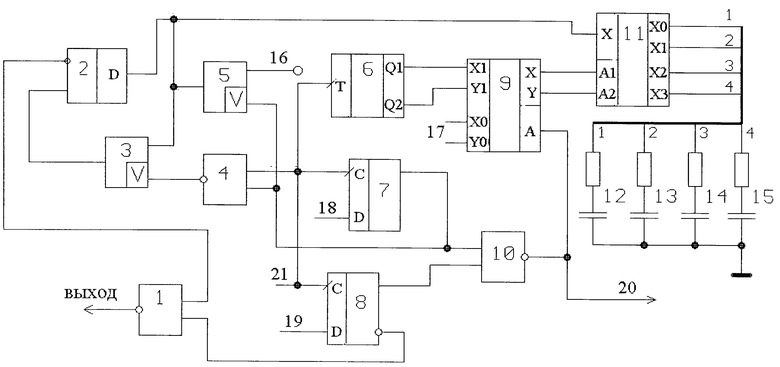

На чертеже приведена электрическая принципиальная схема ячейки памяти.

Ячейка памяти содержит логический элемент ИЛИ-НЕ 1, асинхронный D-триггер 2, двунаправленный ключ 3, логический элемент ИЛИ-НЕ 4, двунаправленный ключ 5, счетчик импульсов 6, синхронные D-триггеры 7, 8, мультиплексор 9, логический элемент ИЛИ-НЕ 10, коммутатор 11, последовательные RC-цепи 12-15, вход данных 16, шину адреса 17, входы записи и считывания 18, 19, стробирующий выход 20, синхронизирующий вход 21 и выход. Первые выводы последовательных RC-цепей 12-15 соединены с соответствующими выводами коммутатора 11, а вторые - с общей шиной. Вход данных 16 соединен с входом двунаправленного ключа 5, выход которого соединен с выходом коммутатора 11, входом асинхронного D-триггера 2 и выходом двунаправленного ключа 3, прямой выход асинхронного D-триггера 2 соединен с входом двунаправленного ключа 3, управляющий вход которого соединен с выходом логического элемента ИЛИ-НЕ 4, первый вход которого соединен с входом счетчика импульсов 6, С-входами двух синхронных D-триггеров 7, 8 и входом синхронизации 21 ячейки памяти, прямые выходы синхронных D-триггеров 7, 8 соединены с первым и вторым входами логического элемента ИЛИ-НЕ 10 соответственно, выход которого соединен с управляющим входом мультиплексора 9 и является стробирующим выходом 20 ячейки памяти. Инверсные выходы асинхронного D-триггера 2 и синхронного D-триггера 8 соединены соответственно с первым и вторым входами логического элемента ИЛИ-НЕ 1, выход которого является выходом ячейки памяти, первый вход логического элемента ИЛИ-НЕ 10 соединен со вторым входом элемента ИЛИ-НЕ 4 и управляющим входом двунаправленного ключа 5. Информационные входы синхронных D-триггеров 7, 8 являются соответственно входами записи 18 и считывания 19 ячейки памяти.

В качестве элементной базы устройства выбрана серия 564, выполненная по КМОП-технолоии.

Ячейка памяти работает следующим образом.

Ячейка памяти имеет режим записи данных, режим считывания данных и режим хранения, в котором происходит динамическая регенерация данных.

В режиме записи данные поступают на вход двунаправленного ключа 5 через вход данных 16, а сигнал логической "1", разрешающий запись, поступает на вход данных синхронного D-триггера 7 через вход записи 18. По фронту синхросигнала, поступающего на синхронизирующий вход 21 ячейки памяти, на выходе синхронного D-триггера 7 появляется сигнал логической "1", который поступает на второй вход логического элемента ИЛИ-НЕ 4, на выходе которого появляется сигнал логического "0", который закрывает двунаправленный ключ 3, что приводит к отключению входа D-триггера 2 от его прямого выхода. Сигнал логической "1" с выхода синхронного D-триггера 7 также поступает на управляющий вход двунаправленного ключа 5, в результате чего данные с входа данных 16 ячейки памяти поступают на вход Х коммутатора 11 (он же выход). Этот же логический сигнал с выхода синхронного D-триггера 7 поступает и на первый вход логического элемента ИЛИ-НЕ 10, на выходе которого образуется сигнал логического "0", который поступает на стробирующий выход 20 ячейки памяти и управляющий вход мультиплексора 9, в результате его выходы X, Y подключаются к адресной шине 17, комбинация сигналов на которой определяет адрес разряда ячейки памяти, в которую происходит запись данных.

В режиме считывания на вход данных синхронного D-триггера 8 через вход считывания 19 поступает сигнал логической "1". По фронту сигнала синхронизации, поступающего на вход 21 ячейки памяти, на прямом выходе синхронного D-триггера 8 появляется сигнал логической "1", который поступает на второй вход логического элемента ИЛИ-НЕ 10, после чего устанавливается адрес ячейки памяти, из которой происходит считывание данных, аналогично режиму записи данных. Данные поступают с выхода Х коммутатора 11 на вход асинхронного D-триггера 2, с инверсного выхода которого данные поступают на первый вход логического элемента ИЛИ-НЕ 1. С инверсного выхода синхронного D-триггера 8 на второй вход логического элемента ИЛИ-НЕ 1 поступает сигнал логического "0", после чего данные поступают на выход ячейки памяти.

В режиме хранения на входах записи 18 и считывания 19 присутствуют уровни логического "0", а на вход синхронизации 21 подается синхроимпульс, что приводит к появлению на выходе логического элемента ИЛИ-НЕ 10 уровня логической "I", который поступает на управляющей вход мультиплексора 9. Его выходы Х и Y подключаются к входам XI и Y1 соответственно, и счетчик импульсов 6 производит последовательный перебор адресов разрядов ячейки памяти. По фронту синхросигнала на входе синхронизации 21 ячейки памяти соответственно происходит изменение адреса разряда устройства и через логический элемент ИЛИ-НЕ 4 и двунаправленный ключ 3 отключается вход асинхронного D-триггера 2 от его прямого выхода. Информация, хранимая разрядом устройства с выбранным адресом (регенерируемый разряд) появляется на выходе Х коммутатора 11. Данные с прямого выхода асинхронного D-триггера 2 поступают на вход двунаправленного ключа 3, при окончании синхроимпульса на выходе логического элемента ИЛИ-НЕ 4 образуется сигнал логической "1", в результате чего замыкается двунаправленный ключ 3 и регенерированные данные поступают снова на вход Х коммутатора 11 и далее в выбранный разряд ячейки памяти.

Частота синхроимпульсов, поступающих на вход синхронизации 21 ячейки памяти должна быть такой, чтобы в режиме хранения состояние разрядов ячейки памяти сохранялись в интервалах между синхроимпульсами (конденсаторы RC-цепей 12-15 должны сохранять свой заряд).

Изготовлен лабораторный макет ячейки памяти, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ | 2002 |

|

RU2222100C2 |

| ЯЧЕЙКА ПАМЯТИ | 2001 |

|

RU2214037C2 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2042268C1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2110146C1 |

| СИСТЕМА ПЕРЕДАЧИ И ОБРАБОТКИ СИГНАЛОВ О СОСТОЯНИИ ОБЪЕКТОВ | 1994 |

|

RU2087036C1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

Изобретение относится к области импульсной техники и может быть использовано в устройствах вычислительной техники и систем управления. Техническим результатом является увеличение надежности в режиме хранения памяти. Устройство содержит коммутатор, N последовательных RC-цепей, асинхронный D-триггер, два двунаправленных ключа, три логических элемента ИЛИ-НЕ, мультиплексор, счетчик импульсов, два синхронных D-триггера. 1 ил.

Ячейка памяти, содержащая коммутатор, N последовательных RC-цепей, первые выводы которых соединены с соответствующими выводами коммутатора, а вторые выводы - с общей шиной, асинхронный D-триггер, два двунаправленных ключа, выход первого из которых соединен со входом второго двунаправленного ключа и входом асинхронного D-триггера, прямой выход которого соединен с входом второго двунаправленного ключа, управляющий вход которого соединен с выходом первого логического элемента ИЛИ-НЕ, отличающаяся тем, что дополнительно введены мультиплексор, счетчик импульсов, два синхронных D-триггера, два логических элемента ИЛИ-НЕ, выход второго логического элемента ИЛИ-НЕ является выходом данных ячейки памяти, а первый вход соединен с инверсным выходом асинхронного D-триггера, вход которого соединен с выходом коммутатора, управляющие входы которого соединены с соответствующими выходами мультиплексора, первые два входа которого соединены с соответствующими выходами счетчика импульсов, а два других входа мультиплексора являются адресными входами ячейки памяти, вход счетчика импульсов соединен с первым входом первого логического элемента ИЛИ-НЕ, С-входами первого и второго синхронных D-триггеров, прямые выходы которых соединены соответственно с первым и вторым входами третьего логического элемента ИЛИ-НЕ, выход которого соединен с управляющим входом мультиплексора и является стробирующим выходом ячейки памяти, инверсный выход второго из синхронных D-триггера соединен со вторым входом второго логического элемента ИЛИ-НЕ, прямой выход первого из синхронных D-триггеров соединен с вторым входом первого логического элемента ИЛИ-НЕ и управляющим входом первого двунаправленного ключа, вход которого является входом данных ячейки памяти, информационные входы первого и второго синхронных D-триггеров являются соответственно входами записи и считывания.

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2042268C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1990 |

|

SU1706362A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО МАГАЗИННОГО ТИПА | 1991 |

|

RU2081459C1 |

| US 4805139 A, 14.02.1989 | |||

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

Авторы

Даты

2004-02-20—Публикация

2002-02-26—Подача