Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известен триггер [1] содержащий статический триггер, выполненный на логических элементах, два магнитных сердечника с прямоугольной петлей гистерезиса, управляющие обмотки которых включены в соответствующие плечи триггера и содержащие подмагничивающие обмотки. Входы логических элементов, соединенные с управляющими обмотками, через резистор подключены к источнику питания. Подмагничивающая обмотка каждого сердечника включена последовательно с управляющей обмоткой другого сердечника. Выходы логических элементов через соответствующие диоды соединены с источником питания.

Недостатками данного триггера являются сложность, связанная с наличием двух магнитных сердечников, двух резисторов и двух диодов, и большая потребляемая мощность, так как схема потребляет большой ток в режиме хранения информации.

Наиболее близкой к предлагаемому изобретению по технической сущности является энергонезависимая ячейка памяти [2] содержащая сердечник с прямоугольной петлей гистерезиса (ППГ) и обмоткой, логические элементы, триггер и резистор. Средняя точка обмотки сердечника соединена с одним выводом резистора, конец обмотки подключен к выходу первого логического элемента, начало к одному из входов второго логического элемента, второй вход которого подключен к шине разрешения, а выход к единичному входу триггера. Нулевой вход триггера подключен к шине сброса, счетный вход к информационной шине, а прямой и инверсный выходы к входам первого и третьего логических элементов соответственно, вторые входы которых подключены к шине перемагничивания. Другой вывод резистора подключен к источнику питания. Выход третьего логического элемента соединен с началом обмотки сердечника. Логические элементы выполнены в виде элементов И-НЕ.

Недостатком указанной ячейки памяти является сложность схемы, связанная с необходимостью использования счетного триггера, содержащего большое число элементов (Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. М. Советское радио, 1975, с.71, рис.2,18а).

Цель изобретения упрощение схемы.

Для этого в энергонезависимую ячейку памяти, содержащую сердечник с прямоугольной петлей гистерезиса и обмоткой, средняя точка которой соединена с одним выводом резистора, конец с выходом первого логического элемента, начало с первым входом второго логического элемента, второй вход которого подключен к шине разрешения, а также третий логический элемент, информационную и выходную шины и шину сброса, введена шина опроса, а во второй логический элемент третий вход, подключенный к шине сброса и одному из входов третьего логического элемента, другой вход которого соединен с шиной опроса, а выход с другим выводом резистора, первый вход первого логического элемента соединен с выходом второго логического элементе и выходной шиной, а второй вход с информационной шиной, при этом логические элементы выполнены в виде элементов ИЛИ-НЕ.

Указанная совокупность признаков позволяет упростить схему энергонезависимой ячейки памяти за счет включения обмотки сердечника в цепь обратной связи RS-триггера, построенного на первом и втором логических элементах, что приводит к уменьшению схемных затрат путем исключения счетного триггера.

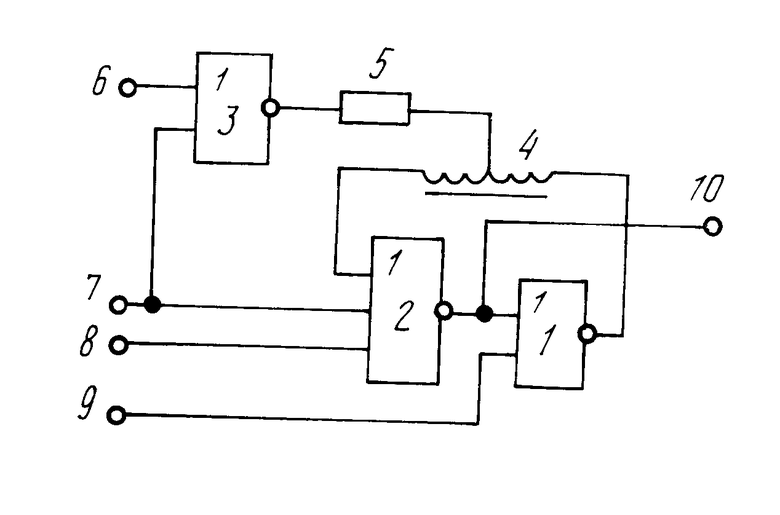

На чертеже приведена схема энергонезависимой ячейки памяти.

Энергонезависимая ячейка памяти содержит первый 1, второй 2 и третий 3 элементы ИЛИ-НЕ, сердечник 4 с ППГ и обмоткой, резистор 5, шину 6 опроса, шину 7 сброса, шину 8 разрешения, информационную 9 и выходную 10 шины. Средняя точка обмотки сердечника 4 через резистор 5 соединена с выходом элемента ИЛИ-НЕ 3, конец обмотки подключен к выходу элемента ИЛИ-НЕ 1, а начало к первому входу элемента ИЛИ-НЕ 2, второй вход которого соединен с шиной 8 разрешения. Третий вход элемента ИЛИ-НЕ 2 соединен с шиной 7 сброса и первым входом элемента ИЛИ-НЕ 3, второй вход которого соединен с шиной 6 опроса. Выход элемента ИЛИ-НЕ 2 соединен с выходной шиной 10 и первым входом элемента ИЛИ-НЕ 1, второй вход которого соединен с информационной шиной 9.

Энергонезависимая ячейка памяти работает следующим образом.

В режиме хранения информации на шинах опроса 6, сброса 7, информационной 9 и выходной 10 присутствуют уровни логического "0", а на шине 9 разрешения уровень логической "1". Обмотка сердечника 4 обесточена, и сердечник 4 сохраняет записанную в нем информацию.

Перемагничивание сердечника 4 в состояние логического "0" осуществляется подачей уровня логической "1" на шину 7 сброса. При этом на выходе элемента ИЛИ-НЕ 3 появляется уровень логического "0" и сердечник 4 перемагничивается в состояние логического "0" током, протекающим с выхода элемента ИЛИ-НЕ 1 через обмотку сердечника 4 и резистор 5 на выход элемента ИЛИ-НЕ 3.

Перемагничивание сердечника 4 в состояние логической "1" осуществляется подачей уровня логической "1" на информационную шину 9. При этом на выходе элемента ИЛИ-НЕ 1 появляется уровень логического "0" и сердечник 4 перемагничивается в состояние логической "1" током, протекающим с выхода элемента ИЛИ-НЕ 3 через резистор 5 и обмотку сердечника 4 на выход элемента ИЛИ-НЕ 1.

Считывание информации, записанной в сердечник 4, осуществляется следующим образом. На шину 6 опроса подается уровень логической "1". При этом на выходе элемента ИЛИ-НЕ 3 появляется уровень логического "0" и начинает протекать ток с выхода элемента ИЛИ-НЕ 1 через обмотку сердечника 4 и резистор 5 на выход элемента ИЛИ--НЕ 3, который перемагничивает сердечник 4 в состояние логического "0". В начале обмотки сердечника 4 появится сигнал с уровнем логического "0", который представляет собой короткую (около 1 мкс) помеху, связанную с непрямоугольностью петли гистерезиса, если сердечник 4 был намагничен в состояние логического "0", или сигнал нормальной длительности (около 20 мкс), если сердечник 4 был намагничен в состояние логической "1". С задержкой (5 мкс) относительно подачи на шину 6 опроса уровня логической "1" на шину 8 разрешения подается уровень логического "0". Если в сердечнике 4 был записан логический "0", то к этому моменту времени помеха от непрямоугольности петли гистерезиса в начале обмотки сердечника 4 закончится, с выхода элемента ИЛИ-НЕ 1 через обмотку сердечника 4 на первый вход элемента ИЛИ-НЕ 2 будет поступать уровень логической "1", а на выходной шине 10 сохранится уровень логического "0". Если в сердечнике 4 была записана логическая "1", то к этому моменту времени сигнал логического "0" в начале обмотки сердечника 4 сохранится, на выходе элемента ИЛИ-НЕ 2 и на выходной шине 10 появится уровень логической "1", а на выходе элемента ИЛИ-НЕ 1 уровень логического "0". При этом обмотка сердечника 4 окажется обесточенной и уровень логического "0" с выхода элемента ИЛИ-НЕ 1 будет через обмотку сердечника 4 поступать на вход элемента ИЛИ-НЕ 2, удерживая на выходной шине 10 уровень логической "1".

В режиме хранения информации в сердечнике устройство может быть отключено от источника питания.

Таким образом, энергонезависимая ячейка памяти выполняет функции сброса, записи, считывания и хранения информации в магнитном сердечнике при меньших, чем у прототипа, схемных затратах.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1991 |

|

RU2036547C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 2002 |

|

RU2230427C2 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207717C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1992 |

|

RU2040113C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1780487A1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

SU1811353A1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207718C1 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

Использование: изобретение относится к импульсной технике. Цель изобретения - упрощение схемы. Сущность изобретения: энергонезависимая ячейка памяти содержит 3 элемента ИЛИ-НЕ (1 - 3), сердечник 4 с прямоугольной петлей гистерезиса и обмоткой, резистор 5, шину 6 опроса, шину 7 сброса, шину 8 разрешения, информационную 9 и выходную 10 шины. 1 ил.

ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ, содержащая сердечник с прямоугольной петлей гистерезиса и обмоткой, средняя точка которой соединена с одним выводом резистора, конец подключен к выходу первого логического элемента, начало к первому входу второго логического элемента, второй вход которого подключен к шине разрешения, а также третий логический элемент, информационную и выходную шины и шину сброса, отличающаяся тем, что, с целью упрощения, в нее введена шина опроса, а во второй логический элемент третий вход, соединенный с шиной сброса и одним из входов третьего логического элемента, другой вход которого соединен с шиной опроса, выход с другим выводом резистора, первый вход первого логического элемента соединен с выходом второго логического элемента и выходной шиной, второй вход с информационной шиной, при этом логические элементы выполнены в виде элементов ИЛИ НЕ.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Энергонезависимая ячейка памяти | 1979 |

|

SU845287A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-04-30—Публикация

1991-06-05—Подача