Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др.

Известны реляторные модули (см., например, патент РФ 2188453, кл. G06G 7/25, 2002 г.), которые обеспечивают выбор минимального или максимального из трех входных аналоговых сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных реляторных модулей, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется выбор медианного из трех входных аналоговых сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип реляторный модуль (патент РФ 2195701, кл. G06G 7/25, 2002 г.), который содержит реляторы и обеспечивает выбор минимального, медианного или максимального из трех входных аналоговых сигналов. При этом максимальное время задержки распространения сигнала в прототипе равно 2τр, где τр есть время задержки релятора.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся большие аппаратурные затраты, обусловленные тем, что прототип содержит шесть реляторов.

Техническим результатом изобретения является уменьшение аппаратурных затрат при сохранении функциональных возможностей и быстродействия прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в реляторном модуле, содержащем четыре релятора, каждый из которых содержит компаратор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, размыкающий и замыкающий ключи, причем первый и второй компараторные входы релятора образованы соответственно неинвертирующим и инвертирующим входами компаратора, подключенного выходом к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является входом управления релятора, а выход соединен с управляющим входом размыкающего и замыкающего ключей, входы которых образуют соответственно первый и второй переключательные входы релятора, а выходы являются соответственно первым и вторым выходами релятора, вход управления четвертого релятора и объединенные входы управления первого, второго, третьего реляторов соединены соответственно с первым и вторым входами управления реляторного модуля, выходы j-го

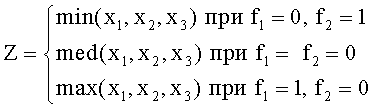

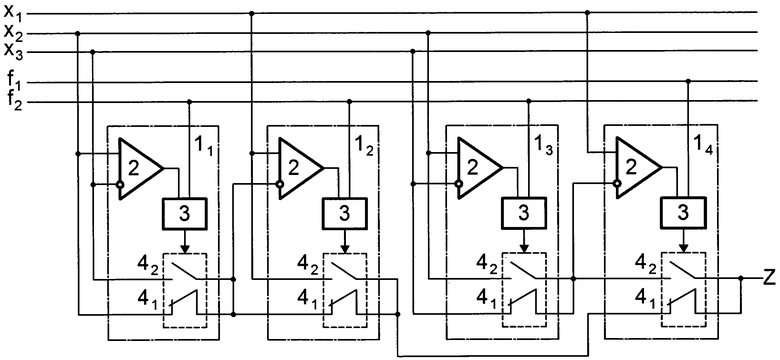

На чертеже представлена схема предлагаемого реляторного модуля.

Реляторный модуль содержит реляторы 11, …, 14. Каждый релятор содержит компаратор 2, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, размыкающий и замыкающий ключи 41 и 42, причем первый и второй компараторные входы релятора образованы соответственно неинвертирующим и инвертирующим входами компаратора 2, подключенного выходом к первому входу элемента 3, второй вход которого является входом управления релятора, а выход соединен с управляющим входом ключей 41 и 42, входы которых образуют соответственно первый и второй переключательные входы релятора, а выходы являются соответственно первым и вторым выходами релятора. Вход управления релятора 14 и объединенные входы управления реляторов 11, 12, 13 соединены соответственно с первым и вторым входами управления реляторного модуля, к выходу которого подключены выходы релятора 14, первый выход релятора 11 соединен с первым переключательным входом релятора 12, второй переключательный и первый компараторный входы которого объединены, первые и вторые компараторные входы реляторов 11, 13 подключены соответственно к второму и третьему входам реляторного модуля, первый вход которого соединен с первыми компараторными входами реляторов 12, 14, первый и второй компараторные входы релятора 11 (13) соединены соответственно с его первым (вторым) и вторым (первым) переключательными входами, второй компараторный вход релятора 1i(i∈{2,4}) соединен с выходами релятора 1i-1, а выходы релятора 12 соединены с первым переключательным входом релятора 14, подсоединенного вторым переключательным входом к выходам релятора 13.

Работа предлагаемого реляторного модуля осуществляется следующим образом. На его первый, второй и третий входы подаются соответственно аналоговые сигналы (напряжения) x1, x2 и x3; на его первом, втором входах управления фиксируются соответственно необходимые управляющие сигналы f1, f2∈{0,1}. Если на входе управления релятора присутствует лог. «0» (лог.«1») и сигнал на его первом компараторном входе больше либо меньше сигнала на его втором компараторном входе, то ключ 41 соответственно разомкнут (замкнут) либо замкнут (разомкнут), а ключ 42 соответственно замкнут (разомкнут) либо разомкнут (замкнут). В представленной ниже таблице приведены все возможные варианты упорядочения сигналов x1, x2, x3, и соответствующие этим вариантам значения сигнала Z на выходе предлагаемого реляторного модуля при некоторых комбинациях значений сигналов f1 и f2. С учетом данных, приведенных в таблице, операция, воспроизводимая предлагаемым модулем, определяется выражением:

При этом максимальное время задержки распространения сигнала в предлагаемом модуле равно 2τр, где τр есть время задержки релятора.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый реляторный модуль обеспечивает выбор минимального, медианного или максимального из трех входных аналоговых сигналов, имеет быстродействие прототипа и обладает меньшими по сравнению с ним аппаратурными затратами.

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др. Техническим результатом изобретения является уменьшение аппаратурных затрат при сохранении функциональных возможностей и быстродействия. Реляторный модуль предназначен для выбора минимального, медианного или максимального из трех входных аналоговых сигналов и может быть использован в системах аналоговой вычислительной техники как средство предварительной обработки информации. Реляторный модуль содержит четыре релятора (11, …, 14), каждый из которых содержит компаратор (2), элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (3), размыкающий и замыкающий ключи (41 и 42). 1 ил., 1 табл.

Реляторный модуль, предназначенный для выбора минимального, медианного или максимального из трех входных аналоговых сигналов, содержащий четыре релятора, каждый из которых содержит компаратор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, размыкающий и замыкающий ключи, причем первый и второй компараторные входы релятора образованы соответственно неинвертирующим и инвертирующим входами компаратора, подключенного выходом к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является входом управления релятора, а выход соединен с управляющим входом размыкающего и замыкающего ключей, входы которых образуют соответственно первый и второй переключательные входы релятора, а выходы являются соответственно первым и вторым выходами релятора, вход управления четвертого релятора и объединенные входы управления первого, второго, третьего реляторов соединены соответственно с первым и вторым входами управления реляторного модуля, выходы j-го (

| РЕЛЯТОРНЫЙ МОДУЛЬ | 2001 |

|

RU2195701C1 |

| РЕЛЯТОРНЫЙ МОДУЛЬ | 2011 |

|

RU2445697C1 |

| US 5642070, 24.06.1997 | |||

| МЕТАЛЛОПОРИСТЫЙ ПРОПИТАННЫЙ КАТОД ДЛЯ МАГНЕТРОНА | 2007 |

|

RU2342732C1 |

| JP 59221770 A, 13.12.1984. | |||

Авторы

Даты

2013-08-20—Публикация

2012-07-03—Подача