Изобретение относится к аналоговой вычислительной технике, к электронным устройствам автоматики и систем управления и может быть использовано для параллельного воспроизведения бинарных операций комплементарной алгебры - КА-конъюнкции и КА-дизъюнкции, для взвешенного суммирования и воспроизведения среднего значения двух аналоговых сигналов и др.

Известны коммутаторные схемы, построенные на ключах со скрещенным соединением двух из четырех ключей (см., например, Шестаков В.И. Алгебра коммутаторных схем // Синтез релейных структур: Труды международного симпозиума. - М.: Наука, 1965, с. 87-96, рис. 2, 3 и др.).

Известные коммутаторы воспроизводят только одну функцию - операцию инверсии разности двух аналоговых сигналов, что существенно ограничивает их функциональные возможности.

Наиболее близким к предложенному схемному решению является коммутационный релятор, построенный на четырех ключах с перекрестным соединением двух последовательно соединенных однотипных ключей, в котором управление состоянием ключей (замкнут, разомкнут) осуществляется от компаратора, на первый и второй входы которого подаются управляющие аналоговые напряжения (см. Волгин Л.И. Логико-алгебраические модели электрических цепей, содержащих реляторные коммутаторы // Математические методы и модели: Труды международной конференции. - Ульяновск: УлГТУ. Т. 3, с. 85-88, рис. 1).

Недостатком прототипа является ограниченные функциональные возможности.

Технический результат - расширение функциональных возможностей за счет увеличения числа воспроизводимых операций.

Технический результат достигается тем, что в коммутационный релятор, содержащий компаратор, выход которого соединен с управляющими входами первого, второго, третьего и четвертого ключей, введены первый, второй, третий и четвертый резисторы, выходные выводы которых соединены соответственно с входными выводами первого, второго, третьего и четвертого ключей, входные выводы первого и второго резисторов соединены и образуют первый переключательный вход коммутационного релятора, входные выводы третьего и четвертого резисторов соединены и образуют второй переключательный вход коммутационного релятора.

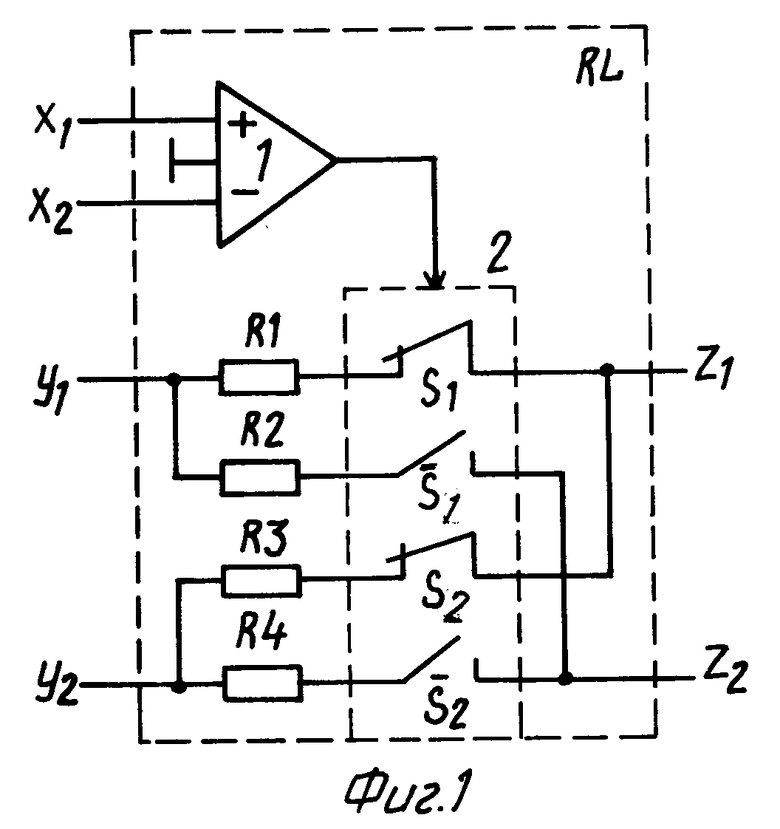

Схема коммутационного релятора изображена на фиг. 1. Здесь 1 есть компаратор, на неинвертирующий и инвертирующий входы которого подаются управляющие напряжения x1 и x2; 2 - группа четырех ключей, содержащая первый замыкающий S, второй размыкающий  третий замыкающий S2 и четвертый размыкающий

третий замыкающий S2 и четвертый размыкающий  ключи; R1, R2, R3 и R2 - соответственно первый, второй, третий и четвертый резисторы с сопротивлениями R1, R2, R3 и R4.

ключи; R1, R2, R3 и R2 - соответственно первый, второй, третий и четвертый резисторы с сопротивлениями R1, R2, R3 и R4.

Схема содержит базовый релятор, содержащий компаратор 1 и группу ключей 2, состоящую из первого замыкающего S1, второго размыкающего  третьего замыкающего S2 и четвертого размыкающего

третьего замыкающего S2 и четвертого размыкающего  ключей. Управляющие входы всех ключей присоединены к выходу компаратора 1, неинвертирующий и инвертирующий входы которого являются соответственно первым и вторым компараторными входами коммутационного релятора.

ключей. Управляющие входы всех ключей присоединены к выходу компаратора 1, неинвертирующий и инвертирующий входы которого являются соответственно первым и вторым компараторными входами коммутационного релятора.

К входным выводам первого, второго, третьего и четвертого ключей присоединены соответственно выходные выводы первого R1, второго R2, третьего R3 и четвертого R4 резисторов. Выходные выводы первого S1 и третьего S2 ключей соединены, второго  и четвертого

и четвертого  ключей соединены и образуют соответственно первый Z1 и второй Z2 выходы коммутационного релятора. Входные выводы первого R1 и второго R2 резисторов соединены и образуют первый переключательный вход коммутационного релятора, входные выводы третьего R3 и четвертого R4 резисторов соединены и образуют второй переключательный вход коммутационного релятора.

ключей соединены и образуют соответственно первый Z1 и второй Z2 выходы коммутационного релятора. Входные выводы первого R1 и второго R2 резисторов соединены и образуют первый переключательный вход коммутационного релятора, входные выводы третьего R3 и четвертого R4 резисторов соединены и образуют второй переключательный вход коммутационного релятора.

Работа коммутационного релятора осуществляется следующим образом. При x1 > x2 ключи S1 и S2 замкнуты, а ключи  разомкнуты, что соответствует положению ключей на фиг. 1. Следовательно сигналы y1 и y2 проходят на первый выход коммутационного релятора, а Z2=0 (сигнал на выходе Z2 отсутствует). При x1 < x2 имеем обратную картину - ключи S1 и S2 разомкнуты, а ключи

разомкнуты, что соответствует положению ключей на фиг. 1. Следовательно сигналы y1 и y2 проходят на первый выход коммутационного релятора, а Z2=0 (сигнал на выходе Z2 отсутствует). При x1 < x2 имеем обратную картину - ключи S1 и S2 разомкнуты, а ключи  замкнуты, т.е. сигналы y1 и y2 через ключи

замкнуты, т.е. сигналы y1 и y2 через ключи  проходят на второй выход Z2, а сигнал на первом выходе Z1 отсутствует (Z1 = 0).

проходят на второй выход Z2, а сигнал на первом выходе Z1 отсутствует (Z1 = 0).

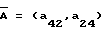

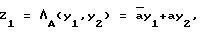

Следовательно для ненагруженного коммутационного релятора

Z1 = ΛA(y1,y2) = a31y1+a13y2, Z2 = 0 при x1 > x2, (1) Z1 = 0 при x1 < x2, (2)

Z1 = 0 при x1 < x2, (2)

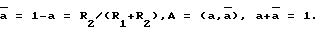

где Λ и V есть символы соответственно КА-конъюнкции и КА-дизъюнкции. Здесь

a13 = R1/(R1 + R3), a31 = R3/(R1 + R3), a24 = R2/(R2 + R4), a42 = R4/ (R2 + R4)

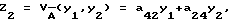

есть весовые коэффициенты, связанные в (1) и (2) попарно условиями комплементарности a13 + a31 = 1, a24 + a42 = 1, A = (a13, a31) и  - кортежи весовых коэффициентов соответственно в выражениях (1) и (2).

- кортежи весовых коэффициентов соответственно в выражениях (1) и (2).

Согласно (1) и (2) коммутационный релятор по первому и второму выходам воспроизводит соответственно операции КА-конъюнкции и КА-дизъюнкции, т.е. взвешенные суммы двух аналоговых сигналов y1 и y2.

Согласно (1) и (2) при a13 = a31 и a24 = a42 (при R1 = R3, R2 = R4, R1, R2, R3 и R4 - соответственно первый, второй, третий и четвертый резисторы с сопротивлениями R1, R2, R3 и R4) коммутационный релятор воспроизводит среднее арифметическое двух сигналов

Z1 = (y1 + y2)/2, Z2 = 0 при x1 > x2;

Z2 = (y1 + y2)/2, Z1 = 0 при x1 < x2,

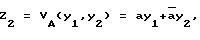

При R3 = R2, R4 = R1 воспроизводятся двойственные КА-конъюнкция и КА-дизъюнкция, т. е. бинарные КА-функции в едином базисе весовых коэффициентов  и предикатных переменных Y = (y1, y2):

и предикатных переменных Y = (y1, y2): Z2 = 0 при x1 > x2,

Z2 = 0 при x1 > x2, Z1 = 0 при x1 < x2,

Z1 = 0 при x1 < x2,

где a = R1/(R1 + R2),

Если при x1 > x2 входное напряжение y2=0, то выходные напряжения

Z1 = y1R3/(R1 + R3) = y1a31, Z2 = 0

При y1 = 0 и x1 < x2 выходные напряжения

Z2 = y2R2/(R2 + R4) = y2a24, Z1 = 0.

В этом случае коммутационный релятор является делителем напряжения с управляемой коммутацией выходных напряжений Z1 и Z2.

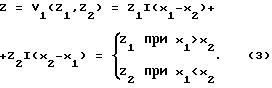

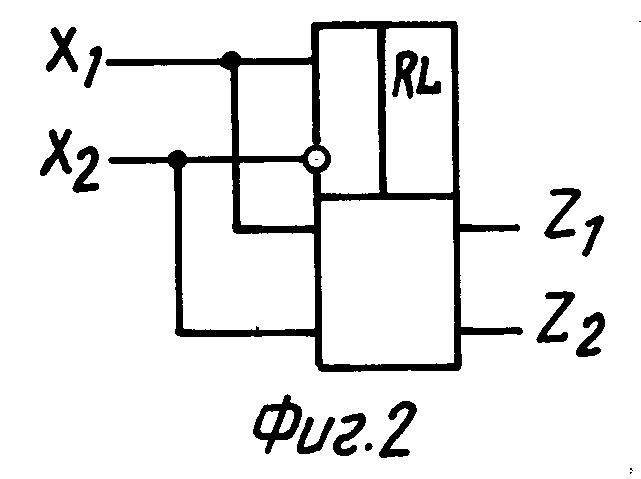

При y1 = x1 и y2 = x2 (при согласованном соединении первого и второго переключательных входов соответственно с первым и вторым компараторными входами коммутационного релятора), приходим к схеме коммутационного релятора, изображенной на фиг. 2, с принудительным переключением состояний ключей на дуальные, воспроизводящего бинарные операции предикатной алгебры выбора:

Здесь I(x) есть единичная функция (оператор Хевисайда), равная нулю при x < 0 и единице при x > 0, I = (I12, I21) - базовый кортеж весовых коэффициентов I12 = I(x1 - x2), I21 = I(x2 - x1) = 1-I12, I12 + I21 = 1.

Согласно (3) схема, представленная на фиг. 2, воспроизводит операцию альтернативного выбора одного из выходных напряжений Z1 и Z2. При этом все вышеприведенные формулы для Z1 и Z2 остаются в силе при замене в них переменных y1 и y2 соответственно на x1 и x2.

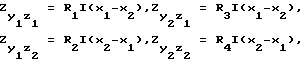

Коммутационный релятор может быть использован и как параметрический R-релятор с использованием в качестве выходных величин сопротивлений Ri:

где подстрочные индексы указывают входы и выходы, между которыми фиксируются сопротивления Ri∈{R1,R2,R3,R4}.

Таким образом, предложенная схема имеет более широкие функциональные возможности при минимальных аппаратурных затратах.

Изобретение относится к аналоговой вычислительной технике, к электронным устройствам автоматики и систем управления и может быть использовано для параллельного воспроизведения бинарных операций комплементарной алгебры. Техническим результатом является расширение функциональных возможностей за счет увеличения числа воспроизводимых операций. Устройство содержит компаратор, ключи и резисторы. 2 ил.

Коммутационный релятор для воспроизведения базовых операций комплементарной алгебры, содержащий компаратор, выход которого соединен с управляющими входами первого замыкающего, второго размыкающего, третьего замыкающего и четвертого размыкающего ключей, выходные выводы первого и третьего ключей объединены и образуют первый выход коммутационного релятора, выходные выводы второго и четвертого ключей объединены и образуют второй выход коммутационного релятора, отличающийся тем, что в схему коммутационного релятора введены первый, второй, третий и четвертый резисторы, выходные выводы которых присоединены соответственно к входным выводам первого, второго, третьего и четвертого ключей, входные выводы первого и второго резисторов соединены и образуют первый переключательный вход коммутационного релятора, входные выводы третьего и четвертого резисторов соединены и образуют второй переключательный вход релятора.

| ВОЛГИН Л.И | |||

| Логико-алгебраические модели электрических цепей, содержащие реляторные коммутаторы // Математические методы и модели: Труды международной конференции | |||

| -Ульяновск: УлГТУ | |||

| Т | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

| ВОЛГИН Л.И | |||

| Синтез устройств для обработки и преобразования информации в элементном базисе реляторов | |||

| -Таллинн: Валгус, 1989, с | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| Минимаксный амплитудный селектор | 1985 |

|

SU1322325A1 |

| РЕЛЯТОРНЫЙ АМПЛИТУДНЫЙ СЕЛЕКТОР | 1996 |

|

RU2112276C1 |

Авторы

Даты

2001-07-10—Публикация

2000-11-10—Подача