Изобретение относится к вычислительной технике и может быть использовано для построения вычислительных систем с повышенной достоверностью выдаваемых данных.

Известна ячейка памяти (АС СССР SU №1234883, МКИ 6 G 11 С 19/14, заявлено 13.04.84, опубл. 30.05.86), содержащая элемент запрета, инверторы, накопительный элемент на трансформаторе, два шунтирующих элемента на диодах, накопительный элемент на конденсаторе, три пассивных элемента на резисторах, ключевой элемент. Способ повышения надежности, реализованный в известном устройстве, заключается в восстановлении состояния ячейки при перерывах в питании.

Недостатки данного способа заключаются в том, что в режиме нормального функционирования не проводится проверка правильности записываемых и выдаваемых данных, что, в свою очередь, не дает возможности повысить достоверность выдаваемых результатов.

Причины, препятствующие достижению требуемого технического результата, заключаются в отсутствии возможности проверки правильности записываемого и выдаваемого кода данных.

Известно запоминающее устройство с исправлением ошибок (авт. свид. СССР №920845, МКИ 6 G 11 С 29/00, заявлено 17.10.79, опубл. 15.04.82), содержащее накопитель, группу сумматоров по модулю 2, регистр сдвига, регистр числа, блок коррекции, блок кодирования-декодирования, генератор импульсов и блок управления. Способ обнаружения и коррекции ошибок заключается в том, что сигналы данных считывают, вводят в корректирующий блок, проверяют правильность кода с использованием избыточного корректирующего кода и при обнаружении ошибки вводят сигналы данных в блок исправления ошибки и выводят сигналы исправленных данных.

Недостатки данного способа заключаются в том, что в режиме нормального функционирования для обнаружения ошибки необходимо использование корректирующих кодов, что требует повышенного объема аппаратурных затрат. Кроме того, устройство обеспечивает обнаружение только одиночных и двойных ошибок.

Причины, препятствующие достижению требуемого технического результата, заключаются в ограниченной возможности проверки правильности записываемого и выдаваемого кода данных и повышенном объеме аппаратуры.

Известно запоминающее устройство с автономным контролем, наиболее близкое к заявляемому (АС СССР SU №1417678, МКИ 6 G 11 С 29/00, заявлено 18.12.86, опубл. 30.03.94), содержащее накопитель, три блока согласования сигналов, блок контроля адреса по четности, блок контроля данных по четности, элементы РАВНОЗНАЧНОСТЬ.

Способ обнаружения ошибок заключается в том, что вводят сигналы двоичного кода данных и двоичного кода адреса, проверяют правильность кода данных и кода адреса в соответствующих блоках контроля по четности, при отсутствии обнаруженной ошибки вводят сигналы кодов данных и адреса в накопитель, запоминают сигналы кода данных, выводят сигналы запомненных сигналов данных и проверяют их в блоке контроля данных по четности, при обнаружении ошибки по модулю 2 выдают сигнал ошибки.

Недостатками данного способа являются ограниченные возможности по обнаружению ошибок, т.к. контроль по четности позволяет обнаружить не более 50% возникающих ошибок.

Причины, препятствующие достижению требуемого технического результата, заключаются в ограниченной возможности проверки правильности записываемого и выдаваемого кода данных.

Задачей, на решение которой направлено предлагаемое техническое решение, является построение вычислительных систем с повышенной достоверностью получения результатов и равномерного распределения энергии в процессе работы, что особенно важно при реализации аппаратуры системы в виде СБИС.

Технический результат, достигаемый при осуществлении изобретения, заключается в повышении достоверности записи, хранения и выдачи данных с возможностью поразрядного контроля и равномерного распределения энергии по разрядам в процессе работы, что особенно важно при реализации аппаратуры системы в виде СБИС.

Заявляемый технический результат достигается тем, что в способе хранения данных с автономным контролем, заключающемся во введении сигналов данных в двоичном коде, выводе сигналов запомненных данных в двоичном коде и при обнаружении ошибки выводе сигнала ошибки, сигналы каждых двух разрядов кода введенных данных преобразуют в код "1 из 4", запоминают сигналы результатов в коде "1 из 4" на элементах хранения, для хранения сигналов каждого четверичного разряда данных используют четыре элемента хранения, при этом один из четырех элементов хранения имеет высокий потенциал, а три оставшихся имеют низкий потенциал, причем для запоминания сигналов кода нуля устанавливают высокий потенциал в первом элементе хранения и низкий потенциал в трех остальных, для запоминания сигналов кода единицы устанавливают высокий потенциал во втором элементе хранения и низкий потенциал в трех остальных, для запоминания сигналов кода двойки устанавливают высокий потенциал в третьем элементе хранения и низкий потенциал в трех остальных, для запоминания сигналов кода тройки устанавливают высокий потенциал в четвертом элементе хранения и низкий потенциал в трех остальных, вводят запомненные сигналы в устройство контроля кода "1 из 4" и при несовпадении с кодом "1 из 4" выдают сигнал ошибки и блокируют выдачу данных.

Технический результат достигается также тем, что в устройство для хранения данных с автономным контролем, содержащее входы данных в двоичном коде, выходы данных в двоичном коде, накопитель и блок контроля данных, причем выходы данных накопителя соединены с входами данных блока контроля данных, введены группа дешифраторов, коммутатор и группа шифраторов, при этом блок контроля данных выполнен в виде группы узлов контроля кода "1 из 4", входы каждого узла контроля кода "1 из 4" группы соединены со входами соответствующих разрядов в коде "1 из 4" входа данных блока контроля данных, выходы сигнала ошибки узлов контроля кода "1 из 4" группы соединены с выходом сигнала ошибки блока контроля данных, выход данных узлов контроля кода "1 из 4" группы соединены с выходом данных блока контроля данных и подключены ко входу данных коммутатора, управляющий вход которого соединен с выходом сигнала ошибки блока контроля данных, выходы разрядов коммутатора в коде "1 из 4" подключены ко входам соответствующих шифраторов группы, выходы которых соединены с выходами данных в двоичном коде устройства, входы разрядов данных накопителя в коде "1 из 4" соединены с выходами соответствующих дешифраторов группы, входы которых подключены к соответствующим парам разрядов входов данных в двоичном коде устройства, выход сигнала ошибки коммутатора соединен с выходом сигнала ошибки устройства, входы выбора ячейки и управления накопителя соединены соответственно с адресным и управляющим входами устройства.

Возможность проведения контроля данных основана на том, что четверичный код "1 из 4" имеет в составе всегда только одну единицу (все возможные комбинации этого кода 0001=0, 0010=1, 0100=2 и 1000=3) и, таким образом, из общего числа возможных ошибочных комбинаций для 4-разрядного слова, равному 15, количество неопознанных ошибок составит только 3. Таким образом, заявляемый способ обеспечивает распознавание 80% ошибок.

Кроме того, распределение энергии при вводе, хранении и выводе данных в коде "1 из 4" всегда одинаково по всем разрядам кода данных, т.к. структурно каждый четверичный разряд содержит строго один высокий и три низких потенциала. Это свойство особенно важно при создании устройств и систем на кристаллах СБИС.

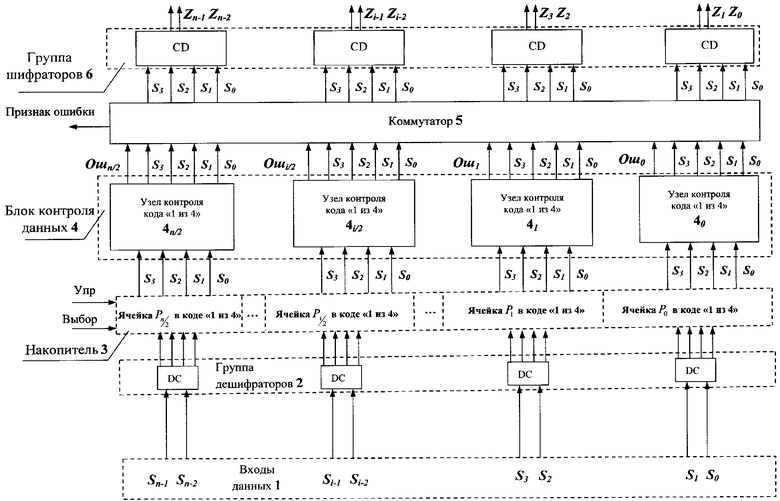

На чертеже представлена функциональная схема устройства, обеспечивающего реализацию способа хранения данных с автономным контролем, где 1 - входы данных в двоичном коде устройства, 2 - группы дешифраторов, 3 - накопитель, 4 - блок контроля данных, в котором 40-4n/2 - узлы контроля кода "1 из 4" (n - разрядность двоичного кода), 5 - коммутатор, 6 - группа шифраторов.

Сигналы данных в двоичном коде S поступают на вход устройства 1. Каждая пара разрядов Si-1 Si-2 поступает на соответствующий дешифратор группы 2 и преобразуется в код "1 из 4". С выходов дешифраторов группы 2 сигналы четверичных разрядов в коде "1 из 4" поразрядно поступают на входы ячеек накопителя 3. Количество четверичных разрядов в накопителе 2, очевидно, в два раза меньше, чем количество двоичных разрядов входных данных (в случае, если количество двоичных разрядов n нечетно, старший разряд дополняется нулем). Процесс хранения может быть организован в зависимости от типа накопителя 3. Это может быть:

- триггерная ячейка - все виды статической памяти (SRAM);

- ячейка на конденсаторе с группой ключей - все виды динамической памяти (DRAM);

- ячейка на отражающей способности вещества - CD ROM, CD R, CDRW;

- ячейка на магнитных свойствах вещества - магнитные и магнитооптические накопители.

Управление процессами записи/считывания осуществляется по входам выбора ячейки и управления накопителя 3.

При считывании записанных сигналов данных из накопителя 3 коды данных поразрядно в коде "1 из 4" вводятся в соответствующие узлы 40-4n/2 контроля кода "1 из 4" блока контроля данных 4. Конструкция узлов контроля кода "1 из 4" известна (см. "Устройство для контроля кода "1 из n", патенты SU 1195451, МКИ 6 Н 03 М 7/22; SU 1683178, МКИ 6 Н 03 М 7/22). Если введенные сигналы соответствуют коду "1 из 4", то сигнала признака ошибки Ошi, не возникает на выходах узлов 40 -4п/2 контроля кода "1 из 4" блока контроля данных 4 и данные передаются на выход коммутатора.

При несоответствии поступивших сигналов данных коду "1 из 4" хотя бы в одном разряде выдается сигнал ошибки Ошi. Сигналы Ошi в коммутаторе 5 объединяются по ИЛИ и в случае появления хотя бы одного активного сигнала Ошi на выходе узла 4i контроля кода "1 из 4" блока контроля данных 4 выдача сигналов кода данных блокируется в коммутаторе 5 и выдается сигнал ошибки.

Сигналы данных выдаются поразрядно в коде "1 из 4" в соответствующие преобразователи группы 6. Преобразователи из кода "1 из 4" в двоичный код реализуются на стандартных четырехвходовых шифраторах. С выходов шифраторов группы 6 сигналы данных в двоичном коде выводятся на выход устройства.

Таким образом, предложенный способ обеспечивает повышение достоверности обработки и хранения данных за счет поразрядного контроля выполнения операции и хранения результата. При этом обеспечивается обнаружение 80% ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ОБРАБОТКИ ДАННЫХ | 2003 |

|

RU2250488C1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2003 |

|

RU2251144C1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство переадресации накопителя информации системы обработки данных | 1982 |

|

SU1072053A2 |

| Запоминающее устройство | 1990 |

|

SU1794261A3 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Тренажер оператора автоматизированной системы управления | 1981 |

|

SU983738A1 |

| Запоминающее устройство | 1988 |

|

SU1547035A1 |

| Устройство для прерывания программ | 1982 |

|

SU1072045A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения вычислительных систем с повышенной достоверностью получения результатов. Технический результат заключается в повышении достоверности получения результатов с возможностью поразрядного контроля и равномерного распределения энергии по разрядам в процессе работы. Устройство содержит накопитель, блок контроля данных, группу дешифраторов, коммутатор, группу шифраторов. Способ описывает работу указанного устройства. 2 н.п.ф-лы, 1 ил.

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ | 1986 |

|

SU1417678A1 |

Авторы

Даты

2005-08-27—Публикация

2003-07-29—Подача