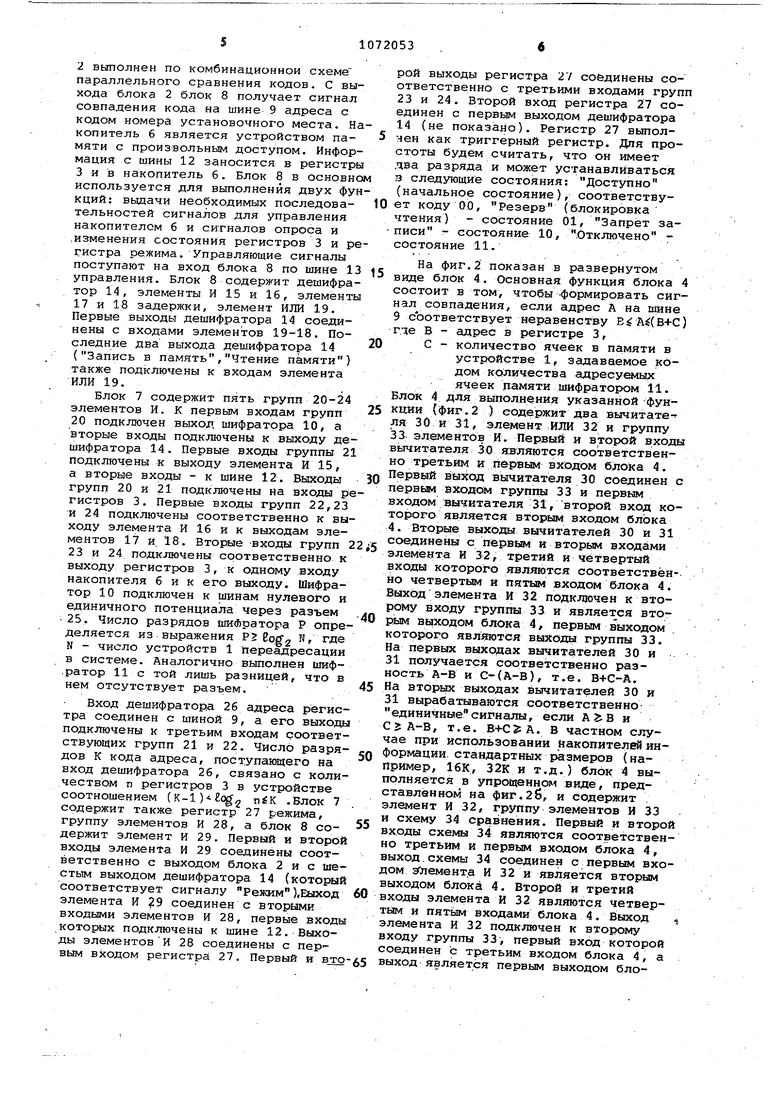

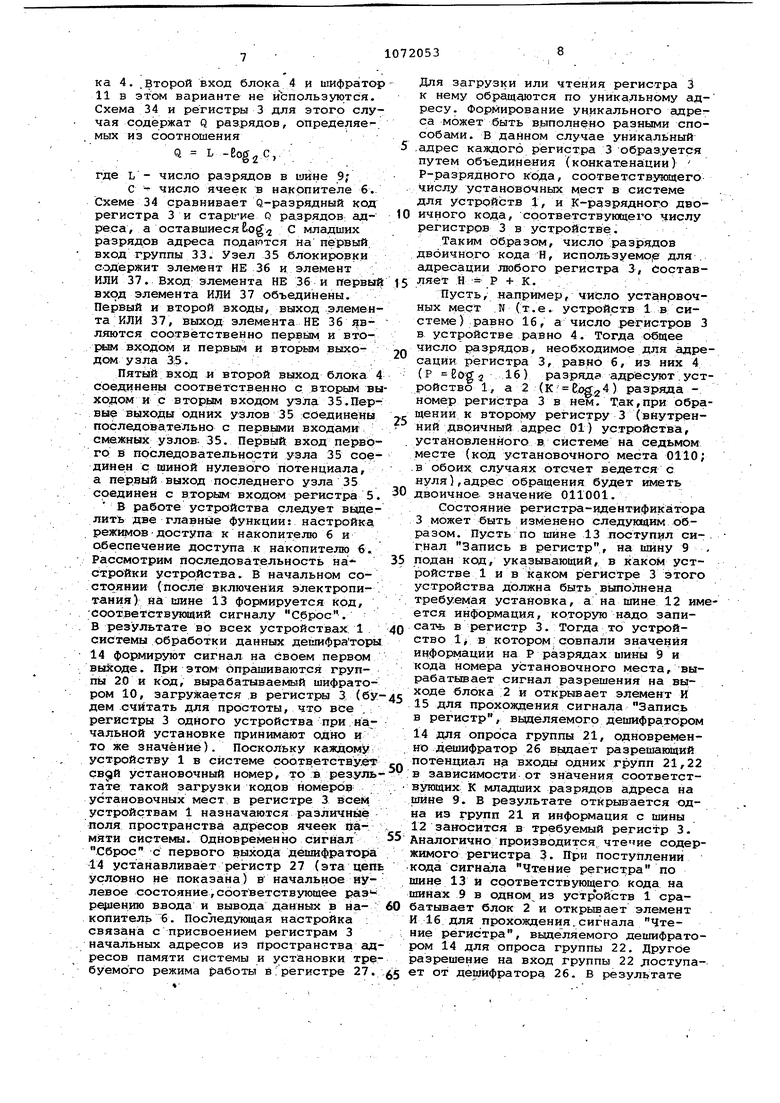

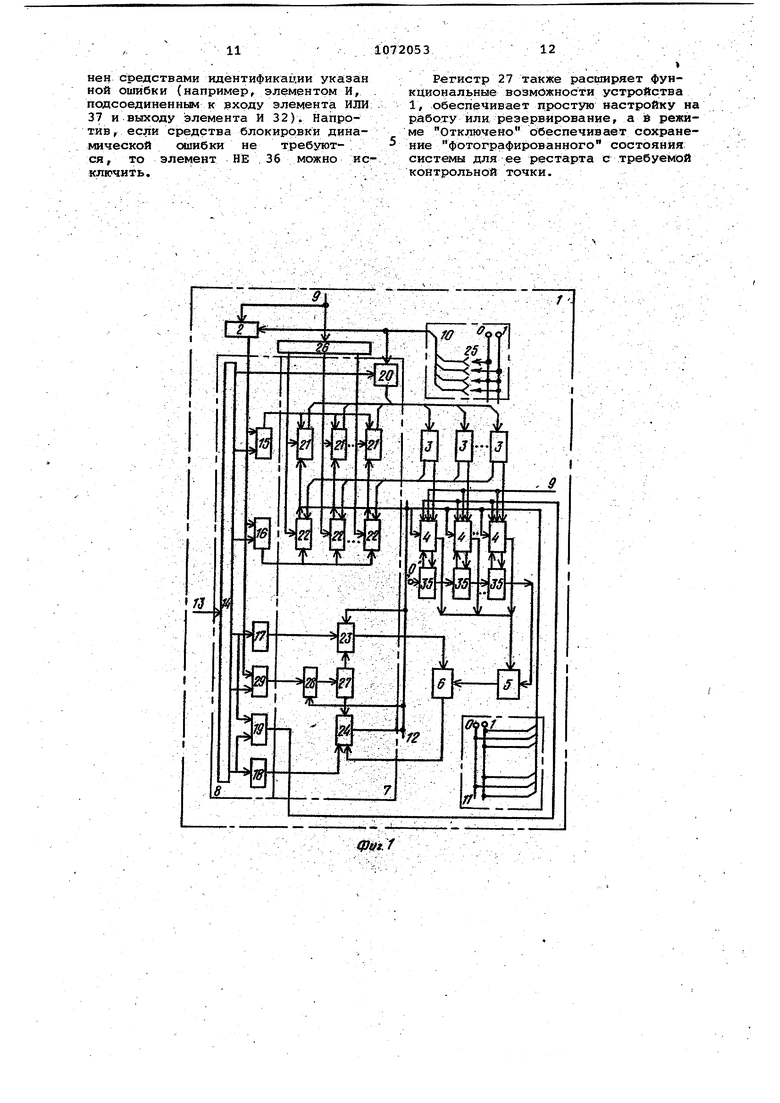

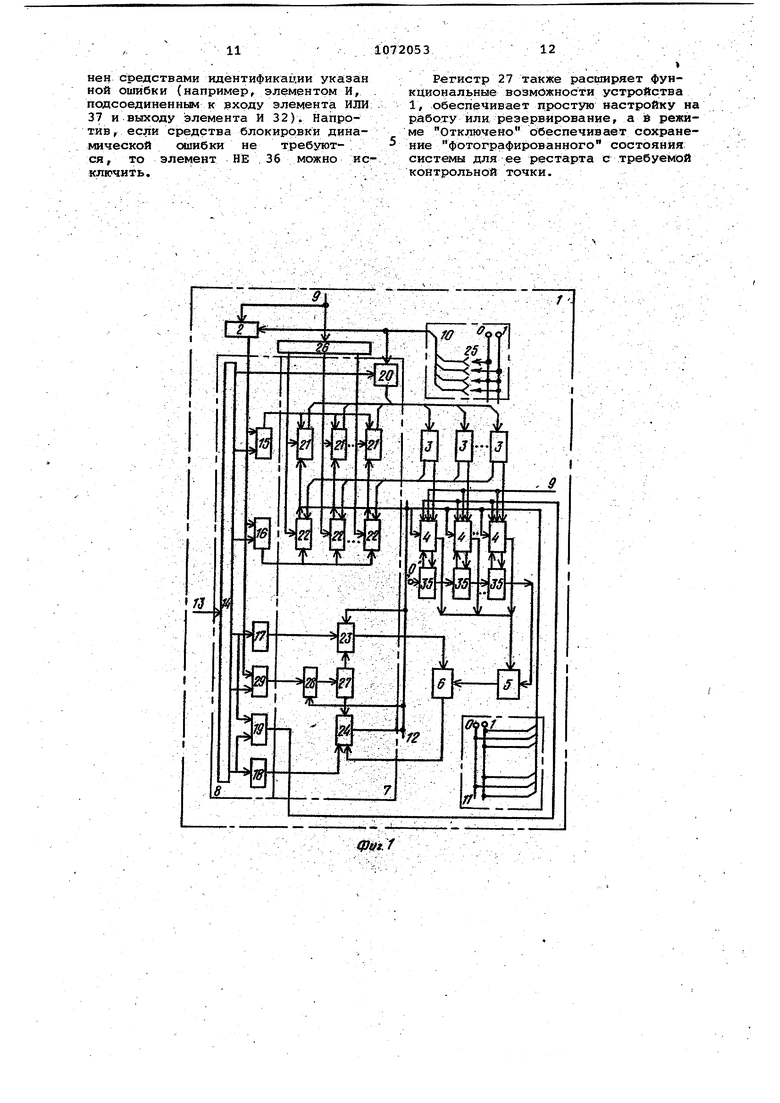

.Изобретение относится к цифровой вычислительной технике, а именно к устройствам управления систем :обработки дйнных с основной памятью, включающей несколько независимых за поминающих устройств (ЗУ), и может быть применено в ЦВМ, которые должн обладать программно-управляемой Kpa ностью ре.зервирования памяти и использовать параллельные принципы обработки информации. fto основному авт. ев. № 845157 известно устройство, содержащее блок сравнения кодов, регистр идентификации, блОк селекции адреса, ре гистр адреса, накопитель инфЬр 4ации блок ввода-вывода, включающий пять групп элементов И, блок управления, включающий дешифратор, два элемента И, два элемента задержки, элемент HJre, шифратор системных соединеваяй и шифратор внутренних соединений, причем вход дешифратора соединен с шиной управления устройства а вы ходы дешифратора подключены соответ ственно к первым входам первого и вторюго элементов И, входам первого и второго элементов задержки, элемента или и первым входам элементов И первой группы, первый и второй вх ды блока сравнения кодов соединены соответственно с шиной адреса устройства и выходом шифратора Системных соединений, а ВЕЛСОД блока сравнения кодов подключен к вторЕ входам первого и второго элементов И, вторые входы элементов И первой гру пы соединены с выходом шифратора си стемных соединений, а выходы элемен тов И первой группы подключены к вх дам регистра идентификации и выходам - элементов Ивторой группы, первые и вторые входы которых соединены соот ветственно с вьгходом первого элемен та И и выходами элементов И третьей группы, первые и воюрие входы элементов И третьей группы подключены соответственно к выходу регистра идентификации и выходу второго элемента И, первый, второй, и третий входы и вйход блока селекции адреса соединены соответственно с шиной адреса устройства, выходом регистра идентификации, выходом элемента ИЖ и информационным входом регистра адреса, информационный и адресный входы и выход накопителя инфор.мации подключены соответственно к выходам элементов И четвертой rpirn-пы, выходу регистра адреса и первь1м входам элементов И пятой группы первые и вторые входы элементов И четвёртой группы соединены соответственно с шиной данных устройства и выходом первого элемента задержки, вторые входы и выходы элементов И пятой группы подключены соответстве но. к выходу второго элемента задхержки и шине данных устройства I . В известной системе обработки данных, оперативная память которой име-. ет мнЬгоблсг чную структуру и йсподь зует в качестве блоков памяти ЗУ, при оргайизации доступа к накопителю от нескольких одновременно функцнонирующих абонентов памяти динамическое йзмене ние СОСТОЯНИЙ регистровидентификаторов в интересах одного из абонентов памяти (например,процессора) в общем случае может привести К: нарушению.; правильности выполняемьгх действий других абонентов памяти (например, ;каналов ввода-вьшода), которые имели доступ к этому блоку памяти наряду с первым абонентом и к моменту изменения состояний евде не закончили свою работу. Для орг анизации динамического управления обработки данньгх в известном устройс:тве операционной cHCTiSMe приходится перед принятием решения о переключении сОстЬянНя регистра-идентифнкатора устройства перёадресации производить сложный учет работы всех абонентов, нспользующих в текущий момент данный накопитель, и не производить перерас пре1аеление этого ресурса до тех пор, пока все его пользователи, имеющие, как правило, разные скорости функционирования, полностью не завераат выполняемый ими обмен или обработку. В результате усложняетсяЕ программное обеспечение, планирующее работу системы, а главное, снижается эффектив-. ность работы системы в цёлсмм из-за появления за видимости работы одних абонентов памяти от других. Цель изобретения - повышение:-надежности и расширение функаиональ ныэс воэможностей, nyTfflvi независимой настройки устройства переадресации накопителя информации дл;я различных абонентов одновременно на различные значения из пространства адресов ячеек памяти системы обработки данных. . ..,:, ;, . ;;....: ., .. ; Поставленная цель достигается TeMjчто в устройство переадресации на-, копителя информации системы обработ ки данных введены дешиф атор адреса регистра,, регистр ражшла, шестая: группа элементов И, третий элемент И, п регистров идентификации,п блокировки и п блоков адреса, управляющий вход, адрее11ый Вход, вход идентификации, вхбд бло- . кировки и первый выход каадого из которых соединены соответственно с выходом элемента ИЛИ, адресным входом устройства, первым вбосодрмбоответствующего регистра и;вентификации, первым выходом и itepsb входном соответствующего узла блокировки/ при дтом второй вход nepBoiro уэла блокировки подключен к шине нулевого потенциала, второй каждого узла блокировки, кроме последнего, с вторым входом следующего узла блокировки г а второй выход последнего узла блокировки подключен к управляющему входу регистра адреса, информационный вход которого соединен с вторыми выходами всех блоков, селекции адреса, входы регистров идентификации подключены к выходам элементов И первой группы, а вторые выходы регистров иден.тификации соединены с вторыми входами соответствующих элементов И второй группы, вход дешифратора адреса регистра подключен к адресно му входу устройства, а выходы дешифратора адреса регистра соединены с: третьими входами соответствующих элемнетов И ,третьей группы, первый вход, второй вход и выход третьего элемента И пЪдключены соот ветственно к выходу блока сравнения второму выходу дешифратора кода опе рации и первым входам элементов И шестой группы, вторые входы и выход .которых соединены соответственно с входом данных устройства и входом регистра-режима, а первый и второй выходы регистра режима подключены к .третьим входам элементов И соответственно четвертой и пятой групп. Кроме того, блок селекции адреса содержит элемент И, группу элементо И и схему сравнения, первый вход/ второй вход и выход которой соедине ны соотв.етственно с адресным входом входом идентификации и первым выходом блЬка, первый, второй и третий входы и выход элемента И подключены соответственно к выходу схемы сравнения, управляющему входу и вхо цу блокировки блока и первым входам элементов И труппы, вторые входы и выходы которых соединены соответственно с адресным входом и вторым вы ходом блока. Узел блокировки содержит элемент НЕ и элемент ИЛИ, первый вход, второй вход и выход которого подключены соответственно к первому .входу, второму входу и второму выходу узла, при этом вход и выход элемента НЕ соединены соответственно с вторым, входом и первым выходом узла. На фиг.1 изображено устройство переадресации накопителя информации на фиг.2 - варианты выполнения блока селекции адреса и узел блокировки ; . Устройство 1 переадресации накоТ1ителя инфО1 лации содержит блок 2 сравнения кода, находящегося на шин адреса, с кодом номера установочног места, поступающего из шифратора си стемных соединений п регистров 3 идентификации для хранения, кодов ад ресов первых ячеек из пространства адресов ячеек памяти системы, блоки 4 селекции адреса для сравнения кода адреса, находящегося на шине адреса, с границами поля адресов,, определяемыми кодами, находящимися в регистрах 3, и кодом, соответствующим количеству адресуемых ячеек, и для формирования кода адреса на регистре 5 адреса для хранения адресаи коммутации накопителя 6 информации,к которой происходит обращение в текущем цикле работы.Устройство также, со- . держит блок 7 ввода-вывода для ввода информации в накопитель 6 информации от. шины данных ив регистры 3 от шины данных и от шифратора системных соединений для вывода на ши-. ну данных информации из накопителя б, регистров 3 и шифратора системных соединений, блок 8 управления для приема и передачи управлякядих сигналов,..устройства 1. Второй вход блока 2 является первым адресным входом устройства и соединен с .шиной 9 адреса. Первый вход блока 2 соединен с шифратором 10 системных соединений. Зыхрд блока 2 соединен с первым входом блока 8, второй вход которого является управлякядим входом устройства 1. Управляющий вход устройства соединен с шиной управления. . Входы регистров 3 соединены с . первыми выходами блока 7, выходы с первыми входами соответствующих им, блоков 4 и пятыми входами блока -7. Вторые входы блоков 4 соединены с выходом шифратора 11 внутренних соединений, хранящим код количества адресуемых ячеек, число разрядов п в котором связано с числом С;ячеек соотношением (п-1) Eotf/j Cin. Третьи входы блока 4 подключены к второму адресному входу устройства, который соединен с шиной 9 адреса. Четвертые входы блока 4 соединены с выходом блока 8, первые выходы блоков 4 поразрядно объединены и подключены к первому входу регистра 5. Выход регист ра 5 соединен с адресным входом накопителя б, информационный вход KOTOpo.ro соединен с первым выходом блока 7. Информационный выход накопителя б .соединен с первым входом блока 7. .Информационный выход ус.тройства является вторым выходом блока 7 и соединен с шиной 12 данных. Третий вход блока 7 соединен с выходом блока 8, четвертый вход является установочным входом устройства, а пятый вход соединен с выходом дешифратора адреса регистра, вход которого подключен к первому адресному входу. Все базовые компоненты устройст.ва 1 переадресации накопителя информации выполнены аналогично Ij . Блок 2выполнен по комбинационной схеме параллельного сравнения кодов. С выхода блока 2 блок 8 получает сигнал совпадения кода на шине 9 адреса с кодом номера установочного места. На копитель б является устройством памяти с произвольным доступом. Информация с шины 12 заносится в регистры 3и в накопитель 6. Блок 8 в основно используется для выполнения двух фун кций: вьщачи необходимых последовательностей сигналов для управления накопителем 6 и сигналов опроса и .изменения состояния регистров 3 и ре гистра режима. Управляющие сигналы поступают на вход блока 8 по шине 13 управления. Блок 8 содержит дешифратор 14, элементы И 15 и 16, элементы 17 и 18 задержки, элемент ИЛИ 19. Первые выходы дешифратора 14 соединены с входами элементов 19-18. Последние два выхода дешифратора 14 (Запись в память,Чтение памяти) также подключены к входам элемента ИЛИ 19., Блок 7 содержит пять групп 20-24 элементов И. К первым входам групп 20 подключен выход шифратора 10, а вторые входы подключены к выходу дешифратора 14. Первые входы группы 21 подключены к выходу элемента И 15, а вторые входы - к шине 12. Выходы групп 20 и 21 подключены на входы ре гистров 3. Первые входы групп 22,23 и 24 подключены соответственно к выходу элемента И 16 и к выходам элементов 17 и. 18. Вторые Входы групп 2 23 и 24 подключены соответственно к выходу регистрюв 3, к одному входу накопителя б и к его выходу. Шифратор 10 подключен к шинам нулевого и единичного потенциала через разъем 25. Число разрядов шифратора Р определяется из - выражения Р2 Bptfg N, где N - число устройств 1 Иереадресации в системе. Аналогично выполнен шиф.ратор 11с той лишь разницей, что в нем отсутствует разъем. Вход дешифратора 26 адреса регистра соединен с шиной 9, а его выходы подключены к третьим входам соответствующих групп 21 и 22. Число разрядов К кода адреса, поступающего на вход дешифратора 26, связано с количеством п регистров 3 в устройстве соотношением (K-l)cg2 К .Блок 7 содержит также регистр 27 режима, группу элементов И 28, а блок 8 содержит элемент И 29. Первый и второй входы элемента И 29 соединены соответственно с выходом блока 2 и с шестым выходом дешифратора 14 (который соответствует сигналу Режим ),Еыход элемента И 9 соединен с вторыми входыми элементов И 28, первые входы которых подключены к шине 12. Выходы элементовИ 28 соединены с первым входом регистра 27. Первый и вто рой выходы регистра 27 соединены соответственно с третьими входами групп 23 и 24. Второй вход регистра 27 соединен с первым в.ыходом дешифратора 14 (не показано). Регистр 27 выполнен как триггерный регистр. Для простоты будем считать, что он имеет два разряда и может устанавливаться 3 следующие состояния: Доступно (начальное состояние), соответствует коду 00, Резерв (блокировка чтения) - состояние 01, Запрёт записи - состояние 10, .Отключено состояние 11. На фиг.2 показан в развернутом виде блок 4. Основная функция блока 4 состоит в том, чтобы формировать сигнал совпадения, если адрес А на шине 9 соответствует неравенству В А(В+С) е В - адрес в регистре 3, С - количество ячеек в памяти в устройстве 1, задаваемое кодом количества адресуемых ячеек дамяти шифратором 11. Блок 4 для выполнения указанной функции (фиг.2 ) содержит два вычитателя 30 и 31, элемент ИЛИ 32 и группу 33; элементов И. Першый и второй входы вычитателя 3:0 являются соответственно третьим и первым входом блока 4. Первый выход вычитателя 30 соединен с первым входом группы 33 и первым входом вычитателя 31, второй вход которого является вторым входом блока 4. Вторьте выходы вычитателей 30 и 31 соединены с первым и вторым входами элемента Н 32, третий и четвертый входы которого являются соответствен-, но четвертым и пятым входом блока 4. Выход элемента И 32 подключен к второму входу группы 33 и является вторым выходом блока 4, первым выходом которого являются выходы группы 33. На первых выходах вычитателей 30 и 31 получается соответственно разность А-В и С(Л-В), т.е. В+С-А, На вторых выходах вычитателей 30 и 31 вырабатываются соответственно единичные сигналы, если и С г А-В, т.е. В+С А. В частном случае при использовании накопителей информации стандартных размеров (например, 16К, 32К и т.д.) блок 4 выполняется в упрощенном виде, представленном на фиг.2б, и содержит . элемент И 32, группу элементов И 33 и схему 34 Сравнения. Первый и второй входы схемы 34 являются соответственно третьим и первым входом блока 4, выход.схемы 34 соединен с первым входом Элемента И 32 и является BTOJ«JIM выходом блока 4. Второй и третий входы элемента И 32 являются четвертым и пятым входами блока 4. Выход элемента И 32 подключен к второму входу группы 33, первый вход которой соединен с третьим входом блока 4, а выход является первым выходом блока 4. .Второй вход блока 4 и шифратор 11 в этом варианте не используются. Схема 34 и регистры 3 для этого случая содержат Q разрядов, опредеттяв-. мых из соотношения Q L -Bog2 С,. где L - число разрядов в шине 9; С - число ячеек в накопителе 6. Схеме 34 сравнивает Q-разрядный код регистра 3 и стари-ие о разрядов; ajtiреса, а оставшиеся E,ogv2 С младших разрядов адреса подаются на первый, вход группы 33. Узел 35 блокировки содержит элемент НЕ 36 и элемент ИЛИ 37. Вход элемента НЕ 36 и первы вход элемента ИДИ 37 объединены. Первый и второй входы, выход элемента ИЛИ 37, ВЫХОД: элемента НЕ 36 j|Bляются соответственно первым и входом и первым и вторым выходом узла 3:5.. Пятый:вход и второй выход блока 4 с-рединены соответственно с вторым вы ходом и с вторьм входом узла 35.Первые БИХОДЫ одних узлов 35 соединены последовательно с первыми входамк: смежных узлов 35. Первый вход первого g последовательности узла 35 соединен с шиной нулевого потенциала, а первый выход последнего узла 35 соединен с вторым входом регистра 5 В работе устройства следует ввделить две главные функции: настройка режшчовдоступа к накопителю 6 и обеспечение доступа к накопителю 6. Рассмотрим последовательность настройки устройства. В начальном состоянии (после включения электропитания) на шине 13 формируется код, соответствукяций сигналу Сброс. В результате во всех устройствах 1 системы обработки данных дешифраторы 14 формируют сигнал на своем первом выводе. При этом Опрашиваются группы 20 и код, вырабатываемый шифратором 10, загружается в регистры 3 (бу дем .считать для простоты, что все регистры 3 одного устройства при на чальной установке принимают одно и то же значение). Поскольку каждому устройству 1 в системе соответству; установочный номер, то в резуль тате такой загрузки кодов номеров установочных мест в регистре 3 всей устройствам 1 назначаются различные поля пространства адресов ячеек оамяти системы. Одновременно сигйал Сброс с первого выхода дешифратора 14 устанавливает регистр 27 (эта цеп условно не показана) в начальное нулевое состояние,соответствующее раэ ре{11ению Ввода и вывода данных в накопитель 6. Последующая настройка : связана с присвоением регистрам 3 начальных адресов из Пространства гщ ресов памяти системы и установки тре буемого режима работы в регистре 27, Для загрузки или чтения регистра 3 к нему обращаются по уникальному адресу. Формирование уникального адреса может быть вьтполнено разными способами . В данном случае уникальный .адрес каждого регистра 3 образуется путем объединения (коякатена:ции) Р-разрядного кода, соответствующего числу установочных мест в системе для устройств 1, и К-разрядного двоичного кода, соответствующего числу регистров 3 в устройстве. Таким образом, число разрясдов двоичного кода Н, используемо для . адресации лю.бого регистра 3, Составляет Н Р + к. . Пусть, например, чиоло устанрвочных мест .N (т.е. устройств 1 в системе) равно 16, а число регистров 3 в устройстве ра,вно 4. Тогда общее число разрядов, необходимое ДJIЯ адресации регистра 3, равно 6, из них 4 (р Bo-g2 16) разряда адрёс1тот.устройство 1, а 2 (K E.og2) разряда номер регистра 3 в нем. Так,при обращении к второму регистру 3 (внутренний двричный адрес 01) устройства, установленного в системе на седьмом месте (код установочного места ОНО; в обоих случаях отсчет ведется с нуля),адрес обращения будет иметь двоичное значенке 011001. Состояние регистра-идентификатора 3 может быть изменено следующим образом. Пусть по шине 13 лоступил си- . гнал Запись в регистр, на шину 9 . подан код, указывающий, в каком устройстве 1 и в каком регистре 3 этого устройства должна быть вьшолнен.а требуемая установка, а на шине 12 имеется информация, которую надо записать в регистр 3. Тогда то устройство 1 в котором совпали значения информации на Р разрядах шины 9 и кода номера установочного места, вырабатывает сигнал разрешения на вьгходе блОка 2 и открывает элемент И 15 для прохождения сигнала Запись в регистр, выделяемого дешифратором 14 для опроса группы 21, одновременно дешифратор 26 вьщает разрешаклций потёндиал на входы одних групп 21,22 в зависимости от значения соответствующих К младших разрядов адреса на шине 9. В результате открывается одна из групп 21 и информация с шины 12 заносится в требуемый регистр 3. Аналогично производится чтение содержимого регистра 3. При поступлении кода сигнала Чтение регистра по шине 13 и сротвётствующего кода на шинах 9 в одном из устрЪйств 1 срабатывает блок 2 и открывает элемент И 16 для прохождения.сигнала Чтение регистра, вьщеляемого дешифратором 14 для опроса группы 22. Другое разрешение на вход группы 22 лоступает от дешифратора 26. В результате

информация из регистра 3 поступает на шину 12. Подобным же образом производится занесение информации в регистр 27. При поступлении кода сигнала Режим по шине 13 и соответствующего Р-разрядного кода на шинах 9 (коды младших К разрядов игнорируются) в одном из устройств 1 срабатывает блок 2 и открывает элемент И 29 для прохояддения сигнала Режим, выделяемого дешифратором 14 для опроса элементов И 28. В результате информация с шины 12 поступает в регистр 27.

Рассмотрим работу устройства при обеспечении доступа к накопителю 6. Для обращения к накопителю 6 по шине 13 передаются сигналы Запись в память, Чтение памяти, которые, проходя через дешифратор 14, поступают на элемент ИЛИ 19 и на один из элементов 17 или 18 соответственно. Сигнал с выхода элемента ИЛИ 19 поступает на входы блоков 4. Одновременно на все блоки 4 подается информация с шин 9, данные с регистров 3 и код количества адресуемых в устройстве ячеек памяти из шифратора 11. Первоначально на входах и выходах всех элементов ИЛИ 37 узлов 35 отсутствуют сигналы, а на выходах всех элементов НЕ 36 имеется разреш.ающий потенциал, который подается на элемент И 32. Если адрес, заданный на шине 9, попадает в пространство адресов, определяемое настройкой регистров 3 и объемом накопителя б данного устройства 1, т.е. вьшолняется условие + С , то вычитатели 30 и 31 (фиг.2а) одновременно выдают на элемент И 32 единичный признак результата или срабаты вает схема 34 (фиг.2б) и выдает на вход, элемента И 32 потенциал разрешения. В результате в блоке 4, в котором выполняется условие селекции, т.е. соотношение ВгА(В + С) срабатывает элемент И 32, открываются элементы рруппы 33 и разность (А-В) (Фиг. 2) или младшие С разрядов шины 9 (фйг.25) поступают на вход регистра. 5. Эта разность (или младшие t)a3pHj H адреса) далее записывается в регистр 5 и используется в качестве внутреннего адреса для ввода и выборки информации в (из) накопителя 6. Пусть, например, в системе обработки данных имеются накопители емкостью , а число разрядов в шине 9 равно, 18, «спользуем вариант, -показанный на фиг.2б, тогда Q 18Во 2 16К 4. т.е. регистры 3 и схема 35 должны быть четырехразрядными.

Допустим, что состояние одного регистра 3 равно О, а другого 3. Следовательно, в рассматриваемой системе при указанной настройке регистров 3 они будут открывать доступ к соответствующим накопителям б , если адрес

будет лежать соответственно в границах 0 А г:(0+1)-16К и 3-16К А (3+1)1бК . В случае, если рассматриваемые регистры 3 управляют одним накопителем б, то, как видно из примери, для различнр1Х абонентов памяти могут быть определены разные (в данном случае непересекающиеся) физические адреса. Сигнал выполнения условия селекции поступает с выхода

элемента И 32 на вход элемента ИЛИ 37 и далее последовательно переносится на вход и выход элементов ИЛИ 37 в других узлах 35 устройства 1. Сигнал с выхода элемента ИЛИ 37 последнего узла 35 разрешает прием в регистр 5 адреса с выхода группы 35 одного из блоков 4 и формирует начало операции обращения к накопителю б, Выборка информации происходит следующим образом. Сигнал Чтение памя jjH поступает с выхода дешифратора 14 на элемент 18 и далее на первый вход группы 24. ЕсЛи обращение к накопителю 6 было разрешено и если регистр 27 выдает разрешающий сигнал

на Третьи входы группы 24, то группа 24 выдает информацию из накопителя б на шину 12. Аналогично производится ввод информации. Сигналы Запись в Память поступают с выхода

дешифратора 14 на элемент 17 и далее поступают на первый вход груп пы 23. При наличии йбращения и разрешения ввода от .регистра 27 внакопитель б записываются данные через группу 23. Поскольку в системе обработки данных могут оказаться несколько устройств 1, для которых справедливо соотношение В2А(В+С), то одна и та же. операция-ввода или

выборки может одновременно происходить в нескольких устройствах 1 системы. Устройства 1 системы, в KQторых неравенство В. А(В+С) не выполняется, остаются пассивными.

Регистры 3 в одном устройстве 1

должны настраиваться , чтобы задаваемое ими пространство адресов ячеек памяти не пересекалось. Инь1ми словами, при правильной настройке устройства 1 должен срабатывать

элемент И 32 только в одном блоке 4.

Для предотвращения неопределенных последствий, которые могут возникнуть в результате динамической ошибки или сбоя, блоки 4 охвачены

приоритетными средствами бJJoкиpoвки. С этой цель к входу элемента ИЛИ 37 подключен элемент НЕ 36. В результате, при Появлении сигнал.а селекции в одном из блоков 4 он поступает

в узел 35 на вход и выход элемента ИЛИ 37 и исопльзуется элемент НЕ 36 для подавления возникновения сигналов селекции в других оставшихся блоках 4. При необходимости

контроля за динамическими ошибками блок 4 легко может быть дополнен средствами идентификации указан ной ошибки (например, элементом И, подсоединенным к входу элемента ИЛИ 37 и выходу элемента И 32). Напротив , если средства блокировки динамической ошибки не требуются, то элемент НЕ 36 можно исключить.. .

Регистр 27 также расширяет функциональные возможности устройства 1, обеспечивает простую настройку на работу или резервирование, аи режиме Отключено обеспечивает сохранение фотографированного состояния системы для ее рестарта с требуемой койтрольной точки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство переадресации накопителяиНфОРМАции СиСТЕМы ОбРАбОТКи дАННыХ | 1979 |

|

SU845157A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| Постоянное запоминающее устрой-CTBO | 1979 |

|

SU809379A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Устройство для ввода информации | 1978 |

|

SU746484A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

1. УСТРОЙСТВО ПЕРЕАДРЕСАЦИИ ВАКОПИТЕЛЯ ИНФОРГ4АЦИИ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ по авт.св. № 845157, о т л и ч а ю щ ее с я тем, что, С целью расширения его,-функциональных возможностей путём независимой перестройки для различных абонентов / оно содержит дешифратор адреса реги;стра, регистр режима, шестую группу . элементов И, третий элемент И,п регистров идентификации, п узлов блокировки и п блоков селекции адреса, управляющий вход, адресный вход,вход идентификации, вход блокировки и первый выход каждого из которых соединены соответственно с выходом элемента ИЛИ, адресным входом устройства, первьо выходом соответствуючего регистра идентификации, первьа выходом и первым входом соответствующего узла блокировки, при этом второй вход первого узла блокировки подключен к шине нулевого потенциала; второй выход каждого узла блокировки, кроме последнего, соединен с вторым входом следующего узла блокировки, а второй выход последнего узла блокировки подклк)чен к управлякяцему входу регистра адреса, информационный вход которого соединен с вторыми выходами всех блоков селекции адреса, входы регистров идентификации подключены к выходам эле- . ментов И первой группы, а вторые выходы регистров идентификации соединены с вторыми входами соответствующих элементов И второй группы, вход дешифратора адреса регистра подключен к адресному входу устройства, а выходы дешифратора адреса регистра соединены с третьими входами соответствующих элементов И третьей группы, первый вход, второй вход и выход третьего элемента И подключены соответственно к выхбду блока сравнения, второму выходу дешифратора кода операции и первым входам элементов И шестой группы, вторые входал и выходы которых соединены соответственно с входом данных устройства и входом регистра режима, а первый, и второй выходы регистра режима подключены к третьим входам элементов § И соответственно четвертой и :пятой групп. 2. Устройство по П.1, от л и ч а ю щ е е с я тем, что блок селекции адреса содержит элемент И, S группу элементов И и схему сравнения, первый вход, второй вход и выход которой соединены соответственно с адресным входом, входом идентификации и первым выходом блока, первый, втооой и третий входы и выход элемента И подключены соответственно к выходу схемы сравнения, управляющему входу и входу блокировки блока и первым входам элементов И группы, вторые входы и выходы которых соединены соотвётотвенно с гщресным входом и вторым выходом блока. : 3. Устройство по П.1, о т л и чающее с я тем, что узел блокировки содержит элемент НЕ и.элемент ИЛИ, первый вход, второй вход и выход которого подключены соответ.ственно к первому входу, второму входу и второму выходу узла, при этом вход и выход элемента НЕ соединены соответственно с вторым входом и первым входом узла.

..rrLS

. fa

И

СжЗС

3S

ц 37

Фиг.2е

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство переадресации накопителяиНфОРМАции СиСТЕМы ОбРАбОТКи дАННыХ | 1979 |

|

SU845157A1 |

Авторы

Даты

1984-02-07—Публикация

1982-04-26—Подача