Изобретение относится к области вычислительной техники, в частности к устройствам сложения чисел с плавающей запятой, и может быть использовано при разработке арифметических устройств микропроцессоров как универсальных, так и специализированных.

При сложении/вычитании чисел с плавающей запятой возможны ситуации, когда требуется нормализация - сдвиг суммы влево на большое количество разрядов. Для формирования мантиссы и порядка результата нужно определить положение старшего значащего нуля или единицы (в зависимости от знака результата). При нормализации предварительный порядок результата ПБ (порядок большего слагаемого) уменьшается на величину, равную количеству старших незначащих разрядов мантиссы. Согласно стандарту “ANSI/IEEE 754” на двоичную арифметику порядок результата должен быть не меньше единицы. Таким образом, результат должен нормализоваться на количество разрядов, не превосходящее максимально допустимую для них величину, равную М=ПБ-1. Величина М называется кодом ограничения. Если код ограничения меньше кода сдвига SH, то в этом случае мантисса сдвигается на М разрядов влево, и результат будет денормализованным числом.

Известно устройство для сложения и нормализации вещественных чисел, содержащее сумматор мантисс, блок предсказания старших разрядов кода сдвига, блок определения младших разрядов кода сдвига, нормализатор (US №4926369, кл. G 06 F 007/38, 1990).

Недостатком устройства является необходимость коррекции кода сдвига, так как предсказанное значение может отличаться от действительного на "1", а также отсутствие учета ограничения величины сдвига, что обусловлено отсутствием соответствующих узлов в блоке предсказания старших разрядов кода сдвига и блоке определения младших разрядов кода сдвига.

Наиболее близким по технической сущности к изобретению является устройство для суммирования мантисс и нормализации результата при вычислениях с плавающей запятой, содержащее блок предсказания старших разрядов кода сдвига, сумматор мантисс и нормализатор результата, причем первый и второй входы сумматора мантисс являются первым и вторым входами устройства и присоединены соответственно к первому и второму входам блока предсказания старших разрядов кода сдвига, третий вход которого является третьим входом устройства, выход узла предсказания старших разрядов кода сдвига соединен с управляющим входом нормализатора результата, выход которого является выходом устройства (US №5732007, кл. G 06 F 007/42, 1998).

Недостатком данного устройства является относительная сложность оборудования, в особенности блока предсказания старших разрядов кода сдвига, что в значительной мере связано с формированием младших разрядов кода сдвига.

Техническим результатом является упрощение устройства для суммирования мантисс и нормализации результата при вычислениях с плавающей запятой с обеспечением необходимого быстродействия.

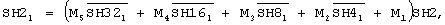

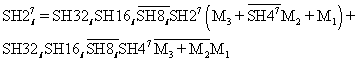

Достигается это тем, что в устройство для суммирования мантисс и нормализации результата при вычислениях с плавающей запятой, содержащее блок предсказания старших разрядов кода сдвига, сумматор мантисс и нормализатор результата, причем первый и второй входы сумматора мантисс являются первым и вторым информационными входами устройства и присоединены соответственно к первому и второму инфомационным входам блока предсказания старших разрядов кода сдвига, вход кода ограничения которого является третьим информационным входом устройства, выход узла предсказания старших разрядов кода сдвига соединен с управляющим входом нормализатора результата, выход которого является выходом устройства, согласно изобретению введен блок определения младших разрядов кода сдвига с учетом ограничения величины сдвига, причем выход сумматора мантисс подключен к первому информационному входу блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига, второй информационный вход которого соединен с входом кода ограничения блока предсказания старших разрядов кода сдвига, выход которого соединен с управляющим входом блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига, выход которого подключен к информационному входу нормализатора результата, кроме того блок определения младших разрядов кода сдвига с учетом ограничения величины сдвига содержит элемент ИЛИ и N узлов определения младших разрядов кода сдвига по группе выходных разрядов сумматора, где N равно 16 или 8, управляющий, первый и второй информационные входы каждого из вышеупомянутых узлов подключены к соответствующим управляющему, первому и второму информационным входам блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига, выходы вышеупомянутых узлов соединены с соответствующими информационными входами элемента ИЛИ, выход которого и первый информационный вход блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига образуют выход блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига, а каждый из вышеупомянутых N узлов, при N=8, без учета ограничения величины сдвига выполняет параллельно следующие логические функции:

- для сдвига на четыре разряда,

- для сдвига на четыре разряда,

- для сдвига на два разряда,

- для сдвига на два разряда,

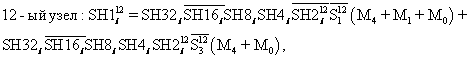

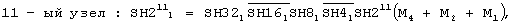

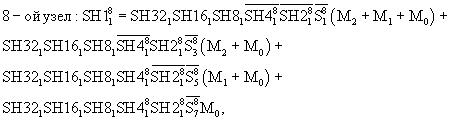

после чего с учетом ограничения величины сдвига для сигнала сдвига на четыре разряда каждый из восьми вышеупомянутых узлов параллельно реализует соответственно одну из следующих логических функций:

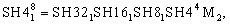

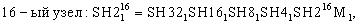

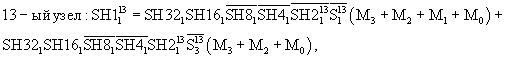

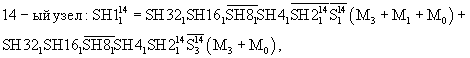

1-ый узел:

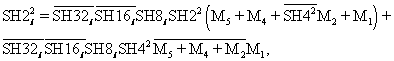

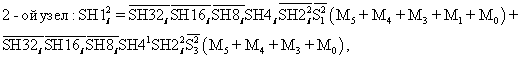

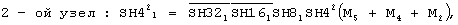

2-ой узел:

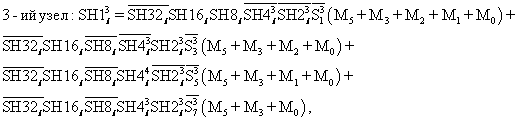

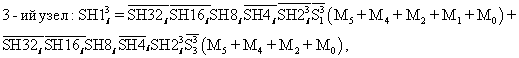

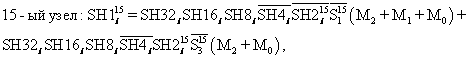

3-ий узел:

4-ый узел:

5-ый узел:

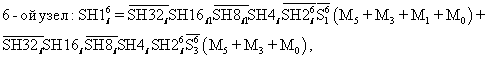

6-ой узел:

7-ой узел:

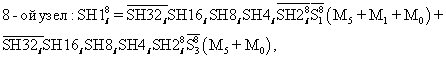

8-ой узел:

SH4l=Σ SH4

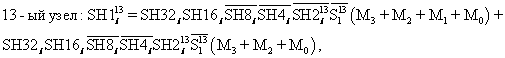

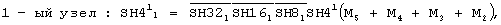

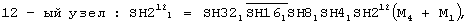

с учетом ограничения величины сдвига для сигнала сдвига на два разряда, каждый из восьми узлов параллельно реализует соответственно одну из следующих логических функций:

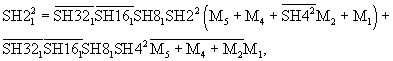

1-ый узел:

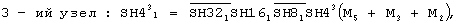

2-ой узел:

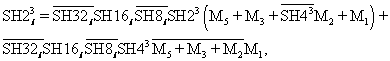

3-ий узел:

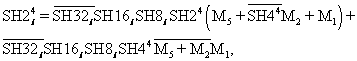

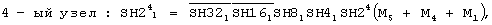

4-ый узел:

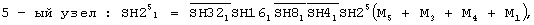

5-ый узел:

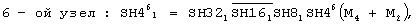

6-ой узел:

7-ой узел:

8-ой узел:

SH2l=Σ SH2

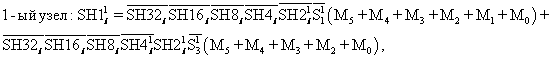

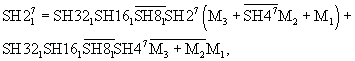

с учетом ограничения величины сдвига для сигнала сдвига на один разряд каждый из восьми узлов параллельно реализует соответственно одну из следующих логических функций:

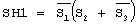

SH1l=Σ SH1

где S

- сдвиг на два разряда,

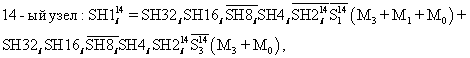

- сдвиг на два разряда,

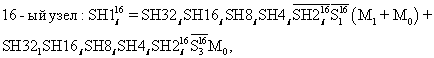

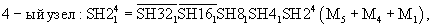

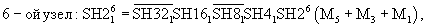

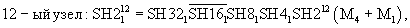

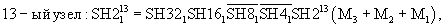

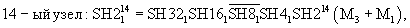

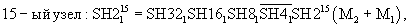

после чего с учетом ограничения величины сдвига для сигнала сдвига на два разряда каждый из шестнадцати узлов параллельно реализует соответственно одну из следующих логических функций:

SH2l=Σ SH2

с учетом ограничения величины сдвига для сигнала сдвига на один разряд каждый из шестнадцати узлов параллельно реализует соответственно одну из следующих логических функций:

SH1l=Σ SH1

где S

- сдвиг на два разряда,

- сдвиг на два разряда,

- сдвиг на один разряд,

- сдвиг на один разряд,

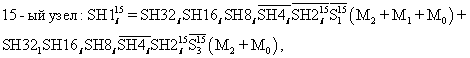

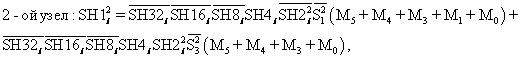

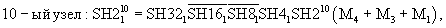

после чего с учетом ограничения величины сдвига этот узел реализует одну из следующих логических функций:

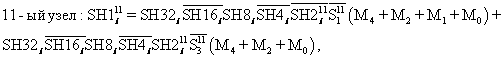

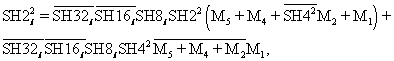

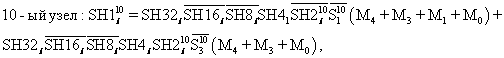

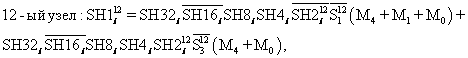

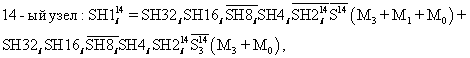

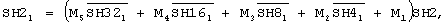

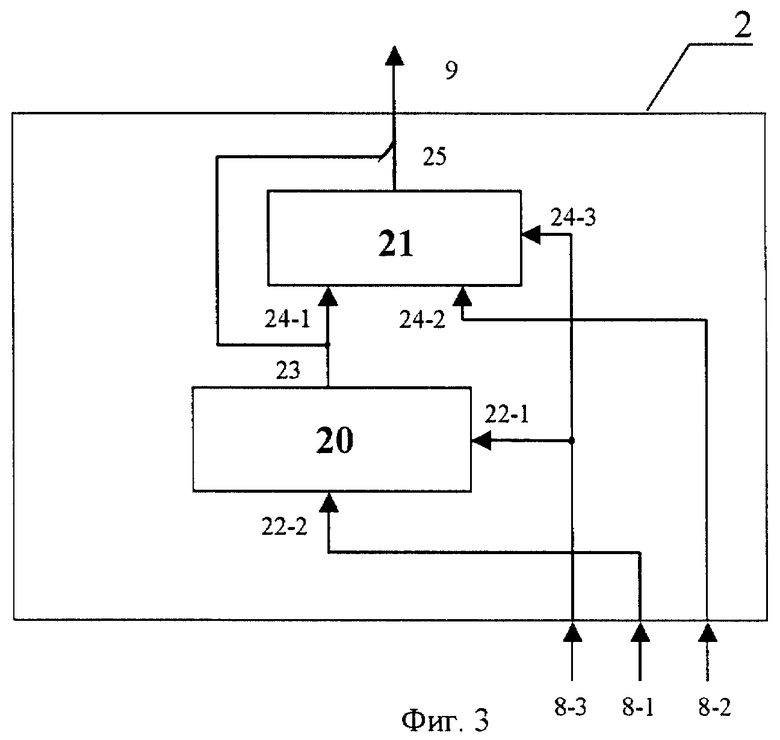

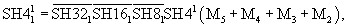

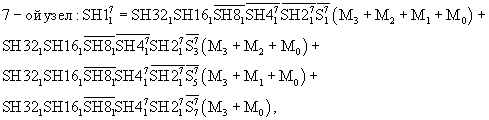

где Si - i-й разряд в старшей тетраде частично нормализованной суммы, являющийся входом блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, SH32l, SH16l, SH8l, SH4l - сигналы кода сдвига с учетом ограничения величины сдвига соответственно на "32", "16", "8" и "4" разряда, поступающие на управляющий вход блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига, SH2 - сигнал сдвига на два разряда в старшей тетраде без учета ограничения величины сдвига, SH2l - сигнал сдвига на два разряда с учетом ограничения, формируемый блоком 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, SH1 - сигнал сдвига на один разряд в старшей тетраде без учета ограничения величины сдвига, SH1l – сигнал сдвига на один разряд с учетом ограничения величины сдвига, формируемый блоком 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, Mk - k-й разряд кода ограничения, являющийся входом блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

Сущность изобретения заключается в том, что выполнение заявляемого устройства вышеописанным образом с использованием блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига, учитывающего предсказанные старшие разряды кода сдвига, сумму и код ограничения, позволяет обеспечить высокое быстродействие при значительном упрощении устройства.

Сравнение заявляемого устройства с ближайшим аналогом позволяет утверждать о соответствии критерию "новизна", а отсутствие в аналогах отличительных признаков заявляемого устройства говорит о соответствии критерию "изобретательский уровень".

Предварительные испытания позволяют судить о возможности широкого промышленного использования.

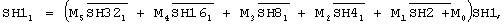

На фиг.1 представлена блок-схема устройства сложения и нормализации чисел с плавающей запятой; на фиг.2 и 3 представлены блок-схемы различных реализаций блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига; на фиг.4-9 представлены примеры реализации логических узлов по соответствующим логическим формулам.

Устройство содержит блок 1 предсказания старших разрядов кода сдвига, блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, сумматор 3 мантисс, нормализатор 4 результата, первый, второй и третий информационные входы 5-1, 5-2 и 5-3 устройства и выход 5-4. Устройство также содержит внутренние связи - первый и второй информационные входы 6-1 и 6-2 блока 1 предсказания старших разрядов кода сдвига, выход 7 сумматора 3 мантисс, первый и второй информационные входы 8-1 и 8-2 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, управляющий вход 8-3 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, выход 9 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, выход 10 блока 1 предсказания старших разрядов кода сдвига, управляющий вход 11-1 и информационный вход 11-2 нормализатора 4.

Первый и второй входы сумматора 3 мантисс являются первыми и вторыми информационными входами 5-1 и 5-2 устройства и присоединены соответственно к первому и второму информационным входам 6-1 и 6-2 блока 1 предсказания старших разрядов кода сдвига, третий информационный вход которого является третьим информационным входом 5-3 устройства, выход 10 узла 1 предсказания старших разрядов кода сдвига соединен с управляющим входом 11-1 нормализатора 4 результата, выход 5-4 которого является выходом устройства, выход 7 сумматора 3 мантисс подключен к первому информационному входу 8-1 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, второй информационный вход 8-2 которого соединен со входом 5-3 кода ограничения блока 1 предсказания старших разрядов кода сдвига, выход 10 которого соединен с управляющим входом 8-3 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, выход 9 которого подключен к информационному входу 11-2 нормализатора 4 результата.

Блок 1 предсказания старших разрядов кода сдвига содержит узлы, формирующие сигналы сдвига на "32", "16", "8" разрядов (см. фиг.7-9 в прототипе) или на "32", "16", "8", "4" разряда (см. фиг.7-10 в прототипе) в зависимости от варианта реализации в устройстве блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, которые могут быть выполнены аналогично соответствующим узлам блока в прототипе и при этом не используется значительная часть его оборудования, которая приходится на младшие разряды кода сдвига (см. соответственно фиг.10-12 или 11-12 в прототипе), что обеспечивает большую экономию.

Сумматор 3 мантисс может быть так же выполнен, как аналогичный блок в прототипе с расширением разрядности слагаемых до 64, что означает использование двойного расширенного формата.

Нормализатор 4 может быть выполнен, как в прототипе, и представляет собой стандартный сдвигатель влево, управляемый в зависимости от реализации шестью сигналами кода сдвига SH32l, SH16l, SH8l, SH4l, SH2l, SH1l либо двумя SH2l, SH1l, когда в нормализатор 4 приходит частично нормализованная с точностью до тетрады сумма.

Блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига может быть реализован различными способами.

Блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, представленный на фиг.2, состоит из восьми 8-ми разрядных узлов и содержит элемент 12 ИЛИ с выходом 13 и узлы 15-1,... , 15-8 определения младших разрядов кода сдвига по группе выходных разрядов сумматора с выходами 16-1,... , 16-8, управляющими входами 17-1,... , 17-8, первыми и вторыми информационными входами 18-1,... , 18-8 и 19-1,... , 19-8 соответственно.

Управляющие, первые и вторые информационные входы 17-1, 17-2,... , 17-8, 18-1, 18-2,... , 18-8 и 19-1, 19-2,... , 19-8 соответствующих узлов 15-1, 15-2,... , 15-8 подключены к соответствующим управляющему, первому и второму информационным входам 8-3, 8-1 и 8-2 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, а их выходы 16-1, 16-2,... , 16-8 соединены с соответствующими информационными входами 14-1, 14-2,... , 14-8 элемента 12 ИЛИ, выход которого и первый информационный вход 8-1 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига образуют выход 9 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

В каждом из узлов 15-1, 15-2,... , 15-8 определения младших разрядов кода сдвига по группе выходных разрядов сумматора вычисляется код сдвига внутри данного узла, исходя из соответствующих 8-ми разрядов суммы, поступающей на его вход.

Причем, если сдвиг на четыре, два или на один разряд принципиально существует, то он определится только в одном соответствующем узле, несмотря на то, что сдвиги на эти разряды могут существовать в любом из 8-ми узлов. Это достигается тем, что каждый сигнал кода сдвига стробирован сигналом, соответствующим номеру узла, который определяется старшими разрядами кода сдвига, сформированными в блоке 1 предсказания старших разрядов кода сдвига. Таким образом, чтобы получить любой младший разряд кода сдвига, достаточно взять из каждой группы соответствующие разряды и объединить их логической операцией ИЛИ.

Работа узлов 15-i, где i=1-8, без учета ограничения величины сдвига описывается следующими формулами:

- для сдвига на четыре разряда,

- для сдвига на четыре разряда,

- для сдвига на два разряда,

- для сдвига на два разряда,

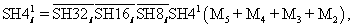

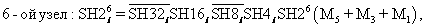

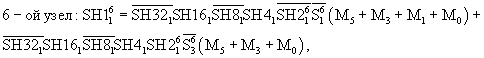

после чего с учетом ограничения величины сдвига для сигнала сдвига на четыре разряда, каждый из восьми узлов 15-i, где i=1-8, параллельно реализует соответственно одну из следующих логических функций:

Тогда сигнал сдвига на четыре разряда, формируемый блоком 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, определяется как логическое сложение кодов сдвига на четыре разряда всех восьми узлов:

SH4l=Σ SH4

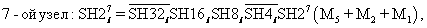

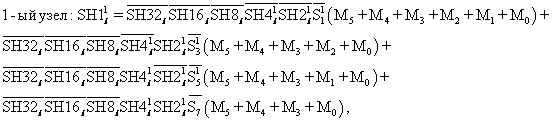

С учетом ограничения величины сдвига для сигнала сдвига на два разряда каждый из восьми узлов параллельно реализует соответственно одну из следующих логических функций:

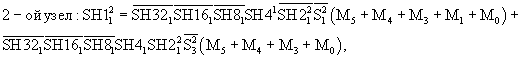

1-й узел:

2-й узел:

3-й узел:

4-й узел:

5-й узел:

6-й узел:

7-й узел:

8-й узел:

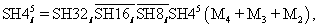

Тогда сигнал сдвига на два разряда, формируемый блоком 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, определяется как логическое сложение кодов сдвига на два разряда всех восьми узлов:

SH2l=Σ SH2

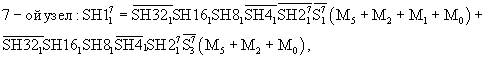

С учетом ограничения величины сдвига для сигнала сдвига на один разряд каждый из восьми узлов параллельно реализует соответственно одну из следующих логических функций:

Тогда сигнал сдвига на один разряд, формируемый блоком 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, определяется как логическое сложение кодов сдвига на один разряд всех восьми узлов:

SH1l=Σ SH1

где S

SH32l, SH16l, SH8l - сигналы кода сдвига с учетом ограничения величины сдвига соответственно на "32", "16", "8" разрядов, поступающие на управляющий вход блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

SH4

SH4l - сигнал сдвига на четыре разряда с учетом ограничения величины сдвига, формируемый блоком определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

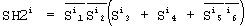

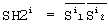

SH2i - сигнал сдвига на два разряда без учета ограничения величины сдвига, формируемый i-м узлом,

SH2

SH2l - сигнал сдвига на два разряда с учетом ограничения величины сдвига, формируемый блоком определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

SH1

SH1l - сигнал сдвига на один разряд с учетом ограничения величины сдвига, формируемый блоком определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

Mk - k-й разряд кода ограничения, являющийся входом блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

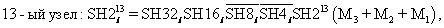

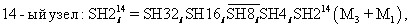

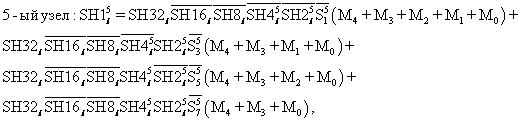

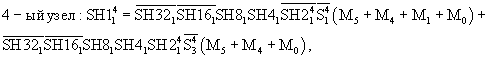

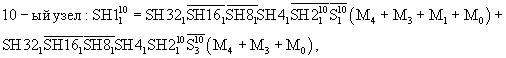

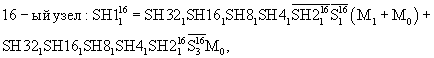

В случае, когда блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига включает в себя шестнадцать 4-разрядных узлов 15-i определения кода сдвига по группе выходных разрядов сумматора, его состав и связи аналогичны блоку 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига и описывается следующими формулами:  - сигнал сдвиг на два разряда без учета ограничения величины сдвига, после чего с учетом ограничения величины сдвига для сигнала сдвига на два разряда каждый из шестнадцати узлов 15-i, где i=1-16, параллельно реализует соответственно одну из следующих логических функций:

- сигнал сдвиг на два разряда без учета ограничения величины сдвига, после чего с учетом ограничения величины сдвига для сигнала сдвига на два разряда каждый из шестнадцати узлов 15-i, где i=1-16, параллельно реализует соответственно одну из следующих логических функций:

Тогда сигнал сдвига на два разряда, формируемый блоком 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, определяется как логическое сложение кодов сдвига на два разряда всех восьми узлов:

SH2l=Σ SH2

С учетом ограничения величины сдвига для сигнала сдвига на один разряд каждый из шестнадцати узлов параллельно реализует соответственно одну из следующих логических функций:

Тогда сигнал сдвига на один разряд, формируемый блоком 2 определения младших разрядов кода сдвига, с учетом ограничения величины сдвига определяется как логическое сложение кодов сдвига на один разряд всех восьми узлов:

SH1l=Σ SH1

где S

SH32l, SH16l, SH8l, SH4l - сигналы кода сдвига с учетом ограничения величины сдвига соответственно на "32", "16", "8", "4" разряда, поступающие на управляющий вход блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

SH2i - сигнал сдвига на два разряда без учета ограничения величины сдвига, формируемый i-м узлом,

SH2

SH2l - сигнал сдвига на два разряда с учетом ограничения величины сдвига, формируемый блоком определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

SH1

SH1l - сигнал сдвига на один разряд с учетом ограничения величины сдвига, формируемый блоком определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

Mk - k-й разряд кода ограничения, являющийся входом блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

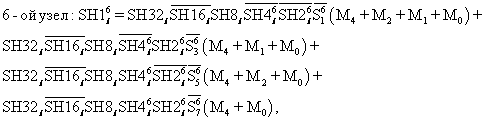

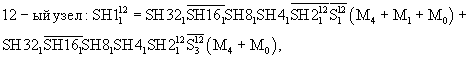

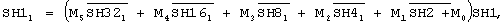

Блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, представленный на фиг.3, содержит нормализатор 20, узел 21 определения младших разрядов кода сдвига в старшей тетраде с учетом ограничения величины сдвига. Нормализатор 20 содержит управляющий вход 22-1 (старшие разряды кода сдвига), информационный вход 22-2 (сумма) и выход 23 (сумма, нормализованная с точностью до тетрады). Узел 21 определения младших разрядов кода сдвига в старшей тетраде с учетом ограничения величины сдвига содержит первый, второй информационные входы 24-1, 24-2, управляющий вход 24-3 (старшие разряды кода сдвига) и выход 25 (младшие разряды кода сдвига).

Информационный вход 22-2 нормализатора 20 подключен к информационному входу 8-1 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, выход 23 нормализатора 20 и выход 25 узла 21 определения младших разрядов кода сдвига в старшей тетраде с учетом ограничения величины сдвига образуют выход 9 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига. Первый информационный вход 24-1 узла 21 определения младших разрядов кода сдвига в старшей тетраде с учетом ограничения величины сдвига соединен с выходом 23 нормализатора 20, управляющий вход 22-1 которого и управляющий вход 24-3 узла 21 определения младших разрядов кода сдвига в старшей тетраде с учетом ограничения величины сдвига подключены к управляющему входу 8-3 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, ко второму информационному входу 8-2 которого подключен второй информационный вход 24-2 узла 21 определения младших разрядов кода сдвига в старшей тетраде с учетом ограничения величины сдвига.

В нормализаторе 20 нормализуется (сдвигается влево) сумма на количество разрядов, равное величине предсказанной блоком 1 предсказания старших разрядов кода сдвига, причем этот блок формирует сдвиги только на "32", "16", "8" и "4" разряда, поэтому сумма нормализуется с точностью до тетрады. Узел 21 определения младших разрядов кода сдвига в старшей тетраде с учетом ограничения величины сдвига, основываясь на анализе старшей тетрады частично нормализованной суммы, определяет коды сдвига на "2" и "1" разряд с учетом и без учета ограничения, соответствующие сигналы которых коммутируются между собой сигналом, определяющим меньшую величину из старших разрядов кода сдвига и кода ограничения.

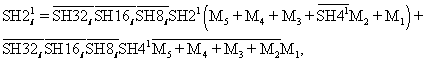

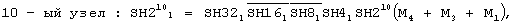

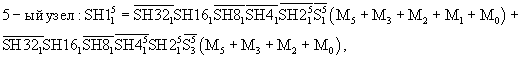

Работа узла 21 определения младших разрядов кода сдвига в старшей тетраде с учетом ограничения величины сдвига при формировании сигналов сдвига на "2" и "1" разряд без учета ограничения величины сдвига описывается следующими формулами:

- сдвиг на два разряда,

- сдвиг на два разряда,

- сдвиг на один разряд,

- сдвиг на один разряд,

после чего с учетом ограничения величины сдвига этот узел реализует следующие логические функции:

где Si - i-й разряд в старшей тетраде частично нормализованной суммы, являющийся входом блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

SH32l, SH16l, SH8l, SH4l - сигналы кода сдвига с учетом ограничения величины сдвига соответственно на "32", "16", "8" и "4" разряда, поступающие на управляющий вход блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

SH2 - сигнал сдвига на два разряда без учета ограничения величины сдвига,

SH2l - сигнал сдвига на два разряда с учетом ограничения величины сдвига, формируемый блоком определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

SH1 - сигнал сдвига на один разряд без учета ограничения величины сдвига,

SH1l - сигнал сдвига на один разряд с учетом ограничения величины сдвига, формируемый блоком определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

Mk - k-й разряд кода ограничения, являющийся входом блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

На фиг.4 изображен фрагмент реализации блока 1 (аналогично фиг.7 в прототипе), при этом выход фрагмента подключен к выходу 10 и формирует сигнал сдвига на "32" разряда. Данный фрагмент содержит узел 26 формирования предварительных сигналов, выходы которого подключены к логическим элементам типа И-ИЛИ-НЕ, которые участвуют в формировании сигнала SH32l. Узел 26 формирования предварительных сигналов выполнен с возможностью формирования логических функций вида ТТ, GG, ZZ, TG, TZ, а также функции распространения и генерации переноса р и g для различного количества разрядов. Логическая функция ТТ для шестнадцати разрядов имеет вид, идентичный прототипу:

TT1-16=T1T2...T16, где Ti=Ai ⊕Bi (Ai и Bi - i-e разряды слагаемых), то есть для получения ТТ1-16 используется логическая операция И на "16" переменных Тi.

Логическая функция GG для шестнадцати разрядов имеет вид, идентичный прототипу:

GG1-16=G1G2...G16, где Gi=Ai •Bi (Ai и Bi - i-e разряды слагаемых), то есть для получения GG1-16 используется логическая операция И на "16" переменных Gi.

Остальные логические функции ZZ, TG, TZ, р, g также имеют вид аналогичных функций прототипа.

Фрагменты реализации блока 1, формирующие сдвиги на "16", "8" и "4" разряда, выполняются аналогично вышеописанному.

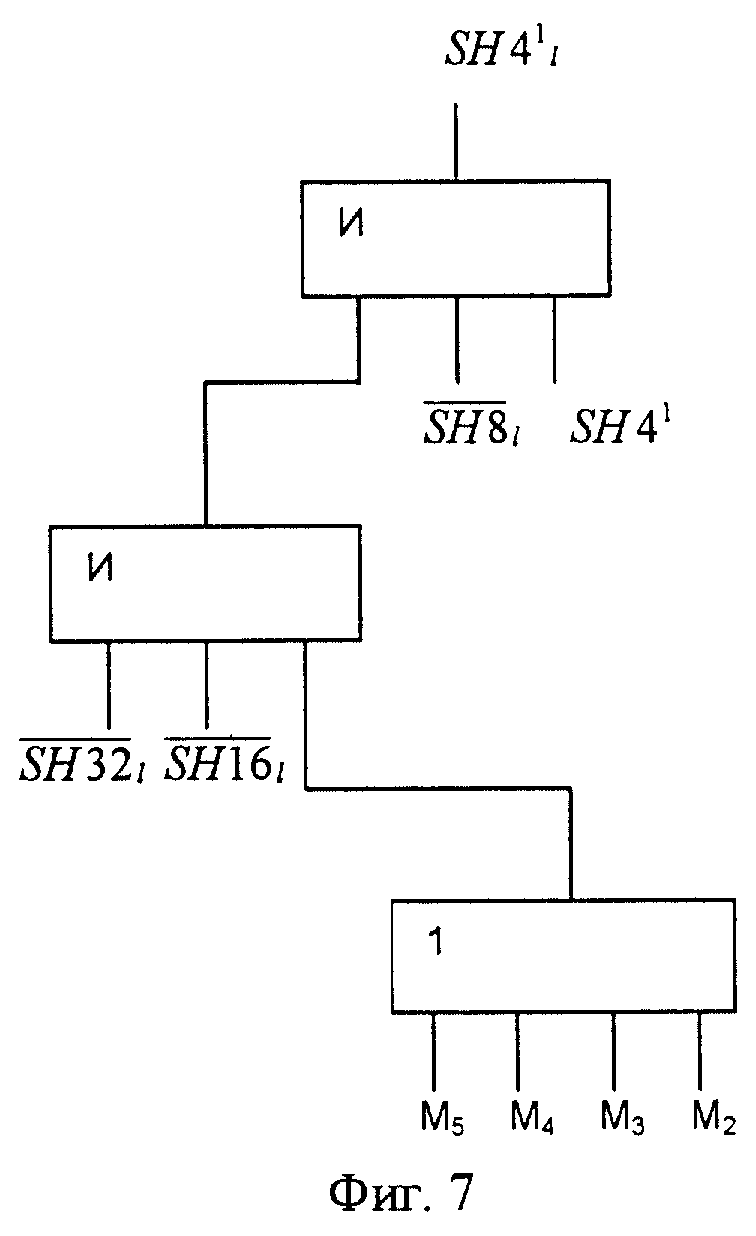

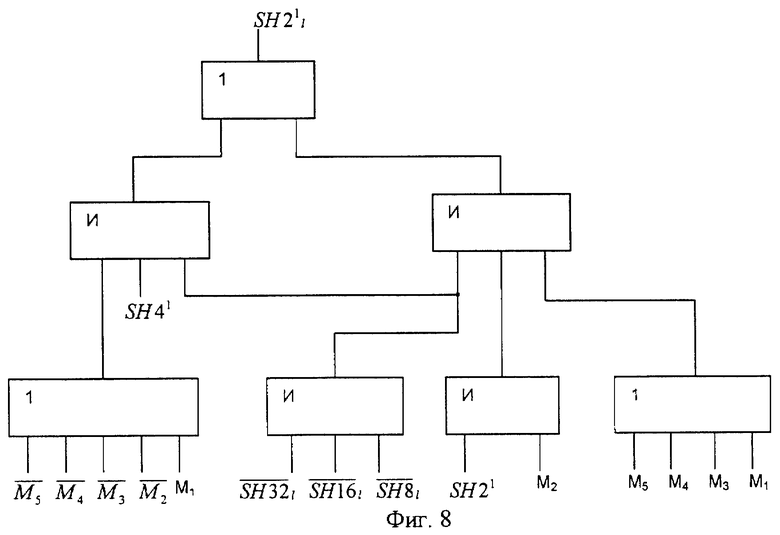

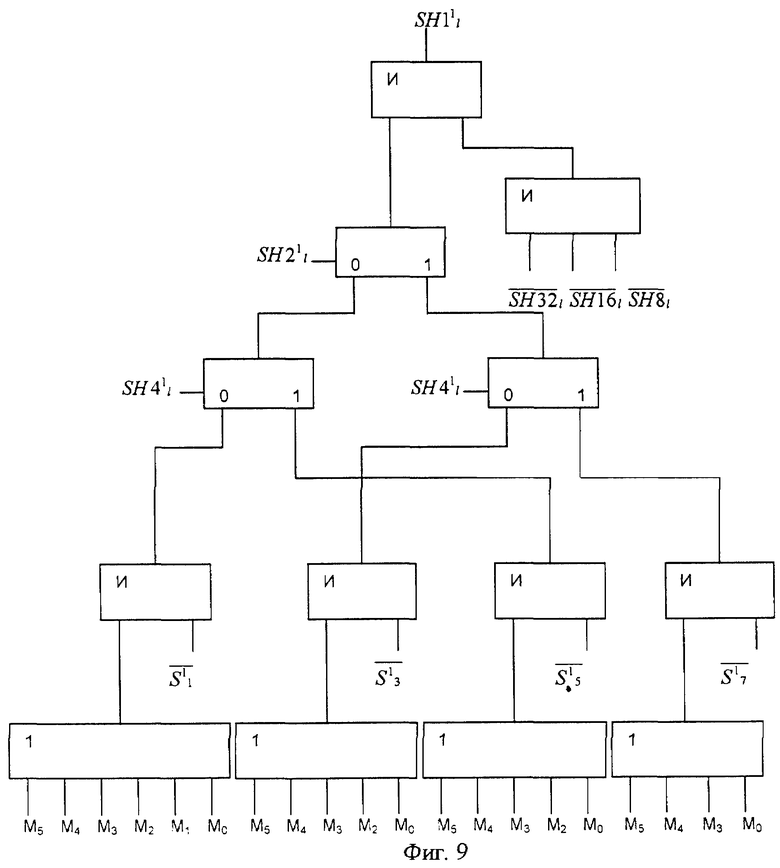

Примеры реализации логических формул для сдвигов на "4" и "2" разряда без учета ограничения в узле 15-1 (1-й узел) определения младших разрядов кода сдвига по группе выходных разрядов сумматора представлены на фиг.5 и 6, а примеры реализации логических формул для сдвигов на "4", "2" и "1" разряд с учетом ограничения в вышеупомянутом узле представлены на фиг.7-9 соответственно.

Таким образом, введение блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига позволяет вместо сложнейшей конструкции блока предсказания кода сдвига прототипа использовать отдельные фрагменты его функциональной схемы для получения блока 1 предсказания старших разрядов кода сдвига, значительно упростив при этом схемотехнику всего устройства.

Устройство работает следующим образом

При N="8" (фиг.2) блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига не нормализует сумму с точностью до тетрады, а блок 1 предсказания старших разрядов кода сдвига предсказывает три старших разряда кода сдвига на "32", "16" и "8" разрядов.

64-разрядные мантиссы чисел по первому и второму информационным входам 5-1 и 5-2 устройства поступают соответственно в сумматор 3 мантисс, а также в блок 1 предсказания старших разрядов кода сдвига по присоединенным к ним первому и второму информационным входам 6-1 и 6-2 вышеупомянутого блока (см. фиг.1). Шестиразрядный код ограничения величины сдвига М по третьему информационному входу 5-3 поступает в блок 1 предсказания старших разрядов кода сдвига и блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига по присоединенному к нему второму информационному входу 8-2 блока 2.

В сумматоре 3 формируется 64-разрядная сумма, которая поступает на первый информационный вход 8-1 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

Блок 1 предсказания старших разрядов кода сдвига, исходя из анализа мантисс слагаемых, кода ограничения величины сдвига М, предсказывает сдвиги на "32", "16" и "8" разрядов, сигналы SH32l, SH16l и SH8l которых поступают на управляющий вход 8-3 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига и на управляющий вход 11-1 нормализатора 4 результата.

Разряды суммы с выхода 7 сумматора 3 мантисс, поступающие на первый информационный вход 8-1 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, разбиты на 8 групп по "8" разрядов в каждой, которые поступают соответственно на информационные входы 18-1, 18-2,... , 18-8 соответствующих узлов 15-1, 15-2,... , 15-8 определения младших разрядов кода сдвига по группе выходных разрядов сумматора. Исходя из анализа соответствующих "8"-ми разрядов суммы соответствующей группы вычисляются сигналы кода сдвига на "2" и "1" разряд без учета ограничения величины сдвига, а далее, учитывая код ограничения величины сдвига М (8-2) и предсказанные старшие разряды кода сдвига SH32l, SH16l и SH8l (8-3), сигналы которых являются входными для каждого из узлов 15-1, 15-2,... , 15-8, в каждом из этих узлов вычисляется код сдвига по соответствующей восьмиразрядной группе выходных разрядов сумматора с учетом ограничения величины сдвига. Причем, если сдвиг на четыре, два или на один разряд принципиально существует, то он определится только в одном соответствующем узле, несмотря на то, что сдвиги на эти разряды могут существовать в любом из узлов 15-i. Это достигается тем, что каждый сигнал кода сдвига стробирован сигналом, соответствующим номеру узла 15-i, который определяется старшими разрядами кода сдвига, поступающими на управляющий вход 8-3 блока 2, сформированными в блоке 1 предсказания старших разрядов кода сдвига. Таким образом, чтобы получить любой младший разряд кода сдвига, достаточно взять из каждого узла 15-1, 15-2,... , 15-8 определения младших разрядов кода по группе выходных разрядов сумматора соответствующие разряды и объединить их логической операцией ИЛИ, что совершается элементом 12 ИЛИ. Таким образом определяются коды сдвига на "4", "2" и "1" разряд, сигналы SH4l, SH2l и SH1l которых вместе с суммой мантисс с выхода 9 блока 2 поступают на информационный вход 11-2 нормализатора 4 результата.

Нормализатор 4 формирует мантиссу результата, сдвигая сумму мантисс влево на количество разрядов, равное величине кода сдвига, старшие разряды которого предсказаны блоком 1 предсказания старших разрядов кода сдвига, а младшие определены блоком 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

При N="16" блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига не нормализует сумму с точностью до тетрады, а блок 1 предсказания старших разрядов кода сдвига предсказывает три старших разряда кода сдвига на "32", "16", "8" и "4" разряда.

64-разрядные мантиссы чисел по первому и второму информационным входам 5-1 и 5-2 устройства поступают соответственно в сумматор 3 мантисс, а также в блок 1 предсказания старших разрядов кода сдвига по присоединенным к ним первому и второму информационным входам 6-1 и 6-2 вышеупомянутого блока (см. фиг.1). Шестиразрядный код ограничения величины сдвига М по третьему информационному входу 5-3 поступает в блок 1 предсказания старших разрядов кода сдвига и блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига по присоединенному к нему второму информационному входу 8-2 блока 2.

В сумматоре 3 формируется 64-разрядная сумма, которая поступает на первый информационный вход 8-1 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

Блок 1 предсказания старших разрядов кода сдвига, исходя из анализа мантисс слагаемых, кода ограничения величины сдвига М, предсказывает сдвиги на "32", "16", "8" и "4" разряда, сигналы SH32l, SH16l, SH8l и SH4l которых поступают на управляющий вход 8-3 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига и на управляющий вход 11-1 нормализатора 4 результата.

Работа блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига в случае, когда он содержит "16" узлов определения кода сдвига по группе выходных разрядов сумматора, аналогична его работе, когда он содержит "8" узлов определения кода сдвига по группе выходных разрядов сумматора. При этом блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига, исходя из анализа суммы, поступающей на его первый информационный вход 8-1 кода ограничения величины сдвига М, поступающей на его второй информационный вход 8-2, и старших разрядов кода сдвига SH32l, SH16l, SH8l и SH4l, поступающих на его управляющий вход 8-3, определяет младшие разряды кода сдвига на "2" и "1" разряд, сигналы SH2l и SH1l которых вместе с суммой мантисс с выхода 9 блока 2 поступают на информационный вход 11-2 нормализатора 4 результата.

Нормализатор 4 формирует мантиссу результата, сдвигая сумму мантисс влево на количество разрядов, равное величине кода сдвига, старшие разряды которого предсказаны блоком 1 предсказания старших разрядов кода сдвига, а младшие определены блоком 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

Когда блок 1 предсказания старших разрядов кода сдвига предсказывает четыре старших разряда кода сдвига на "32", "16", "8" и "4" разряда, а блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига нормализует сумму с точностью до тетрады, устройство работает следующим образом.

64-разрядные мантиссы чисел по первому и второму информационным входам 5-1 и 5-2 устройства поступают соответственно в сумматор 3 мантисс, а также в блок 1 предсказания старших разрядов кода сдвига по присоединенным к ним первому и второму информационным входам 6-1 и 6-2 вышеупомянутого блока (см. фиг.1). Шестиразрядный код ограничения величины сдвига М по третьему информационному входу 5-3 поступает в блок 1 предсказания старших разрядов кода сдвига и блок 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига по присоединенному к нему второму информационному входу 8-2 блока 2.

В сумматоре 3 формируется 64-разрядная сумма, которая поступает на первый информационный вход 8-1 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

Блок 1 предсказания старших разрядов кода сдвига, исходя из анализа мантисс слагаемых, кода ограничения величины сдвига М, предсказывает сдвиги на "32", "16", "8" и "4" разряда, сигналы SH32l, SH16l, SH8l и SH4l которых поступают на управляющий вход 8-3 блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига и на управляющий вход 11-1 нормализатора 4 результата.

У блока 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига в нормализаторе 20 сумма, поступающая на его информационный вход 22-2, нормализуется (сдвигается влево) на количество разрядов, равное величине предсказанной блоком 1 предсказания старших разрядов кода сдвига, причем этот блок формирует сдвиги только на "32", "16", "8" и "4" разряда, сигналы SH32l, SH16l, SH8l и SH4l которых поступают на управляющий вход 8-3 блока 2, поэтому сумма нормализуется с точностью до тетрады. Узел 21 определения младших разрядов кода сдвига в старшей тетраде с учетом ограничения величины сдвига, исходя из анализа частично нормализованной суммы, поступающей на его первый информационный вход 24-1, кода ограничения величины сдвига М, поступающей на его второй информационный вход 24-2, и старших разрядов кода сдвига SH32l, SH16l, SH8l и SH4l, поступающих на его управляющий вход 24-3, определяет младшие разряды кода сдвига на "2" и "1" разряд, сигналы SH2l и SH1l которых вместе с частично нормализованной суммой мантисс с выхода 9 блока 2 поступают на информационный вход 11-2 нормализатора 4 результата.

Нормализатор 4 формирует мантиссу результата, сдвигая частично нормализованную сумму мантисс влево на количество разрядов, равное величине кода сдвига, который определен блоком 2 определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

Таким образом, в заявляемом изобретении достигается требуемый технический результат: значительно упрощается схемотехника устройства и обеспечивается высокое быстродействие.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ПОРЯДКА РЕЗУЛЬТАТА СЛОЖЕНИЯ ЧИСЕЛ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ | 2004 |

|

RU2267806C1 |

| УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ И ОКРУГЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ | 1992 |

|

RU2018921C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

| Устройство для сложения (I) | 1989 |

|

SU1837281A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1989 |

|

SU1656526A2 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1986 |

|

SU1376080A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

Изобретение относится к области вычислительной техники, в частности к устройствам сложения чисел с плавающей запятой, и может быть использовано при разработке арифметических устройств микропроцессоров как универсальных, так и специализированных. Техническим результатом является упрощение устройства с обеспечением необходимого быстродействия. Технический результат достигается за счет того, что в устройство, содержащее блок предсказания старших разрядов кода сдвига, сумматор мантисс и нормализатор результата, введен блок определения младших разрядов кода сдвига с учетом ограничения величины сдвига, причем выход сумматора мантисс подключен к первому информационному входу блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига, второй информационный вход которого соединен с входом кода ограничения блока предсказания старших разрядов кода сдвига, выход которого соединен с управляющим входом блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига, выход которого подключен к информационному входу нормализатора результата. 2 з.п. ф-лы, 9 ил.

- для сдвига на четыре разряда,

- для сдвига на четыре разряда,

- для сдвига на два разряда, после чего с учетом ограничения величины сдвига для сигнала сдвига на четыре разряда каждый из восьми вышеупомянутых узлов параллельно реализует соответственно одну из следующих логических функций:

- для сдвига на два разряда, после чего с учетом ограничения величины сдвига для сигнала сдвига на четыре разряда каждый из восьми вышеупомянутых узлов параллельно реализует соответственно одну из следующих логических функций:

1-ый узел:

2-ой узел:

3-ий узел:

4-ый узел:

5-ый узел:

6-ой узел:

7-ой узел:

8-ой узел:

SH4l=ΣSH4

с учетом ограничения величины сдвига для сигнала сдвига на два разряда, каждый из восьми узлов параллельно реализует соответственно одну из следующих логических функций:

1-ый узел:

2-ой узел:

3-ий узел:

4-ый узел:

5-ый узел:

6-ой узел:

7-ой узел:

8-ой узел:

SH2l=ΣSH2

с учетом ограничения величины сдвига для сигнала сдвига на один разряд, каждый из восьми узлов параллельно реализует соответственно одну из следующих логических функций:

SH1l=ΣSH1

где S

SH32l, SH16l, SH8l - сигналы кода сдвига с учетом ограничения величины сдвига, соответственно, на “32”, “16”, “8” разрядов, поступающие на управляющий вход блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

SH4i - сигнал сдвига на четыре разряда без учета ограничения величины сдвига, формируемый i-ым узлом,

SH4

SH4l - сигнал сдвига на четыре разряда с учетом ограничения величины сдвига, формируемый блоком определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

SH2i - сигнал сдвига на два разряда без учета ограничения величины сдвига, формируемый i-ым узлом,

SH2

SH2l - сигнал сдвига на два разряда с учетом ограничения величины сдвига, формируемый блоком определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

SH1

SH1l - сигнал сдвига на один разряд с учетом ограничения величины сдвига, формируемый блоком определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

Mk - k-ый разряд кода ограничения, являющийся входом блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

а каждый узел для N=16, без учета ограничения величины сдвига, выполняет следующую логическую функцию:

- сдвиг на два разряда,

- сдвиг на два разряда,

после чего с учетом ограничения величины сдвига для сигнала сдвига на два разряда каждый из шестнадцати узлов параллельно реализует соответственно одну из следующих логических функций:

SH2l=ΣSH2

SH1l=ΣSH1

где SH4l - сигнал кода сдвига с учетом ограничения величины сдвига на 4 разряда, поступающий на управляющий вход блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига.

- сдвиг на два разряда,

- сдвиг на два разряда,

- сдвиг на один разряд,

- сдвиг на один разряд,

после чего с учетом ограничения величины сдвига этот узел реализует следующие логические функции:

где Si - i-ый разряд в старшей тетраде частично нормализованной суммы, являющийся входом блока определения младших разрядов кода сдвига с учетом ограничения величины сдвига,

SH2 - сигнал сдвига на два разряда без учета ограничения величины сдвига,

SH1 - сигнал сдвига на один разряд без учета ограничения величины сдвига.

| US 5732007 А, 24.03.1998 | |||

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Суммирующее устройство | 1991 |

|

SU1807480A1 |

| US 4926369 A, 15.09.1990 | |||

| JP 59226944 A, 20.12.1984 | |||

| US 4488252 A, 11.12.1984. | |||

Авторы

Даты

2004-12-10—Публикация

2003-04-29—Подача