Изобретение относится к области электрорадиотехники и может быть использовано в качестве функциональных узлов различных аналоговых микросхем.

Известны источники опорного тока (ИОТ) на базе токовых зеркал, которые стали основой построения современных аналоговых микросхем (AM) различного назначения [1, 2]. Проблема повышения их выходного сопротивления, которое оказывает существенное влияние на качественные показатели AM, относится к числу одной из актуальных проблем современной аналоговой микросхемотехники.

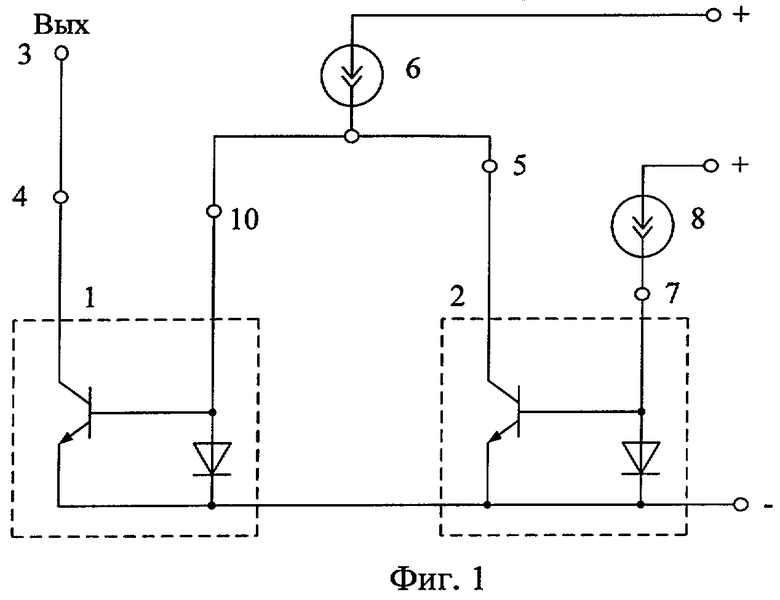

Ближайшим прототипом (фиг.1) заявляемого устройства является источник опорного тока в структуре дифференциального усилителя [Патент США №6201446], содержащий первое и второе токовые зеркала, причем выход источника опорного тока соединен с выходом первого токового зеркала, выход второго токового зеркала подключен к первому токостабилизирующему двухполюснику и ко входу первого токового зеркала, а его вход связан со вторым токостабилизирующим двухполюсником. Устройство-прототип использовалось также в структурах дифференциального усилителя по патенту Японии JP 2003110379 H 03 f, а также патенту США №5714906.

Существенный недостаток известного устройства состоит в том, что оно имеет сравнительно невысокие значения выходного сопротивления, которое для схем с низковольтным питанием (1-1,5 В) лежит в диапазоне десятков килоом. Этот недостаток связан с физическими ограничениями на работу типовых токовых зеркал при данных условиях.

Основная цель предлагаемого изобретения состоит в повышении выходного сопротивления источника опорного тока на 1-2 порядка.

Поставленная цель достигается тем, что в источнике опорного тока, содержащем первое и второе токовые зеркала, имеющие соответствующие входы и выходы, а также первый токостабилизирующий двухполюсник, причем выход источника опорного тока подключен к выходу первого токового зеркала, а вход второго токового зеркала связан с первым токостабилизирующим двухполюсником, вводятся новые элементы и связи - выход источника опорного тока связан со входом дополнительного транзисторного каскада, имеющего эмиттерный и коллекторный выходы, причем эмиттерный выход подключен к выходу второго токового зеркала, а коллекторный выход соединен со входом первого токового зеркала.

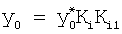

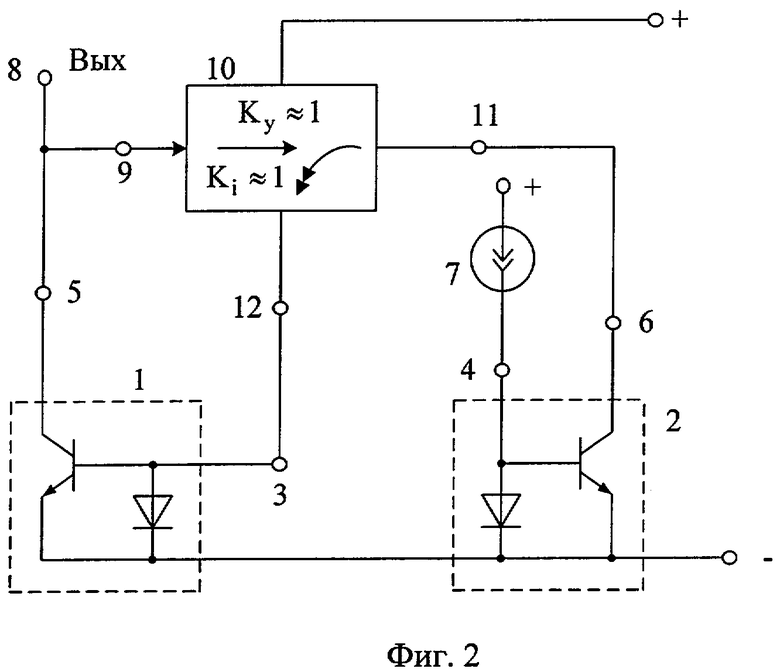

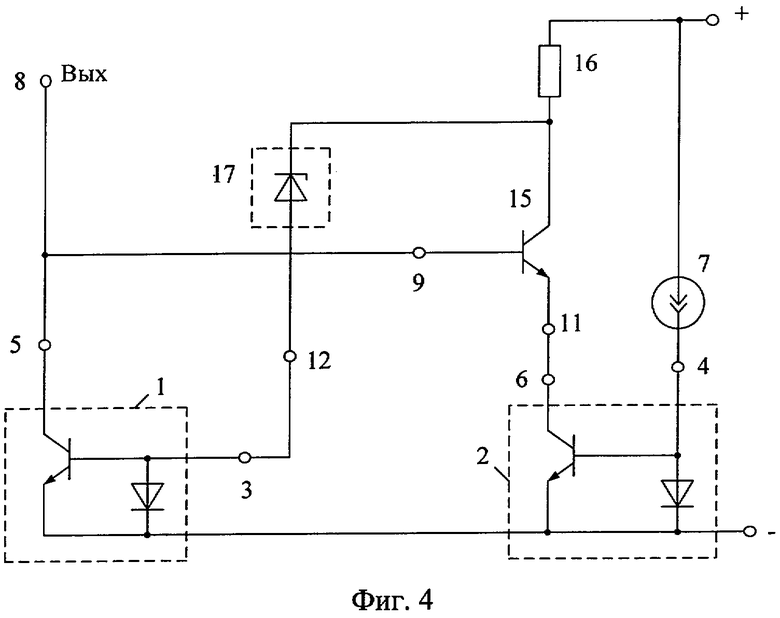

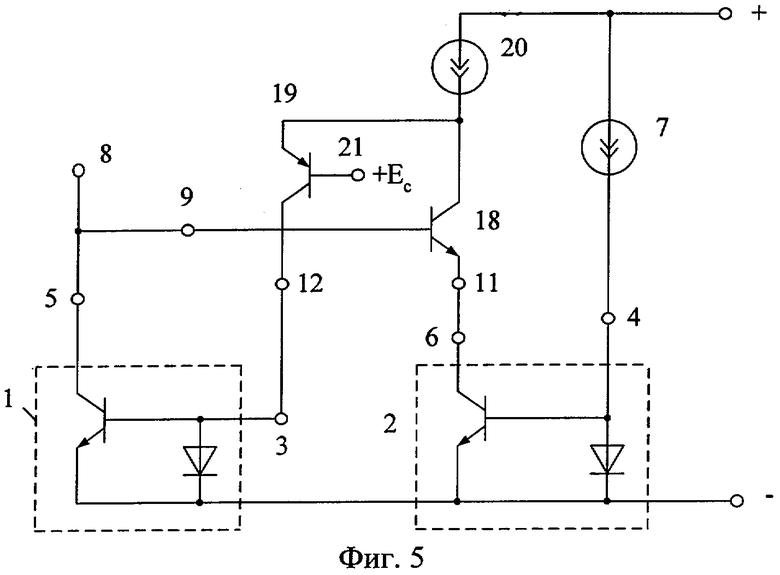

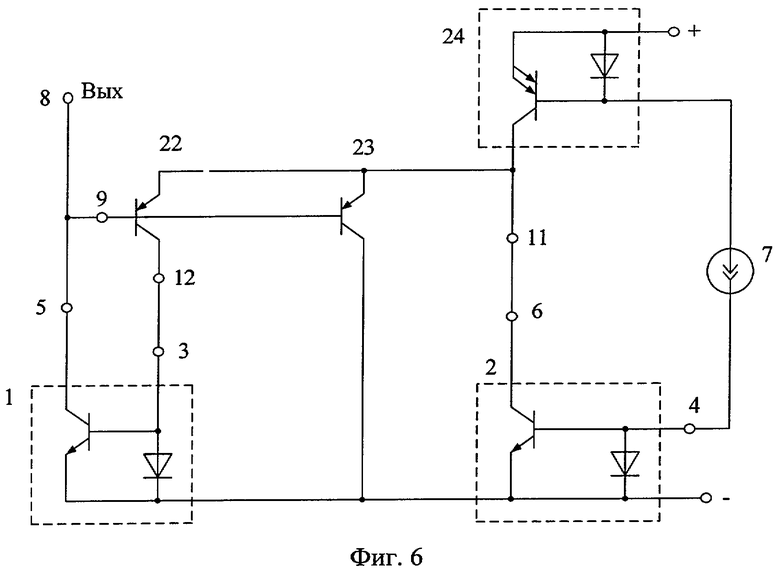

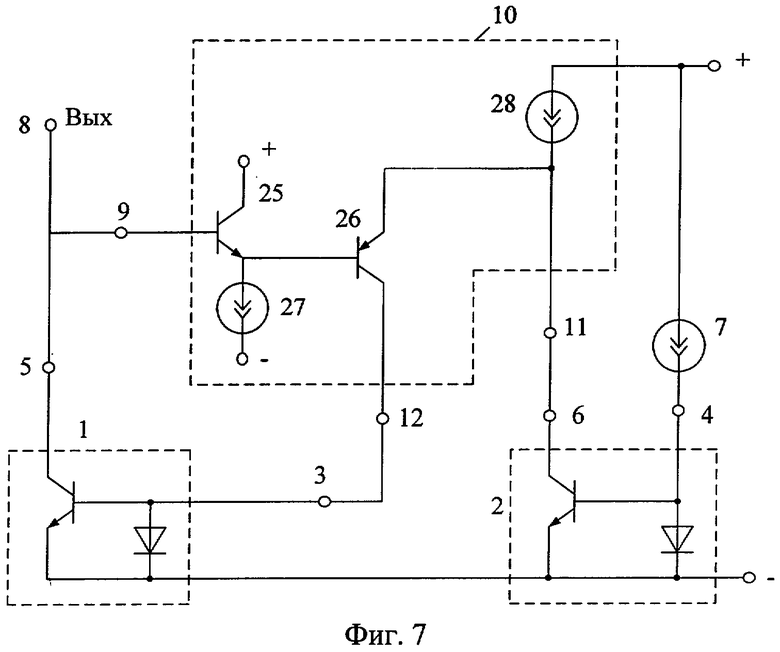

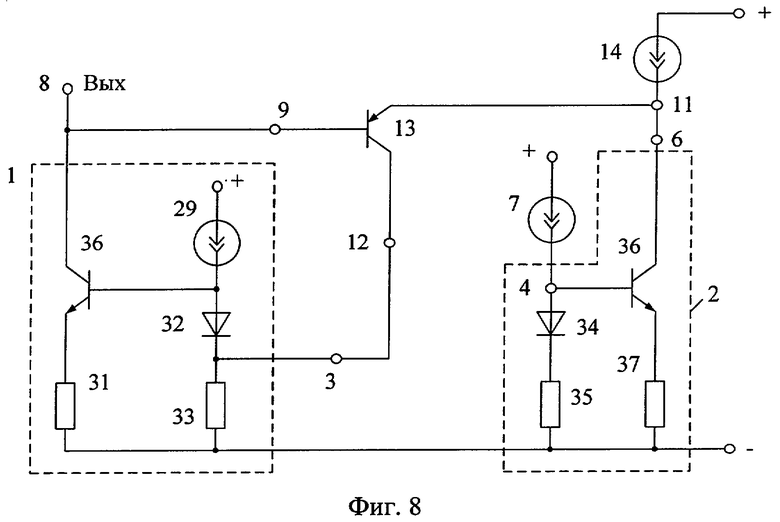

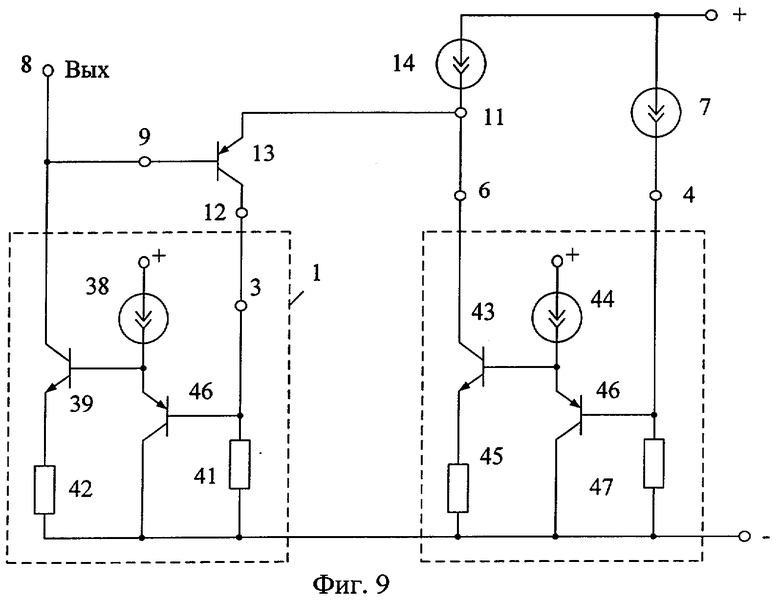

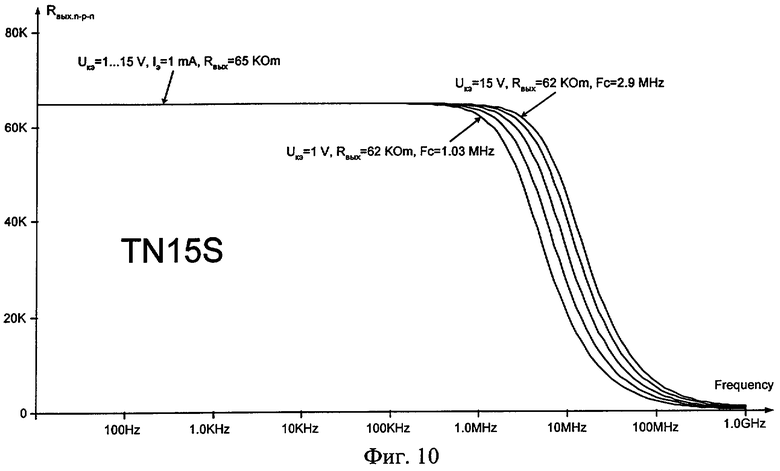

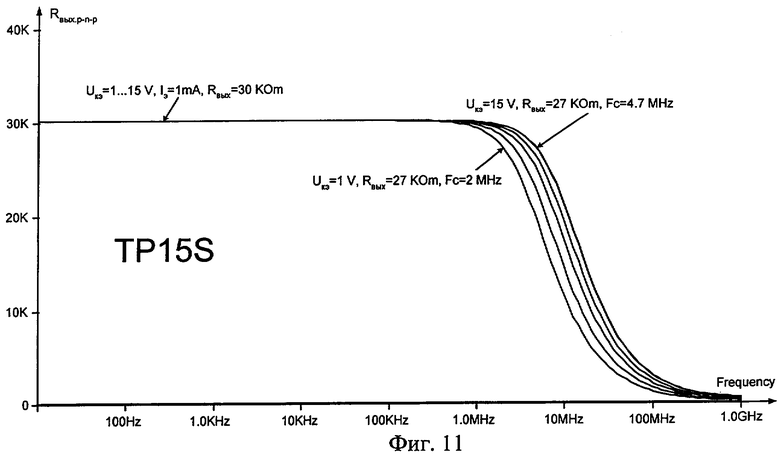

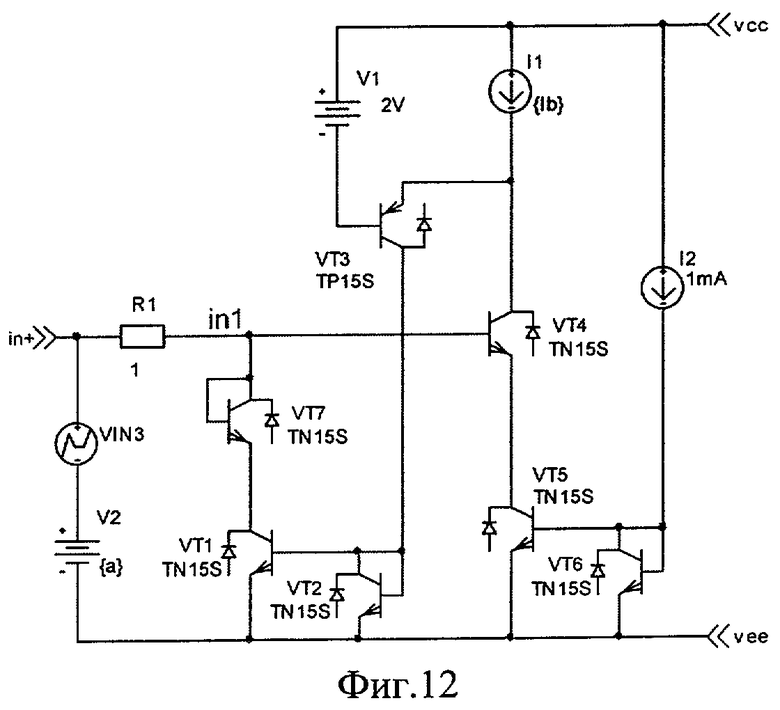

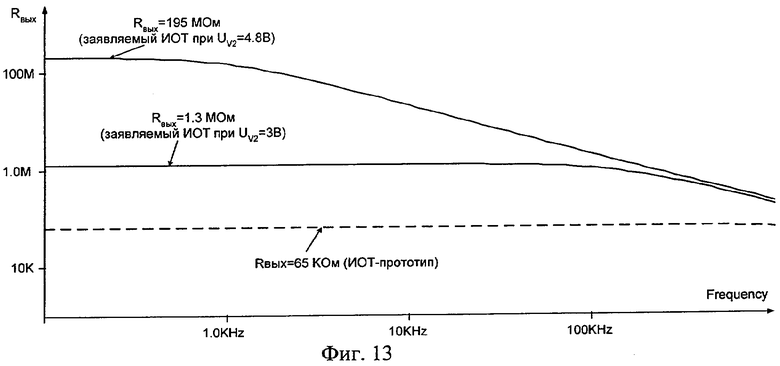

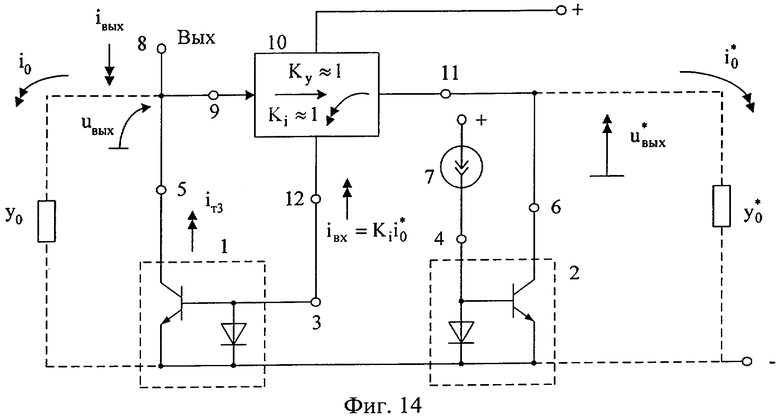

На фиг.2 показана схема заявляемого устройства. На фиг.3, 4, 5, 6, 7 приведены частные варианты построения ИОТ фиг.2, соответствующие пунктам 2-6 формулы изобретения. На фиг.8, 9 приведены схемы ИОТ фиг.3, отличающиеся вариантами построения токовых зеркал 1 и 2. На фиг.10, 11 приведены графики зависимости выходного сопротивления типового токового зеркала на n-р-n (фиг.10) и р-n-р (фиг.11) интегральных биполярных транзисторах в ФГУП "Пульсар" при токах коллектора 1 мА и изменении напряжения Uкэ от 1 до 15 (В). На фиг.12 показана схема исследованного в среде PSpice ИОТ, соответствующего фиг.5. На фиг.13 приведены результаты экспериментального исследования схемы фиг.12 при выходном токе 1 мА и статических значениях источника постоянного напряжения Uv2=3 B и Uv2=4,8 B и прототипа, которые показывают улучшение выходного сопротивления в заявляемой схеме на 1-2 порядка в широком диапазоне частот. На фиг.14 показаны переменные токи и напряжения ИОТ фиг.2.

Предлагаемый источник опорного тока (фиг.2) содержит первое 1 и второе 2 токовые зеркала, имеющие соответственно входы 3, 4 и выходы 5, 6, а также первый токостабилизирующий двухполюсник 7, причем выход 8 источника опорного тока подключен к выходу 5 первого токового зеркала 1, а вход 4 второго токового зеркала 2 связан с первым токостабилизирующим двухполюсником 7. Выход 8 источника опорного тока связан со входом 9 дополнительного транзисторного каскада 10, имеющего эмиттерный 11 и коллекторный 12 выходы, причем эмиттерный выход 11 подключен к выходу 6 второго токового зеркала 2, а коллекторный выход 12 соединен со входом 3 первого токового зеркала 1.

В схеме фиг.3, соответствующей п.2 формулы изобретения, дополнительный транзисторный каскад 10 содержит биполярный р-n-р транзистор 13, эмиттер которого соединен с эмиттерным выходом 11 дополнительного транзисторного каскада 10 и первым вспомогательным токостабилизирующим двухполюсником 14, коллектор является коллекторным выходом дополнительного транзисторного каскада 10, а база соединена со входом 9 дополнительного транзисторного каскада 10.

В схеме фиг.4, соответствующей п.3 формулы изобретения, дополнительный транзисторный каскад 10 выполнен на n-р-n транзисторе 15, эмиттер которого соединен с эмиттерным выходом 11, а коллектор связан со вторым вспомогательным токостабилизирующим двухполюсником 16 и через цепь смещения статического уровня 17 соединен с коллекторным выходом 12 дополнительного транзисторного каскада 10.

В схеме фиг.5, соответствующей п.4 формулы изобретения, дополнительный транзисторный каскад 10 содержит n-р-n транзистор 18, эмиттер которого соединен с эмиттерным выходом 11 дополнительного транзисторного каскада 10, а коллектор связан с эмиттером р-n-р транзистора 19 и третьим вспомогательным токостабилизирующим двухполюсником 20, причем коллектор р-n-р транзистора является коллекторным выходом дополнительного транзисторного каскада 10, база соединена с источником опорного напряжения 21, а база n-р-n транзистора 18 соединена со входом 9 дополнительного транзисторного каскада 10.

В схеме фиг.6, соответствующей п.5 формулы изобретения, дополнительный транзисторный каскад 10 содержит два р-n-р транзистора 22, 23, базы которых соединены со входом 9 дополнительного транзисторного каскада 10, эмиттеры связаны с эмиттерным выходом 11 дополнительного транзисторного каскада 10 и вспомогательным токовым зеркалом 24, коллектор первого р-n-р транзистора 22 соединен с коллекторным выходом 12 дополнительного транзисторного каскада 10, а коллектор второго р-n-р транзистора 23 связан с шиной источника питания.

В схеме фиг.7, соответствующей п.6 формулы изобретения, дополнительный транзисторный каскад 10 содержит n-р-n (25) и р-n-р (26) транзисторы, четвертый 27 и пятый 28 вспомогательные токостабилизирующие двухполюсники, причем эмиттер р-n-р транзистора 26 связан с эмиттерным выходом 11 дополнительного транзисторного каскада 10 и пятым вспомогательным токостабилизирующим двухполюсником 28, коллектор - является коллекторным выходом 12 дополнительного транзисторного каскада, а база - соединена с эмиттером n-р-n транзистора 25 и четвертым 27 токостабилизирующим двухполюсником, база n-р-n транзистора 26 соединена со входом 9 дополнительного транзисторного каскада 10.

На чертеже фиг.8 токовые зеркала 1 и 2 реализованы на элементах 29-37, а в схеме фиг.9 - на элементах 38-47.

Анализ устройства-прототипа.

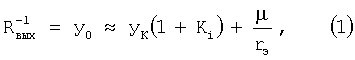

При типовом построении токового зеркала 1 и 2 (фиг.1) на n-р-n транзисторах и Iэ=1÷3 mA (Iэ=Iо - статический ток эмиттера выходного транзистора) выходное сопротивление ИОТ фиг.1 лежит в диапазоне нескольких десятков килоом. Причем

где  - проводимость коллектор-база выходного транзистора токового зеркала 1 в схеме с общей базой;

- проводимость коллектор-база выходного транзистора токового зеркала 1 в схеме с общей базой;

μ4=10-3 - коэффициент внутренней обратной связи выходного транзистора токового зеркала 1 в схеме с общей базой;

- сопротивление эмиттерного перехода выходного транзистора токового зеркала 1 в схеме с общей базой;

- сопротивление эмиттерного перехода выходного транзистора токового зеркала 1 в схеме с общей базой;

Кi≈1 - коэффициент передачи по току токового зеркала 1.

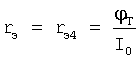

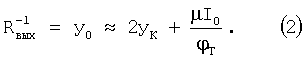

Поэтому

ϕТ = 25 мВ - температурный коэффициент.

Небольшие значения Rвых в схеме известного источника опорного тока (фиг.10, фиг.11) отрицательно сказываются на качественных параметрах многих аналоговых устройств, которые строятся с его использованием.

Анализ заявляемого устройства.

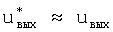

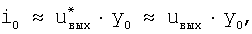

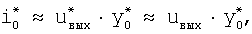

Если на выход источника опорного тока подается сигнал uвх, то напряжение на выходных проводимостях токовых зеркал 1 и 2 у0 и  будет близко к uвх:

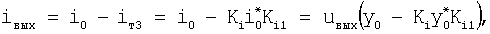

будет близко к uвх:  . Поэтому приращение напряжений и токов в элементах схемы фиг.13 можно определить с учетом законов Ома и Кирхгофа по следующим формулам:

. Поэтому приращение напряжений и токов в элементах схемы фиг.13 можно определить с учетом законов Ома и Кирхгофа по следующим формулам:

где iт3 - приращение выходного тока токового зеркала.

где Ki1 - коэффициент передачи по току токового зеркала 1.

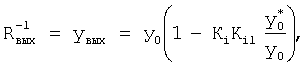

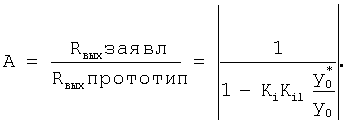

Так как при интегральной технологии и высокой идентичности элементов Ki≈1, Ki1≈1,  выигрыш по выходному сопротивлению заявляемого ИОТ достигает нескольких порядков

выигрыш по выходному сопротивлению заявляемого ИОТ достигает нескольких порядков

Введение новых элементов и связей в соответствии с пп.2-6 формулы изобретения обеспечивает:

- более точное поддержание равенства  , т.е. повышенные значения Rвых в широком диапазоне выходных напряжений рабочих токов ИОТ фиг.2;

, т.е. повышенные значения Rвых в широком диапазоне выходных напряжений рабочих токов ИОТ фиг.2;

- работу ИОТ при малых напряжения питания;

- более широкий допустимый диапазон изменения выходных напряжений ИОТ при заданных значениях выходного сопротивления;

- уменьшение влияния нестабильности источников питания на выходной ток ИОТ.

Компьютерное моделирование частных вариантов заявляемого устройства, выполненное в среде PSpice, подтверждает эффективность рассмотренных схемотехнических решений - выходное сопротивление повышается более чем на 1-2 порядка.

Источники информации

1. Патент США №6201446.

2. Патент США №6680605.

3. Патент США №6373329.

4. Патент США №6456163.

5. Патент США №6680651.

6. Патент США №6737849.

7. Патент США №3829789.

8. Патент США №4879524.

9. Патент США №5399914.

10. Патент США №4241315.

11. Патент США №4013973.

12. Патент США №3992676.

13. Патент ФРГ №2311447.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ПОМЕХИ ПО ПИТАНИЮ | 2007 |

|

RU2331973C1 |

| Безрезистивный арсенид-галлиевый дифференциальный каскад и операционный усилитель на его основе с малым напряжением смещения нуля | 2023 |

|

RU2815912C1 |

| ШИРОКОПОЛОСНЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2432669C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2007 |

|

RU2331968C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ ПО СИНФАЗНОМУ СИГНАЛУ | 2006 |

|

RU2310269C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2331971C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2333593C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319294C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2349023C1 |

| ВЫХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2006 |

|

RU2311729C1 |

Изобретение относится к области электрорадиотехники и может быть использовано в качестве функциональных узлов различных аналоговых микросхем. Техническим результатом изобретения является повышение на 1-2 порядка выходного сопротивления источника опорного тока. Источник опорного тока содержит первое и второе токовые зеркала, имеющие соответствующие входы и выходы, а также первый токостабилизирующий двухполюсник, причем выход источника опорного тока подключен к выходу первого токового зеркала, а вход второго токового зеркала связан с первым токостабилизирующим двухполюсником. Выход источника опорного тока связан со входом дополнительного транзисторного каскада, имеющего эмиттерный и коллекторный выходы, причем эмиттерный выход подключен к выходу второго токового зеркала, а коллекторный выход соединен со входом первого токового зеркала. 5 з.п. ф-лы, 14 ил.

| Источник тока | 1986 |

|

SU1410006A1 |

| US 6201446 А, 13.03.2001 | |||

| US 4879524 А, 07.11.1989. | |||

Авторы

Даты

2006-09-27—Публикация

2005-02-24—Подача