Изобретение относится к радиотехнике и может быть использовано в системах цифровой обработки речи и изображений в реальном масштабе времени.

Известен цифровой фильтр в системе остаточных классов (аналог) [1, с.243, рис.7.4 и рис.7.5], содержащий преобразователь двоичного позиционного кода в код системы остаточных классов, цифровые фильтры по модулю mi ( ; N - количество оснований системы остаточных классов; mi - взаимно простые целые положительные числа) и преобразователь кода системы остаточных классов в двоичный позиционный код. При этом каждый цифровой фильтр по модулю mi содержит 2·К цифровых линий задержки (регистров хранения промежуточных результатов расчета), К сумматоров по модулю mi и К умножителей по модулю mi, где К - порядок цифрового фильтра.

; N - количество оснований системы остаточных классов; mi - взаимно простые целые положительные числа) и преобразователь кода системы остаточных классов в двоичный позиционный код. При этом каждый цифровой фильтр по модулю mi содержит 2·К цифровых линий задержки (регистров хранения промежуточных результатов расчета), К сумматоров по модулю mi и К умножителей по модулю mi, где К - порядок цифрового фильтра.

Недостаток аналога - большая длительность конвейерной задержки в цифровых фильтрах по модулям системы остаточных классов при расчете реакции фильтра на входное воздействие, прямо пропорциональная порядку К цифрового фильтра.

Наиболее близким по технической сущности (прототипом к предлагаемому изобретению) является цифровой фильтр в системе остаточных классов [2, с.10-11, рис.4 и 5], содержащий вычислители по модулю mi ( ; N - количество оснований системы остаточных классов; mi - взаимно простые целые положительные числа) и преобразователь кода системы остаточных классов в код позиционной системы счисления, причем i-й вычислитель по модулю

; N - количество оснований системы остаточных классов; mi - взаимно простые целые положительные числа) и преобразователь кода системы остаточных классов в код позиционной системы счисления, причем i-й вычислитель по модулю  содержит два преобразователя позиционного кода в модулярную дискретно-логарифмическую форму, 2·К сдвиговых регистра хранения цифровых отсчетов сигнала и цифровых отсчетов импульсной характеристики фильтра, К сумматоров по модулю (mi-1), К преобразователей кода из дискретно-логарифмической в модулярную форму (К - порядок цифрового фильтра) и пирамидальный сумматор по модулю mi, состоящий из двухвходовых сумматоров по модулю mi, аналогичных сумматорам в двоичной позиционной системе счисления.

содержит два преобразователя позиционного кода в модулярную дискретно-логарифмическую форму, 2·К сдвиговых регистра хранения цифровых отсчетов сигнала и цифровых отсчетов импульсной характеристики фильтра, К сумматоров по модулю (mi-1), К преобразователей кода из дискретно-логарифмической в модулярную форму (К - порядок цифрового фильтра) и пирамидальный сумматор по модулю mi, состоящий из двухвходовых сумматоров по модулю mi, аналогичных сумматорам в двоичной позиционной системе счисления.

Недостаток прототипа - большая длительность задержки при расчете реакции цифрового фильтра на входное воздействие, прямо пропорциональная количеству ярусов в пирамидальном сумматоре по модулю mi, число которых равно  , где

, где  - символ округления в большую сторону до ближайшего целого числа.

- символ округления в большую сторону до ближайшего целого числа.

Задача, на решение которой направлено заявляемое устройство, состоит в сокращении времени задержки при расчете реакции цифрового фильтра на входное воздействие.

Технический результат выражается в повышении быстродействия выполнения арифметических операций по модулю  при расчете разностного уравнения цифрового фильтра.

при расчете разностного уравнения цифрового фильтра.

Технический результат достигается тем, что в цифровой фильтр в системе остаточных классов, содержащий вычислители по модулю mi ( ; N - количество оснований системы остаточных классов; mi - взаимно простые целые положительные числа) и преобразователь кода системы остаточных классов в код позиционной системы счисления, выход которого является выходом устройства, причем первый и второй входы i-го вычислителя по модулю

; N - количество оснований системы остаточных классов; mi - взаимно простые целые положительные числа) и преобразователь кода системы остаточных классов в код позиционной системы счисления, выход которого является выходом устройства, причем первый и второй входы i-го вычислителя по модулю  подключены соответственно к первому и второму входам цифрового фильтра, а выход i-го вычислителя по модулю mi - к соответствующему входу преобразователя кода системы остаточных классов в код позиционной системы счисления, при этом i-й вычислитель по модулю mi содержит первый и второй преобразователи позиционного кода в модулярную дискретно-логарифмическую форму, входы которых соответственно являются первыми и вторыми входами i-го вычислителя по модулю mi, К последовательно соединенных сдвиговых регистров цифровых отсчетов сигнала, К последовательно соединенных сдвиговых регистров цифровых отсчетов импульсной характеристики фильтра, К сумматоров по модулю (mi-1) и К преобразователей кода из дискретно-логарифмической в модулярную форму (К - порядок цифрового фильтра), при этом вход первого сдвигового регистра цифровых отсчетов сигнала и вход первого сдвигового регистра цифровых отсчетов импульсной характеристики фильтра подключены соответственно к выходу первого и выходу второго преобразователей позиционного кода в модулярную дискретно-логарифмическую форму, причем выходы j-х

подключены соответственно к первому и второму входам цифрового фильтра, а выход i-го вычислителя по модулю mi - к соответствующему входу преобразователя кода системы остаточных классов в код позиционной системы счисления, при этом i-й вычислитель по модулю mi содержит первый и второй преобразователи позиционного кода в модулярную дискретно-логарифмическую форму, входы которых соответственно являются первыми и вторыми входами i-го вычислителя по модулю mi, К последовательно соединенных сдвиговых регистров цифровых отсчетов сигнала, К последовательно соединенных сдвиговых регистров цифровых отсчетов импульсной характеристики фильтра, К сумматоров по модулю (mi-1) и К преобразователей кода из дискретно-логарифмической в модулярную форму (К - порядок цифрового фильтра), при этом вход первого сдвигового регистра цифровых отсчетов сигнала и вход первого сдвигового регистра цифровых отсчетов импульсной характеристики фильтра подключены соответственно к выходу первого и выходу второго преобразователей позиционного кода в модулярную дискретно-логарифмическую форму, причем выходы j-х  сдвиговых регистров цифровых отсчетов сигнала и сдвиговых регистров цифровых отсчетов импульсной характеристики фильтра соединены соответственно с первым и вторым входами j-го

сдвиговых регистров цифровых отсчетов сигнала и сдвиговых регистров цифровых отсчетов импульсной характеристики фильтра соединены соответственно с первым и вторым входами j-го  сумматора по модулю (mi-1), выход которого подключен ко входу j-го преобразователя кода из дискретно-логарифмической в модулярную форму, согласно изобретению в состав цифрового фильтра в системе остаточных классов введен генератор гармонического сигнала, выход которого подключен к третьим входам вычислителей по модулю mi, а в состав вычислителей по модулю mi введены К управляемых фазовращателей и измеритель сдвига фазы, выход которого является выходом i-го вычислителя по модулю

сумматора по модулю (mi-1), выход которого подключен ко входу j-го преобразователя кода из дискретно-логарифмической в модулярную форму, согласно изобретению в состав цифрового фильтра в системе остаточных классов введен генератор гармонического сигнала, выход которого подключен к третьим входам вычислителей по модулю mi, а в состав вычислителей по модулю mi введены К управляемых фазовращателей и измеритель сдвига фазы, выход которого является выходом i-го вычислителя по модулю  , причем первый вход измерителя сдвига фазы и первый вход первого управляемого фазовращателя соединены с третьим входом i-го вычислителя по модулю mi, выход l-го

, причем первый вход измерителя сдвига фазы и первый вход первого управляемого фазовращателя соединены с третьим входом i-го вычислителя по модулю mi, выход l-го  управляемого фазовращателя соединен с первым входом (l+1)-го управляемого фазовращателя, выход К-го управляемого фазовращателя подключен ко второму входу измерителя сдвига фазы, а второй вход j-го

управляемого фазовращателя соединен с первым входом (l+1)-го управляемого фазовращателя, выход К-го управляемого фазовращателя подключен ко второму входу измерителя сдвига фазы, а второй вход j-го  управляемого фазовращателя соединен с выходом j-го

управляемого фазовращателя соединен с выходом j-го  преобразователя кода из дискретно-логарифмической в модулярную форму.

преобразователя кода из дискретно-логарифмической в модулярную форму.

Анализ научно-технической литературы показал, что до даты подачи заявки отсутствовали устройства с указанной совокупностью признаков.

Следовательно, предложение отвечает требованию новизны.

Кроме того, требуемый технический результат достигается всей вновь введенной совокупностью существенных признаков, в частности тем, что в цифровой фильтр введены новые функциональные элементы - генератор гармонического сигнала, последовательно соединенные управляемые фазовращатели и измеритель сдвига фазы.

В известной литературе отсутствуют сведения об использовании указанной совокупности элементов для решения указанной технической задачи.

Следовательно, предложение отвечает требованию изобретательского уровня.

При этом, как будет показано ниже, все использованные в предлагаемом устройстве элементы являются стандартными цифровыми элементами, применяемыми в вычислительной технике, и стандартными элементами радиотехнических устройств СВЧ-диапазона.

Следовательно, предложение отвечает требованию промышленной применимости.

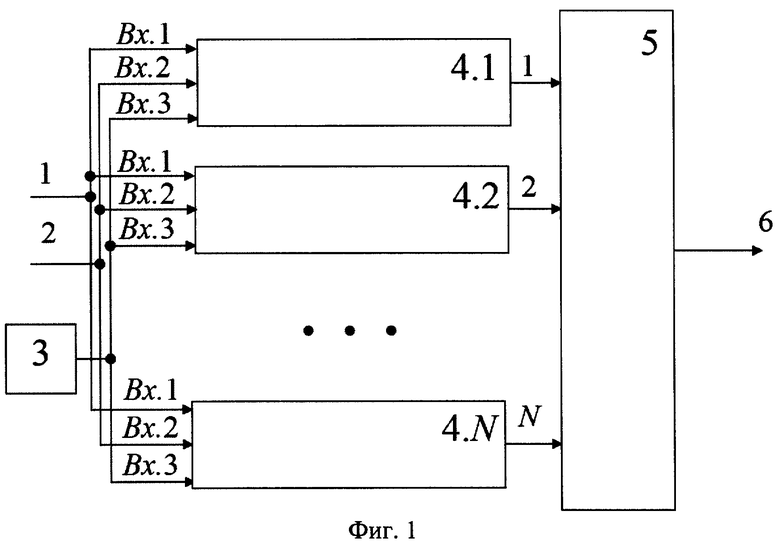

На фиг.1 представлена структурная схема предлагаемого цифрового фильтра в системе остаточных классов, где 1 и 2 - входы цифрового фильтра, 3 - генератор гармонического сигнала, 4.i - вычислитель по модулю  , 5 - преобразователь кода системы остаточных классов в код позиционной системы счисления, 6 - выход цифрового фильтра.

, 5 - преобразователь кода системы остаточных классов в код позиционной системы счисления, 6 - выход цифрового фильтра.

Входы 1 и 2 цифрового фильтра соединены соответственно с входами Вх.1 и Вх.2 вычислителей по модулю mi 4.1-4.N, ко входу Вх.3 которых подключен выход генератора гармонического сигнала 3, при этом выходы вычислителей по модулю mi 4.1-4.N соединены с соответствующими входами преобразователя кода системы остаточных классов в код позиционной системы счисления 5, выход которого является выходом 6 цифрового фильтра в системе остаточных классов.

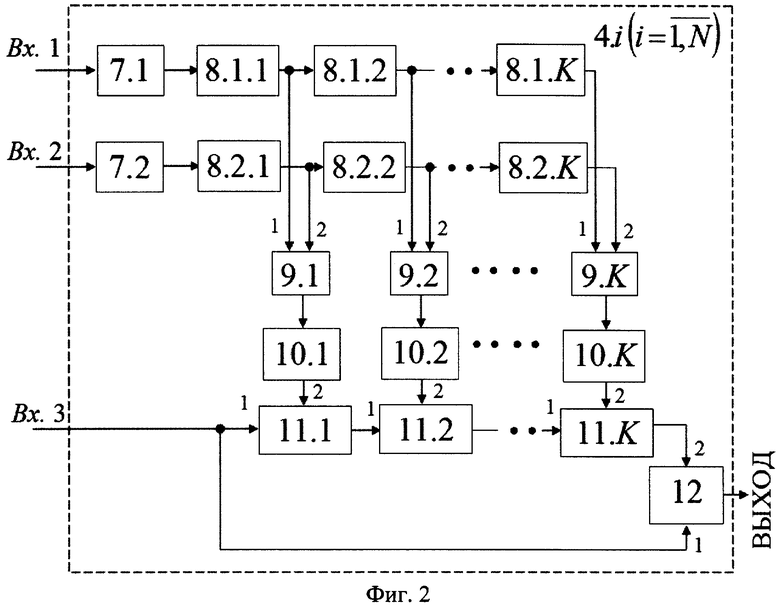

На фиг.2 представлена структурная схема вычислителя по модулю mi 4.i  , где 7.1 и 7.2 - соответственно первый и второй преобразователи позиционного кода в модулярную дискретно-логарифмическую форму, 8.1.1-8.1.K и 8.2.1-8.2.К - соответственно сдвиговые регистры цифровых отсчетов сигнала и сдвиговые регистры цифровых отсчетов импульсной характеристики фильтра, 9.1-9.К - сумматоры по модулю (mi-1), 10.1-10.К - преобразователи кода из дискретно-логарифмической в модулярную форму, 11.1-11.К - управляемые фазовращатели, 12 - измеритель сдвига фазы.

, где 7.1 и 7.2 - соответственно первый и второй преобразователи позиционного кода в модулярную дискретно-логарифмическую форму, 8.1.1-8.1.K и 8.2.1-8.2.К - соответственно сдвиговые регистры цифровых отсчетов сигнала и сдвиговые регистры цифровых отсчетов импульсной характеристики фильтра, 9.1-9.К - сумматоры по модулю (mi-1), 10.1-10.К - преобразователи кода из дискретно-логарифмической в модулярную форму, 11.1-11.К - управляемые фазовращатели, 12 - измеритель сдвига фазы.

Входы первого и второго преобразователей позиционного кода в модулярную дискретно-логарифмическую форму 7.1 и 7.2 соединены соответственно с входами Вх.1 и Вх.2 вычислителя по модулю mi 4.i, а выходы преобразователей 7.1 и 7.2 подключены соответственно ко входу сдвигового регистра цифровых отсчетов сигнала 8.1.1 и ко входу сдвигового регистра цифровых отсчетов импульсной характеристики фильтра 8.2.1, при этом выход регистра 8.1.j соединен со входом регистра 8.1.(j+1) и первым входом сумматора по модулю (mi-1) 9.j  , а выход регистра 8.2.j - со входом регистра 8.2.(j+1) и вторым входом сумматора по модулю (mi-1) 9.j

, а выход регистра 8.2.j - со входом регистра 8.2.(j+1) и вторым входом сумматора по модулю (mi-1) 9.j  , причем выходы регистров 8.1.K и 8.2.K подключены соответственно к первому и второму входам сумматора по модулю (mi-1) 9.К, выход сумматора по модулю (mi-1) 9.l

, причем выходы регистров 8.1.K и 8.2.K подключены соответственно к первому и второму входам сумматора по модулю (mi-1) 9.К, выход сумматора по модулю (mi-1) 9.l  через преобразователь кода из дискретно-логарифмической в модулярную форму 10.l соединен со вторым входом управляемого фазовращателя 11.l, при этом первый вход управляемого фазовращателя 11.1 подключен ко входу Вх.3 вычислителя по модулю mi 4.i и к первому входу измерителя сдвига фазы 12, а выход управляемого фазовращателя 11.j соединен с первым входом управляемого фазовращателя 11.(j+1)

через преобразователь кода из дискретно-логарифмической в модулярную форму 10.l соединен со вторым входом управляемого фазовращателя 11.l, при этом первый вход управляемого фазовращателя 11.1 подключен ко входу Вх.3 вычислителя по модулю mi 4.i и к первому входу измерителя сдвига фазы 12, а выход управляемого фазовращателя 11.j соединен с первым входом управляемого фазовращателя 11.(j+1)  , причем выход управляемого фазовращателя 11.К подключен ко второму входу измерителя сдвига фазы 12, выход которого является выходом вычислителя по модулю mi 4.i.

, причем выход управляемого фазовращателя 11.К подключен ко второму входу измерителя сдвига фазы 12, выход которого является выходом вычислителя по модулю mi 4.i.

Рассмотрим работу цифрового фильтра в системе остаточных классов.

Перед началом работы цифрового фильтра через его вход 2 в регистры 8.2.1-8.2.K вычислителя по модулю mi 4.i  записываются преобразованные из двоичного позиционного кода в дискретно-логарифмическую форму в преобразователе 7.2 цифровые отсчеты импульсной характеристики фильтра.

записываются преобразованные из двоичного позиционного кода в дискретно-логарифмическую форму в преобразователе 7.2 цифровые отсчеты импульсной характеристики фильтра.

Дискретно-логарифмическое представление целого числа а по произвольному целочисленному модулю  здесь применяется для замены выполнения операции умножения по модулю т сложением по модулю (m-1) на основе использования свойств дискретных логарифмов и антилогарифмов [2, с.8-9], где

здесь применяется для замены выполнения операции умножения по модулю т сложением по модулю (m-1) на основе использования свойств дискретных логарифмов и антилогарифмов [2, с.8-9], где  - вычет числа а по модулю m. В этом случае при расчете разностного уравнения цифрового фильтра в вычислителе по модулю mi 4.i

- вычет числа а по модулю m. В этом случае при расчете разностного уравнения цифрового фильтра в вычислителе по модулю mi 4.i  :

:

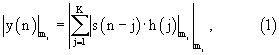

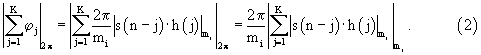

операция умножения по модулю mi цифровых отсчетов импульсной характеристики фильтра h(j) на цифровые отсчеты сигнала s(n-j) может быть заменена более экономной операцией сложения по модулю (mi-1), где у(n) - n-й цифровой отсчет выходного сигнала фильтра.

При поступлении на вход 1 цифрового фильтра цифровых отсчетов сигнала s(n) они из двоичного позиционного кода переводятся в дискретно-логарифмическую форму в преобразователе 7.1 вычислителя по модулю mi 4.i  . Преобразованные цифровые отсчеты сигнала на каждом такте работы цифрового фильтра последовательно "продвигаются" в регистрах 8.1.1-8.1.К. Снимаемые с выхода регистров 8.1.j и 8.2.j

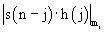

. Преобразованные цифровые отсчеты сигнала на каждом такте работы цифрового фильтра последовательно "продвигаются" в регистрах 8.1.1-8.1.К. Снимаемые с выхода регистров 8.1.j и 8.2.j  данные на каждом такте складываются по модулю (mi-1) в сумматоре 9.j. Тем самым формируется дискретный логарифм произведения

данные на каждом такте складываются по модулю (mi-1) в сумматоре 9.j. Тем самым формируется дискретный логарифм произведения  в разностном уравнении (1) на n-м такте как сумма дискретных логарифмов чисел

в разностном уравнении (1) на n-м такте как сумма дискретных логарифмов чисел  и

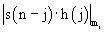

и . Полученный результат сложения затем преобразуется в модулярную форму в преобразователе 10.j. В данном преобразователе осуществляется процедура вычисления дискретного антилогарифма и перехода от представления числа по модулю (mi-1) к представлению по модулю mi числа

. Полученный результат сложения затем преобразуется в модулярную форму в преобразователе 10.j. В данном преобразователе осуществляется процедура вычисления дискретного антилогарифма и перехода от представления числа по модулю (mi-1) к представлению по модулю mi числа  [2, с.8].

[2, с.8].

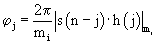

Затем в соответствии с полученным результатом произведения по модулю mi цифрового отсчета сигнала на цифровой отсчет импульсной характеристики фильтра в управляемом фазовращателе 11.j  установится сдвиг фазы на угол

установится сдвиг фазы на угол  . После прохождения через последовательно соединенные управляемые фазовращатели 11.1-11.K гармонического сигнала, поступающего на Вх.3 вычислителя по модулю mi 4.i

. После прохождения через последовательно соединенные управляемые фазовращатели 11.1-11.K гармонического сигнала, поступающего на Вх.3 вычислителя по модулю mi 4.i  с выхода генератора 3, на выходе последнего фазовращателя 11.К установится суммарный набег фазы:

с выхода генератора 3, на выходе последнего фазовращателя 11.К установится суммарный набег фазы:

Из (2) и (1) видно, что суммарный набег фазы в данном случае будет прямо пропорционален величине n-го цифрового отсчета выходного сигнала фильтра у(n) по модулю mi.

В измерителе сдвига фазы 12 происходит сравнение фазы сигнала на выходе генератора 3 и управляемого фазовращателя 11.K и выносится решение о величине модульной суммы  . Этот результат поступает с выхода вычислителя по модулю mi 4.i

. Этот результат поступает с выхода вычислителя по модулю mi 4.i  на соответствующий вход преобразователя кода системы остаточных классов в код позиционной системы счисления 5. В преобразователе 5 на основе китайской теоремы об остатках [2, с.11; 3, с.36] реализуется алгоритм перевода кода числа

на соответствующий вход преобразователя кода системы остаточных классов в код позиционной системы счисления 5. В преобразователе 5 на основе китайской теоремы об остатках [2, с.11; 3, с.36] реализуется алгоритм перевода кода числа  из системы остаточных классов в позиционный код числа у(n). Полученный результат вычисления у(n) подается на выход 6 цифрового фильтра в системе остаточных классов.

из системы остаточных классов в позиционный код числа у(n). Полученный результат вычисления у(n) подается на выход 6 цифрового фильтра в системе остаточных классов.

В качестве элементов для реализации цифрового фильтра в системе остаточных классов могут быть использованы полупроводниковые интегральные постоянные запоминающие устройства при построении преобразователей 7.1, 7.2 и 10.1-10.К, полупроводниковые интегральные триггеры при построении регистров 8.1.1-8.1.К и 8.2.1-8.2.K, двоичные позиционные сумматоры при построении сумматоров 9.1-9.К и преобразователя 5. При реализации генератора 3, управляемых фазовращателей 11.1-11.К и измерителя сдвига фазы 12 могут быть использованы схемные решения СВЧ-техники. В частности, управляемые фазовращатели могут быть реализованы как коммутируемые pin-диодами полосковые линии задержки [4, с.102], а измеритель сдвига фазы может быть выполнен по схеме измерителя неэнергетических параметров сигнала известной формы, построенного в виде набора из mi корреляторов [5, с.488, рис.12.1].

С учетом изложенного сравним быстродействие вычисления разностного уравнения (2) в прототипе и предлагаемом цифровом фильтре.

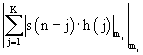

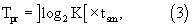

Вследствие применения одинаковых блоков в прототипе и предлагаемом фильтре равно по величине как время преобразования кодов из позиционной системы счисления в модулярную дискретно-логарифмическую форму и в модулярную форму, так и время вычисления сумм по модулю (mi-1). Отличие будет заключаться во времени формирования результатов суммирования К чисел по модулю mi. Как уже отмечалось выше, в прототипе время сложения К чисел по модулю mi будет прямо пропорционально  . С учетом того, что в прототипе сложение К чисел осуществляется в пирамиде двухвходовых сумматоров, общее время формирования данной суммы будет равно:

. С учетом того, что в прототипе сложение К чисел осуществляется в пирамиде двухвходовых сумматоров, общее время формирования данной суммы будет равно:

где tsm - время сложения двух чисел в позиционном сумматоре [2, с.11]: tsm=5×tper; tper - время распространения сигнала переноса в сумматоре.

Так как время формирования сигнала переноса tper не может быть меньше времени переключения полупроводникового логического вентиля tν, то в качестве оценки времени сложения двух чисел можно воспользоваться выражением: tsm≈5×tν. С учетом приведенной в [6, с.173] оценки предельного времени переключения полупроводникового логического вентиля tν=10-10 с, получаем на основании (3) расчетное время формирования в прототипе суммы К чисел по модулю:

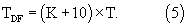

Время вычисления суммы К чисел по модулю в предлагаемом цифровом фильтре будет складываться из времени задержки гармонического сигнала при прохождении через К управляемых фазовращателей и времени принятия решения о значении результата арифметической операции в измерителе сдвига фазы. Учитывая, что поворот фазы на 360 градусов соответствует задержке сигнала на его период Т, максимальное время задержки в управляемых фазовращателях будет равно К·Т. Время принятия решения о значении результата в измерителе сдвига фазы можно оценить продолжительностью протекания переходных процессов в его корреляторах, которое приближенно равно длительности 5...10 периодов гармонического сигнала: (5...10)·T. Таким образом, общее время вычисления суммы К чисел по модулю в предлагаемом цифровом фильтре составит:

Известно [4], что уже сейчас на практике реализованы вплоть до 150 ГГц типовые радиотехнические элементы (в том числе и в интегральном исполнении), на основе которых могут быть построены генератор 3, управляемые фазовращатели 11.1-11.K и измеритель сдвига фазы 12. Тогда при частоте генератора гармонического сигнала ƒ=150 ГГц (T=0,0066 нс) получаем с учетом (5):

Из сравнения (4) и (6) видно, что предлагаемый цифровой фильтр предпочтительнее прототипа, если

Данное условие выполняется при К<740.

Таким образом, если порядок цифрового фильтра не превышает величины 740, то предлагаемая архитектура цифрового фильтра в системе остаточных классов предпочтительнее прототипа.

Источники информации

1. Нейрокомпьютеры в остаточных классах. Кн.11 (Червяков Н.И., Сахнюк П.А., Шапошников А.В., Макоха А.Н.): Учеб. пособие для вузов. - М.: Радиотехника, 2003. - 272 с.

2. Амербаев В.М., Стемпковский А.Л., Широ Г.Э. Быстродействующий согласованный фильтр, построенный по модулярному принципу // Информационные технологии, 2004, №9, с.5-12.

3. Акушский И.Я., Юдицкий Д.И. Машинная арифметика в остаточных классах. - М.: Сов. Радио, 1968. - 440 с.

4. Радиоприемные устройства: Учеб. пособие для радиотехнич. спец. вузов / Ю.Т.Давыдов, Ю.С.Данилич, А.П.Жуковский. - М.: Высш. шк., 1989. - 342 с.

5. Тихонов В.И. Статистическая радиотехника. - М.: Сов. радио, 1966. - 678 с.

6. Акаев А.А., Майоров С.А. Оптические методы обработки информации. - М.: Высш. шк., 1988. - 237 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ФИЛЬТР В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2005 |

|

RU2291557C1 |

| СИНТЕЗАТОР ЧАСТОТЫ | 2002 |

|

RU2237972C2 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЛА В МОДУЛЯРНОМ КОДЕ НА ОСНОВАНИЕ СИСТЕМЫ СЧИСЛЕНИЯ | 2002 |

|

RU2237274C2 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЛА В МОДУЛЯРНОМ КОДЕ НА ОСНОВАНИЕ СИСТЕМЫ СЧИСЛЕНИЯ | 2002 |

|

RU2231822C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ГАРМОНИЧЕСКИХ КОЛЕБАНИЙ | 2003 |

|

RU2239281C2 |

| УСТРОЙСТВО ДЛЯ МАСШТАБИРОВАНИЯ ЧИСЛА В МОДУЛЯРНОЙ СИСТЕМЕ СЧИСЛЕНИЯ | 2002 |

|

RU2246753C2 |

| ФОРМИРОВАТЕЛЬ ПЕРИОДИЧЕСКИХ СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2003 |

|

RU2271602C2 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ К ЧИСЕЛ ПО МОДУЛЮ М | 2017 |

|

RU2653312C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2744475C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

Изобретение относится к радиотехнике. Его использование в системах цифровой обработки речи и изображений в реальном масштабе времени позволяет получить технический результат в виде повышения быстродействия выполнения арифметических операций по модулю при расчете разностного уравнения цифрового фильтра. Цифровой фильтр в системе остаточных классов включает в свой состав генератор гармонического сигнала, преобразователь кода системы остаточных классов в код позиционной системы счисления и N вычислителей по модулю, каждый из которых содержит преобразователи позиционного кода в модулярную дискретно-логарифмическую форму, сдвиговые регистры цифровых отсчетов сигнала и сдвиговые регистры цифровых отсчетов импульсной характеристики фильтра, сумматоры по модулю, преобразователи кода из дискретно-логарифмической в модулярную форму, управляемые фазовращатели и измеритель сдвига фазы. 2 ил.

Цифровой фильтр в системе остаточных классов, содержащий вычислители по модулю mi ( ; N - количество оснований системы остаточных классов; mi - взаимно простые целые положительные числа) и преобразователь кода системы остаточных классов в код позиционной системы счисления, выход которого является выходом устройства, причем первый и второй входы i-го вычислителя по модулю mi(

; N - количество оснований системы остаточных классов; mi - взаимно простые целые положительные числа) и преобразователь кода системы остаточных классов в код позиционной системы счисления, выход которого является выходом устройства, причем первый и второй входы i-го вычислителя по модулю mi( ) подключены соответственно к первому и второму входу цифрового фильтра, а выход i-го вычислителя по модулю mi - к соответствующему входу преобразователя кода системы остаточных классов в код позиционной системы счисления, при этом i-ый вычислитель по модулю mi содержит первый и второй преобразователи позиционного кода в модулярную дискретно-логарифмическую форму, входы которых соответственно являются первыми и вторыми входами i-го вычислителя по модулю mi, К последовательно соединенных сдвиговых регистров цифровых отсчетов сигнала, К последовательно соединенных сдвиговых регистров цифровых отсчетов импульсной характеристики фильтра, К сумматоров по модулю (mi-1) и К преобразователей кода из дискретно-логарифмической в модулярную форму (К - порядок цифрового фильтра), при этом вход первого сдвигового регистра цифровых отсчетов сигнала и вход первого сдвигового регистра цифровых отсчетов импульсной характеристики фильтра подключены соответственно к выходу первого и выходу второго преобразователей позиционного кода в модулярную дискретно-логарифмическую форму, причем выходы j-ых

) подключены соответственно к первому и второму входу цифрового фильтра, а выход i-го вычислителя по модулю mi - к соответствующему входу преобразователя кода системы остаточных классов в код позиционной системы счисления, при этом i-ый вычислитель по модулю mi содержит первый и второй преобразователи позиционного кода в модулярную дискретно-логарифмическую форму, входы которых соответственно являются первыми и вторыми входами i-го вычислителя по модулю mi, К последовательно соединенных сдвиговых регистров цифровых отсчетов сигнала, К последовательно соединенных сдвиговых регистров цифровых отсчетов импульсной характеристики фильтра, К сумматоров по модулю (mi-1) и К преобразователей кода из дискретно-логарифмической в модулярную форму (К - порядок цифрового фильтра), при этом вход первого сдвигового регистра цифровых отсчетов сигнала и вход первого сдвигового регистра цифровых отсчетов импульсной характеристики фильтра подключены соответственно к выходу первого и выходу второго преобразователей позиционного кода в модулярную дискретно-логарифмическую форму, причем выходы j-ых  сдвиговых регистров цифровых отсчетов сигнала и сдвиговых регистров цифровых отсчетов импульсной характеристики фильтра соединены соответственно с первым и вторым входом j-го

сдвиговых регистров цифровых отсчетов сигнала и сдвиговых регистров цифровых отсчетов импульсной характеристики фильтра соединены соответственно с первым и вторым входом j-го  сумматора по модулю (mi-1), выход которого подключен ко входу j-го преобразователя кода из дискретно-логарифмической в модулярную форму, отличающийся тем, что в него введен генератор гармонического сигнала, выход которого подключен к третьим входам вычислителей по модулю mi, а в состав вычислителей по модулю mi введены К управляемых фазовращателей и измеритель сдвига фазы, выход которого является выходом i-го вычислителя по модулю

сумматора по модулю (mi-1), выход которого подключен ко входу j-го преобразователя кода из дискретно-логарифмической в модулярную форму, отличающийся тем, что в него введен генератор гармонического сигнала, выход которого подключен к третьим входам вычислителей по модулю mi, а в состав вычислителей по модулю mi введены К управляемых фазовращателей и измеритель сдвига фазы, выход которого является выходом i-го вычислителя по модулю  , причем первый вход измерителя сдвига фазы и первый вход первого управляемого фазовращателя соединены с третьим входом i-го вычислителя по модулю mi, выход 1-го

, причем первый вход измерителя сдвига фазы и первый вход первого управляемого фазовращателя соединены с третьим входом i-го вычислителя по модулю mi, выход 1-го  управляемого фазовращателя соединен с первым входом (1+1)-го управляемого фазовращателя, выход К-го управляемого фазовращателя подключен ко второму входу измерителя сдвига фазы, а второй вход j-го

управляемого фазовращателя соединен с первым входом (1+1)-го управляемого фазовращателя, выход К-го управляемого фазовращателя подключен ко второму входу измерителя сдвига фазы, а второй вход j-го  управляемого фазовращателя соединен с выходом j-го

управляемого фазовращателя соединен с выходом j-го  преобразователя кода из дискретно-логарифмической в модулярную форму.

преобразователя кода из дискретно-логарифмической в модулярную форму.

| Цифровой фильтр | 1984 |

|

SU1246344A1 |

| Цифровой согласованный фильтр | 1985 |

|

SU1272475A1 |

| Адаптивный цифровой фильтр | 1986 |

|

SU1387173A1 |

| JP 61029208 A, 10.02.1986 | |||

| СПОСОБ СТИМУЛЯЦИИ РЕПАРАТИВНЫХ И ТРОФИЧЕСКИХ ПРОЦЕССОВ В ТКАНЯХ ОРГАНИЗМА | 1994 |

|

RU2095067C1 |

Авторы

Даты

2006-11-20—Публикация

2005-07-11—Подача