Изобретение относится к области вычислительной техники и цифровой автоматики. Известен накапливающий сумматор (далее - объект), рассмотренный в книге М.А.Карцева Арифметика цифровых машин, М., Наука, 1969, стр.247, рис.2-45, а также объекты по а.с. 911517 и а.с. 1043638. Недостатками указанных объектов является наличие в каждом разряде двух триггеров и элемента временной задержки импульсов, поступающих на счетный вход триггера, что усложняет объект и снижает его быстродействие. Кроме того, для построения каждого разряда требуется два триггера, что усложняет устройство, повышает потребление электропитания и стоимость объекта. Наиболее близкими, принятыми за прототип, является накапливающий сумматор по а.с. 1291968. Каждый разряд прототипа выполнен только на основе логических элементов И, ИЛИ, НЕ и одного RS-триггера. Аппаратурные затраты для построения одного разряда прототипа, оцениваемые суммарным числом входов логических элементов, равны 32 (цена Квайна), и являются минимальными для известных сумматоров рассматриваемого класса. Однако и прототип имеет рад недостатков. Основной недостаток заключается в том, что объект не выполняет операцию сдвига кода вправо, что не позволяет использовать его для выполнения операций умножения (деления). Кроме того, не выполняются операции сдвига кода влево, инвертирования, логического сложения и логического умножения. Целью изобретения является расширение функциональных возможностей объекта за счет выполнения дополнительных операций (сдвиг вправо, сдвиг влево, инвертирование, логическое сложение и логическое умножение, установка нуля, прием единицы) при минимальных затратах аппаратурных средств. Заметим, что расширение перечня выполняемых операций позволяет снизить время вычислительных задач за счет исключения излишних пересылок кодов в другие блоки и устройства для выполнения операций, которые не выполняет конкретный объект, например прототип.

Для устранения отмеченных недостатков известных устройств предложен объект, выполненный на логических элементах И, ИЛИ, НЕ, содержащий в каждом разряде один RS-триггер, шесть элементов И, четыре элемента ИЛИ, три элемента НЕ, пять входов управления, вход установки нуля и информационный вход, при этом первые входы первого и второго элементов И соединены с первым и вторым входами управления соответственно, вторые входы упомянутых элементов И связаны с информационным входом и выходом переноса из младшего разряда соответственно, выходы этих элементов И подключены к первому и второму входам первого элемента ИЛИ, выход которого связан с первым входами третьего и четвертого элементов И, вторые входы этих элементов И соединены с входом и выходом первого элемента НЕ, выходы третьего и четвертого элементов И через третий и четвертый элементы НЕ подключены к R- и S-входу RS-триггера соответственно, единичный выход триггера соединен с первым входом второго элемента ИЛИ, второй его выход связан с выходом третьего элемента И, третий выход соединен с третьим входом управления, а его выход подключен к первому входу пятого элемента И, второй вход этого элемента И соединен с четвертым входом управления, третий вход подключен к S-входу RS-триггера, выход пятого элемента И соединен с входом первого элемента НЕ, и с первым входом третьего элемента ИЛИ, второй вход упомянутого элемента ИЛИ подключен к выходу первого элемента И, третий входы третьего и четвертого элементов ИЛИ соединена с выходом шестого элемента И, первый вход четвертого элемента ИЛИ соединен с выходом переноса из младшего разряда, выходы третьего и четвертого элементов ИЛИ подключены к первому и второму входам шестого элемента И, к его третьему входу подключен пятый вход управления, выход шестого элемента И является входом переноса в старший разряд, отличающийся тем, что в каждый разряд введены пятый и шестой элементы ИЛИ, шестой и седьмой входы управления, при этом первые входы пятого и шестого элементов ИЛИ соединены с шестым входом управления, вторые входы упомянутых элементов подключены к выходам первого элемента НЕ и пятого элемента И старшего разряда соответственно, выходы пятого и шестого элементов ИЛИ соединены с третьими входами третьего и четвертого элементов И соответственно, седьмой вход управления соединен с третьим входом первого элемента ИЛИ.

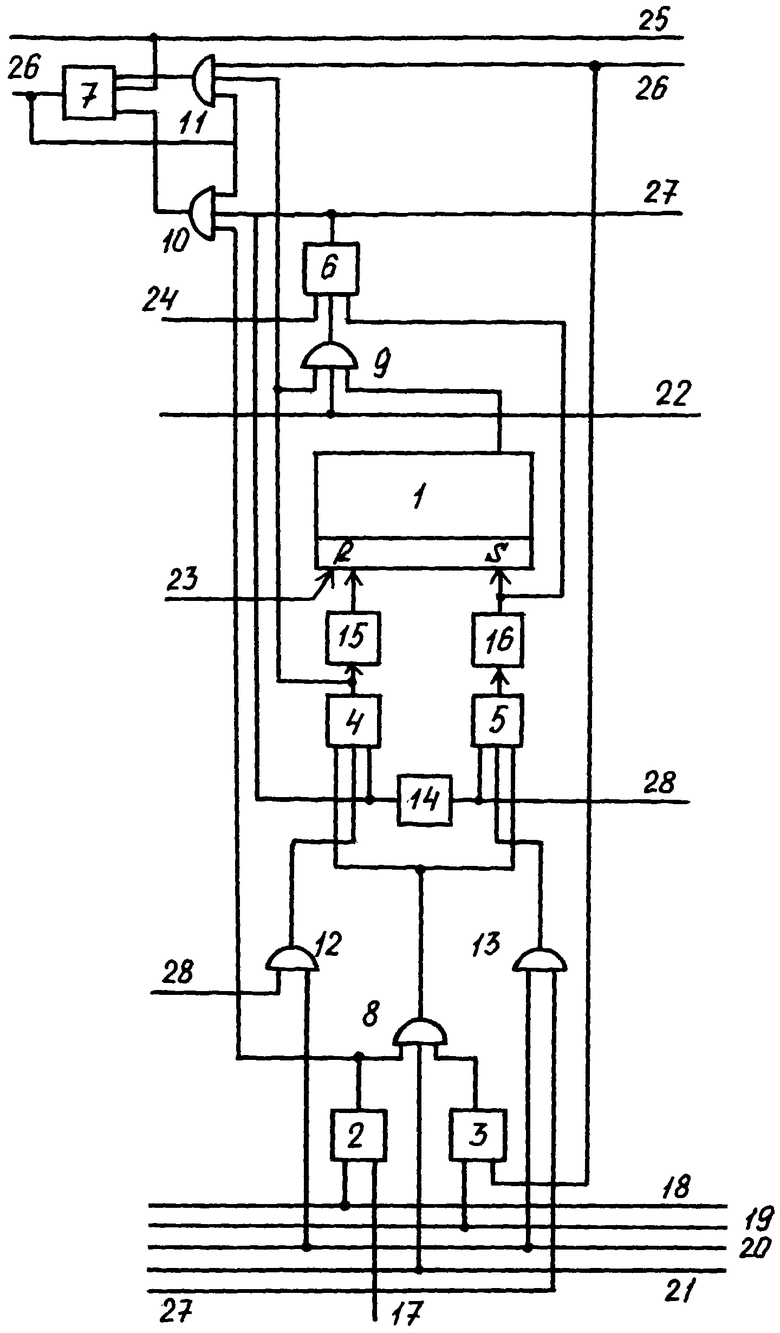

Предлагаемый объект позволяет расширить перечень выполняемых операций с двух (сложение и сложение по модулю два) до девяти (сдвиг вправо, сдвиг влево, инвертирование, логическое сложение, логическое умножение, установка нуля триггера и прием единицы) при минимальных затратах дополнительного оборудования (требуется дополнительно девять входов логических элементов). Для пояснения работы описываемого объекта на чертеже приведена функциональная схема одного разряда, где приняты следующие обозначения: RS-триггер 1, логические элементы И 2-7, элементы ИЛИ 8-13, элементы НЕ 14-16, информационный вход 17, вход управления (ВУ) первым сложением по модулю два 18, ВУ вторым сложением по модулю два 19, ВУ операций сдвига вправо 20, ВУ сдвигом, инвертированием, логическим сложением и логическим умножением 21, ВУ логическим умножением 22, вход установки нуля 23, ВУ логическим сложением 24, ВУ гашением переноса 25, вход переноса 26, единичный выход триггера 27, нулевой выход триггера 28. В исходном положении (статика) триггер 1 установлен в нуль, на всех ВУ отсутствует высокие потенциалы, кроме ВУ 20, 24. На ВУ 20, 24 и на элементах НЕ 14, 15, 16 присутствуют высокие потенциалы. Рассмотрим работу объекта при выполнении арифметических и логических операций (в динамике).

1. Операция сложения. Будем считать, что код первого слагаемого хранится в триггере 1, а код второго слагаемого поступает в сумматор по информационному входу 17. По первому временному такту (t1) выполняются одновременно элементарные операции (ЭО) приема второго слагаемого, сложение по модулю два (первое), формирование и запоминание потенциала переноса в цепи сквозного переноса, данного разряда. Для выполнения этих ЭО на шину 18 подается исполнительный импульс, на шину 25 подается потенциал разрешения прохождения сигнала переноса. Если на шине 17 имеется сигнал, соответствующий коду "1", то исполнительный импульс по цепи ЛЭ И2, ИЛИ8 поступит на первые входы И4, 5. Одновременно этот же импульс с выхода элемента И2 поступает на вход ИЛИ 10, 8. С выхода ИЛИ 8 импульс проходит на входы И4, 5. Если триггер до прихода импульса хранил код единицы, то этот же импульс с выхода И4 через НЕ 15 поступит на R-вход триггера 1 и установит его в нуль. Так как на всех трех входах И7 присутствуют высокие потенциалы, то на его выходе будет высокий потенциал, который по входу 26 поступит в старший разряд. Одновременно за счет связей с выхода И7 с выходами ИЛИ 10, 11 этот потенциал будет автоматически храниться до тех пор, пока с ВУ 25 не будет снят управляющий потенциал. Если до прихода исполнительного импульса триггер хранил код нуля, то импульс проходит по цепи И2, ИЛИ8, И5, НЕ 16 на S-вход триггера 1 и устанавливает его в единицу. Одновременно исполнительный импульс запрещает работу И6 на время его длительности. При этом переключение триггера в единицу не создает условий прохождения потенциала переноса в старший разряд. Если t, триггер будет переключатся из нулевого состояния в единичное и из младшего разряда поступит сигнал переноса, то исполнительный импульс по цепи элементов И2, ИЛИ10 поступит на вход И7, на втором и третьем входах этого элемента также будет присутствовать высокие потенциалы, а с выхода И7 в старший разряд будет поступать потенциал переноса. Этот потенциал будет сохраняться до тех пор, пока с ВУ 25 не будет снят высокий управляющий потенциал. По t2 продолжается формирование и распространение потенциала переноса в сторону старших разрядов. По третьему временному такту t3 выполняется ЭО сложения по модулю два (вторая). Исполнительный импульс поступает по входу 19 и, если в рассматриваемый разряд по входу 26 поступил потенциал переноса из младшего разряда, по цепи И3, ИЛИ8 поступит на входы И4, 5 и проинвертирует код триггера 1. На этом операция сложения завершается. Результат суммирования будет храниться в триггерах 1.

2. Операция сдвига кода вправо. Выполняется за два такта t1 и t2. Для ее выполнения с ВУ 20 снимается высокий потенциал, при этом третьи входы И4, 5 будут управляться с выходов НЕ 4 и И6 старшего разряда соответственно. По времени t1 исполнительный импульс по цепи ВУ 21, ИЛИ8 поступит на первые входы И4, 5. Если в i- 1-м и в i-м разрядах значения кодов триггеров одинаковы, то после прихода исполнительного импульса по ВУ21 состояние триггера i-того разряда не меняется, т.е. импульс не проходит ни на R-, ни на S- вход. Если значения кодов триггеров неидентичны, то при значении триггера i- 1-го разряда, равного единице, триггер i-того разряда после прихода исполнительного импульса будет установлен в единицу. При этом потенциал с выхода И6 i-того разряда по линии связи 27, через ИЛИ 13, И5, НЕ16, поступит на S-вход триггера 1 i-того разряда и установит его в единицу. На время длительности исполнительного импульса условие прохождение сигнала на S-вход не будет меняться, т.к. на третьем входе И6 будет низкий потенциал с выхода НЕ 16. Если триггер i-1-го разряда хранит код нуля, то высокий потенциал с выхода НЕ 14 по линии связи 28, через ИЛИ12, И4, НЕ15 поступит на R-вход триггера i-того разряда и установит его в нуль. На время длительности исполнительного импульса условия прохождения сигнала на R- входе не будут меняться, т.к. сигнал по цепи И4, ИЛИ9, И6 будет поддерживать прохождение сигнала через И4. Таким образом, каждый исполнительный импульс, поступивший по ВУ 21 будет сдвигать код триггеров 1 на один разряд вправо. Второй временной такт (пауза между импульсами) используется для подготовки логических элементов объекта к следующему импульсу сдвига. Операция заканчивается после сдвига кода на заданное число разрядов.

3. Операция инвертирования кода. Выполняется за два такта t1 и t2. По t1 исполнительный импульс, поступивший по ВУ 21, пройдет по цепи ИЛИ 8, И5, НЕ 16 на S- вход триггера, если до прихода импульса он хранил код нуля, и по цепи И4, НЕ 15, если раньше триггер хранил код единицы. Второй такт используется для подготовки объекта к выполнению очередной операции. Для выполнения этой операции не требуется дополнительного оборудования.

4. Операция сложения по модулю два. Принцип выполнения этой операции рассмотрен при описании операции сложения (п.1). Для выполнения этой операции не требуется дополнительного оборудования.

5. Операция сдвига кода влево. С помощью этой операции осуществляется умножение двоичного кода на 2, 4, 8, и т.д. Операция выполняется за четыре временных такта (t1, 2, 3, 4). Для ее выполнения на ВУ 25 подается высокий потенциал. По t1 выполняется операция инвертирование кода, хранящегося в триггерах 1 (п.3). В ходе выполнения инвертирования кода в разрядах, хранящих код единицы, формируется и «запоминается» потенциал переноса. Исполнительный импульс проходит по цепи ВУ21, ИЛИ8, И4, ИЛИ11. По t2 триггер 1 устанавливается в нуль. Для это на вход 23 поступает импульс., устанавливающий триггер 1 в нуль. По t3 осуществляется собственно сдвиг кода влево. Для этого по ВУ 19 подается исполнительный импульс, который по цепи ИЗ, ИЛИ8, И5, НЕ 16 проходит на S- вход триггера и установит его в единицу, если по входу 26 поступил потенциал переноса. Если потенциала переноса нет, то триггер останется в нулевом состоянии. По t4 с ВУ 25 снимается высокий потенциал, т.е. производится ЭО гашения переноса. На этом операция сдвига кода на один разряд влево завершена. Операция будет выполняться до тех пор, пока код числа не будет сдвинуто влево на заданное число разрядов. Для реализации этой операции не требуется дополнительного оборудования.

6. Операция логического сложения. При выполнении этой операции код первого слагаемого хранится в триггерах 1, а второе слагаемое поступает по информационному входу 17. Операция выполняется за два временных такта t1 и t2. Для ее выполнения с ВУ24 снимается высокий потенциал. Высокий потенциал с НЕ 14 разрешит прохождение исполнительного импульса по цепи ВУ18, И2, ИЛИ8, И5, НЕ16 на S-вход триггера, если на входе 17 высокий потенциал. Время второго такта используется для подготовки объекта к выполнению других операций. Для выполнения этой операции требуется только один вход элемента И.

7. Операция логического умножения. Операция выполняется за два временных такта t1 и t2. Для ее выполнения на ВУ 22 подается высокий потенциал, который по цепи ИЛИ9, И6 поступит на второй вход И4. По t1 на ВУ 17 подается инверсный код второго сомножителя, а по ВУ 18 поступает исполнительный импульс. Если на входе 17 присутствует высокий потенциал, соответствующий нулю второго сомножителя в данном разряде, то исполнительный импульс по цепи ВУ 18, И2, ИЛИ8, И4, НЕ 15 поступит на R-вход триггера и установит его в нуль, что соответствует результату выполнения операции логического умножения. Время второго такта используется для подготовки объекта к выполнению последующих операций.

8. Операция установки нуля. В предлагаемом объекте выполняются три варианта установки нуля триггеров 1. Вариант 1. По входу 3 поступает исполнительный импульс, который устанавливает все триггеры 1. Вариант 2. По ВУ 21 и 22 одновременно поступают управляющие импульсы. Вариант 3. По ВУ18, 22 одновременно поступают импульсы. Если на входе 17 присутствует высокий потенциал, то триггер 1 будет установлен в нуль, т.е. от значения кода, поступающего на входы 17 можно выборочно устанавливать в нуль триггер 1 любого разряда. Эта операция используется преимущественно в устройствах цифровой автоматики.

Таким образом, предлагаемый объект позволяет расширить перечень выполняемых операций с двух (сложение и сложение по модулю два) до восьми (сдвиг влево и вправо, инвертирование, логическое сложение, логическое умножение и выборочная установка в нуль отдельных (отдельного) разрядов) при увеличении оборудования каждого разряда объекта по сравнению с прототипом только на девять входов логических элементов (суммарное число входов равно 42).

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2006 |

|

RU2308801C1 |

| УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2381547C2 |

| СУММАТОР КОМБИНАЦИОННОГО ТИПА | 2004 |

|

RU2275676C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2010 |

|

RU2419200C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ | 2005 |

|

RU2308073C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

Изобретение относится к области вычислительной техники и цифровой автоматики. Техническим результатом является расширение функциональных возможностей устройства за счет выполнения дополнительных операций при минимальных аппаратурных затратах. Устройство содержит в каждом разряде RS-триггер, шесть элементов ИЛИ, шесть элементов И, три элемента НЕ, входы управления, вход установки нуля, информационный вход. 1 ил.

Накапливающий сумматор, выполненный на логических элементах И, ИЛИ, НЕ, содержащий в каждом разряде один RS-триггер, шесть элементов И, четыре элемента ИЛИ, три элемента НЕ, пять входов управления, вход установки нуля и информационный вход, при этом первые входы первого и второго элементов И соединены с первым и вторым входами управления соответственно, вторые входы упомянутых элементов И связаны с информационным входом и выходом переноса из младшего разряда соответственно, выходы этих элементов И подключены к первому и второму входам первого элемента ИЛИ, выход которого связан с первыми входами третьего и четвертого элементов И, вторые входы этих элементов И соединены с входом и выходом первого элемента НЕ, выходы третьего и четвертого элементов И через третий и второй элементы НЕ подключены к S- и R-входу RS-триггера соответственно, единичный выход триггера соединен с первым входом второго элемента ИЛИ, второй его вход связан с выходом третьего элемента И и с вторым входом четвертого элемента ИЛИ, третий вход соединен с третьим входом управления, а его выход подключен к первому входу пятого элемента И, второй вход этого элемента И соединен с четвертым входом управления, третий вход подключение к S-входу RS-триггера, выход пятого элемента И соединен с вторым входом третьего элемента И, с входом первого элемента НЕ и с первым входом третьего элемента ИЛИ, второй вход упомянутого элемента ИЛИ подключен к выходу первого элемента И, третьи входы третьего и четвертого элементов ИЛИ соединены с выходом шестого элемента И, первый вход четвертого элемента ИЛИ соединен с выходом переноса из младшего разряда, выходы третьего и четвертого элементов ИЛИ подключены к первому и второму входам шестого элемента И, к его третьему входу подключен пятый вход управления, выход шестого элемента И является входом переноса в старший разряд, вход установки нуля подключен к R-входу RS-триггера, отличающийся тем, что в каждый разряд введены пятый и шестой элементы ИЛИ, шестой и седьмой входы управления, при этом первые входы пятого и шестого элементов ИЛИ соединены с шестым входом управления, вторые входы упомянутых элементов подключены к выходам первого элемента НЕ и пятого элемента И старшего разряда соответственно, выходы пятого и шестого элементов ИЛИ соединены с третьими входами третьего и четвертого элементов И соответственно, седьмой вход управления соединен с третьим входом первого элемента ИЛИ.

| Накапливающий сумматор | 1985 |

|

SU1291968A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| ЦИФРОВОЙ СУММАТОР | 1994 |

|

RU2099776C1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| 1972 |

|

SU416869A1 | |

| US 5691931 A, 25.11.1995. | |||

Авторы

Даты

2006-11-27—Публикация

2005-05-17—Подача