N9

О) N9

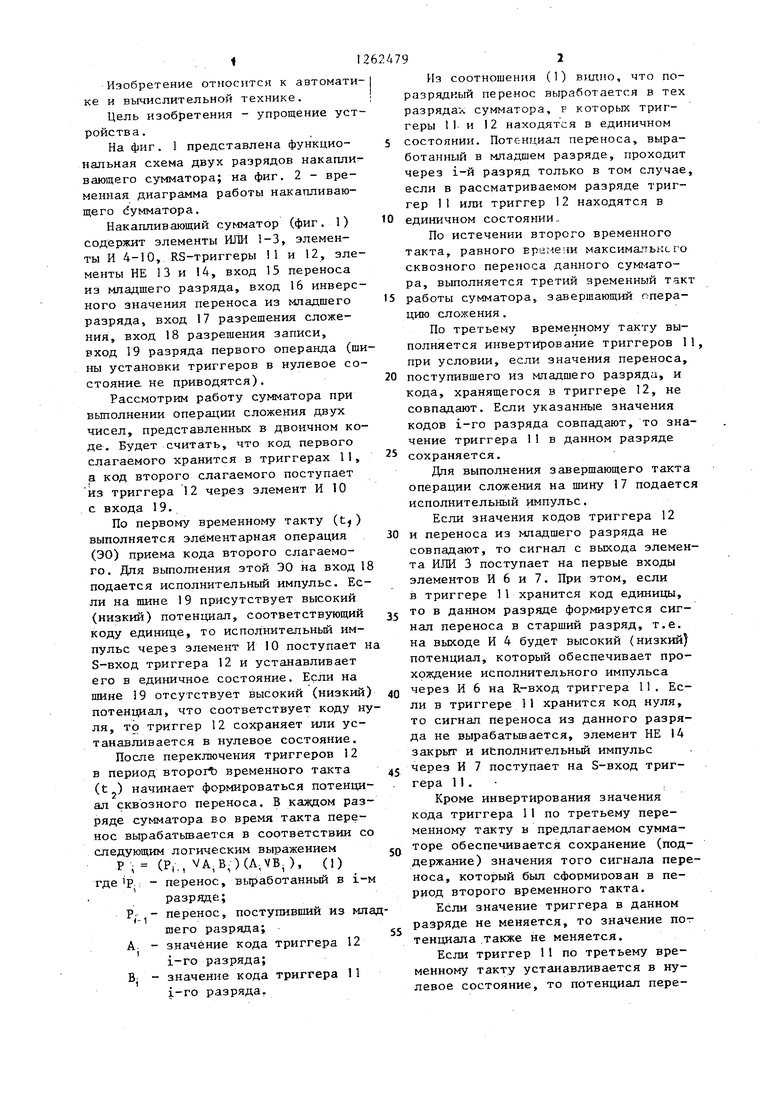

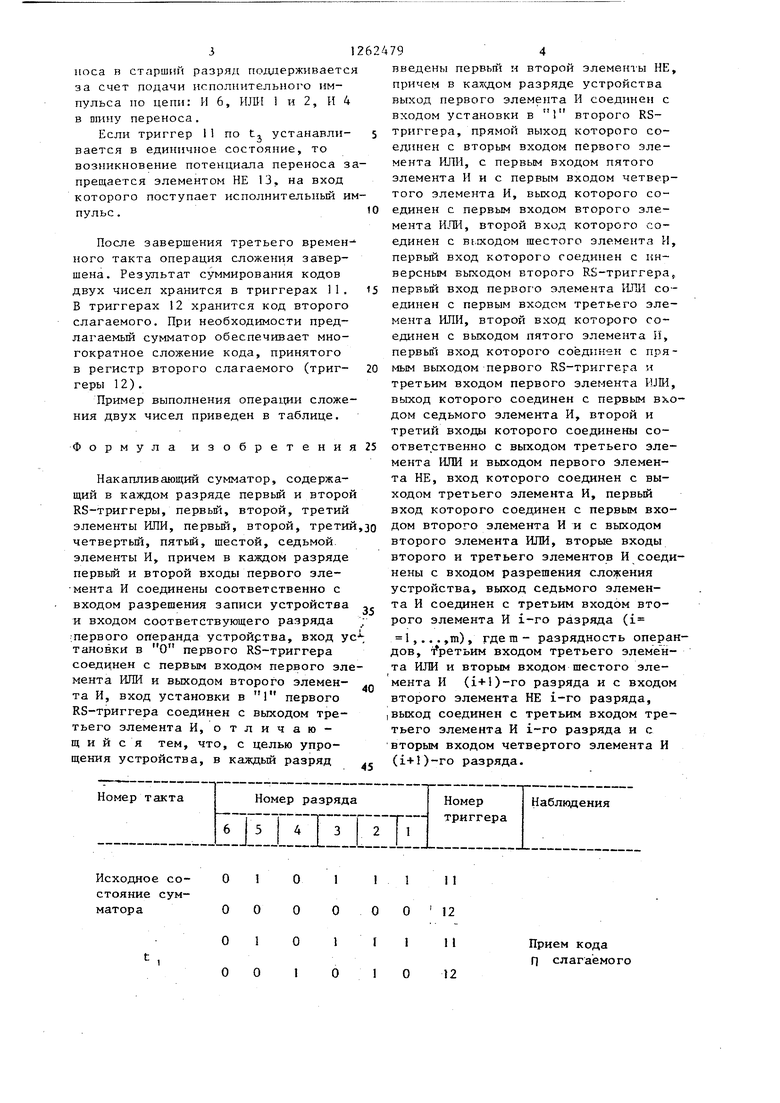

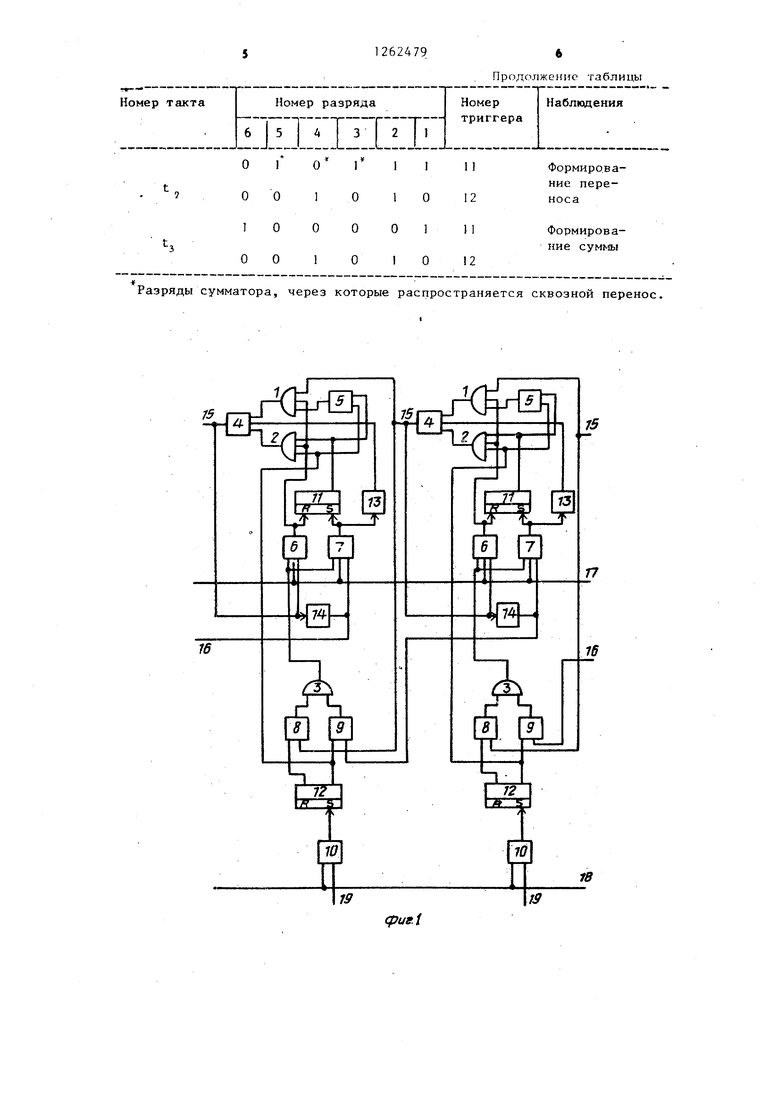

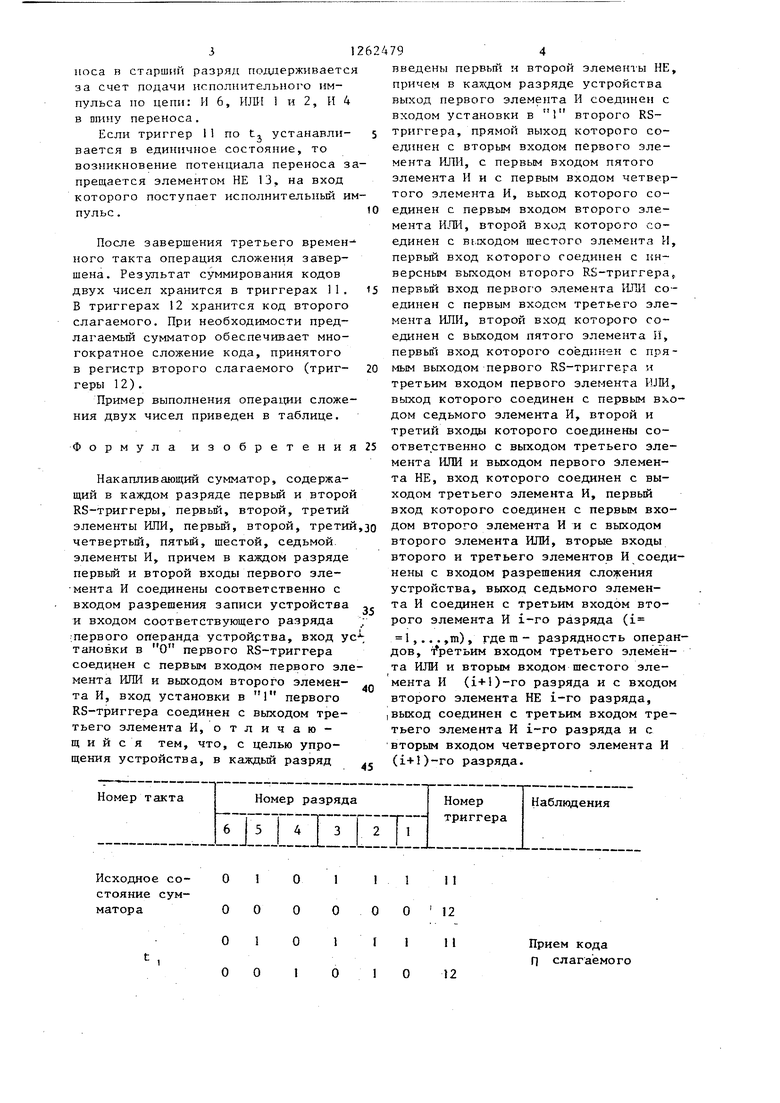

liti СО Изобретение относится к автомати ке и вычислительной технике. Цель изобретения - упрощение уст ройства. На фиг. 1 представлена функциональная схема двух разрядов накапли вающего сумматора; на фиг. 2 - временная диаграмма работы накапливающего dyMMaTopa. Накапливающий сумматор (фиг. 1) содержит элементы ИЛИ 1-3, элементы И 4-10, RS-триггеры 11 и 12, эле менты НЕ 13 и 14, вход 15 переноса из младшего разряда, вход 16 инверс ного значения переноса из младшего разряда, вход 17 разрешения сложения, вход 18 разрешения записи, вход 19 разряда первого операнда (ш ны установки триггеров в нулевое со стояние не приводятся). Рассмотрим работу сумматора при вьтолнении операции сложения двух чисел, представленных в двоичном ко де. Будет считать, что код первого слагаемого хранится в триггерах II, а код второго слагаемого поступает из триггера 12 через элемент И 10 с входа 19. По первому временному такту (tj) выполняется элементарная операция (ЭО) приема кода второго слагаемого. Дпя выполнения этой ЭО на вход 1 подается исполнительный импульс. Ес ли на шине 19 присутствует высокий (низкий) потенциал, соответствующий коду единице, то исполнительный импульс через элемент И 10 поступает S-вход триггера 12 и устанавливает его в единичное состояние. Если на шине 19 отсутствует высокий (низкий потенциал, что соответствует коду н ля, то триггер 12 сохраняет или устанавливается в нулевое состояние. После переключения триггеров 12 в период BTOport) временного такта (t ) начинает формироваться потенци ал сквозного переноса. В каждом раз ряде сумматора во время такта перенос вьфабатьшается в соответствии с следующим логическим выражением Р . (Р,., VA,B.)(A.VB,), (1) где ip. - перенос, выработанньй в iразряде;Р- - перенос, поступивший из мл шего разряда; А. - значение кода триггера 12 i-ro разряда; В - значение кода триггера 11 i-ro разряда. 9 Из соотношения (1) видно, что поразрядный перенос выработается в тех разрядах сумматора, Р которых триггеры Пи 12 находятся в единичном состоянии. Потенциал переноса, выработанный в младшем разряде, проходит через i-й разряд только в том случае, если в рассматриваемом разряде триггер 11 или триггер 12 находятся в единичном состоянии„ По истечении второго временного такта, равного вранени максимальксЕо сквозного переноса данного сум1-1атора, вьшолняется третий временный такт работы сумматора, завершающий операцию сложения. По третьему временному такту выполняется инвертирование триггеров 11, при условии, если значения переноса, поступившего из младшего разряда, и кода, хранящегося в триггере 12, не совпадают. Если указанные значения кодов i-ro разряда совпадают, то значение триггера 11 в данном разряде сохраняется. Дпя выполнения завершающего такта операции сложения на шину 17 подается исполнительный импульс. Если значения кодов триггера 12 и переноса из младшего разряда не совпадают, то сигнал с выхода элемента ИЛИ 3 поступает на первые входы элементов И 6 и 7. При этом, если в триггере 11 хранится код единицы, то в данном разряде формируется сигнал переноса в старший разряд, т.е. на выходе И 4 будет высокий (низкий) потенциал, который обеспечивает прохрждение исполнительного импульса через И 6 на R-вход триггера 11. Если в триггере П хранится код нуля, то сигнал переноса из данного разряда не вырабатьшается, элемент НЕ 14 закрыт и иьполнительный импульс через И 7 поступает на S-вход триггера 11. Кроме инвертирования значения кода триггера 11 по третьему переменному такту в предлагаемом сумматоре обеспечивается сохранение (поддержание) значения того сигнала переноса, который был сформирован в период второго временного такта. Если значение триггера в данном разряде не меняется, то значение по-г тенциала .также не меняется. Если триггер 11 по третьему временному такту устанавливается в нулевое состояние, то потенциал переноса в старший разряд псишержнваетс за счет подачи исполнительного импульса по цепи: И 6, ИШ1 1 и 2, Н 4 в тину переноса. Если триггер по t, устанавливается в единичное состояние, то возникновение потенциала переноса з прещается элементом НЕ 13, на вход которого поступает исполнительный и пульс. После завершения третьего времен ного такта операция сложения завершена. Результат суммирования кодов двух чисел хранится в триггерах 11. В триггерах 12 хранится код второго слагаемого. При необходимости предлагаемый сумматор обеспечивает многократное сложение кода, принятого в регистр второго слагаемого (триггеры 12). Пример выполнения операгщи сложе ния двух чисел приведен в таблице. Формула изобретени Накапливающий сумматор, содержащий в каждом разряде первьш и второ RS-триггеры, первьп, второй, третий элементы ИЛИ, первый, второй, трети четвертый, пятый, шестой, седьмой, элементы И, причем в каждом разряде первьй и второй входы первого эле мента И соединены соответственно с входом разрешения записи устройства и входом соответствующего разряда (Первого операнда устройртва, вход у тановки в О первого RS-триггера соединен с первым входом первого эл мента ИЛИ и выходом второго элемента И, вход установки в 1 первого RS-триггера соединен с выходом третьего элемента И, отличающийся тем, что, с целью упрощения устройства, в каждый разряд введены первый и второй элемвН1Ъ1 НЕ, причем в каждом разряде устройства выход первого элемента И соединен с входом установки в 1 второго RSтриггера, прямой выход которого соединен с вторым входом первого элемента ИЛИ, с первым входом пятого элемента И и с первым входом четвертого элемента И, выход которого соединен с первым входом второго элемента ИШ, второй вход которого соединен с вьжодом шестого элемента И, первьй вход которого соединен с инверсным выходом второго RS-триггера,. первьй вход первого элемента liPJi соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, первьв вход которого соединен с прямым выходом первого RS-триггера и третьим входом первого элемента ИЛИ, выход которого соединен с первым входом седьмого элемента И, второй и третий входь которого соединены соответ.ственно с выходом третьего элемента ИЛИ и выходом первого элемента НЕ, вход которого соединен с выходом третьего элемента И, первый вход которого соединен с первым входом второго элемента И и с выходом второго элемента ИЛИ, вторые входы второго и третьего элементов И соединены с входом разрешения сложения устройства, выход седьмого элемента И соединен с третьим входом второго элемента И i-ro разряда (i 1,.. . ,in) , где m - разрядность операндов, т ретьим входом третьего элемента ИЛИ и вторым входом шестого элемента И (i-bl)-ro разряда и с входом второго элемента НЕ i-ro разряда, выход соединен с третьим входом третьего элемента И i-ro разряда и с вторым входом четвертого элемента И (i+l)-ro разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Накапливающий сумматор | 1987 |

|

SU1418705A1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| Накапливающий сумматор | 1985 |

|

SU1291968A1 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| Накапливающий сумматор | 1987 |

|

SU1418701A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

Изобретение относится к цифровой вычислительной техншсе и может быть использовано в процессорах ЭВМ. Цель изобретения - упрощение устройства. Накапливающий сумматор в- каждом разряде содержит два RS-триггера, три элемента ШШ, семь злементов И, два элемента НЕ и шины управления сумматором. Новыми схемными соединениями в предложенном сумматоре являются соединение входа первого элемента НЕ с шиной переноса из данного разряда и с третьим входом пятого элемента И, а выход этого элемента НЕ соединен с третьим входом шестого элемента И данного разряда и с вторьм входом четвертого элемента И старшего разряда, вход второго элемента НЕ соединен с S-входом второго триггера, а его выход подключен к третьему входу седьмого злемента И, выход которого является шиной переноса в старший разряд, при этом R-вход второго триггера связан с третьими входами первого и третьего элементов ШШ. (Л 2 ил. 1 табл.

Исходное состояние сумматора

Прием кода П слагаемого Разряды сумматора, через которые

75

Продолжение таблицы

1В распространяется сквозной перенос,

(pi/г. 2

| Накапливающий сумматор | 1982 |

|

SU1043638A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Накапливающий сумматор | 1984 |

|

SU1176323A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-01-07—Подача