Изобретение относится к вычислительной технике и предназначено для выполнения операции округления в системе остаточных классов.

Известно устройство для округления числа в системе остаточных классов, содержащее регистры, блоки хранения констант, сумматоры, блоки вычисления неточных рангов, блок коррекции округления, соединенные соответствующими связями [1].

Недостатком этого устройства является невысокое быстродействие.

Наиболее близким к предлагаемому является устройство для округления числа в системе остаточных классов, содержащее входной регистр, первую и вторую группы из n-шифраторов (n - количество оснований системы остаточных классов), первый и второй накапливающий сумматоры, группу из n сумматоров по модулю Pi (Pi - основание системы остаточных классов, i=1, 2, ..., n), выходы которых являются выходами устройства, входы входного регистра являются информационными входами устройства, а выходы подключены к входам соответствующих шифраторов первой группы, входы шифраторов второй группы подключены к входам соответствующих шифраторов первой группы, первые входы сумматоров по модулю Pi подключены к входам соответствующих шифраторов первой группы, выходы шифраторов первой и второй группы подключены к соответствующим входам соответственно первого и второго накапливающих сумматоров, выход первого накапливающего сумматора подключен к первому входу n-го шифратора второй группы, вторые входы сумматоров по модулю Pi группы объединены и подключены к выходам второго накапливающего сумматора, управляющие входы j-ых шифраторов первой и второй групп объединены и являются соответственно j-ми управляющими входами устройства, вторые входы n-шифраторов первой и второй групп являются соответственно n-ым и (n+1)-ым управляющими входами устройства (j=1, 2, ..., n) [2].

Недостатком этого устройства является низкое быстродействие.

Задача предложенного изобретения - в повышении быстродействия при выполнении операции округления числа в системе остаточных классов.

Технический результат достигается тем, что для определения суммы значений с выходов групп шифраторов используется группа сумматоров и все значения с выходов группы шифраторов поступают на входы группы сумматоров одновременно.

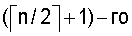

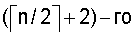

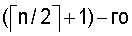

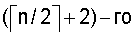

Сущность устройства для округления числа в системе остаточных классов в том, что оно содержит входной регистр, первую и вторую группу из n шифраторов (n - количество оснований системы остаточных классов), первую и вторую группу n-1 сумматоров, группу из n сумматоров по модулю Pi (Pi - основание системы остаточных классов, i=1, 2, ..., n), выходы которых являются выходами устройства, входы входного регистра являются информационными входами устройства, а выходы входного регистра подключены к входам соответствующих шифраторов первой группы, входы шифраторов второй группы подключены к входам соответствующих шифраторов первой группы, первые входы сумматоров по модулю Pi подключены к входам соответствующих шифраторов первой группы, выходы первого и второго шифратора первой группы подключены к первому и второму входу первого сумматора первой группы, выходы третьего и четвертого шифратора подключены к первому и второму входам второго сумматора первой группы, итак далее выходы (n-1)-го и n-го шифратора первой группы подключены к входам  сумматора первой группы, выходы первого и второго сумматора первой группы подключены к первым и вторым входам

сумматора первой группы, выходы первого и второго сумматора первой группы подключены к первым и вторым входам  сумматора первой группы, выходы третьего и четвертого сумматора первой группы подключены к первому и второму входу

сумматора первой группы, выходы третьего и четвертого сумматора первой группы подключены к первому и второму входу  сумматора первой группы, и так далее выходы (n-3)-го и (n-2)-го сумматора первой группы подключены к первому и второму входу (n-1)-го сумматора первой группы, выходы первого и второго шифратора второй группы подключены к первому и второму входу первого сумматора второй группы, выходы третьего и четвертого шифратора второй группы подключены к первому и второму входам второго сумматора второй группы, и так далее выходы (n-2)-го и (n-1)-го шифратора подключены к входам

сумматора первой группы, и так далее выходы (n-3)-го и (n-2)-го сумматора первой группы подключены к первому и второму входу (n-1)-го сумматора первой группы, выходы первого и второго шифратора второй группы подключены к первому и второму входу первого сумматора второй группы, выходы третьего и четвертого шифратора второй группы подключены к первому и второму входам второго сумматора второй группы, и так далее выходы (n-2)-го и (n-1)-го шифратора подключены к входам  сумматора второй группы, выходы первого и второго сумматора второй группы подключены к первым и вторым входам

сумматора второй группы, выходы первого и второго сумматора второй группы подключены к первым и вторым входам  сумматора второй группы, выходы третьего и четвертого сумматора второй группы подключены к первому и второму входу

сумматора второй группы, выходы третьего и четвертого сумматора второй группы подключены к первому и второму входу  сумматора второй группы, и так далее выходы (n-3)-го и (n-2)-го сумматора второй группы подключены к первому и второму входу (n-1)-го сумматора второй группы, выход n-го шифратора второй группы подключен к первому входу n-го сумматора второй группы, выход (n-1)-го сумматора второй группы подключен к второму входу n-го сумматора второй группы, выход (n-1)-го сумматора первой группы подключен к первому входу n-го шифратора второй группы, вторые входы сумматоров по модулю Pi группы объединены и подключены к выходу n-го сумматора второй группы, управляющие входы всех шифраторов, кроме n-го шифратора второй группы объединены и являются первым управляющим входом устройства, управляющий вход n-го шифратора второй группы является вторым управляющим входом устройства.

сумматора второй группы, и так далее выходы (n-3)-го и (n-2)-го сумматора второй группы подключены к первому и второму входу (n-1)-го сумматора второй группы, выход n-го шифратора второй группы подключен к первому входу n-го сумматора второй группы, выход (n-1)-го сумматора второй группы подключен к второму входу n-го сумматора второй группы, выход (n-1)-го сумматора первой группы подключен к первому входу n-го шифратора второй группы, вторые входы сумматоров по модулю Pi группы объединены и подключены к выходу n-го сумматора второй группы, управляющие входы всех шифраторов, кроме n-го шифратора второй группы объединены и являются первым управляющим входом устройства, управляющий вход n-го шифратора второй группы является вторым управляющим входом устройства.

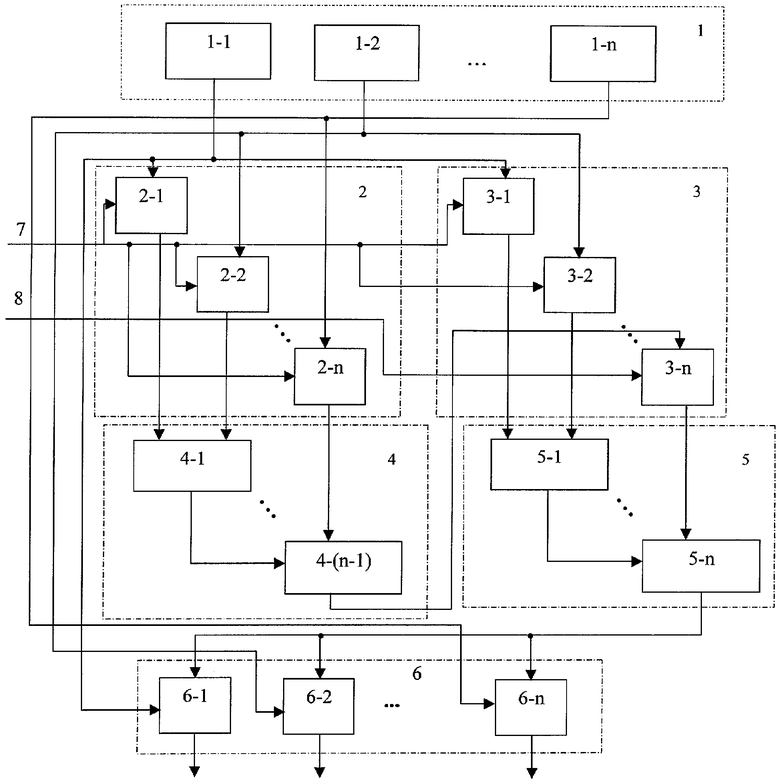

На чертеже представлена структурная схема предлагаемого устройства. Устройство содержит: входной регистр - 1, предназначенный для хранения числа А по n-основаниям в унитарном коде; первую и вторую группу шифраторов - 2; 3; первую группу из n-1 сумматоров - 4 и вторую группы из n сумматоров - 5; группу из n сумматоров по модулю Pi - 6, первый и второй управляющие входы устройства - 7, 8.

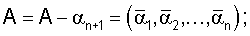

Входной регистр - 1 предназначен для хранения числа А по n-основаниям в унитарном коде; шифраторы группы - 2 служат для кодирования произведения по модулю Pi остатков числа А на постоянные коэффициенты βi, шифраторы группы 3 - для кодирования произведения по модулю D остатков числа А на постоянные коэффициенты  первая группа сумматоров - 4 предназначена для формирования ранга числа, вторая группа сумматоров - 5 для формирования αn+1, сумматоры - 6 - для формирования величины A=(α1, α2, ..., αN)-(αN+1αN+1...) на их выходах формируется округляемое число.

первая группа сумматоров - 4 предназначена для формирования ранга числа, вторая группа сумматоров - 5 для формирования αn+1, сумматоры - 6 - для формирования величины A=(α1, α2, ..., αN)-(αN+1αN+1...) на их выходах формируется округляемое число.

Устройство работает следующим образом.

Код числа А, которое требуется округлить, принимается на входной регистр 1. С входного регистра 1 сигналы поступают на входы блоков 2 и 3 и входы сумматоров по модулю 6. При поступлении тактовых импульсов по шине 7 в блоках 2 и 3 происходит кодирование произведений βi·αimodPN (i=1...n) и  и подача результатов на входы первой и второй группы сумматоров 4 и 5. При подаче тактового импульса по шине 8 происходит кодирование произведения βN·αNmodPN и подача результата на первый вход n-го сумматора второй группы 5, на второй вход n-го сумматора второй группы 5 поступает ранг числа rA с выхода (n-1)-го сумматора первой группы 4. Таким образом, на выходе n-го сумматора второй группы 5 сформировано значение αN+1, которое поступает на вторые входы сумматоров группы, а на первые входы этих сумматоров поданы значения αi. В сумматорах 6 происходит вычисление

и подача результатов на входы первой и второй группы сумматоров 4 и 5. При подаче тактового импульса по шине 8 происходит кодирование произведения βN·αNmodPN и подача результата на первый вход n-го сумматора второй группы 5, на второй вход n-го сумматора второй группы 5 поступает ранг числа rA с выхода (n-1)-го сумматора первой группы 4. Таким образом, на выходе n-го сумматора второй группы 5 сформировано значение αN+1, которое поступает на вторые входы сумматоров группы, а на первые входы этих сумматоров поданы значения αi. В сумматорах 6 происходит вычисление  На выходе сумматоров 6 формируется результат округления числа А.

На выходе сумматоров 6 формируется результат округления числа А.

Конкретный пример осуществления изобретения.

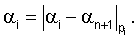

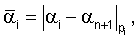

Введем следующие обозначения: P1, P2, ..., Pn - основания системы,  Р - диапазон системы, при этом число А=(α1, α2, ..., αn), где

Р - диапазон системы, при этом число А=(α1, α2, ..., αn), где  - наименьший положительный остаток от деления целого числа А на основание Pi.

- наименьший положительный остаток от деления целого числа А на основание Pi.

Округляющее число выбирается из условия, чтобы исходное число делилось на заданное без остатка, тогда округляющее число равно остатку от деления исходного на заданное. Например, исходное число А=17 и задано число Д=5, тогда округляющее число равно 2, т.к. остаток от деления числа А на число Д равен 2.

А - число, которое делится на число Д без остатка. Тогда

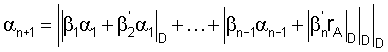

где Д - число, на которое делается округление αn+1=|A|D или

где Д - число, на которое делается округление αn+1=|A|D или

где

i=1, 2, ..., n-1;

i=1, 2, ..., n-1;

βi - ортогональные базисы.

βi=miP/Pi; i=1, 2, ..., n;

mi - целое число, удовлетворяющее выражению miР|Рi≡1(modPi), в котором

i=1, 2, ..., n-1,

i=1, 2, ..., n-1,

Величины βi и  - эти числа не зависят от А и являются константами при выбранной системе оснований.

- эти числа не зависят от А и являются константами при выбранной системе оснований.

Источники информации

1. Авторское свидетельство СССР №398949, кл. G06F 7/52, 1974.

2. Авторское свидетельство СССР №951305, кл. G06F 7/72, 1982.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для округления числа в системе остаточных классов | 1980 |

|

SU951305A1 |

| Аналого-цифровой преобразователь в системе остаточных классов | 1989 |

|

SU1698991A1 |

| СИСТОЛИЧЕСКИЙ ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1992 |

|

RU2029437C1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ОКРУГЛЕНИЯ И МАСШТАБИРОВАНИЯ ЧИСЕЛ, ПРЕДСТАВЛЕННЫХ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2003 |

|

RU2271570C2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД С ПЕРЕСЧЕТОМ ОРТОГОНАЛЬНЫХ БАЗИСОВ | 2005 |

|

RU2298873C1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ИЗ ПОЛИНОМИАЛЬНОЙ СИСТЕМЫ КЛАССОВ ВЫЧЕТОВ В ПОЗИЦИОННЫЙ КОД | 2008 |

|

RU2409840C2 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ОБНАРУЖЕНИЯ, ЛОКАЛИЗАЦИИ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2005 |

|

RU2301442C2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЕЛ ИЗ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЛИАДИЧЕСКИЙ КОД | 2001 |

|

RU2187886C1 |

| Устройство обнаружения и коррекции ошибки модулярного кода | 2017 |

|

RU2653257C1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах округления чисел в системе остаточных классов. Техническим результатом является повышение быстродействия устройства. Устройство содержит входной регистр, две группы шифраторов, первую группу из n-1 сумматора, вторую группу из n сумматоров, группу сумматоров по модулю. 1 ил.

Устройство для округления числа в системе остаточных классов, содержащее входной регистр, первую и вторую группы из n шифраторов, где n - количество оснований системы остаточных классов, n - четное число, группу из n сумматоров по модулю Pi, где Pi - основания системы остаточных классов, выходы которых являются выходами устройства, входы входного регистра являются информационными входами устройства, а выходы подключены к входам соответствующих шифраторов первой группы, входы шифраторов второй группы, кроме n-го, подключены к входам соответствующих шифраторов первой группы, первые входы сумматоров по модулю Pi подключены к входам соответствующих шифраторов первой группы, отличающееся тем, что выходы первого и второго шифраторов первой группы подключены к первому и второму входам первого сумматора первой группы, выходы третьего и четвертого шифраторов подключены к первому и второму входам второго сумматора первой группы, выходы остальных шифраторов первой группы соединены с входами сумматоров первой группы аналогичным образом до (n-1)-го и n-го шифраторов, подключенных выходами к входам [n/2]-го сумматора первой группы, выходы первого и второго сумматора первой группы подключены к первым и вторым входам ([n/2]+1)-го сумматора первой группы, выходы третьего и четвертого сумматора первой группы подключены к первому и второму входам ([n/2]+2)-го сумматора первой группы, выходы остальных сумматоров первой группы соединены аналогичным образом до (n-3)-го и (n-2)-го сумматоров первой группы, подключенных к первому и второму входам (n-1)-го сумматора первой группы, выходы первого и второго шифраторов второй группы подключены к первому и второму входам первого сумматора второй группы, выходы третьего и четвертого шифратора второй группы подключены к первому и второму входам второго сумматора второй группы, выходы остальных шифраторов второй группы соединены с входами сумматоров второй группы аналогичным образом до (n-1)-го и n-го шифраторов, подключенных выходами к входам [n/2]-го сумматора второй группы, выходы первого и второго сумматора второй группы подключены к первым и вторым входам ([n/2]+1)-го сумматора второй группы, выходы третьего и четвертого сумматора второй группы подключены к первому и второму входам ([n/2]+2)-го сумматора второй группы, выходы остальных сумматоров второй группы соединены аналогичным образом до (n-3)-го и (n-2)-го сумматоров, подключенных выходами к первому и второму входам (n-1)-го сумматора второй группы, выход n-го шифратора второй группы подключен к первому входу n-го сумматора второй группы, выход (n-1)-го сумматора второй группы подключен ко второму входу n-го сумматора второй группы, выход (n-1)-го сумматора первой группы подключен к первому входу n-го шифратора второй группы, вторые входы сумматоров по модулю Pi объединены и подключены к выходу n-го сумматора второй группы, управляющие входы шифраторов первой и второй групп, кроме n-го шифратора второй группы, объединены и являются первым управляющим входом устройства, управляющий вход n-го шифратора второй группы является вторым управляющим входом устройства.

| Устройство для округления числа в системе остаточных классов | 1980 |

|

SU951305A1 |

| УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ И ОКРУГЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ | 1992 |

|

RU2018921C1 |

| АНТЕННА ВСЕВОЛНОВАЯ МОНОВИБРАТОРНАЯ | 2000 |

|

RU2210147C2 |

| SU 1190381 A1, 07.11.1984 | |||

| JP 5134851 А, 01.06.1993 | |||

| JP 5173759 А, 13.07.1993. | |||

Авторы

Даты

2007-09-10—Публикация

2005-05-27—Подача