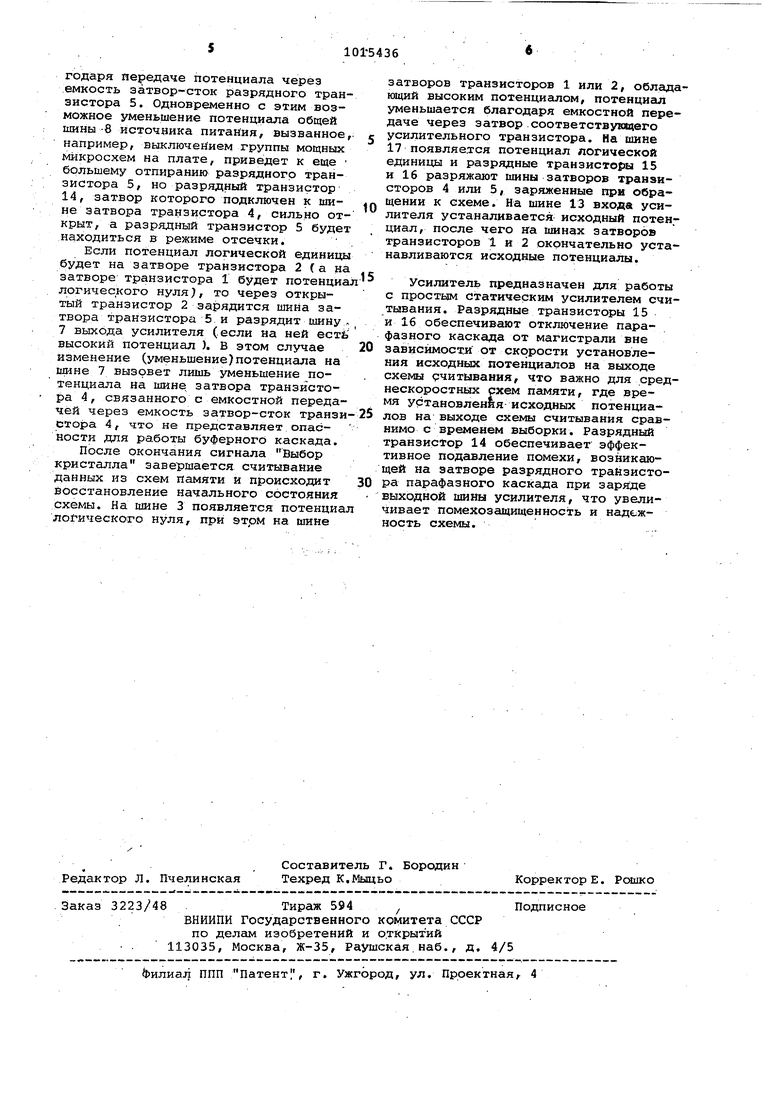

Изоб етение относится к вычислительной технике и может быть исполь зовано при построении микросхем пам ти на МДП-транзисторах. В интегральных схемах памяти на МДП-транзисторах в качестве выхЬдного усилителя используется парафаз ный каскад, выход которого может пр нимать три состояния: логического нуля, логической единицы и состояни с высоким импедансом, при котором оба транзистора парафазного каскада отключены от выходной магистрали. Формирование .сигналов на затворах транзисторов парафазного каскада осуществляют статические вентили, управляемые усилителем считывания. Для снижения потребляемой модности и увеличения быстродействия схе буферного каскада применяют диффере циальные усилители., используемые в качестве предусилителя данного и для формирования прямого и рнверсно го сигналов данного l, а для упра ления парафазным каскадом использую динамические повторители, позволяютцие без потерь мощности формировать прямой или инверсный сигналы данного с амплитудой, равной напряжени источника питания. Однако дифференциальные усилител являются наиболее сложными узлами микросхемы, они предъявляют жесткие требования к качеству технологического процесса, особенно к разбросам параметров элементов и, кроме того, чувствительны к помехам, возникающим в интегральных, схемах при переключении логических вентилей. Обеспечение высокой помехоустойчивости схем выходных усилителей приводит к значительному усложнению схемных решений и увеличению площади, занимаемой схемой на кристалле. Наиболее близок к предлагаемому по техничской сущности выходной усилитель, в котором затворами транзисторов парафазного каскада управляют динамические повторители, а формирование прямого и инверсного сигна лов данного, управляющих работой выходного усилителя, выполняет дифференциальный усилитель считывания, что позволяет добиться высокого быстродействия схемы 2J. Рост напряжения на выходе буферного каскада известной схемы передается через емкость перекрытия затвор-сток разрядного транзистора пар фазного каскада на его затвор, не имеющий в этот момент гальванической связи с шинами источника питания. В современных п-канальных ИС величин пороговых напряжений транзисторов до стигают весьма низких значений (до 0,5 в), так что вследствие передачи потенциала Ь выходного ,усилителя на затвор разрядного транзистора величина потенциала на затворе разрядного транзистора может превысить пороговое напряжение транзи,стора. Кроме того, потенциал общей шины источника питания в вьочислительной системе (на плате) в общем случае колеблется вследствие одновременного переключения групп мощных приборов. При ,налойсении этих эффектов может возникнуть паразитное открывание разрядного транзистора парафазного каскада, приводящее к появлению, сквозного тока- и, соответственно, к непредвиденному росту потребляемой мощности, а также к уменьшению уровня логической единицы на выходе буферного каскада и увеличению длительности фронта выходного сигнала. Таким образом, для системы памяти, где время для приема сигнала жестко ограничено, указанные эффекты могут привести к считыванию ложной информации. Цель изобретения - повышение помехоустойчивости усилителя. Указанная цель достигается тем, что выходной усилитель, содержащий первый и второй усилительные транзисторы, истоки которых соединены с первой шиной тактового сигнала, стоки первого и второго усилительных транзисторов соединены соответственно с затворами зарядного и первого разрядного транзисторов, исток первого разрядного транзистора соединен с первой шиной питания, сток соединен с истоком зарядного транзистора и является выходом усилителя, сток зарядного транзистора соединен со второй шиной питания, затворы первого и второго усилитель- ных транзисторов соединены соответственно с истоками первого и второго проходных транзисторов, сток второго проходного транзистора соединен с истоком, нагрузочного транзистора и стоком ключевого транзистора, затвор которого является входом усилителя, дополнительно содержит второй, третий и четвертый разрядные транзисторы, истоки которых соединены с первой вшной питания, стоки второго и третьего разрядных транзисторов соединены с затвором первого разрядного транзистора, затвор второго разрядного транзистора соединен с затвором зарядного транзистора и стоком четвертого разрядного транзистора, затвор которого соединен с затвором третьего разрядного транзистора и второй шиной тактового сигнала, затворы первого и второго проходных транзисторов соединены с третьей шиной питания, сток первого проходного транзистора соединен с затвором ключевого транзистора, исток которого соединен с первой шиной питания, затвор и сток нагрузочного транзистора соединены с четвертой шиной питания. На чертеже представлена схема выходногр усилителя. I Выходной усилитель содержит первый 1 и Второй 2 усилительные транзи сторы, истоки которых соединены с первой шийой 3 тактового сигнала, стоки первого 1 и второго 2 усилительных транзисторов соединены соответственно с затворами зарядного 4 и первого разрядного 5 транзисторов исток первого разрядного5 транзисто ра соединен с первой шиной б питания сток соединен с истоком зарядного j транзистора и является выходом 7 уси лителя, сток зарядного транзистора 4 соединен со второй шиной 8 питания, затворы первого 1 и второго 2 усилительных транзисторов соединены соответственно с истоками первого 9 и второго 10 проходных транзисторов, сток второго проходного транзистора 10соединен с истоком нагрузочного 11транзистора и стоком ключевого 12транзистора, затвор которого явля ется входом 13 усилителя, истоки вто рого 14, третьего 15 и четвертого 1 разрядных транзисторов соединены с первой шиной б питания, стоки второ го 14 и третьего 15 разрядных транзисторов соединены с затвором первого разрядного транзистора 5, затво второго 14 разрядного тра.нзистора соединен с затвором зарядного транзистора 4 и стоком четвертого разрядного транзистора 16, затвор кото рого соединен с затвором третьего 15 разрядного транзистора и второй шиной 17 тактового сигнала, затворы первого 9 и второго 10 проходных транзисторов соединены с третьей .цш ной 18 питания, сток первого проходного 9 транзистора соединен с за твором ключевого транзистора 12, исток которого соединен с первой ши ной 6 питания, затвор и исток нагру зочного транзистора соединены с. чет вертой 19 шиной питания. Предлагаемый усилитель работает следующим образом. В течение периода ожидания на ши не 17 тактового сигнала поддерживается потенциал логической единицы, разрядные транзисторы 15, 16 открыты, что обеспечивает сохранение nufтенциала логического нуля на затворах транзисторов 4 и 5. Парафазный каскад, состоящий из транзисторов .4 и 5, оказывается таким образом отключенным от выхода усилителя 7. На шине 3 поддерживается потенциал логического нуля. На входе усилителя 13 установлен потенциал, соответствующий невыбранному состоянию (.например. Уровень логического нуля). Тогда на стоке транзистора 10 будет . сформирован инверсный сигнал (уровень логической единица при помощи транзисторов 11 и 12, образующих статический инвертор. При обращении к схеме памяти Снизкий уровень сигнала Выбор кристалла5 после появления данного на выходе усилителя считывания, подключенного к шине 13 входа усилителя, происходит либо изменение потенциала шины 13, ли1бо потенциал сохраняется неизменным. Пусть, например, на шине 13 входа усилителя потенциал принял значение логической единицы, тогда на стоке транзистора 10 установится потенциал логического нуля и разрядится затвор транзистора 2 через проходной транзистор 10. При этом затвор транзистора 1 будет зарялсаться через проходной Транзистор 9 до потенциала равного и/е г где величина опорного напряжения на шине 18; и - пороговое напряжение тран зистора. Величина опорного напряжения на шине 18 должна выбираться такой, чтобы потенциал на затворе транзистора 1 или на затворе транзистора 2 в обратном случае был достаточно высок для того, чтобы обеспечить .эффективную работу усилительных транзисторов. В то же время слишком высокое значение потенциала на шине 18 приведет к увеличению времени переключения шин затворов транзисторов 1и 2. В предлагаемой схеме величина опорного напряжения выбрана равной 8 , напряжение второго источника постоянного питания (Eq 4iQ 12В;. После установления потенциалов на шинах затворов транзисторов 1 и 2усилитель подготовлен к передаче данного на магистраль. После приема сигнала Чтение, на шине 17 тактового сигнала появляется потенциал логического нуля и разрядные транзисторы 15 и 16 пере ходят в режим отсечки. На шине 3 тактового сигнала появляется положительный фронт импульса, приводящий к заряду шины затвора транзистора 4 через открытый транзистор 1 при этом на затворе транзистора 1 растет потенциал благодаря емкостной передаче через емкость затвора транзистора 1. Открывающийся транзистор 4 заряжает шину 7 выхода усилителя. Во время зар5зда шины 7 на затворе транзистора 5, не имеющей связи , с шинами источника питания, начинается паразитный рост потенциала бла-годаря Передаче потенциала через емкость затвор-сток разрядного тран зистора 5. Одновременно с этим возможное уменьшение потенциала общей шины -8 источника питания, вызванное например, выключением группы мощных микросхем на плате, приведет к еще большему отпиранию разрядного транзистора 5, но разрядный транзистор 14, затвор которого подключен к шине затвора транзистора 4, сильно открыт, а разрядный транзистор 5 будет находиться в режиме отсечки. Если потенциал логической единицы будет на затворе транзистора 2 (а на затворе транзистора 1 будет потенциа логического нуля, то через открытый транзистор 2 зарядится шина затвора транзистора 5 и разрядит шину 7 выхода усилителя (.если на ней ecT4 высокий потенциал ). В этом случае изменение (уменьшение)потенциала на шине 7 вызовет лишь уменьшение потенциала на шине затвора транзистора 4 , связанного с емкостной передачей через емкость затвор-сток транзи стора 4, что не представляет опасности для работы буферного каскада. После окончания сигнала Выбор кристалла завершается считывание данных из схем памяти и происходит восстановление начального состояния схемы. На шине 3 появляется потенциа логического нуля, при этрм на шине затворов транзисторов 1 или 2, обладающий высоким потенциалом, потенцигш уменьшается благодаря емкостной передаче через затвор соответствугацего усилительного транзистора. На шине 17 появляется потенциал логической единицы и разрядные транзистор 15 и 16 разряжают шины затворов транзисторов 4 или 5I заряженные при обращении к схеме. На шине 13 входа усилителя устаналивается исходный потенциал, после чего на шинах затворов транзисторов 1 и 2 окончательно устанавливаются исходные потенциалы. Усилитель предназначен для работы с простым статическим усилителем считывания. Разрядные транзисторы 15 и 16 обеспечивают отключение парафазного каскада от магистрали вне зависимости от скорости установления исходных потенциалов на выходе схемы считывания, что важно для среднескрростных схем памяти, где время установления исходиьж потенциалов на выходе схемы считывания сравнимо с временем выборки. Разрядный транзистор 14 обеспечивает эффективное подавление помехи, возникающей на затворе разрядного транзистора парафазного каскада при заря:де выходной шины усилителя, что увеличивает помехозащищенность и надежность схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Стробируемый усилитель | 1986 |

|

SU1332525A1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Усилитель считывания на МДП-транзисторах | 1989 |

|

SU1679547A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Усилитель-формирователь выходных сигналов постоянных запоминающих устройств на МОП-Транзисторах | 1983 |

|

SU1140245A1 |

| Усилитель считывания на КМДП-транзисторах | 1983 |

|

SU1088065A1 |

ВЫХОДНОЙ УСИЛИТЕЛЬ, содержа1чий первый и втброй усилительные -.: транзисторы, истоки которых соеди- . нены с первой шиной тактового сигнала, стоки первого и второго усилительных; транзието юв соединенные соответст енно с затворами зарядного и первого разрядного транзисторов, исток первого разрядного транзистора соедш ен с-первой шиНоЙ питания, сток соеданен с истоком зарядного транзистора и является ВЫХОДОМ усилителя, сток зарядного транзистора соединен с второй шиной питания, затворы первого и второго усилительных транзисторов .соединены соответственно с истоками первого и второго проходных транзисторов, сток второго проходного транзистора соединен с истсэком нагрузочного транзистора и стоком ключевого транзистора, затвор которого является входом усилителя, отличающийся тем, что, ,с целью повшиения помехоустойчивости, В него введены второй, третий и четвертый разрядные транзисторы, истоки которых соединены с первой шиной питания, стоки второго и третьего разрядных транзисторов соединены с затворе первого разрядного транзистора, затвс второго разрядного Транзистора соединен с затвором зарядного транзистора и стоком четвертого разрядного транзистора, затвор которого ш соединен с затвором третьего разрядjjoro транзистора и второй шиной такс тового сигнала, затворы первого и второго проходных транзисторов соеди g нены с третьей шиной питания, сток первого. Проходного транзистора соединен, с затвором ключевого транзистора, исток которого соединен с первой ишной питания, затвор и сток нагрузочного транзистора соединены с четвертой шиной питания. jff сд 4 00 d

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4087704 ,кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электроника, 1978, № 7, с.3237 (прототип). | |||

Авторы

Даты

1983-04-30—Публикация

1981-09-21—Подача