Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики.

Известны регистры сдвига кода, выполненные на основе логических элементов И, ИЛИ, НЕ, содержащие в каждом разряде два RS-триггера, четыре элемента И, две шины управления (см. М.А.Карцев Арифметика цифровых машин. Изд. «Наука», Москва, 1969. стр.267, рис.2-51). Недостатком известных устройств является необходимость использования в каждом разряде двух RS-триггеров, что увеличивает аппаратурные затраты и повышает потребление электропитания.

Наиболее близким, принятым за прототип, является реверсивный регистр сдвига (далее объект), приведенный в книге С.А.Майорова и Г.И.Новикова Принципы организации цифровых машин, изд. «Машиностроение», Ленинград 1974, стр.127-132, рис.4.23. Указанный объект выполняет элементарные операции (ЭО) сдвига кода в сторону младших разрядов (вправо) и в сторону старших разрядов (влево) на один разряд за два временных такта. (Под тактом понимается длительность импульсов пересылки кода из основного регистра в вспомогательный и из вспомогательного снова в основной регистр со сдвигом на один разряд). Этот объект также требует двух RS-триггеров на каждый двоичный разряд, шесть элементов И, двух элементов ИЛИ и трех шин управления. Кроме сравнительно больших аппаратурных затрат, упомянутый объект выполняет только две ЭО. Выполнение каждой дополнительной операции требует увеличения оборудования каждого разряда на два элемента И и еще одной шины управления.

Целью изобретения является упрощение объекта за счет исключения из каждого разряда одного RS-триггера, расширение перечня выполняемых ЭО при минимальных затратах оборудования и повышения быстродействия вычислений. Для этого предложен объект, построенный на основе логических элементов И, ИЛИ, НЕ, отличающийся тем, что каждый разряд содержит, информационный вход, шесть шин управления, восемь логических элементов И, три элемента ИЛИ, четыре элемента НЕ, один RS-триггер и информационный выход, при этом первый вход первого элемента И соединен с выходом восьмого элемента И, второй вход этого элемента И связан с выходом восьмого элемента И младшего разряда, первый вход второго элемента И соединен с выходом второго элемента НЕ младшего разряда, второй его вход соединен с выходом второго элемента НЕ i-го разряда, выходы первого и второго элементов И соединены с входами первого элемента ИЛИ, выход которого через первый элемент НЕ связан с первыми входами третьего элемента И и пятого элемента И младшего разряда, вторые входы упомянутых элементов И соединены с третьей и второй шинами управления соответственно, выходы третьего и пятого элементов И подключены к второму и четвертому входам второго элемента ИЛИ, выход которого связан с первыми входами шестого и седьмого элементов И, вторые входы этих элементов связаны с входом и выходом второго элемента НЕ соответственно, вход второго элемента НЕ соединен с выходом восьмого элемента И, выход которого является информационным выходом i-того разряда, выход шестого элемента И соединен с "входом третьего элемента НЕ и с первым входом третьего элемента ИЛИ, выход седьмого элемента И подключен к входу четвертого элемента НЕ, выход третьего элемента НЕ соединен с R-входом RS-триггера, выход четвертого элемента НЕ соединен с S-выходом RS-триггера и с вторым входом восьмого элемента И, второй и третий входы третьего элемента ИЛИ подключен к единичному выходу RS-триггера и к пятой шине управления, а выход связан с первым выходом восьмого элемента И, третий вход этого элемента связан с шестой шиной управления, первая шина управления подключена к первому входу второго элемента ИЛИ, первый вход четвертого элемента И соединен с четвертой шиной управления, второй его вход связан с информационным входом, а выход упомянутого элемента И подключен к третьему входу второго элемента ИЛИ, кроме того, в первый разряд введена седьмая шина управления, подключенная к третьему входу седьмого элемента И, второй вход первого элемента И соединен с выходом восьмого элемента И последнего разряда, первый вход второго элемента И соединен с выходом второго элемента НЕ последнего разряда, выход первого элемента НЕ подключен к первому входу пятого элемента И последнего разряда; в последний разряд устройства введена восьмая шина управления, подключенная к третьему входу седьмого элемента И, кроме того, в состав оборудования введен девятый элемент И, при этом выходы вторых элементов И каждого четного разряда соединены с входами упомянутого элемента И, высокий потенциал с выхода которого является признаком нулей во всех разрядах устройства.

Отметим основные отличительные признаки объекта и покажем, что обеспечивает каждый признак.

1. Третий элемент ИЛИ, восьмой элемент И и второй элемент НЕ с соответствующими связями с выходами шестого элемента И, четвертого элемента НЕ, соответственно, и связь с выхода восьмого элемента И с входами шестого элемента И и второго элемента НЕ обеспечивают временную задержку сигнала с выхода восьмого элемента И на время длительности импульса сдвига, что позволяет исключить из оборудования каждого разряда один RS-триггер.

2. Первый и второй элементы И, первые элементы ИЛИ и НЕ с соответствующими связям запрещают инвертирование (сдвиг) кода двух смежных разрядов, если они хранят коды 11 или 00, и обеспечивают инвертирование старшего разряда смежных разрядов при сдвиге влево и младшего разряда этой пары при сдвиге вправо, если значение кодов 10 или 01.

3. Четвертый элемент И, информационный вход, четвертая, пятая и шестая шины управления с соответствующими связями обеспечивают выполнение ЭО приема кода в регистр, сложение по модулю два, логического умножения и у логического сложения.

4. Первая шина управления, подключенная к первому входу второго элемента ИЛИ, обеспечивает выполнение ЭО инвертирования, приема всех единиц в триггеры и их установку в нуль.

5. Выходы вторых элементов И четных разрядов объекта, соединенные с входами девятого элемента И, обеспечивают автоматическое определение нулевых значений всех триггеров. Это позволяет в ряде конкретных ситуаций сократить время выполнения ЭО сдвига кода влево или вправо, при этом обеспечивается экономия входов упомянутого элемента И в два раза.

6. Подключение седьмой и восьмой шин управления к третьим входам седьмых элементов И первого и последнего разрядов обеспечивает выполнение операций циклического сдвига кода влево и вправо.

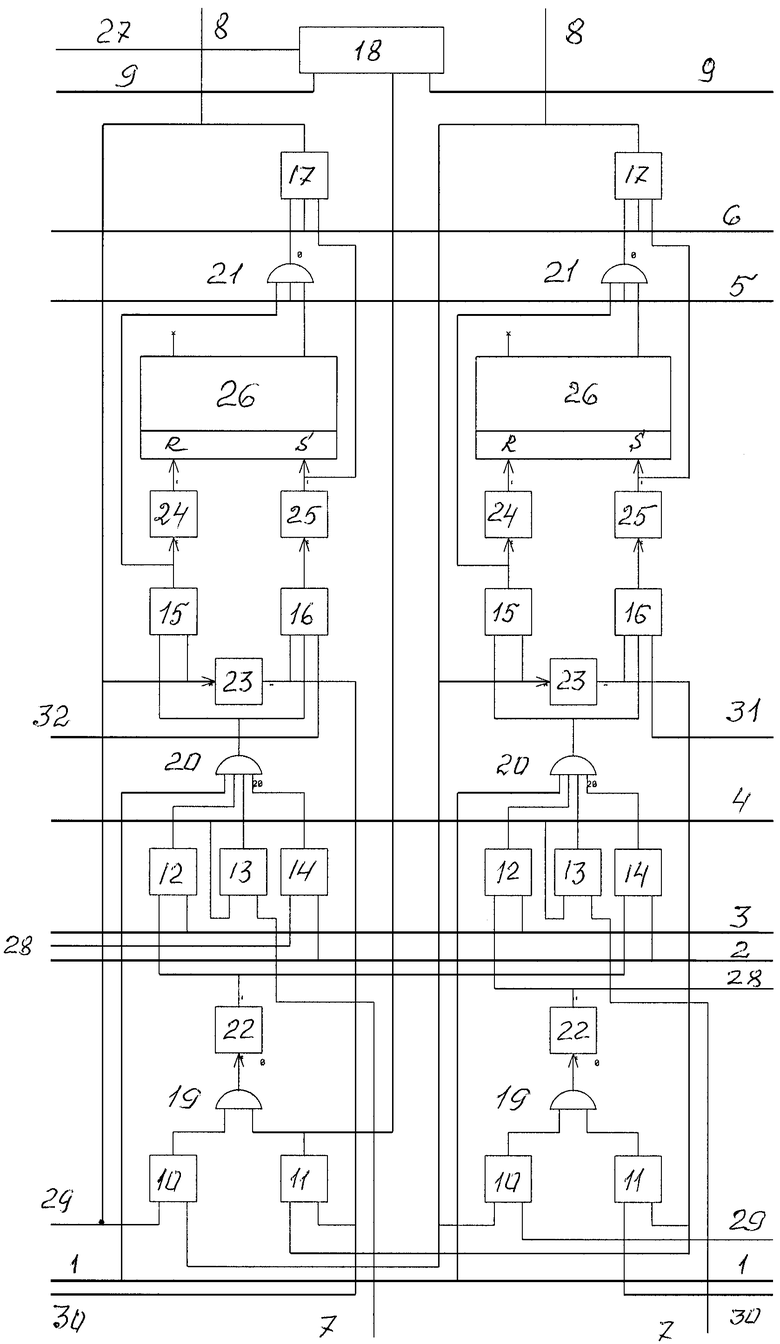

Предлагаемый объект позволяет построить каждый разряд на одном RS-триггере, девяти элементах И, трех элементах ИЛИ, четырех элементах НЕ при шести шинах управления, при этом выполняется десять ЭО (сдвиг влево, сдвиг вправо, циклический сдвиг влево, циклический сдвиг вправо, прием кода, инвертирование кода, сложение по модулю два, логического сложения, логического умножения и определение нулевого значения всех нулей RS-триггеров). Суммарное число входов логических элементов одного разряда объекта равняется 37, т.е. для выполнения одной ЭО в среднем требуется около 3,7 входов, что значительно меньше, чем у прототипа и известных устройств аналогичного назначения. Снижение времени вычислительного процесса достигается за счет расширения перечня выполняемых ЭО, за счет использования схемы определения нулевых значений всех триггеров объекта, а также за счет исключения в каждом разряде одного RS-триггера. В случае использования объекта для управления различными устройствами регулирования обеспечивается сокращение времени от момента поступления импульса сдвига до выработки управляющего потенциала в два раза быстрее, чем в известных устройствах аналогичного назначения. Для пояснения работы на чертеже приведена функциональная схема двух разрядов предлагаемого объекта. Каждый разряд объекта (чертеж) содержит: 1 шину управления (ШУ) инвертированием, 2 ШУ сдвигом вправо, 3 ШУ сдвигом влево, 4 ШУ приемом кода, 5 ШУ ЭО логического умножения, 6 ШУ ЭО логического сложения, 7 информационный вход, 8 информационный выход, 9 вход управления из каждого четного разряда, 10-18 логические элементы И, 19-21 логические элементы ИЛИ, 22-25 логические элементы НЕ, 26 RS-триггер (Tr), 27 признак нулевых значений триггеров, 28 выход с НЕ 22 старшего разряда на И 14 младшего разряда, 29 выход с И 17 i-того разряда на вход И 10 старшего и разряда, 30 выход с НЕ 23 на вход И 11 старшего разряда, 31 ШУ циклическим сдвигом влево, 32 ШУ циклическим сдвигом вправо.

Рассмотрим работу объекта при выполнении всех ЭО. В исходном положении (в статике) все триггеры объекта установлены в нуль, на выходах НЕ 23-25, на ШУ 31, 32, 6, присутствуют высокие разрешающие потенциалы, на выходе НЕ 22, ШУ 1, 2, 3, 4, 5, на входе 7, выходе 8 и единичном выходе Tr 26 - низкие потенциалы.

1. Операция инвертирования кода. Операция выполняется за два временных такта (t1 и t2). По t1 исполнительный импульс (ИИ) по цепи ШУ 1, ИЛИ 20, И 16, НЕ 25 поступает на S-вход Tr 26 и устанавливает его в единицу, т.е. выполнит инвертирование. При этом импульс с выхода НЕ 25 запретит работу И 17 на время длительности импульса инвертир кода, за счет чего условия прохождения импульса на S-вход не меняются. Если Tr 26 до прихода исполнительного импульса хранил код единицы, то высокий потенциал с выхода триггера по цепи элементов ИЛИ 21, И 17 будет разрешать работу И 15 и запрещать прохождение импульса через И 16. Поэтому импульс инвертирования по цепи элементов ШУ 1, ИЛИ 20, И 15, НЕ 24 поступит на R-вход триггера и установит его в нуль, при этом условия прохождения импульса через И 15 на время длительности импульса, поступающего на ШУ 1, сохраняются, т.к. с выхода И 15 через ИЛИ 21, И 17 на входы И 15 и НЕ 23 будет поступать высокий потенциал. Второй временной такт (t2) в этой и во всех последующих ЭО отводится для подготовки объекта к повторению аналогичной или выполнению новой операции. В предлагаемом объекте операция инвертирования является основной (базовой) операцией, т.к. все остальные ЭО выполняются на ее основе. Суммарное оборудование базовой операции, исчисляемое как сумма входов логических элементов одного разряда, равняется 20.

2. Операция сдвига кода вправо. Время выполнения сдвига кода на один разряд равно 2t (t - длительность исполнительного импульса, поступающего на ШУ 2). До прихода первого импульса с ШУ 32 снимается высокий потенциал, а на выходах И 10, 11 i-того разряда будут сформированы высокие потенциалы, если значения кодов триггеров i-того и i-1-го разрядов одинаковы, т.е. триггеры хранят коды 11 или 00. При этом высокий потенциал по цепи ИЛИ 19 поступит на вход НЕ 22, который запретит прохождение исполнительного импульса через И 14 младшего в паре разряда. Если триггеры смежных разрядов хранят коды 10 или 01, то высокий потенциал с выхода НЕ 22 разрешит прохождение импульса через И 14 младшего разряда. Исполнительный импульс по цепи ШУ 2, И 14, ИЛИ 20 поступит на входы И 15, 16 и выполнит инвертирование Tr 26 младшего разряда, т.е. произойдет сдвиг кода, хранящегося в триггере 26, на один разряд вправо. Как видно из описания работы объекта при сдвиге кода вправо, сдвиг кода на один разряд произойдет за время, равное длительности импульса сдвига (t1). Если объект используется как элемент управления различными электронными устройствами, то сдвиг кода на один разряд за время t1 имеет преимущества по быстродействию по сравнению с прототипом в два раза, т.к. в указанных объектах это время равно 2t (пересылка кода в вспомогательный регистр и пересылка в основной регистр со сдвигом). Для реализации ЭО сдвига кода вправо требуется три элемента И, два элемента ИЛИ и один элемент НЕ, т.е. 10 входов логических элементов дополнительного оборудования. После завершения ЭО на ШУ 32 подается высокий потенциал.

3. Операция сдвига кода влево. Операция выполняется аналогично операции сдвига кода вправо (п.2). Отличие состоит только в том, что с ШУ 31 снимается высокий потенциал, а исполнительный импульс поступает на ШУ 3 и далее по цепи элементов И 12, ИЛИ 20 на входы И 15, 16, т.е. при соответствующих условиях инвертироваться будет старший разряд двух смежных разрядов. Для выполнения этой ЭО требуется три входа элементов дополнительного оборудования.

4. Операция циклического сдвига вправо. Выполняется как операция сдвига кода, рассмотренная в п.2. Отличие состоит только в том, что при циклическом сдвиге вправо на ШУ 2 подается высокий (разрешающий) потенциал. При этом потенциал с выхода НЕ 32 самого младшего разряда поступает на первый вход И 14 последнего разряда. Очередной исполнительный импульс по цепи ШУ 2, И 14, ИЛИ 20, И 16, НЕ 25 поступает на S-вход триггера 26 и устанавливает его в единицу. Таким образом, код единицы из самого младшего разряда заносится в триггер 26 самого старшего разряда. Операция будет выполнятся до тех пор, пока не прекратится поступление импульсов сдвига на ШУ2.

5. Операция циклического сдвига влево. Выполняется так же, как это рассмотрено в п.3. Отличие состоит в том, что на ШУ 31 подается высокий (разрешающий) потенциал. При этом потенциал с выхода И 17 самого старшего разряда поступит на вход И 10 самого младшего разряда, а исполнительный импульс по цепи ШУ 3, И 12, ИЛИ 22, И 16, НЕ 25 поступит на S-вход триггера 26 самого младшего разряда и установит его в единицу, т.е. произойдет сдвиг единицы из самого старшего разряда в младший разряд. Операция будет выполняться до тех пор, пока на ШУ 3 будут поступать импульсы сдвига влево. Для реализации операции циклического сдвига влево требуется только один вход элемента И 16 младшего разряда и одна ШУ 31.

6. Операция сложения по модулю два. Операция выполняется за два временных такта. Первое слагаемое хранится в Tr 26, второе - поступает в объект по информационным входам 7. По t1 на ШУ 4 поступает исполнительный импульс и, если по входу 7 поступает высокий потенциал, соответствующий коду единице, то исполнительный импульс по цепи ШУ 4, И 13, ИЛИ 20 поступает на выходы И 15, 16 и выполнит инвертирование кода Tr 26. Если на входе 7 отсутствует высокий потенциал, что соответствует коду нуля в рассматриваемом разряде, то значение Tr 26 сохранение (п.1). Для выполнения операции требуется дополнительно три входа логических элементов И 13, ИЛИ 20.

7. Операция логического сложения. Выполняется за два временных такта. Первое слагаемое хранится в Tr 26, второе - поступает по входу 7. До прихода исполнительного импульса с ШУ 6 снимается высокий потенциал, что обеспечивает появление высокого потенциала с выхода НЕ 23. По t1 на ШУ 4 поступает исполнительный импульс. Если на входе 7 присутствует высокий потенциал, то исполнительный импульс по цепи ШУ 4, И 13, ИЛИ 20, И 16, НЕ 25 поступает на S-вход Tr 26 и устанавливает его в единицу. Для выполнения этой операции требуется один дополнительный вход И 17.

8. Операция логического умножения. Выполняется за два временных такта. Первый сомножитель хранится в Tr 26, а инверсный код второго сомножителя поступает по входу 7. До прихода исполнительного импульса на ШУ 5 поступает высокий потенциал, который по цепи элементов ИЛИ 21, И 17 поступает на входы И 15, НЕ 23. По t1 на ШУ 4 поступает исполнительный импульс. Если код второго сомножителя рассматриваемого разряда равен инверсному значению нуля, т.е. единице, то исполнительный импульс по цепи элементов И 13, ИЛИ 20, И 15, НЕ 24 поступит на R-вход Tr 26 и установит его в нуль. На этом выполнение логического умножения закончено. Для выполнения операции требуется дополнительно один вход элемента ИЛИ 21 (без учета оборудования в схемах формирования инверсного кода второго сомножителя).

9. Операция приема кода. Предлагаемый объект может выполнить параллельный прием кода как прямым, так и инверсным кодом. Для приема прямого кода требуется предварительная установка в нуль Tr 26 с последующим приемом кода, поступающего по входу 7 (операция приема кода рассмотрена в п.5). Для получения инверсного значения принятого кода предварительно выполняется ЭО инвертирования всех триггеров регистра (п.1). Возможны и другие варианты выполнения этой ЭО.

10. Операция определения кода нуля во всех триггерах. Если во всех Tr 26 будут храниться коды нулей, то высокие потенциалы с выходов И 11 четных разрядов поступят на входы И 18 и выработают управляющий потенциал, который используется для управления выполнением последующих ЭО, например, приемом нового кода в регистр и осуществление его сдвига вправо или влево. При выполнении этих ЭО можно оценить ожидаемое повышение быстродействия их выполнения. Например, если выполняется сдвиг кода вправо только одной единицы, принятой в самый младший разряд, то время ЭО равно t. Если же сдвигается код единицы, принятой в самый старший разряд или во все разряды объекта, то время выполнения ЭО будет равно 2tn и среднее значение будет равно nt. В прототипе это время всегда равно 2nt, что обеспечивает повышение быстродействия при выполнении ЭО сдвига кодов приблизительно в два раза, при этом для построения схемы определения кода нулей во всех разрядах требуется элемент И 18 на n/2 входов. В прототипе такая схема потребует n входов.

11. ЭО установки нуля триггеров. Все триггеры объекта одновременно устанавливаются в нуль за счет одновременного поступления исполнительных импульсов на ШУ 1 и 5. При этом на второй вход И 15 по цепи ШУ 5, ИЛИ 21, И 17 поступает высокий потенциал. Исполнительный импульс по цепи ШУ 1, ИЛИ 22, И 15, НЕ 24 поступает на R-вход Tr 26 и устанавливает его в нуль. Для реализации этой операции в разрядной части объекта не требуется дополнительного оборудования.

12. ЭО установки в нуль отдельного триггера. Для ее выполнения на ШУ 5 подается высокий потенциал, который по цепи ИЛИ 21, И 17 поступает на второй вход И 15. Если на входе 7 i-того разряда присутствует высокий потенциал, соответствующий коду единицы, то исполнительный импульс по цепи ШУ 4, И 13, ИЛИ 20, И 15, НЕ 24 поступает на R-вход Tr 26 и устанавливает его в нуль. Для выполнения этой ЭО не требуется дополнительного оборудования.

13. ЭО установки единиц всех триггеров. Для выполнения этой операции с ШУ 6 снимается высокий потенциал, а на ШУ 1 подается исполнительный импульс. При этом высокий потенциал с выхода НЕ 23 разрешает прохождение импульса по цепи ШУ 1, ИЛИ 20, И 16, НЕ 25 на S-вход триггера 26 и устанавливает его в единицу. Для выполнения этой ЭО не требуется дополнительного оборудования.

Таким образом, предлагаемый объект расширяет перечень выполняемых ЭО по сравнению с прототипом в шесть раз, повышает быстродействие выполнения вычислений при минимальных затратах оборудования. Оборудование одного разряда, определяемого суммарным числом входов логических элементов, равняется 37. В среднем для выполнения одной ЭО требуется около 3 входов. В прототипе и в других известных устройствах эти показатели значительно выше.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР КОМБИНАЦИОННО-НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262736C1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2264646C2 |

| СДВИГАЮЩИЙ РЕГИСТР | 2007 |

|

RU2344498C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2005 |

|

RU2284654C2 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2010 |

|

RU2419200C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является упрощение устройства, расширение перечня выполняемых операций и повышение быстродействия вычислений при минимальных затратах оборудования. Каждый разряд устройства содержит один RS-триггер, восемь элементов И, три элемента ИЛИ, четыре элемента НЕ, шесть шин управления. 1 з.п. ф-лы, 1 ил.

| Накапливающий сумматор | 1985 |

|

SU1291968A1 |

| SU 1292479 A1, 07.10.1986 | |||

| Накапливающий сумматор | 1987 |

|

SU1418705A1 |

| Счетчик импульсов | 1986 |

|

SU1422404A1 |

| US 4991186, 05.02.1991 | |||

| БУКРЕЕВ И.Н | |||

| и др., Микроэлектронные схемы цифровых устройств, Москва, Сов | |||

| радио, 1973, с.147. | |||

Авторы

Даты

2007-10-27—Публикация

2006-02-21—Подача