Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики.

Известны сумматоры накапливающего типа (далее - объект), выполненные на основе трех типов логических элементов (ЛЭ) И, ИЛИ, НЕ (смотри, например, книгу М.А. Карцев. Арифметика цифровых машин. М., Наука, 1969, стр. 247, 288; а.с. № 911517, кл. G 06 F 7/50).

Недостатком объекта является наличие трех RS-регистров, что увеличивает аппаратурные затраты, потребление электроэнергии, и некоторое снижение быстродействия.

Наиболее близким, принятым за прототип, является объект по а.с. № 538365.

Известный объект не может быть использован в устройствах, выполняющих операции умножения, т.к. не выполняет элементарные операции (ЭО) сдвига кодов в сторону младших и старших разрядов. Названный объект содержит в каждом двоичном разряде два RS-триггера, что является его недостатком.

Задачей изобретения является сокращение оборудования, повышение быстродействия и расширение перечня выполняемых операций (сдвиг кода влево, сдвиг кода вправо).

Для чего предложен объект, содержащий в каждом разряде один триггер типа RS, установочные входы которого подключены к выходам первого и второго элементов И, первые входы которых объединены и подключены к выходу первого элемента ИЛИ, выход второго элемента ИЛИ соединен с вторым входом второго элемента И и через первый элемент НЕ подключен к второму входу первого элемента И, выход которого через второй элемент НЕ подключен к входу третьего элемента И, второй и третий входы которого соединены с нулевым выходом триггера и первой шиной управления, выход упомянутого элемента И соединен с первым входом второго элемента ИЛИ, второй его вход связан с "единичным" входом триггера, а третий вход подключен к второй шине управления, к входу первого элемента ИЛИ подключен выход четвертого элемента И, первый и второй входы которого подключены к шине переноса из младшего разряда и третьей шине управления; также содержащей группу элементов И-ИЛИ приема кода в сумматор и группу элементов ИЛИ-И формирования сигналов переноса в старший разряд, ОТЛИЧАЮЩИЙСЯ тем, что первые входы пятого и шестого элементов И подключены к четвертой и пятой шине управления, вторые входы этих элементов соединены с числовыми шинами приема прямого и инверсного кодов соответственно, а выходы упомянутых элементов И подключены к входам третьего элемента ИЛИ, выход которого соединен с входом первого и четвертого элементов ИЛИ; второй вход четвертого элемента ИЛИ соединен с выходом седьмого элемента И, а третий вход связан с выходом первого элемента НЕ; первый вход пятого элемента ИЛИ соединен с нулевым входом триггера, его второй вход связан со вторым входом четвертого элемента ИЛИ, а третий вход связан с шиной переноса из младшего разряда и входом четвертого элемента И; выходы четвертого и пятого логических элементов И соединены с первым и третьим входами седьмого элемента И, второй вход этого элемента связан с шестой шиной управления, а его выход является шиной переноса в старший разряд, кроме того, введен восьмой элемент И, первый вход которого соединен с выходом триггера старшего разряда, второй вход подключен к выходу второго элемента НЕ, а его третий вход связан с седьмой шиной управления, выход упомянутого элемента И подключен к четвертому входу второго элемента ИЛИ; к третьему входу первого элемента ИЛИ подключена восьмая шина управления, к четвертому входу второго элемента ИЛИ подключена девятая шина управления.

Предлагаемый объект позволяет построить каждый разряд объекта на основе только одного RS-триггера, при этом совмещаются во времени выполнение ЭО приема второго слагаемого, первого сложения по модулю два, формирования и запоминания сигнала переноса, что повышает быстродействие выполнения арифметических операций. Обеспечивается выполнение ЭО сдвига кода в сторону младших и старших разрядов и инвертирования кода регистра при минимальных затратах оборудования, т.е. расширяются функциональные возможности объекта. Кроме того, приблизительно в полтора раза сокращается потребление электроэнергии.

Отметим основные отличительные признаки и что они позволяют получить:

1. Соединение выхода третьего элемента ИЛИ с входом четвертого и первого элементов ИЛИ обеспечивает формирование переноса и инвертирование кода первого триггера;

2. Соединение выхода седьмого элемента И с вторым входом четвертого и пятого элементов ИЛИ обеспечивает "хранение" сигнала переноса, выработанного в данном разряде, что позволяет исключить из состава оборудования регистр для хранения второго слагаемого;

3. Подключение шестой шины к второму входу седьмого элемента И позволяет гасить потенциалы переносов одновременно во всех разрядах объекта после выполнения второго сложения по модулю два;

4. Подключение входов восьмого элемента И к выходу второго элемента НЕ, к "единичному" выходу триггера старшего разряда и к седьмой шине управления обеспечивает выполнение ЭО сдвига кода в сторону младших разрядов;

5. Соединение выхода первого элемента И с входом пятого элемента ИЛИ обеспечивает формирование переноса в данном разряде.

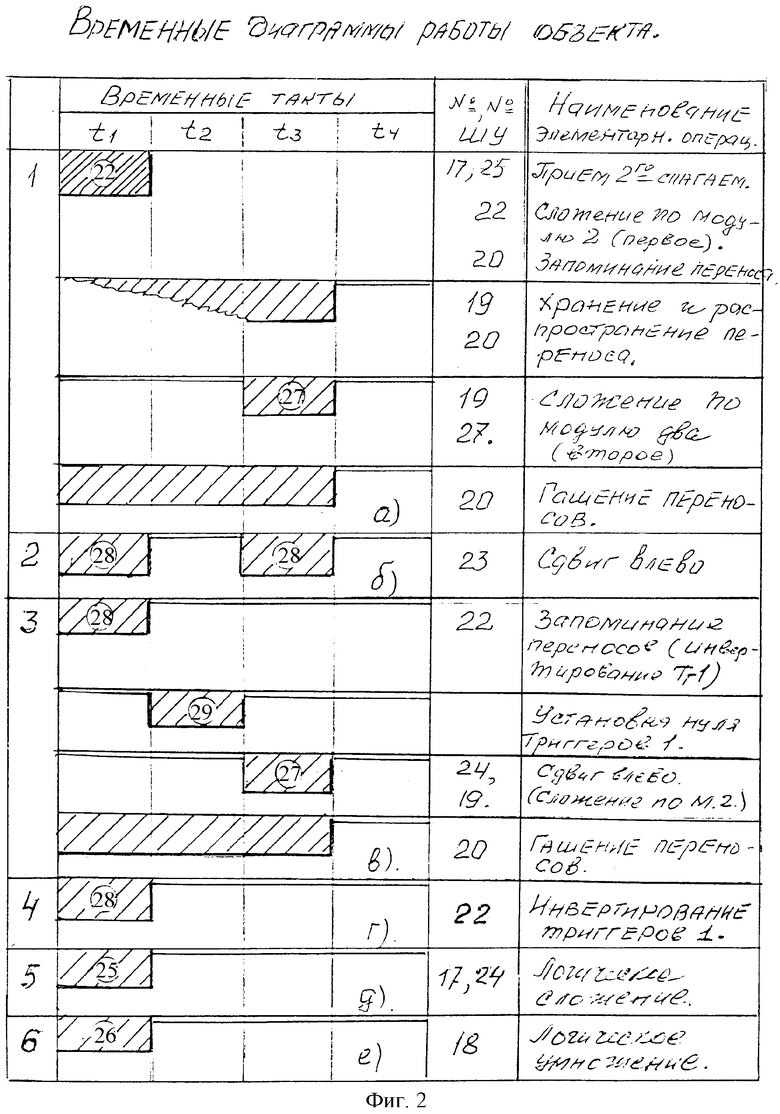

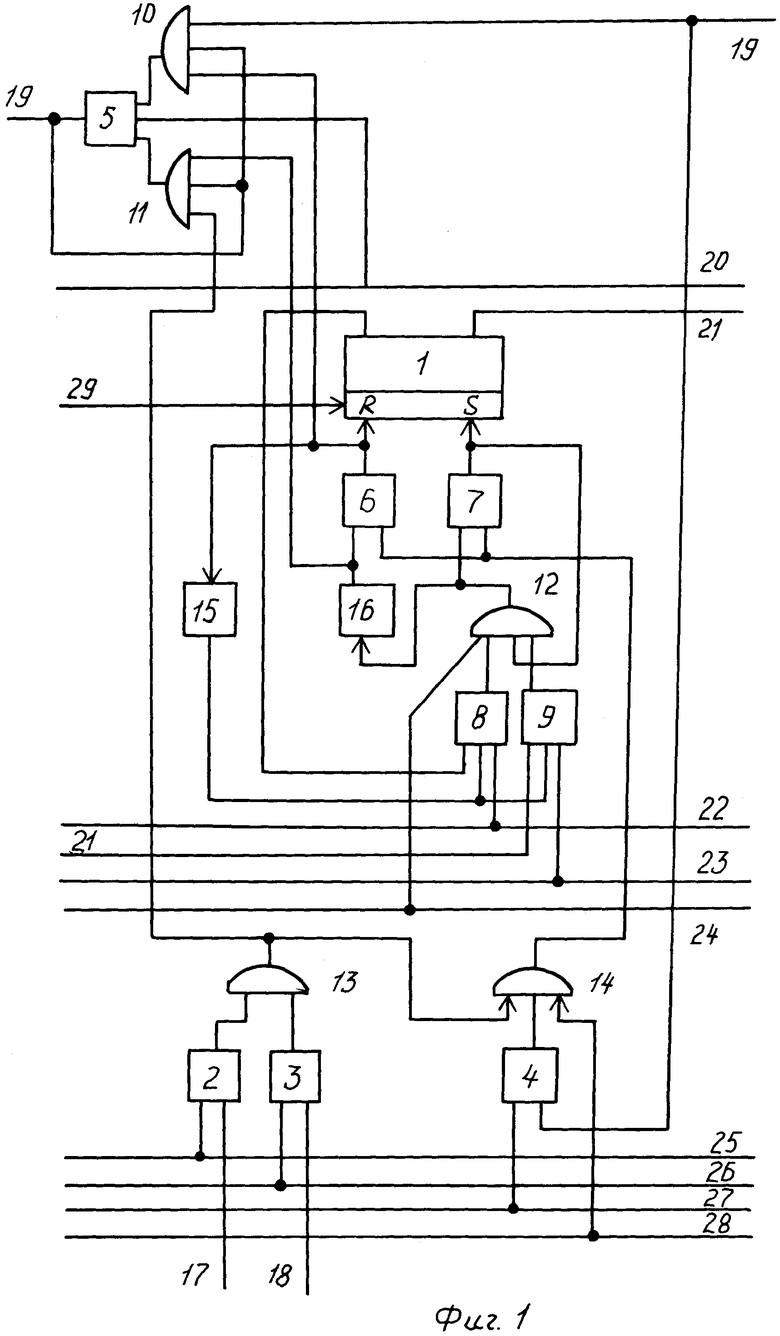

Для пояснения работы описываемого объекта на Фиг.1 приведена функциональная схема (один разряд), а на Фиг.2 приведены временные диаграммы его работы.

Объект содержит RS-триггер 1, элементы И 2-9, элементы ИЛИ 10-14, элементы НЕ 15, 16, информационную шину приема числа 17, информационную шину приема инверсного кода числа 18, шину переноса 19, шину гашения переноса 20, шину инвертирования триггера 22 (потенциал), шину сдвига кода вправо 23, шину логических операций 24, шину приема кода 25, шину приема инверсного кода 26, шину сложения по модулю два (второго) 27, шину инвертирования триггера 28 (импульс), шину установки нуля триггера 29.

Предложенный объект работает следующим образом.

Операция сложения. В исходном состоянии код первого слагаемого хранится в регистре сумматора (триггеры 1). Код второго слагаемого поступает по информационной шине 17. Для выполнения операции на управляющие шины 20 и 22 подаются высокие потенциалы, которые сохраняют свое значение в ходе всей операции (t1, t2, t3). По первому временному такту (t1) на шину 25 подается исполнительный импульс. Если на шине 17 присутствует потенциал, соответствующий коду единицы, то исполнительный импульс по шине И 2, ИЛИ 13, 14 поступит на первые входы элементов И 6, 7. Одновременно этот же импульс поступит на первый вход ИЛИ 11. Если до прихода t1 в триггере хранился код "нуля", то на входы И 8 поступят высокие потенциалы с "нулевого" выхода триггера и с выхода НЕ 15 и выработают потенциал, который с выхода И 8, через ИЛИ 12 разрешит прохождение t1 через И 7 на "единичный" вход триггера 1. Упомянутый триггер будет установлен в "единицу", т.е. его состояние будет проинвертировано. Одновременно t1 с "единичного" входа триггера поступит на вход ИЛИ 12 и поддержит прохождение импульса на единичный вход в течение длительности исполнительного импульса. Во время t1, если по шине 19 поступил перенос из младшего разряда, с выходов ИЛИ 10, 11 на входы И 5 поступят сигналы, которые выработают сигнал переноса в старший разряд. Этот сигнал будет "храниться" до окончания операции за счет связи с выхода И 5 с входом ИЛИ 10, 11. Если до прихода t1 в триггере 1 хранился код "единицы", то с выхода И 8, через ИЛИ 12 на входы И 7, НЕ 16 не будет поступать потенциал, разрешающий работу И 7. При этом высокий потенциал с выхода НЕ 16 разрешит прохождение t1 на "нулевой" вход триггера 1. Триггер будет установлен в "нуль", т.е. его состояние будет проинвертировано. Одновременно t1 через НЕ 15 будет запрещать работу И 8 на время длительности исполнительного импульса и, проходя по цепи ИЛИ 10, И 5, выработает сигнал переноса в старший разряд. Сигнал переноса в старший разряд также будет выработан, если на шине 17 отсутствует высокий потенциал, а из младшего разряда по шине 19 поступил сигнал переноса. При этом высокий потенциал с выхода НЕ 16 через ИЛИ 11 вместе с потенциалом шины переноса 19 выработают сигнал переноса в старший разряд.

По t2 продолжается распространение сигналов переноса от младших разрядов в сторону старших разрядов.

По t3 выполняется второе сложение по модулю два результата первого сложения с сигналом переноса. Для выполнения этой ЭО на шину 27 подается исполнительный импульс. Если в разряд сумматора по шине 19 на вход И 4 поступил сигнал переноса, то импульс проходит по цепи И 4, ИЛИ 14 на входы элементов И 6,7. Этим импульсом производится инвертирование триггера 1. На этом, собственно, операция сложения заканчивается, но для подготовки объекта к выполнению новой операции сложения необходимо "погасить" потенциалы переносов, подав соответствующий импульс на шину 20 (Фиг.2, а).

Операция вычитания выполняется аналогично выполнению операции сложения. Отличие состоит в том, что по t1 принимается в устройство инверсный код числа. Для этого исполнительный импульс подается на шину 26. Исполнительный импульс проходит по цепи И 3, ИЛИ 13,14 на входы И 6, 7.

Элементарная операция сдвига кода в сторону младших разрядов выполняется за один временной такт t1 на один разряд. Для выполнения ЭО сдвига кода на шину 23 подается управляющий потенциал, а на шину 28 подается исполнительный импульс, который по цепи ИЛИ 14 поступает на первые входы элементов И 6, 7. Если из старшего разряда по шине 21 на вход И 9 i-того разряда поступает потенциал "единицы", а с выхода НЕ 15 на второй вход элемента И также поступает высокий потенциал, то с выхода элемента И 9 через элементы ИЛИ 12, И 7 на "единичный" вход поступит исполнительный импульс и установит триггер 1 в "единицу". Если в старшем разряде объекта хранится код "нуля", то на выходе И 12 высокий потенциал будет отсутствовать, а с выхода НЕ 16 на вход И 6 поступит высокий потенциал, разрешающий прохождение исполнительного импульса через И 6 на нулевой вход триггера 1. Таким образом, за один временной такт будет выполнен сдвиг кода на один разряд в сторону младших разрядов (вправо). По окончании выполнения сдвигов с шин 22, 23 управляющий потенциал снимается (Фиг.2, б).

ЭО сдвига кода в сторону старших разрядов (нормализация, умножение кода на 2, 4, 8 и т.д.) выполняется за четыре временных такта на один разряд. Исполнительный импульс t1 подается на шину 28 и через ИЛИ 14 поступает на первый вход И 6. На второй вход упомянутого элемента И с выхода элемента НЕ 16 поступает высокий потенциал, если в триггере 1 хранится код "единицы". При наличии сигналов на всех трех входах элемента И 5 на его выходе вырабатывается сигнал переноса в старший разряд. Этот сигнал "запоминается" (фиксируется) за счет связи выхода И 5 с входами ИЛИ 10, 11.

По t2 триггеры 1 объекта устанавливаются в "нуль" за счет подачи импульса на шину 29.

По t3 выполняется, собственно, сдвиг кода влево на один разряд. Для выполнения этой ЭО на шину 27 подается управляющий потенциал, который по цепи ИЛИ 12 поступает на второй вход И 7, а на шину 27 поступает исполнительный импульс. Этот импульс, в случае наличия сигнала переноса из младшего разряда по шине 19, по цепи И 4, ИЛИ 14, И 7 поступит на "единичный" вход триггера 1 и установит его в "единицу". ЭО выполнена.

По t4 выполняется вспомогательная ЭО гашения переносов, подготавливающая объект к выполнению следующих ЭО. Для ее выполнения с шины 20 снимается высокий потенциал, запрещающий прохождение сигналов через И 5. Таким образом, сигналы переносов гасятся во всех разрядах объекта одновременно (Фиг.2, в).

ЭО инвертирования кода, хранящегося в триггерах 1, выполняется за один временной такт t1. Для ее выполнения на шину 22 подается управляющий потенциал, а на шину 28 - исполнительный импульс. Если в триггере 1 хранится код "нуля", высокий потенциал с "нулевого" выхода через элементы И 8, ИЛИ 12 поступит на первый вход элемента И 7 и разрешит прохождение исполнительного импульса по цепи ИЛИ 14, И 7 на "единичный" вход триггера 1. Если в триггере 1 хранится код "единицы", то с выхода элемента НЕ 16 на первый вход И 6 поступит высокий потенциал и разрешит прохождение исполнительного импульса на "нулевой" вход триггера 1 (Фиг.2, г).

ЭО логического сложения выполняется за один временной такт. Код первого слагаемого хранится в триггере 1, код второго слагаемого поступает по шине 17. На шину 24 подается управляющий потенциал, а на шину 25 - исполнительный импульс, который по цепи И 2, ИЛИ 13, 14, И 7 поступит на "единичный" вход триггера, если в данном разряде на шине 17 присутствует сигнал, соответствующий коду "единица". Операция закончена (Фиг.2, д).

ЭО логического умножения выполняется за один временной такт. До начала выполнения ЭО первый сомножитель хранится в триггерах 1. Второй сомножитель принимается с информационной шины 18 в инверсном коде. Исполнительный импульс по цепи И 3, ИЛИ 13, 14, И 6 проходит на "нулевой" вход триггера и устанавливает его в "нулевое" состояние, если на шине 18 присутствует высокий потенциал, соответствующий инверсному значению кода второго сомножителя. Операция закончена.

ЭО сложения по модулю два детально рассмотрена при описании работы объекта по выполнению операции сложения.

Таким образом, предлагаемый объект позволяет повысить быстродействие выполнения операций сложения (вычитания) по сравнению с прототипом в оптимальном режиме работы приблизительно на 20%. (Оптимальный режим работы предполагает tи=tn; Тпер. max=2tи, здесь tи - длительность исполнительного импульса; tn - длительность паузы между исполнительными импульсами; Тпер. мах - максимальное время распространения сигнала переноса.)

Также расширяется перечень выполняемых ЭО: в объекте выполняются дополнительно операции сдвига влево (нормализация, умножение на 2, 4, 8 и т.д.) и сдвига вправо (деление на 2, 4, 8 и т.д.). Кроме того, достигается некоторое снижение потребления электроэнергии за счет исключения из состава оборудования одного триггерного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| СУММАТОР КОМБИНАЦИОННО-НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262736C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА ВЛАСОВА | 2006 |

|

RU2309536C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2264646C2 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2005 |

|

RU2284654C2 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является сокращение оборудования, повышение быстродействия и расширение перечня выполняемых операций. Устройство содержит в каждом разряде один RS-триггер, восемь элементов И, пять элементов ИЛИ, два элемента НЕ, девять шин управления. 2 ил.

Сумматор накапливающего типа, содержащий в каждом разряде один RS-триггер, первый, второй, третий, четвертый, пятый, шестой и седьмой элементы И, первый, второй, третий, четвертый и пятый элементы ИЛИ, первый и второй элементы НЕ, первую, вторую и третью шины управления, причем установочные входы RS-триггера подключены к выходам первого и второго элементов И, первые входы которых объединены и подключены к выходу первого элемента ИЛИ, выход второго элемента ИЛИ соединен с вторым входом второго элемента И и через первый элемент НЕ подключен к второму входу первого элемента И, выход которого через второй элемент НЕ подключен к входу третьего элемента И, второй и третий входы которого соединены с нулевым выходом триггера и первой шиной управления, выход упомянутого элемента И соединен с первым входом второго элемента ИЛИ, второй его вход связан с "единичным" входом триггера, а третий вход подключен к второй шине управления; к входу первого элемента ИЛИ подключен выход четвертого элемента И, первый и второй входы которого подключены к шине переноса из младшего разряда и третьей шине управления соответственно, отличающийся тем, что первые входы пятого и шестого элементов И подключены к четвертой и пятой шинам управления, вторые входы этих элементов соединены с числовыми шинами приема прямого и инверсного кодов соответственно, а выходы упомянутых элементов И подключены к входам третьего элемента ИЛИ, выход которого соединен с входом первого и четвертого элементов ИЛИ; второй вход четвертого элемента ИЛИ соединен с выходом седьмого элемента И, а третий вход связан с выходом первого элемента НЕ; первый вход пятого элемента ИЛИ соединен с нулевым входом триггера, его второй вход связан со вторым входом четвертого элемента ИЛИ, а третий вход связан с шиной переноса из младшего разряда и входом четвертого элемента И; выходы четвертого и пятого логических элементов ИЛИ соединены с первым и третьим входами седьмого элемента И, второй вход этого элемента связан с шестой шиной управления, а его выход является шиной переноса в старший разряд, кроме того, введен восьмой элемент И, первый вход которого соединен с "единичным" выходом триггера старшего разряда, второй вход подключен к выходу второго элемента НЕ, а его третий вход связан с седьмой шиной управления, выход упомянутого элемента И подключен к четвертому входу второго элемента ИЛИ; к третьему входу первого элемента ИЛИ подключена восьмая шина управления.

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| ЦИФРОВОЙ СУММАТОР | 1994 |

|

RU2099776C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| US 5691931 A, 25.11.1995 | |||

| 1972 |

|

SU416869A1 | |

Авторы

Даты

2005-09-27—Публикация

2003-12-29—Подача