Область техники

Настоящее изобретение относится к устройству обработки данных и способу обработки данных и, например, в частности, относится к устройству обработки данных и способу обработки данных, который может обеспечить LDPC-код, превосходный по характеристикам частоты появления ошибок.

Уровень техники

LDPC (код с низкой плотностью проверок на четность) код имеет значительные возможности коррекции ошибок, и в последнее время широко применяется в системе передачи, которая включает в себя спутниковое цифровое вещание, такое как DVB (Цифровое телевизионное вещание)-S.2 используемое в Европе (например, см. непатентный документ 1). Кроме того, был протестирован LDPC-код при использовании наземного цифрового вещания следующего поколения, такого как DVB-T.2.

Из недавнего исследования, известно, что производительность вблизи предела Шеннона получают из LDPC-кода, когда длина кода увеличивается, подобно турбо коду. В связи с тем, что LDPC-код имеет свойство, которое заключается в том, что кратчайшее расстояние пропорционально длине кода, то LDPC-код имеет отличные характеристики вероятности искажения блока, будучи старшим, и так называемый, наблюдаемый феномен минимального уровня ошибок при декодировании турбо кода, будучи редко генерируемым, как их характеристики.

Далее будет конкретно описан LDPC-код. LDPC-код является линейным кодом и отсутствует необходимость для LDPC-кода быть двоичным кодом. Тем не менее, в этом случае предполагается, что LDPC-код является двоичным кодом.

Максимальная характеристика LDPC-кода представляет собой разряженную матрицу контроля четности, определяющая LDPC-код. В этом случае, разреженная матрица является матрицей, в которой количество «1» элементов матрицы очень мало (матрица, в которой большинство элементов равны 0).

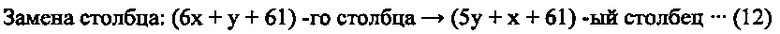

Фиг. 1 иллюстрирует пример матрицы H контроля четности LDPC-кода.

В матрице H контроля четности на фиг. 1, вес каждого столбца (вес столбца) (число "1") становится равным "3" и вес каждой строки (вес строки) становится равным "6".

При кодировании с использованием LDPC-кода (LDPC-кодирование), например, генераторная матрица G генерируется на основании матрицы H контроля четности и генераторная матрица G умножается на двоичные биты информации, так что генерируется кодовое слово (LDPC-код).

В частности, устройство кодирования, которое выполняет LDPC-кодирование, сначала вычисляет генераторную матрицу G, в которой реализуется выражение GHT=0, между транспонированной матрицей HT матрицы Η проверки четности и генераторной матрицей G. В этом случае, когда генераторная матрица G является К×N матрицей, устройство кодирования умножает генераторную матрицу G на битовую строку (вектор u) информационных битов, включающие в себя К биты, и генерирует кодовое слово с (=uG), включающее в себя N битов. Кодовое слово (LDPC-код), которое генерируется устройством кодирования, принимается на приемной стороне посредством заранее определенного коммуникационного тракта.

LDPC-код может быть декодирован с помощью алгоритма называемого вероятностным декодированием, предложенным Галлагером, то есть алгоритм передачи сообщений, используя распространение степени уверенности в так называемом графе Таннера, включающей в себя переменный узел (также называемый как узел сообщений) и узел проверки. Здесь и далее, переменный узел и узел проверки соответственно называются просто узлами.

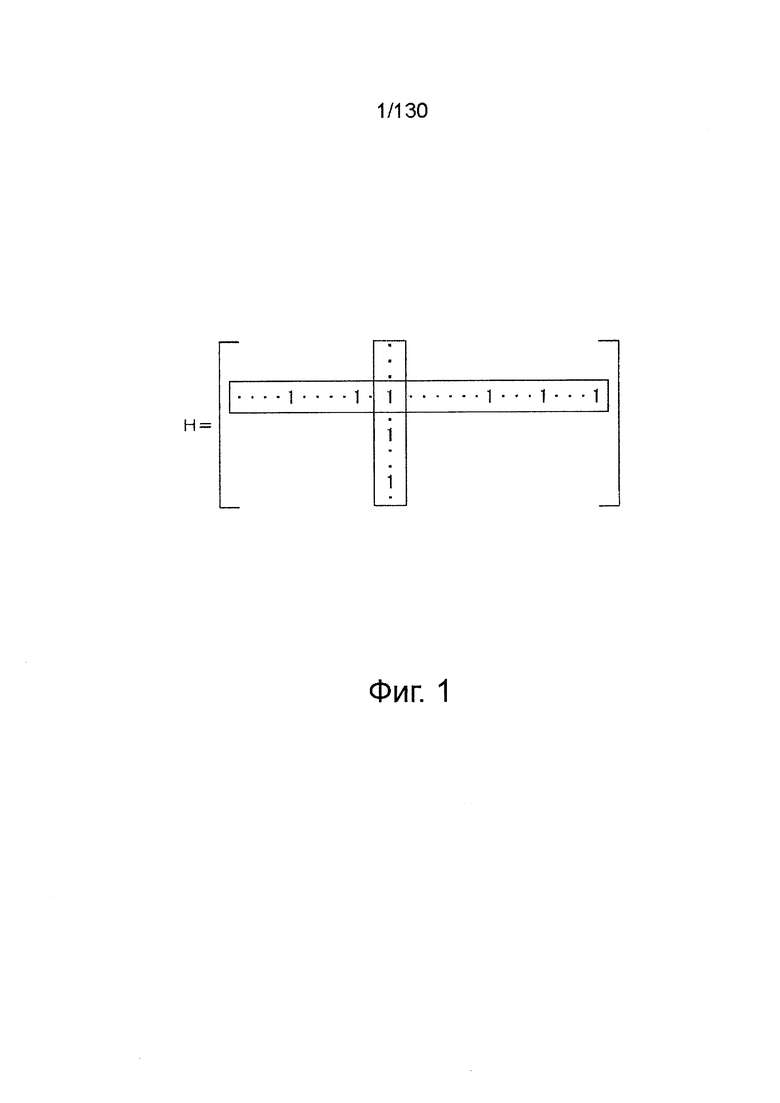

Фиг. 2 иллюстрирует последовательность декодирования LDPC-кода.

Далее реальное значение (LLR приема), которое получается путем представления вероятности "0" значения i битового кода LDPC-кода (одно кодовое слово), принятое на приемной стороне посредством логарифмического отношения правдоподобия, соответственно упоминается как приемное значение u0i. Кроме того, сообщение, вырабатываемое узлом проверки, упоминается как uj, и сообщение, вырабатываемое переменным узлом, называют vi.

Во-первых, при декодировании LDPC-кода, как показано на фиг. 2, на этапе S11 принимается LDPC-код, сообщение uj (сообщение узла проверки) инициализируется на "0", и переменная k, принимая целое число в качестве счетчика повторений обработки, инициализируется на "0", и процесс обработки переходит к этапу S12. На этапе S12 сообщение vi (сообщение переменного узла) рассчитывается посредством выполнения операции (операция переменного узла), представленное выражением (1), на основании приемного значения u0i, полученного путем приема LDPC-кода, и сообщение uj рассчитывается посредством выполнения операции (операция узла проверки), представленное выражением (2), на основании сообщения vi.

[Математика. 1]

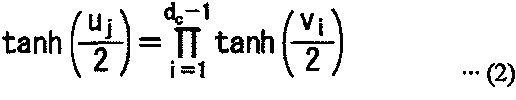

[Математика. 2]

Здесь dv и dc в выражении (1) и выражении (2) соответственно являются параметрами, которые могут быть выбраны произвольно, и иллюстрирует число "1" в продольном направлении (колонка) и в поперечном направлении (строка) матрицы Н контроля четности. Например, в случае LDPC-кода ((3, 6) LDPC-кода) по отношению к матрице Н контроля четности с весом 3 столбца и весом 6 строк, как показано на фиг. 1, устанавливаются dv=3 и dc=6.

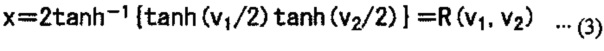

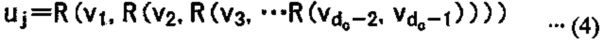

В операции переменного узла выражения (1) и операции узла проверки выражения (2), так как сообщение поступает на вход от границы (линия соединения переменного узла и узла проверки) для вывода сообщения, не является целевой операцией, рабочий диапазон становится равным от 1 до dv - 1 или от 1 до dc - 1. Операция узла проверки выражения (2) выполняется фактически посредством ранее составленной таблицы функции R (v1, v2), представленной выражением (3), определяется одним выходом по отношению к двум входам v1 и v2, и используя таблицу последовательно (рекурсивно), как представлено выражением (4).

[Математика. 3]

[Математика. 4]

На этапе S12 переменная k получает приращение на "1" и процесс обработки переходит на этап S13. На этапе S13 определяется, превышает ли переменная k на количество раз С заданное количество повторений декодирования. Когда определено на этапе S13, что переменная k не превышает С, то процесс обработки возвращается на этап S12, и тот же процесс обработки повторяется.

Когда определено на этапе S13, что переменная k превышает С, то процесс обработки переходит к этапу S14, сообщение vi, которое соответствует результату декодирования, который представляет собой окончательное выходное значение, рассчитывается посредством выполнения операции, представленная выражением (5), и выводится, и на этом процесс декодирования LDPC-кода заканчивается.

[Математика. 5]

В этом случае операция по выражению (5) выполняется с помощью сообщений uj из всех границ с переменным узлом, отличная от операции переменного узла выражения (1).

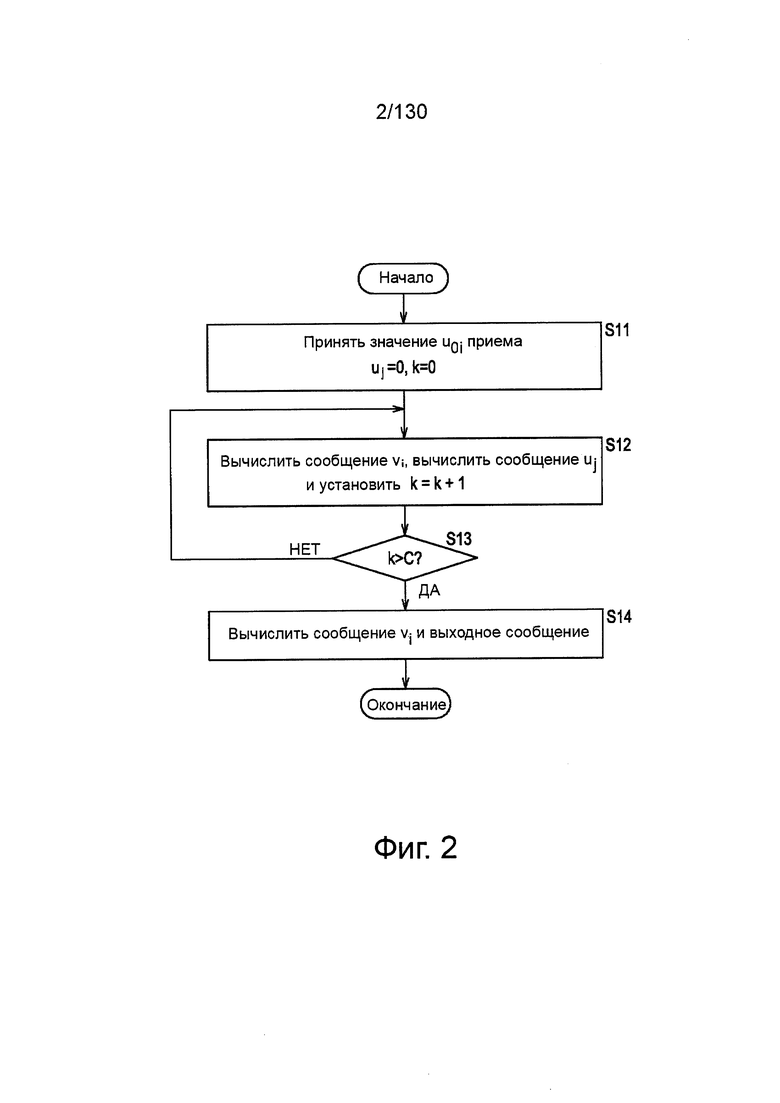

Фиг. 3 иллюстрирует пример матрицы Н контроля четности (3, 6) LDPC-кода (скорость 1/2 кодирования и кодовая длина 12).

В матрице Н контроля четности на фиг. 3, вес столба установлен на 3 и вес строки установлен на 6, аналогично показанной на фиг. 1.

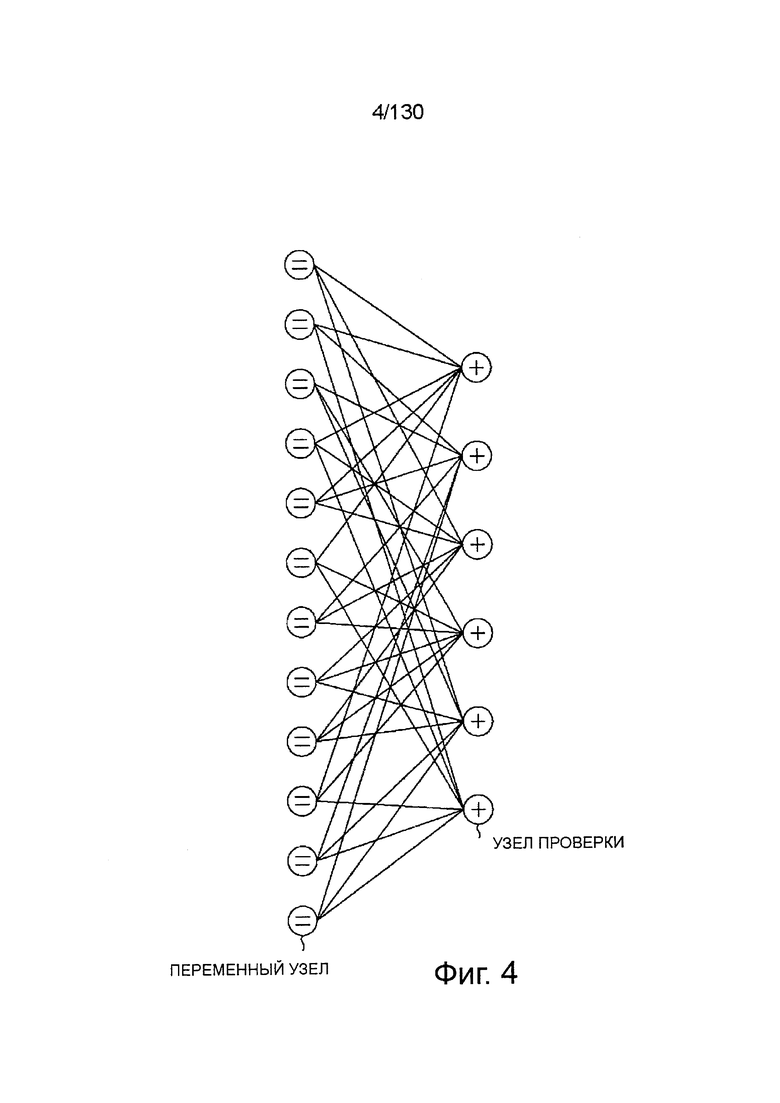

Фиг. 4 иллюстрирует граф Таннера матрицы Н контроля четности на фиг. 3.

На фиг. 4, узел проверка представлен "+" (плюс) и переменный узел представлен «=» (равно). Узел проверки и переменный узел соответствуют строке и столбцу матрицы Н контроля четности. Линия, которая соединяет узел проверки и переменный узел, является границей и соответствует "1" элементов матрицы контроля четности.

То есть, когда элемент j-й строки и i-го столбца матрицы контроля четности равен 1, на фиг. 4, то i-й переменный узел (узел "=") с верхней стороны и j-й узел проверки (узел "+") с верхней стороны, соединены гранью. Грань показывает, что битовый код, соответствующий переменному узлу, имеет условие ограничения, соответствующее узлу проверки.

В алгоритме сумма-произведение, который является способом декодирования LDPC-кода, операция переменного узел и узла проверки периодически выполняются.

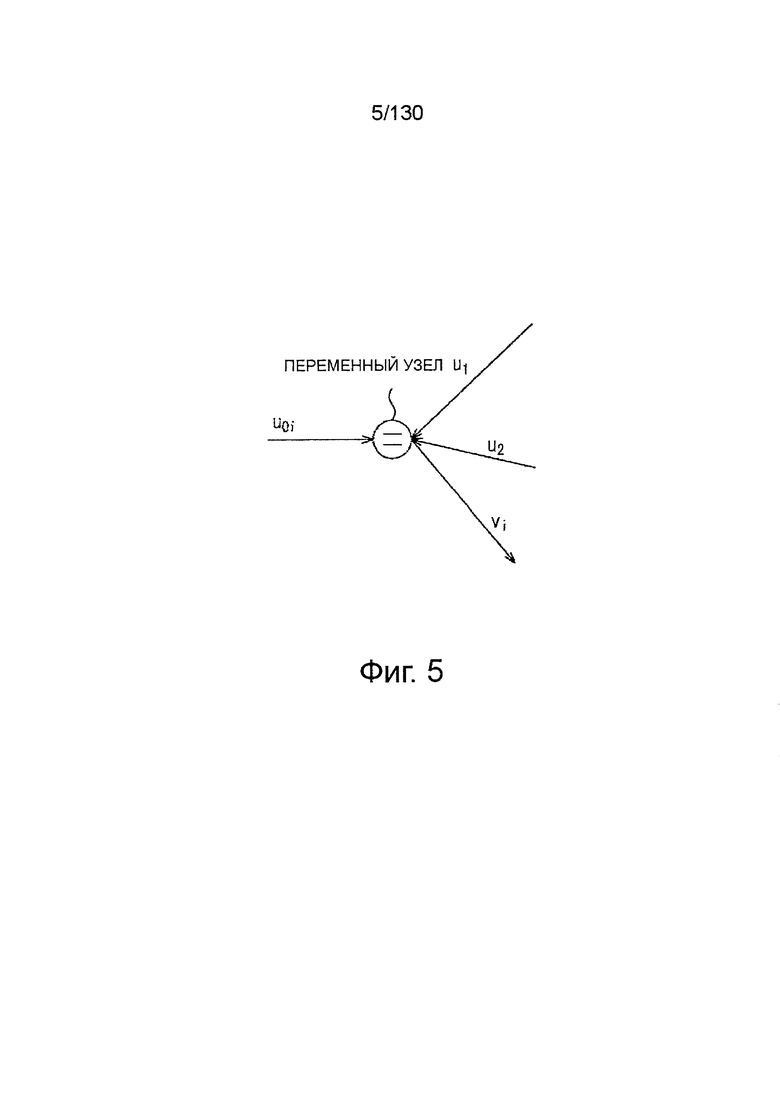

Фиг. 5 иллюстрирует операцию переменного узла, который выполняется с помощью переменного узла.

В переменном узле сообщение vi, которое соответствует грани для расчета, вычисляется посредством операции переменного узла в выражении (1), используя сообщения u1 и u2 из оставшихся граней, соединенных с переменным узлом, и приемное значение u0i. Сообщения, которые соответствуют другим граням, также рассчитываются тем же способом.

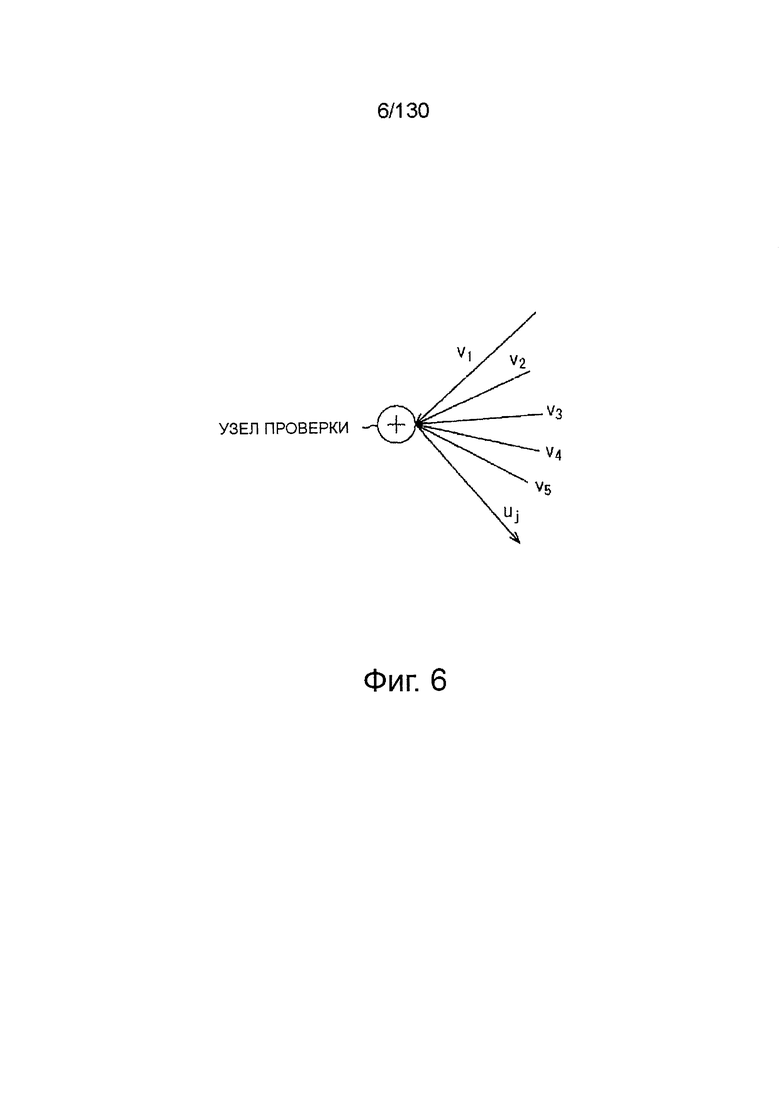

Фиг. 6 иллюстрирует операцию узла проверка, которая выполняется с помощью узла проверки.

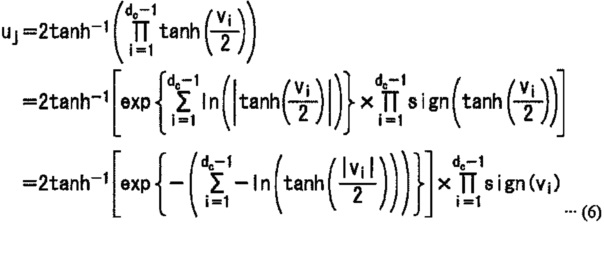

В этом случае, операция узла проверки выражения (2) может быть переписана посредством выражения (6), используя соотношение выражения а×b=exp{ln(|а|)+ln(|b|)}×sign(а)×sign(b). Тем не менее, sign(х) является 1 в случае x≥0 и является -1 в случае x<0.

[Математика. 6]

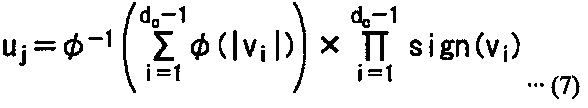

При x≥0, если функция φ(х) определяется как выражение φ(х)=ln(tanh(x/2)), то выполняется выражение φ-1(x)=2tanh-1 (е-x). По этой причине, выражение (6) может быть изменено на выражение (7).

[Математика. 7]

В узле проверки, операция узла проверки выражения (2) выполняется в соответствии с выражением (7).

То есть, в узле проверки, как показано на фиг. 6, сообщение uj, которое соответствует границе для расчета, вычисляется с помощью операции узла проверки выражения (7), используя сообщения v1, v2, v3, v4 и v5 из остальных граней, соединенных с узлом проверки. Сообщения, которые соответствуют другим граням, также рассчитываются тем же способом.

Функция φ(x) выражения (7) может быть представлена в виде φ(x)=ln((ex+1)/(ex-1)) и φ(x)=φ-1(x) выполняется при x>0. Когда функции φ(x) и φ-1(x) установлены на аппаратном оборудовании, функции φ(x) и φ-1(x) могут быть установлены с помощью LUT (просмотровой таблицы). Тем не менее, обе функции φ(x) и φ-1(x) становятся теми же LUT.

Перечень ссылок

Непатентный документ

Непатентный документ 1: DVB-S.2: ETSI EN 302307 V1.2.1 (2009-08)

Раскрытие изобретения

Технические задачи, решаемые с помощью изобретения

DVB стандарт, такой как DVB-S.2, DVB-T.2 и DVB-C.2, которые используют LDPC-код, рассматривает LDPC-код в качестве символа (отображает в символической форме) ортогональной модуляции (цифровой модуляции), такой как QPSK (квадратурная фазовая манипуляция), и символ отображается на сигнальной точке и передается.

Кстати, в последние годы возникла потребность в эффективной передаче, например, данных с большой емкостью, таких как, так называемое 4k изображение, с разрешением по ширине и длине 3840×2160 пикселей изображения четырехкратной полной высокой четкости и 3D (размерность) изображения.

Тем не менее, если приоритет отдан эффективной передаче данных, то частота появления ошибок увеличивается.

С другой стороны, есть случай, когда необходимо осуществить передачу данных с. низким значением частоты появления ошибок, даже если эффективность передачи данных в некоторой степени снижается.

Предполагается, что передача данных с различными значениями эффективности будет востребована в будущем, но, в соответствии с LDPC-кодом, например, путем подготовки множества LDPC-кодов различных скоростей кодирования, можно выполнить передачу данных с различными значениями эффективности.

Таким образом, для передачи данных, желательно, адаптировать скорости кодирования LDPC-кодов, для которых легко могут быть установлены несколько увеличенных значений скоростей кодирования (например, число, равное или больше требуемой для передачи данных).

Дополнительно, даже в случае, когда используется LDPC-код любой скорости кодирования, желательно, чтобы величина сопротивления возникновению ошибки была высокой (сильной), то есть, величина частоты появления ошибок имела превосходное значение.

Настоящее изобретение сделано с учетом такой ситуации и может обеспечить LDPC-код с превосходным значением частоты появления ошибок.

Решения технической задачи

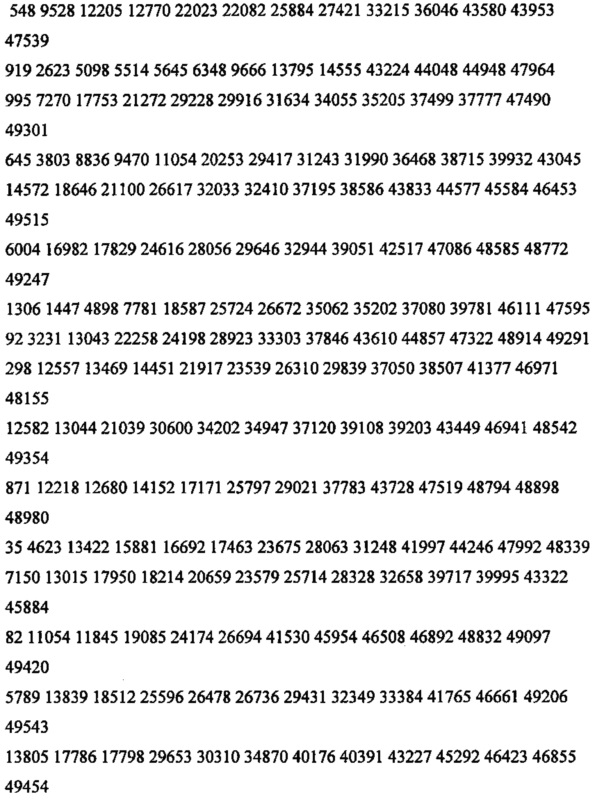

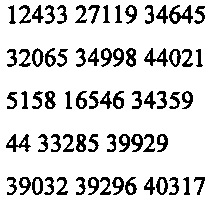

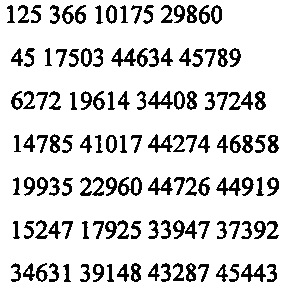

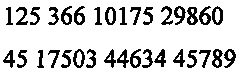

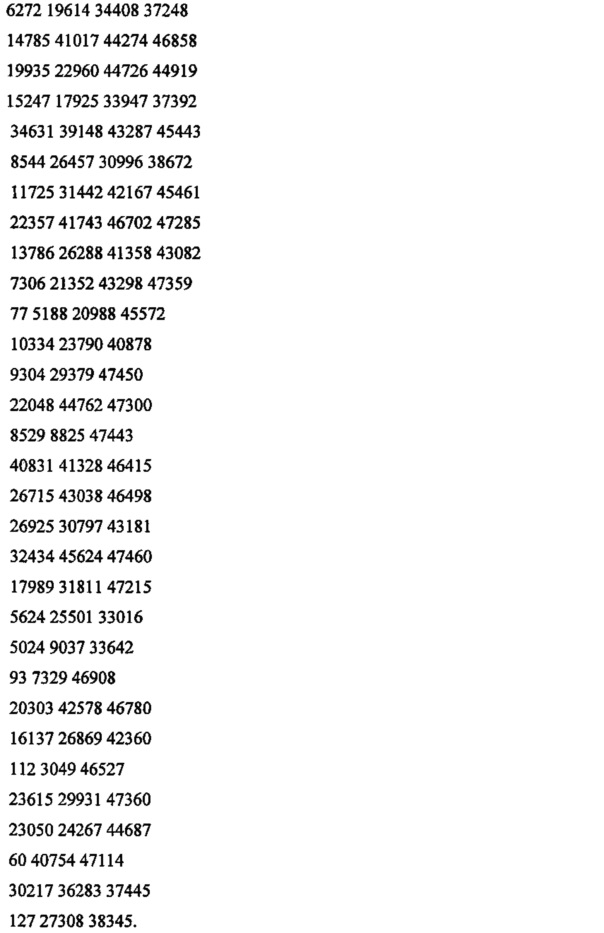

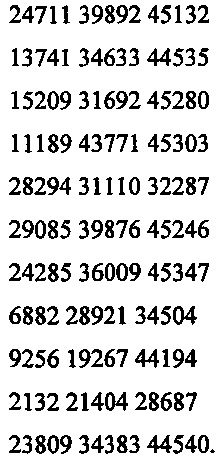

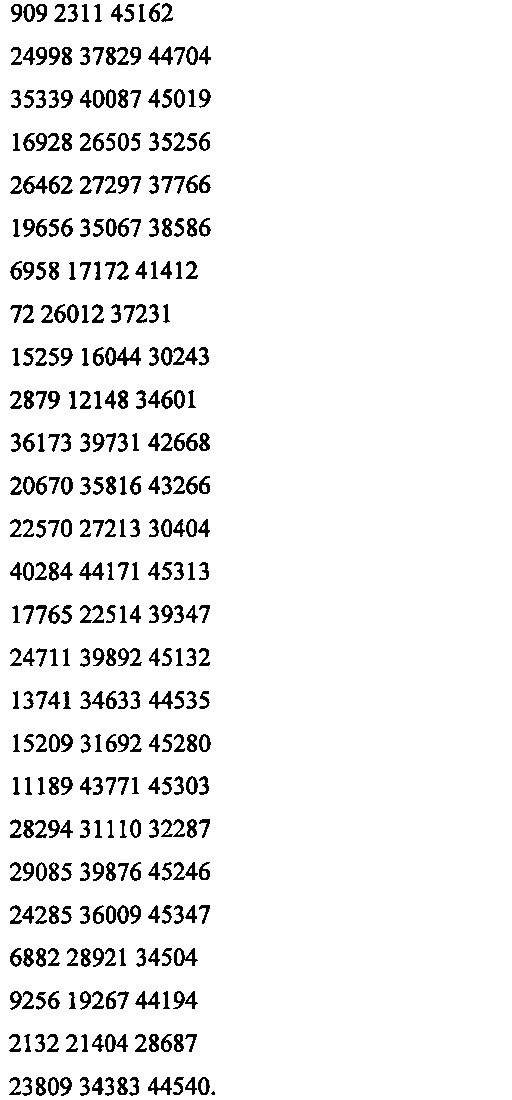

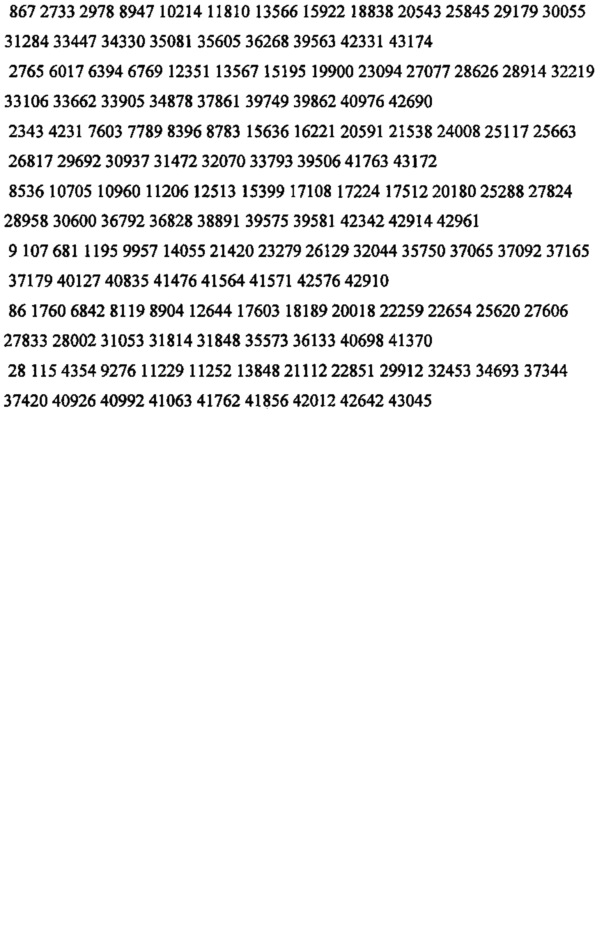

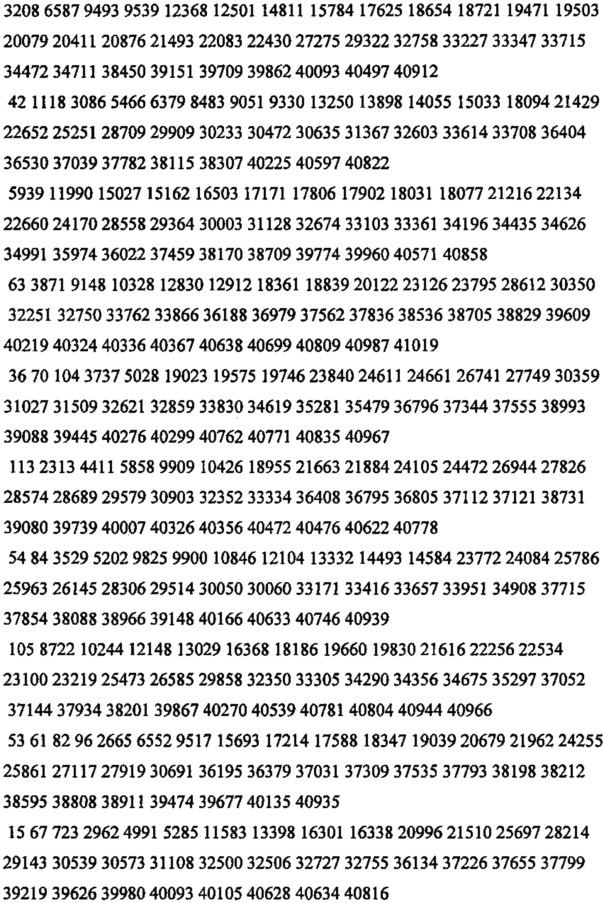

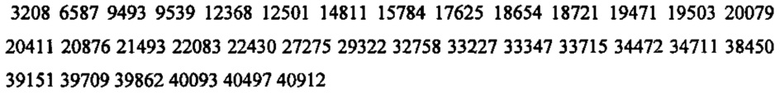

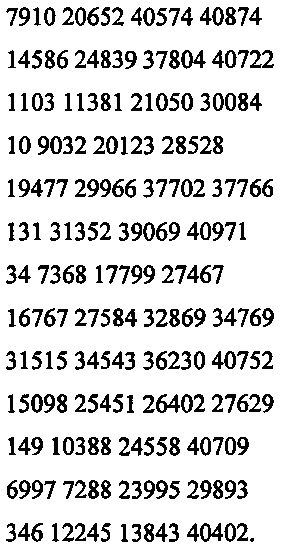

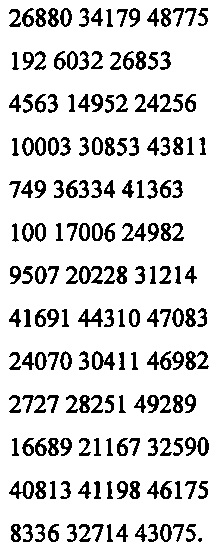

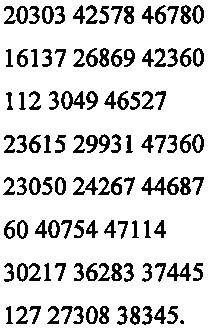

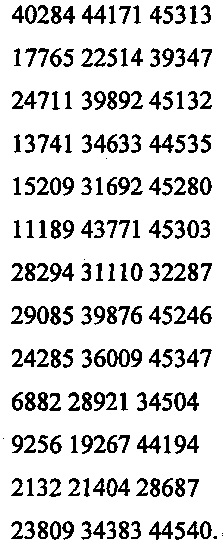

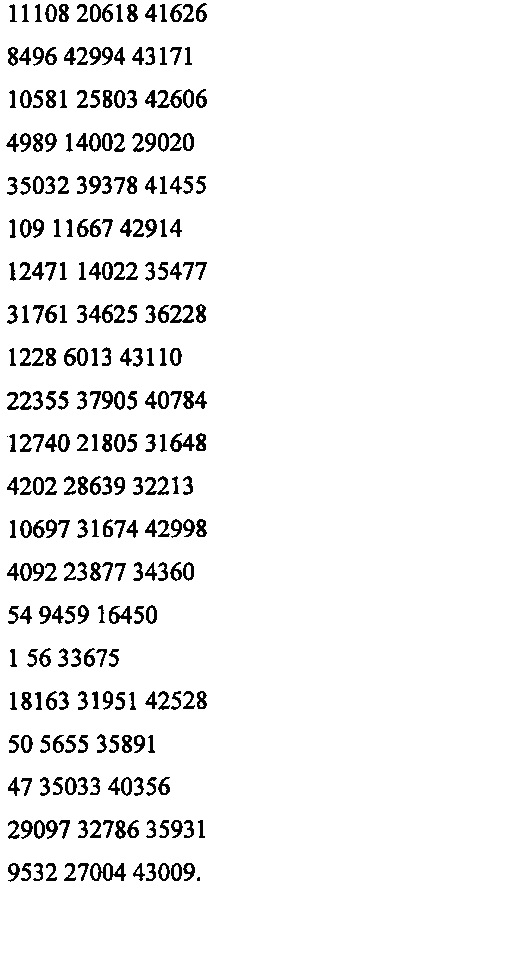

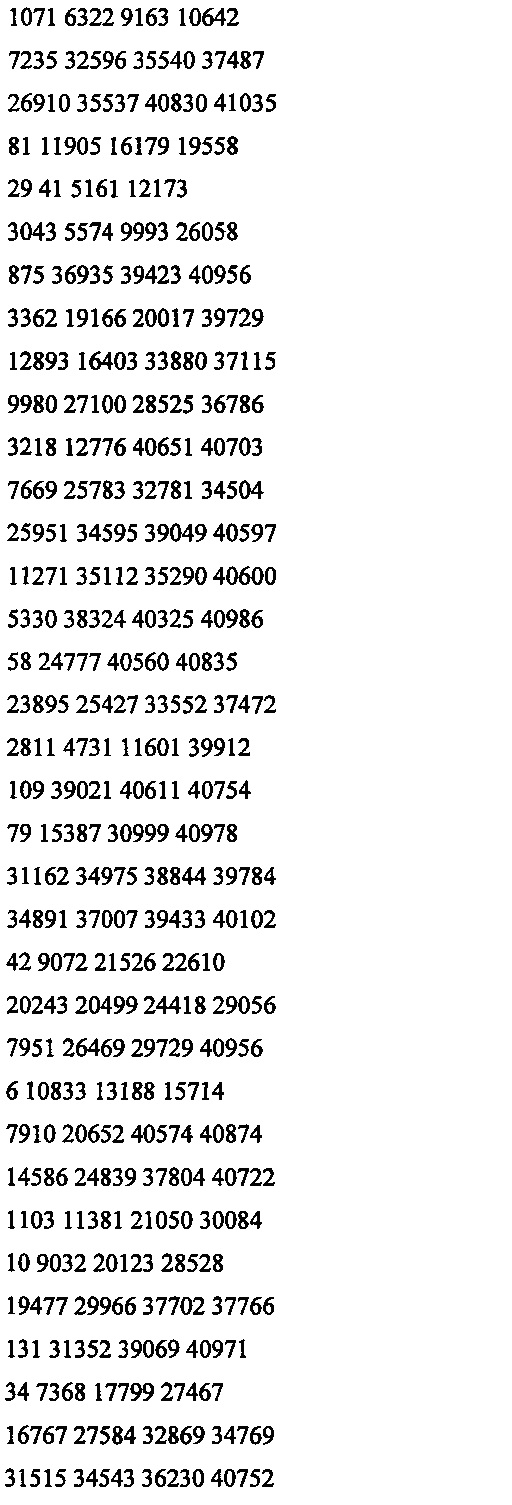

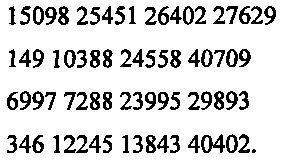

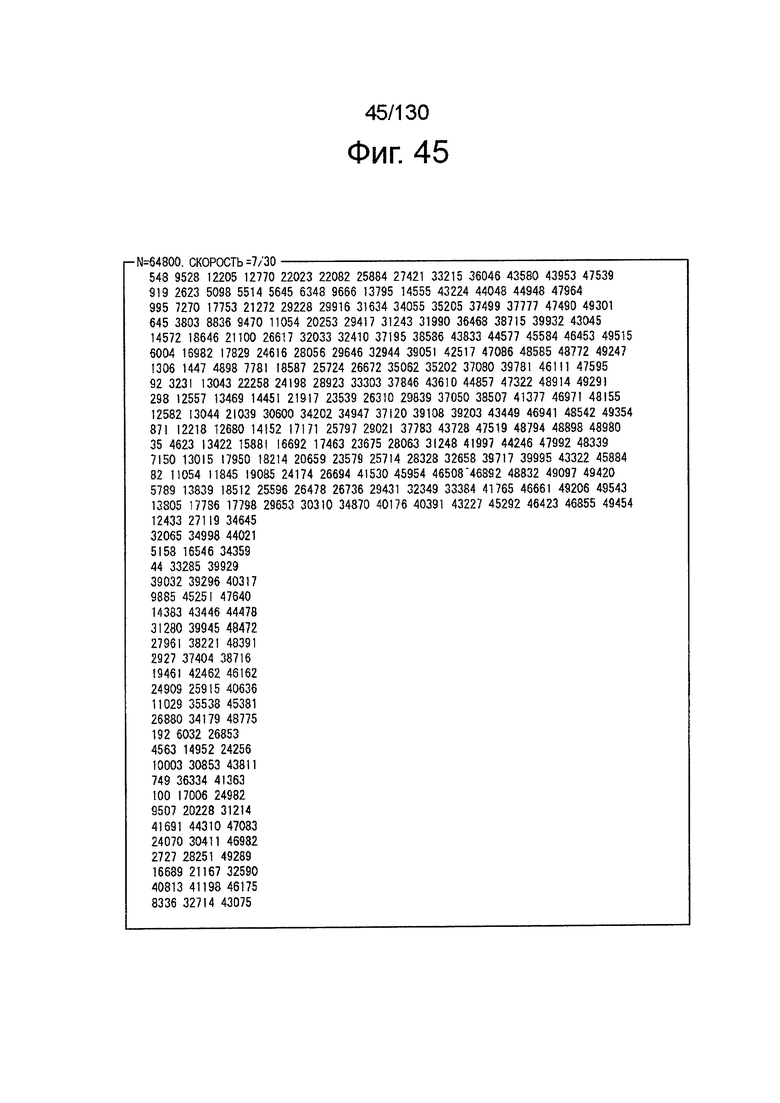

Первое устройство обработки или способ обработки данных в соответствии с настоящим изобретением включает в себя блок кодирования или этап кодирования для кодирования битов информации в LDPC-коде с кодовой длиной 64800 битов и скоростью кодирования 7/30, на основании матрицы контроля четности LDPC (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Второе устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 7/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

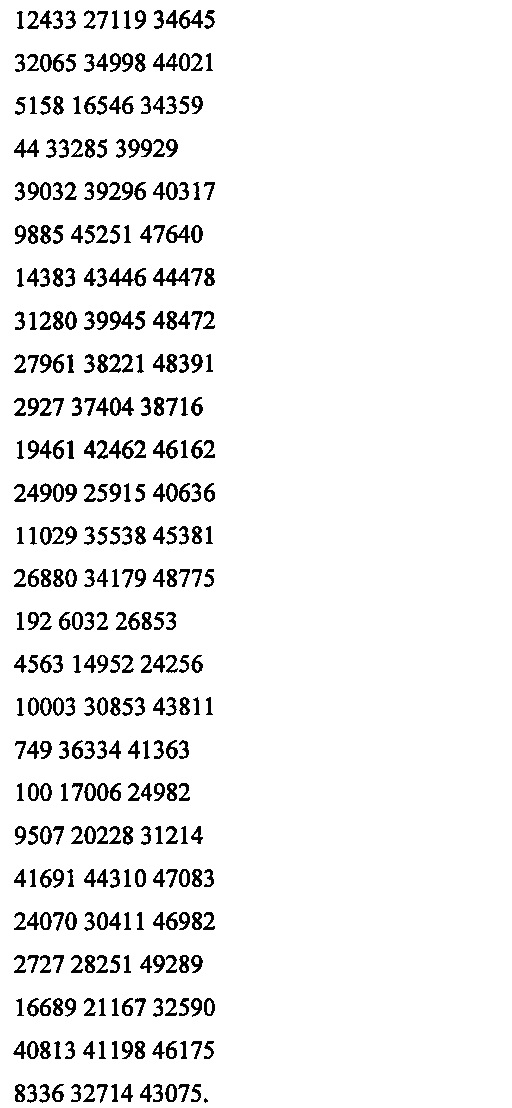

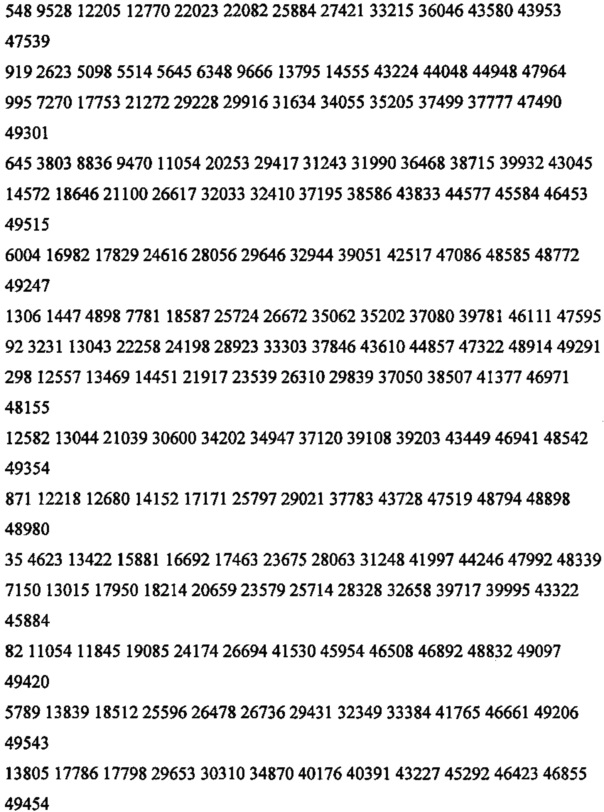

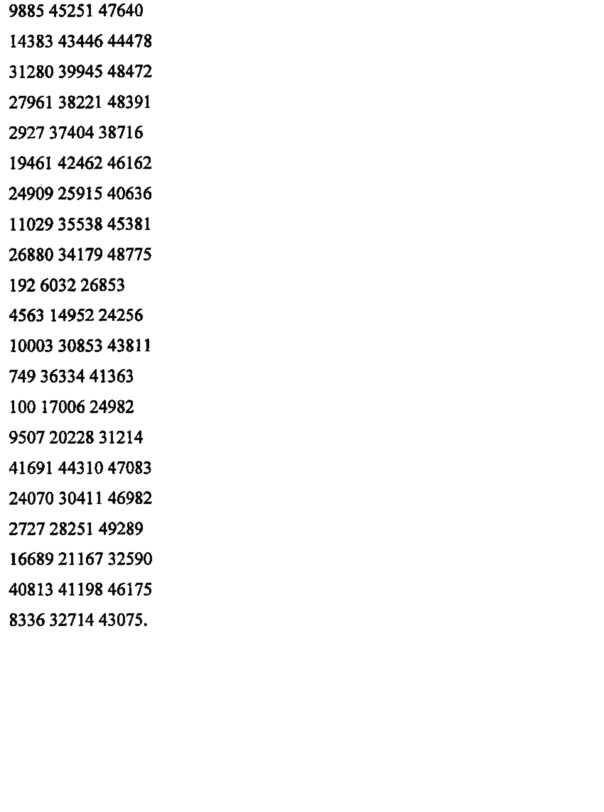

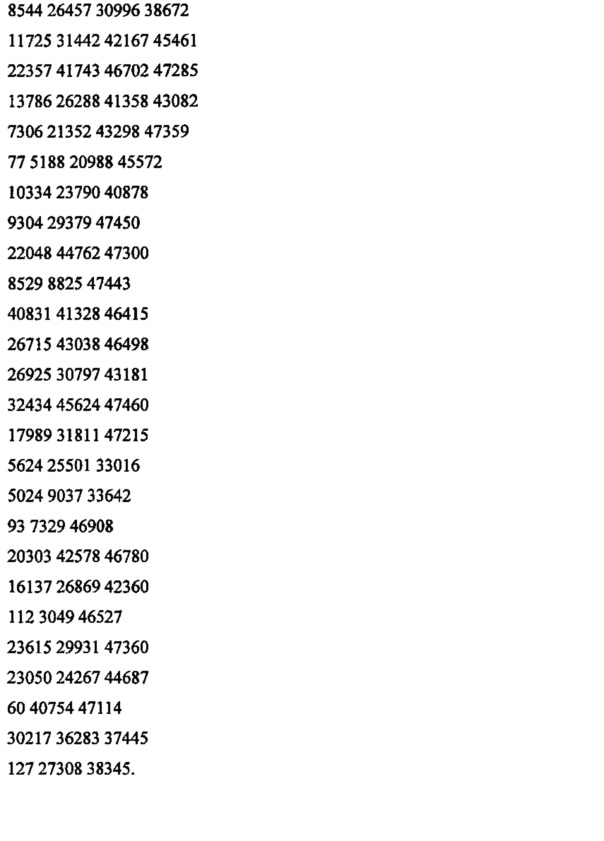

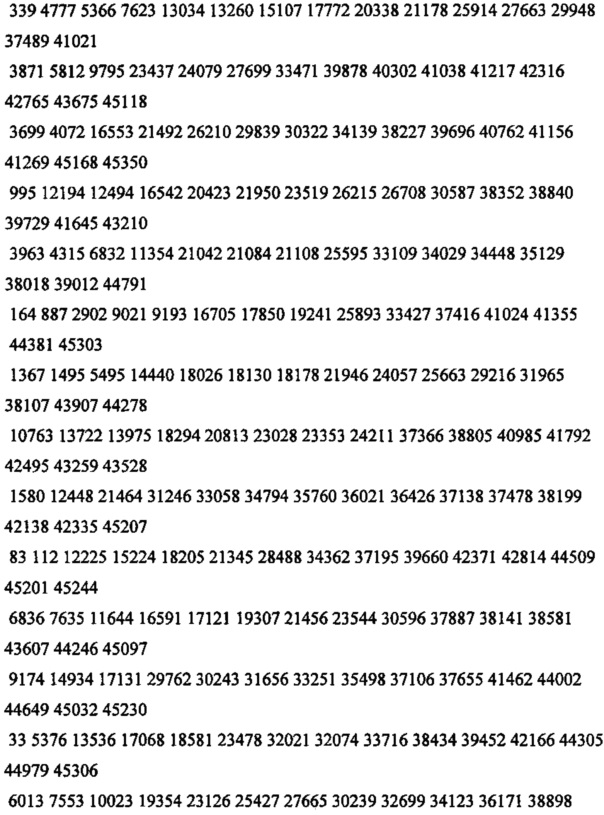

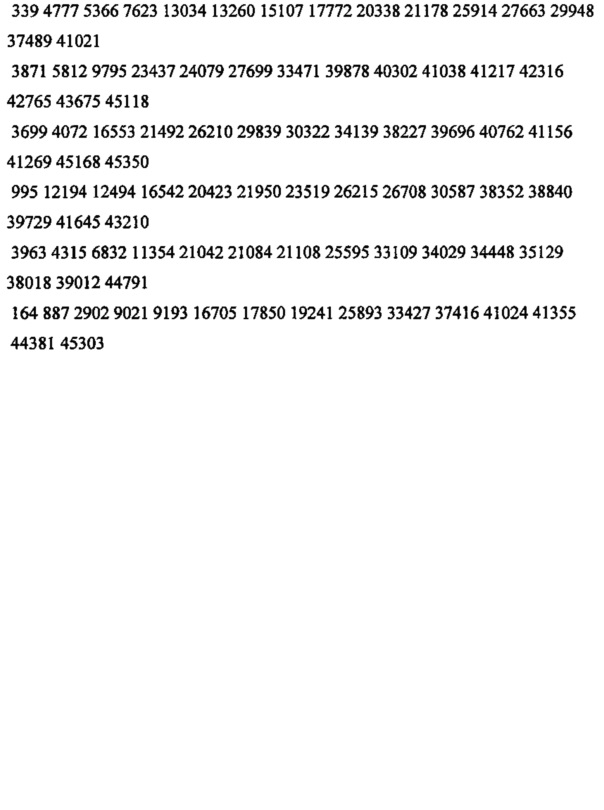

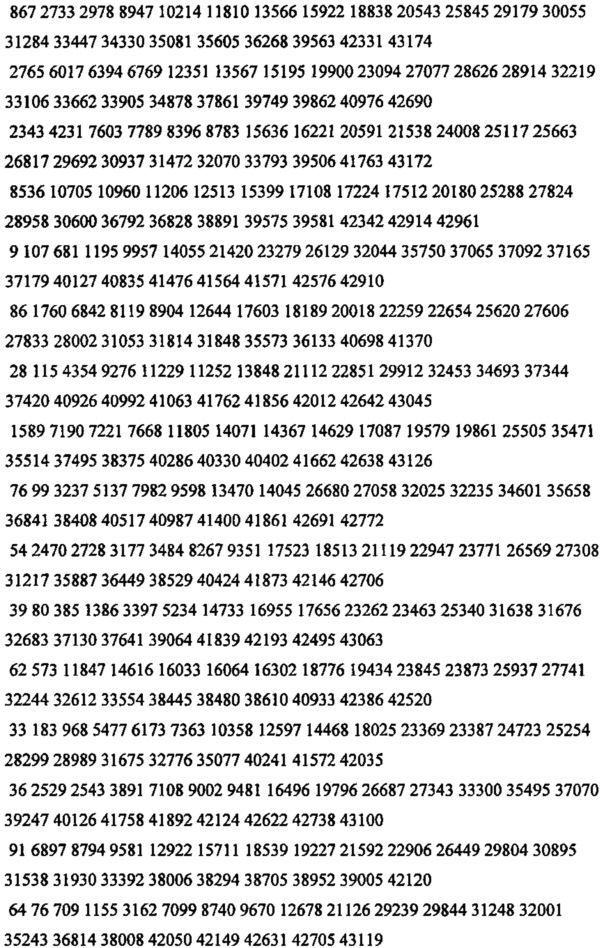

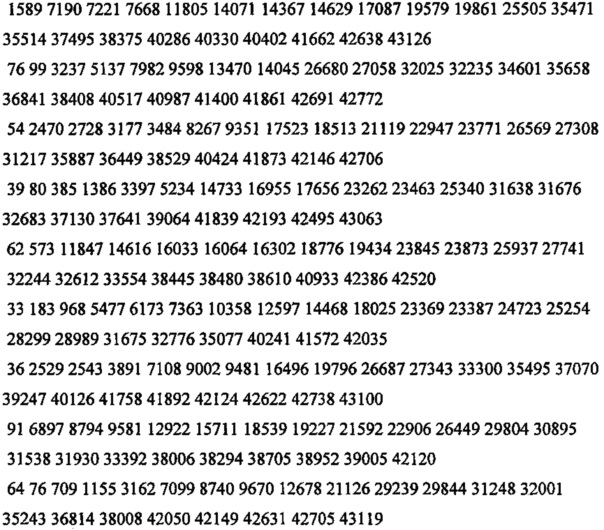

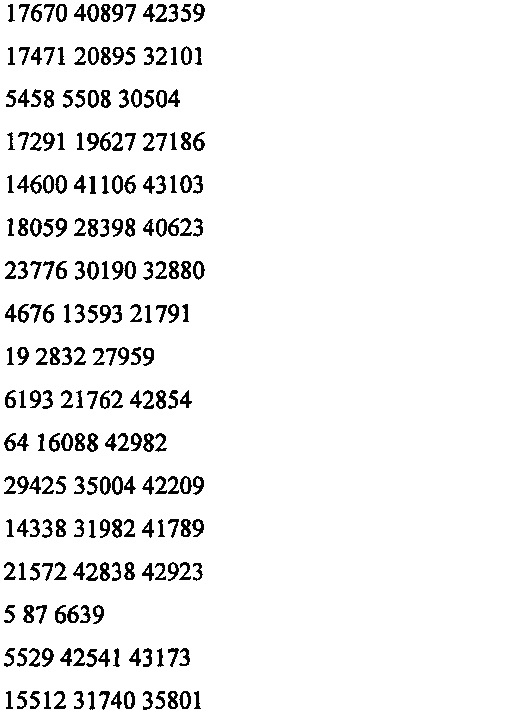

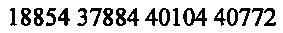

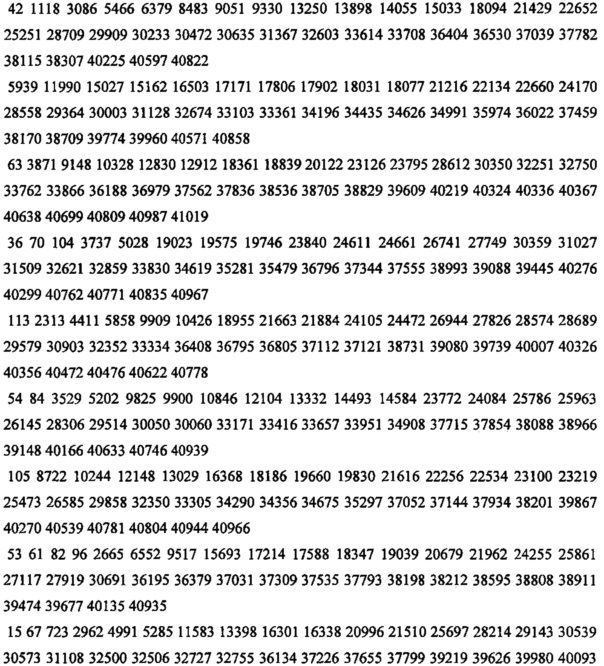

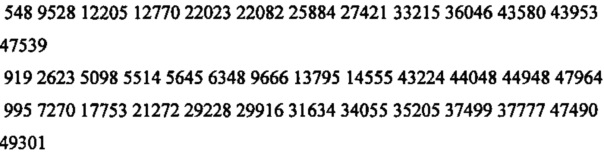

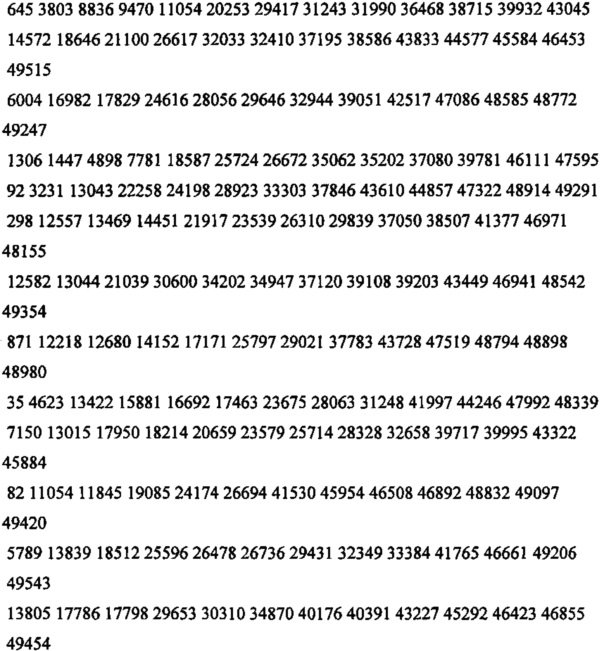

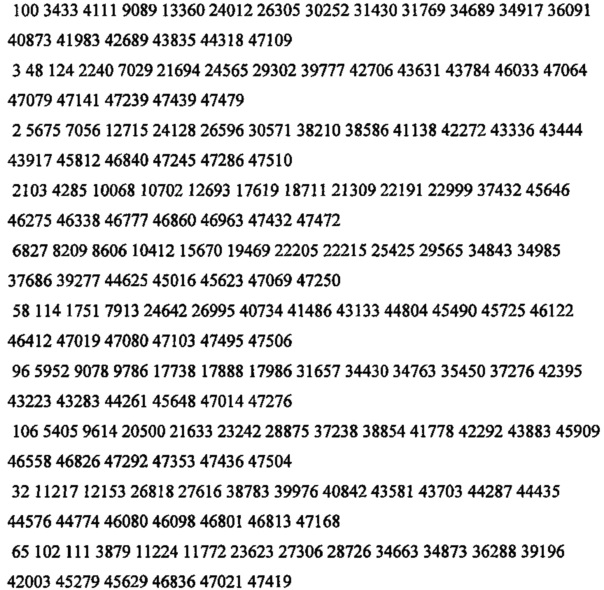

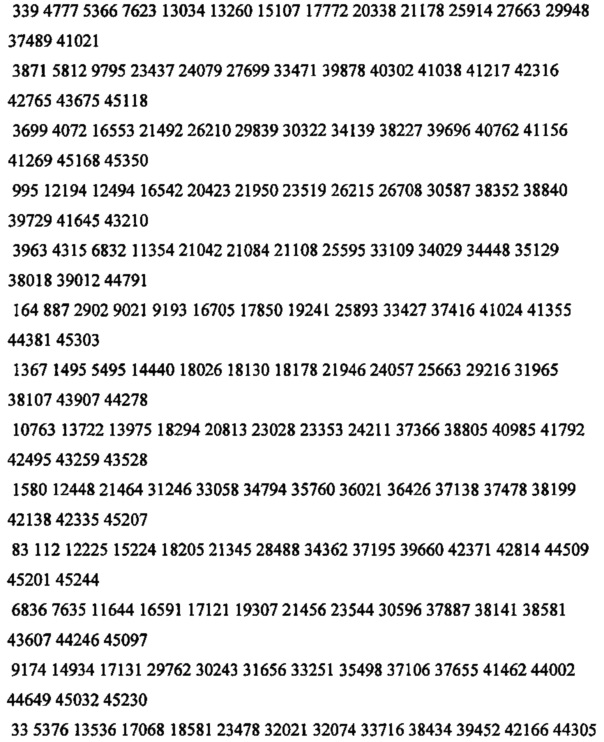

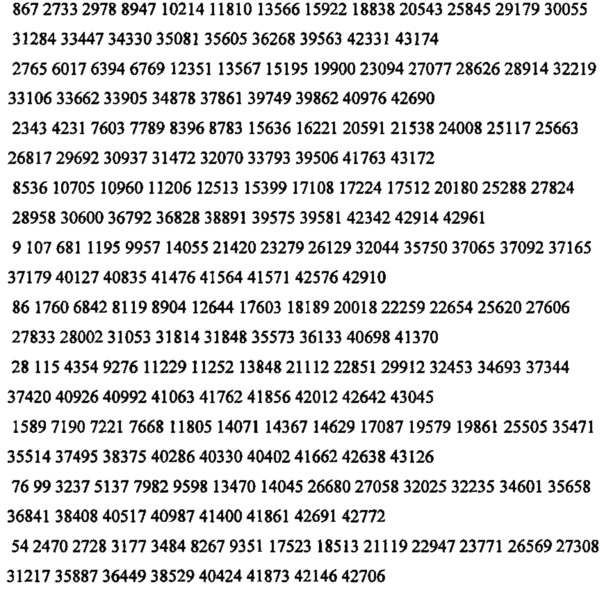

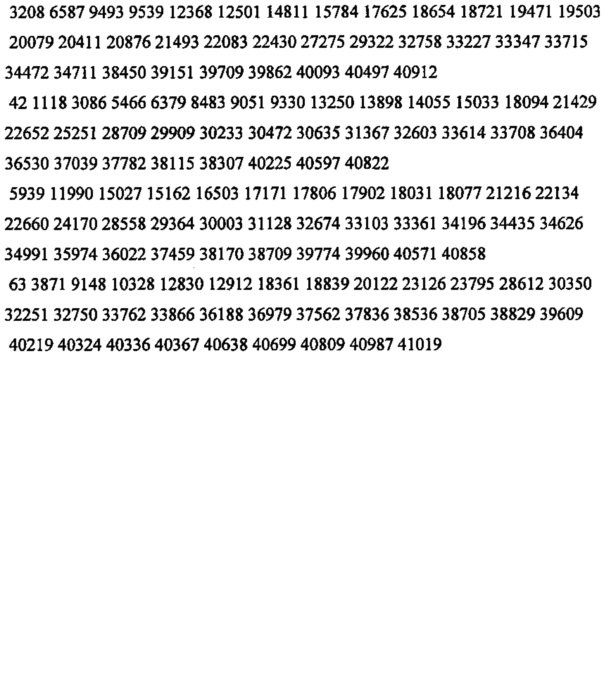

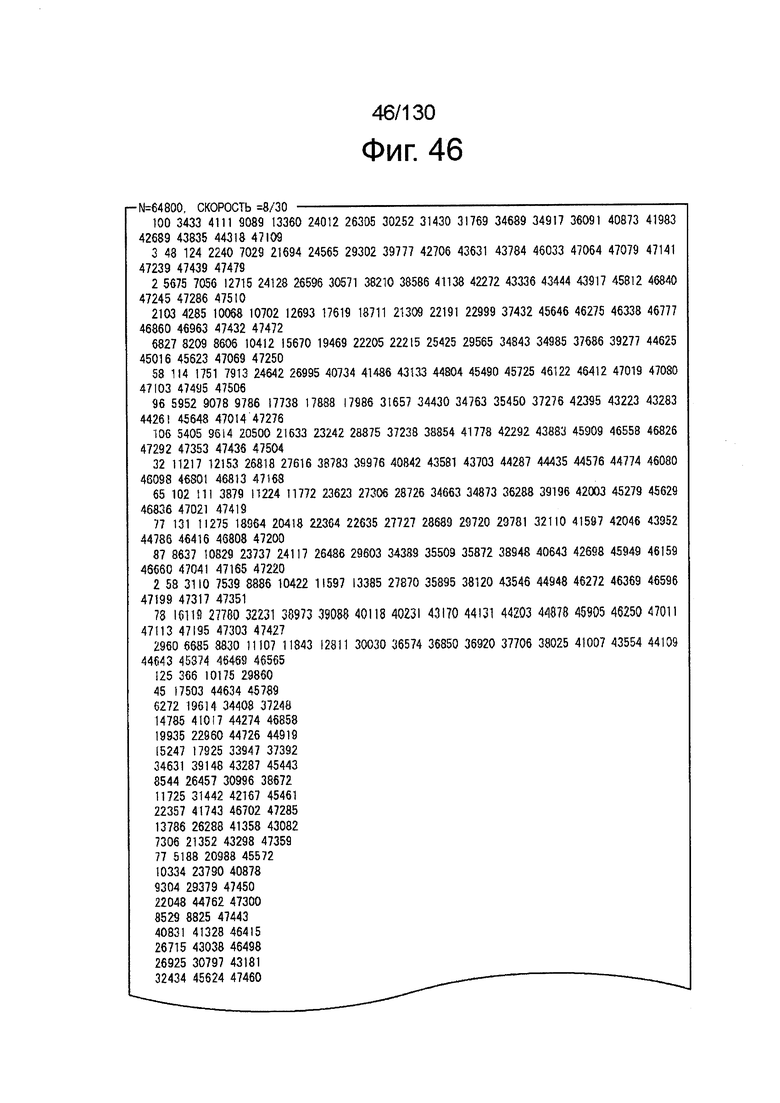

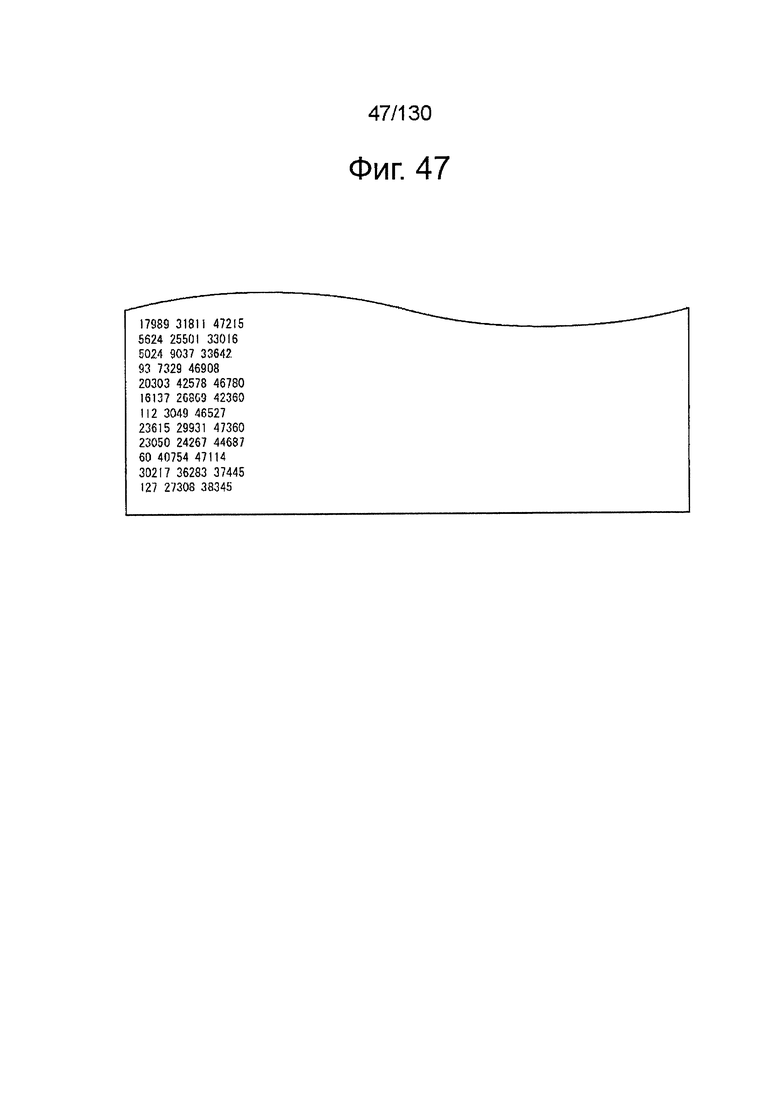

Третье устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок кодирования или этап кодирования для кодирования бита информации LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 8/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Четвертое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 8/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

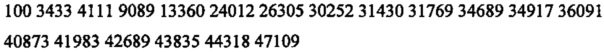

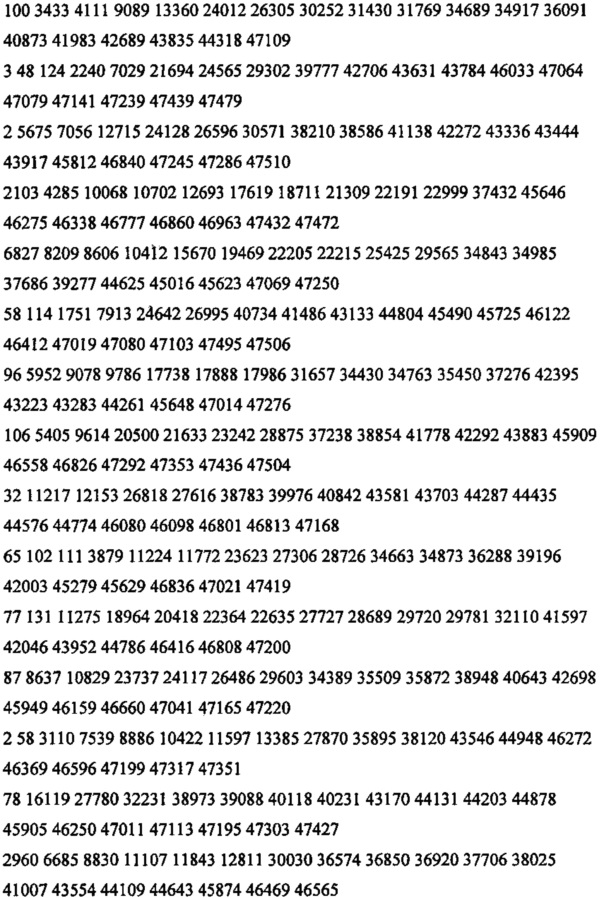

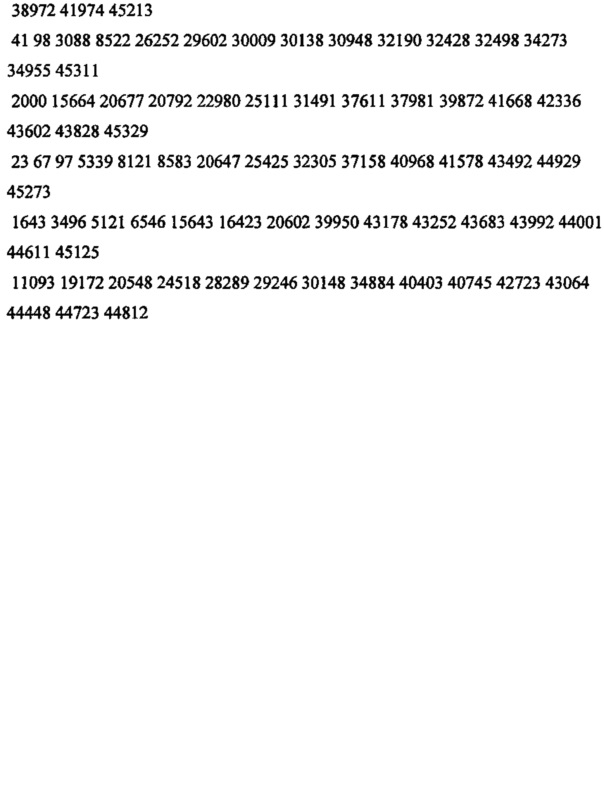

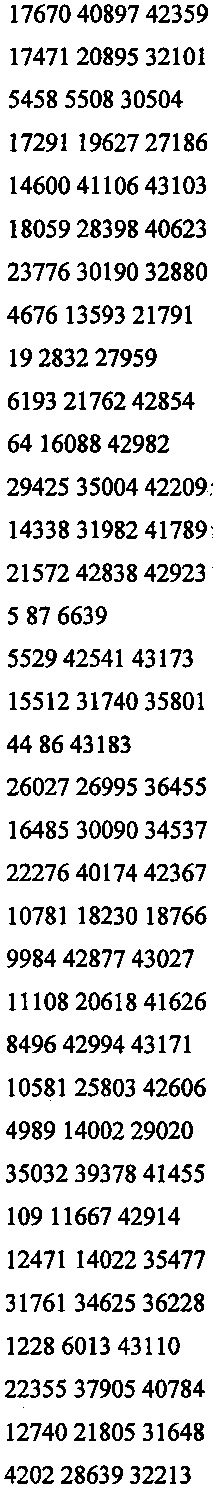

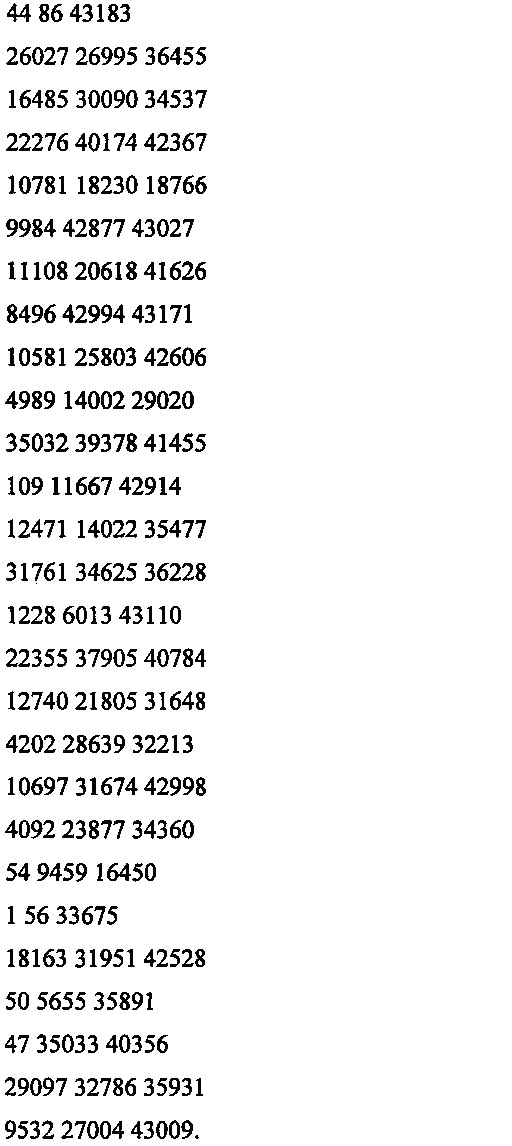

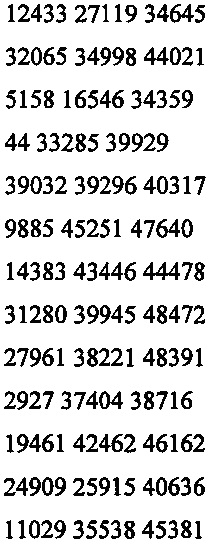

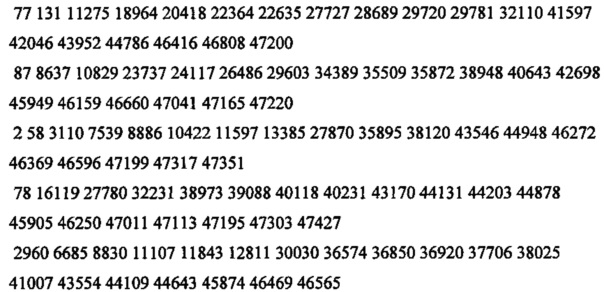

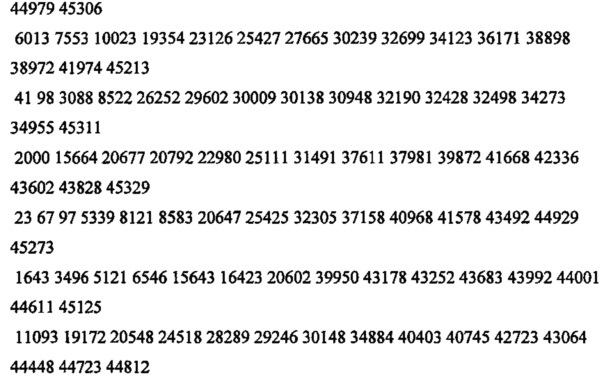

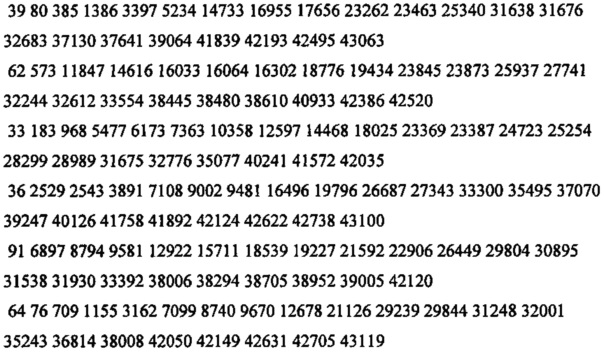

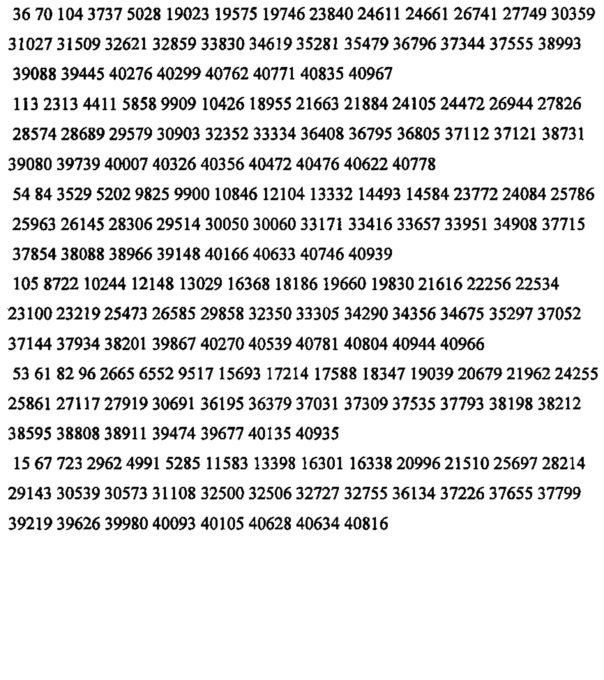

Пятое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок кодирования или этап кодирования для кодирования бита информации LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 9/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Шестое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 9/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

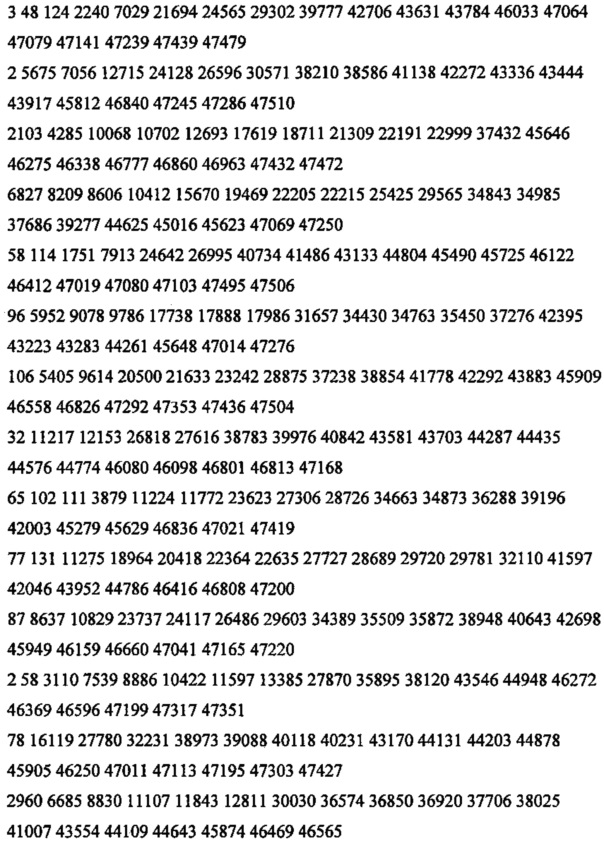

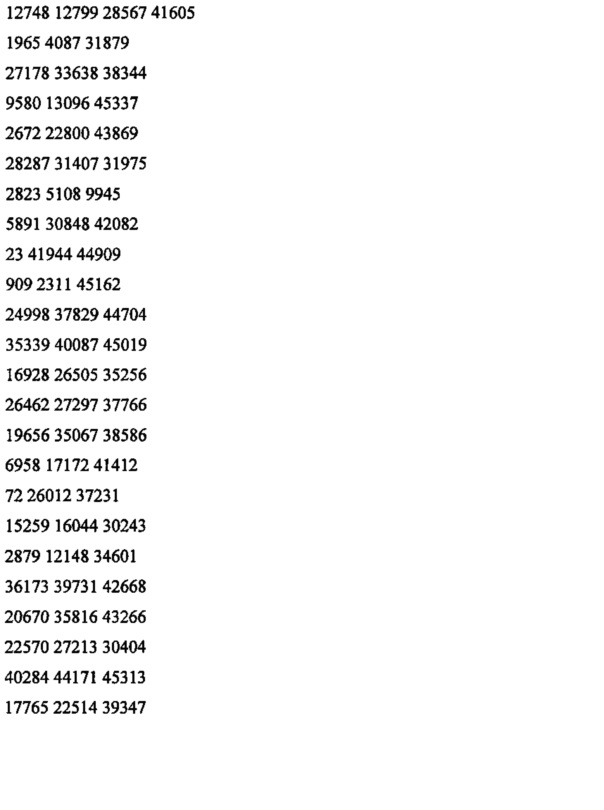

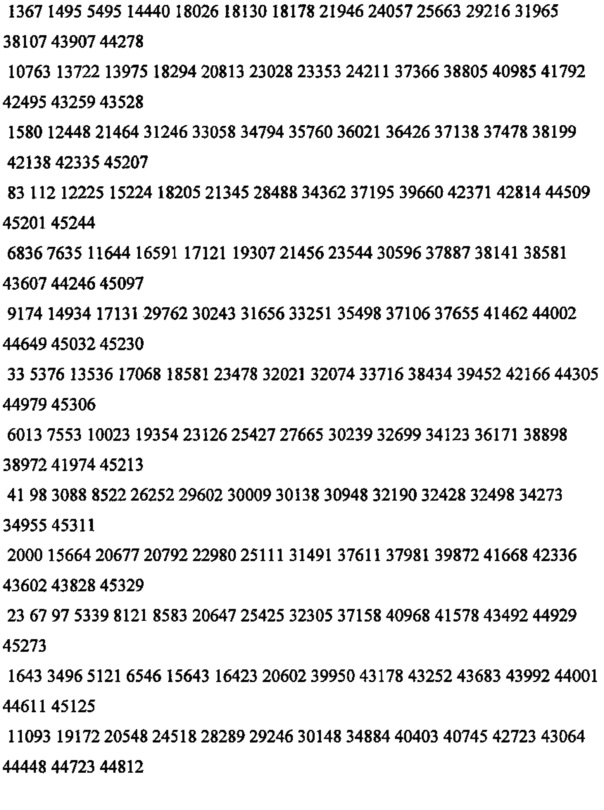

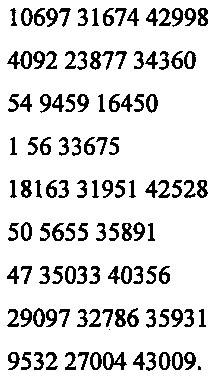

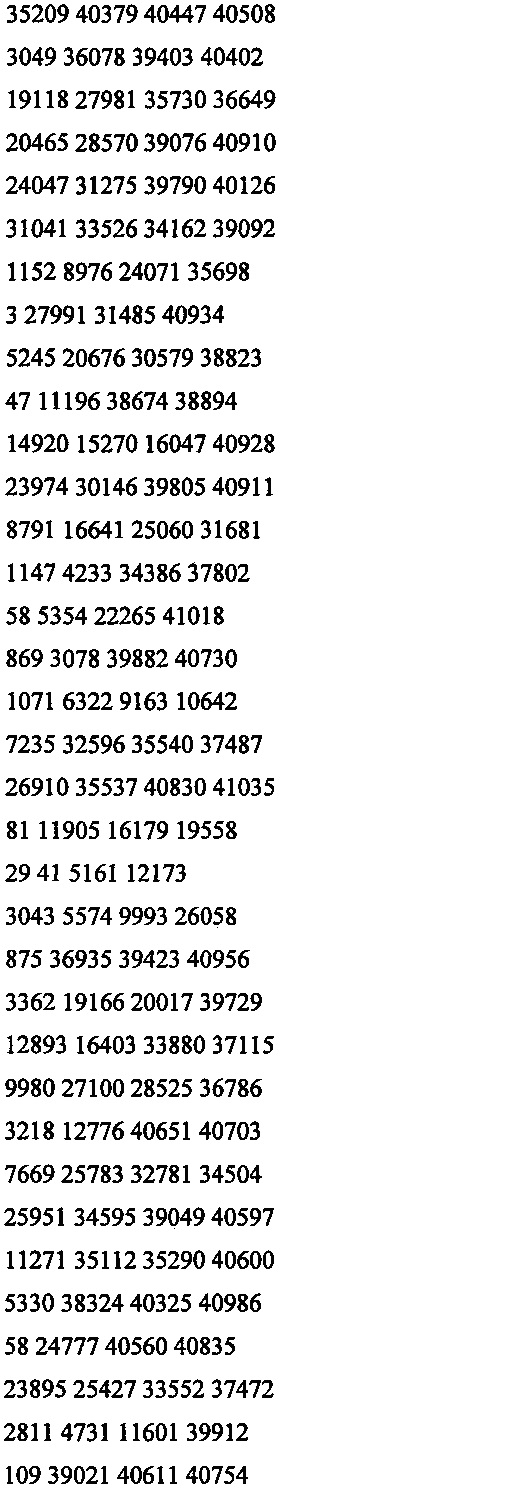

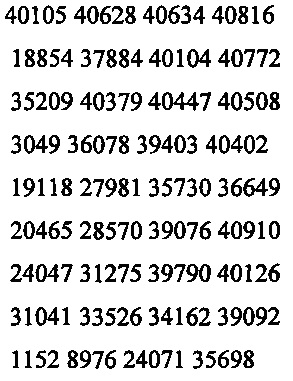

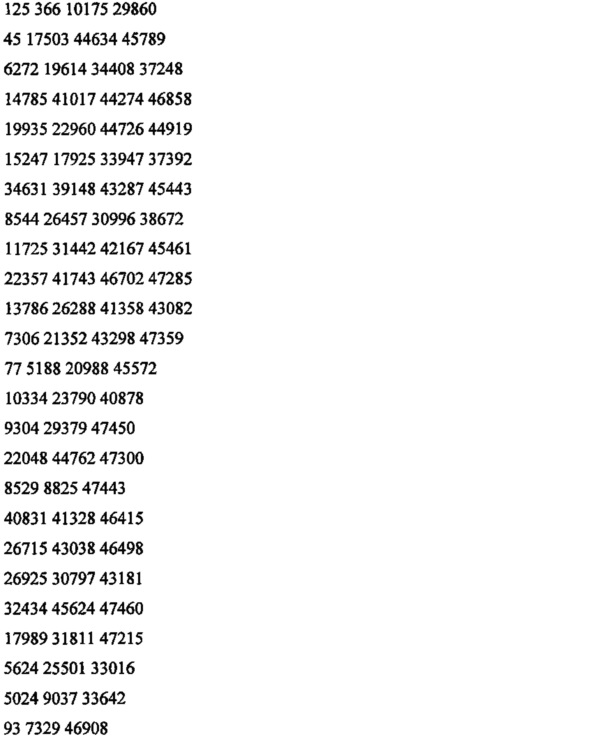

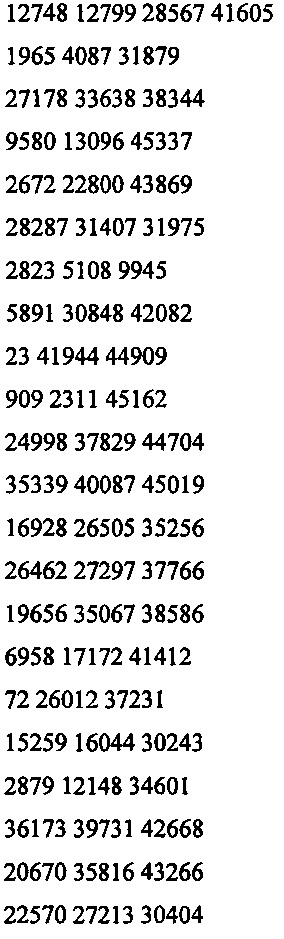

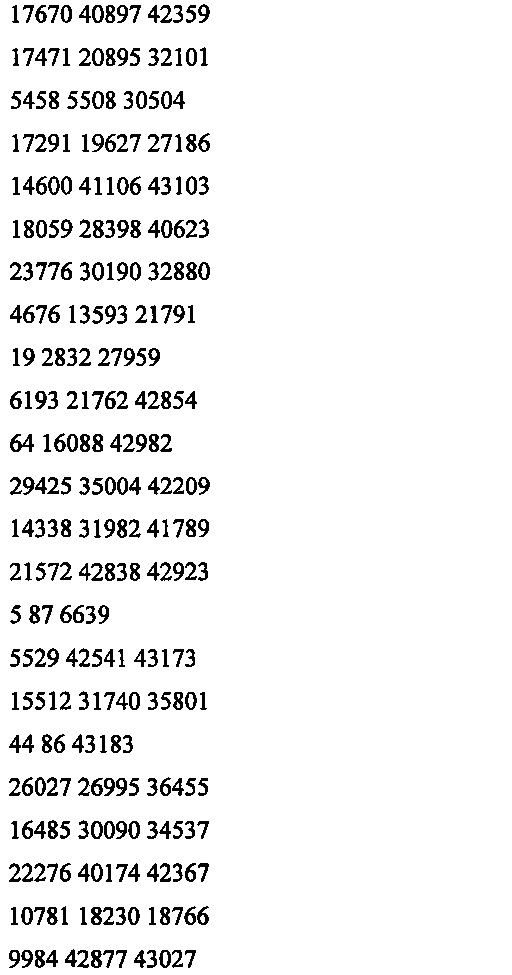

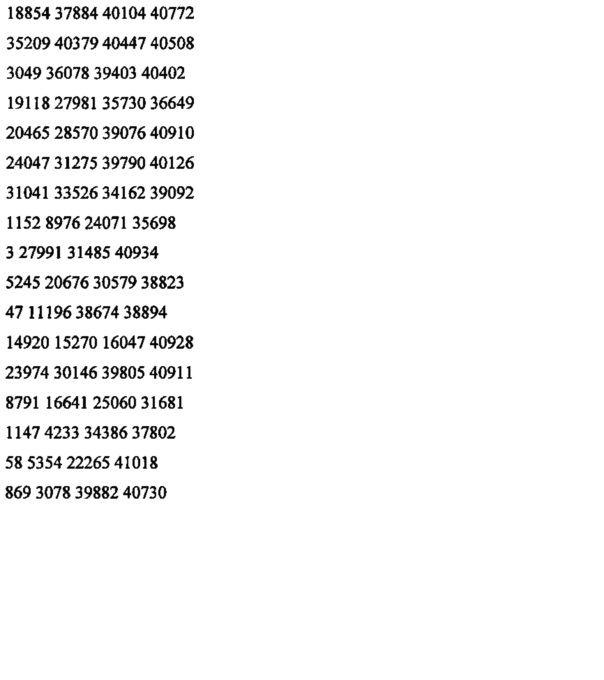

Седьмое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя этап кодирования для кодирования бита информации LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 10/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Восьмое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 10/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую информационному биту, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

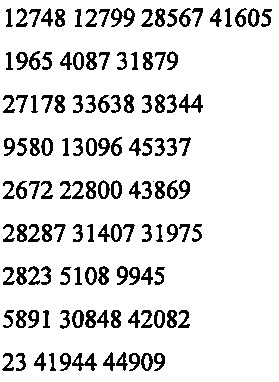

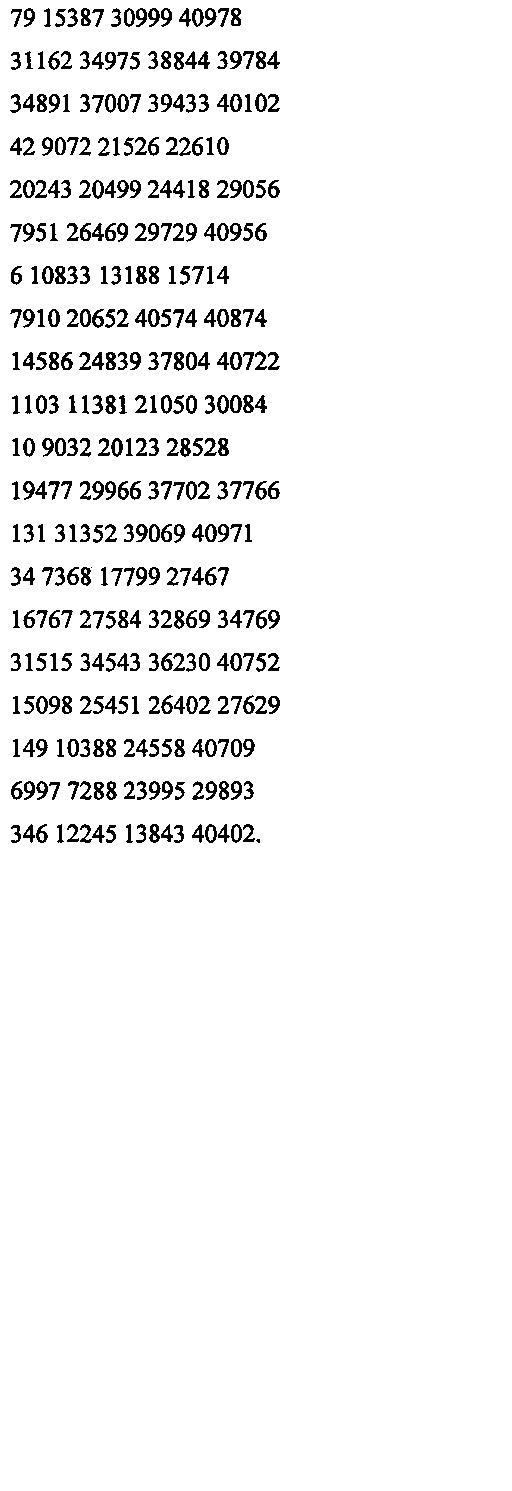

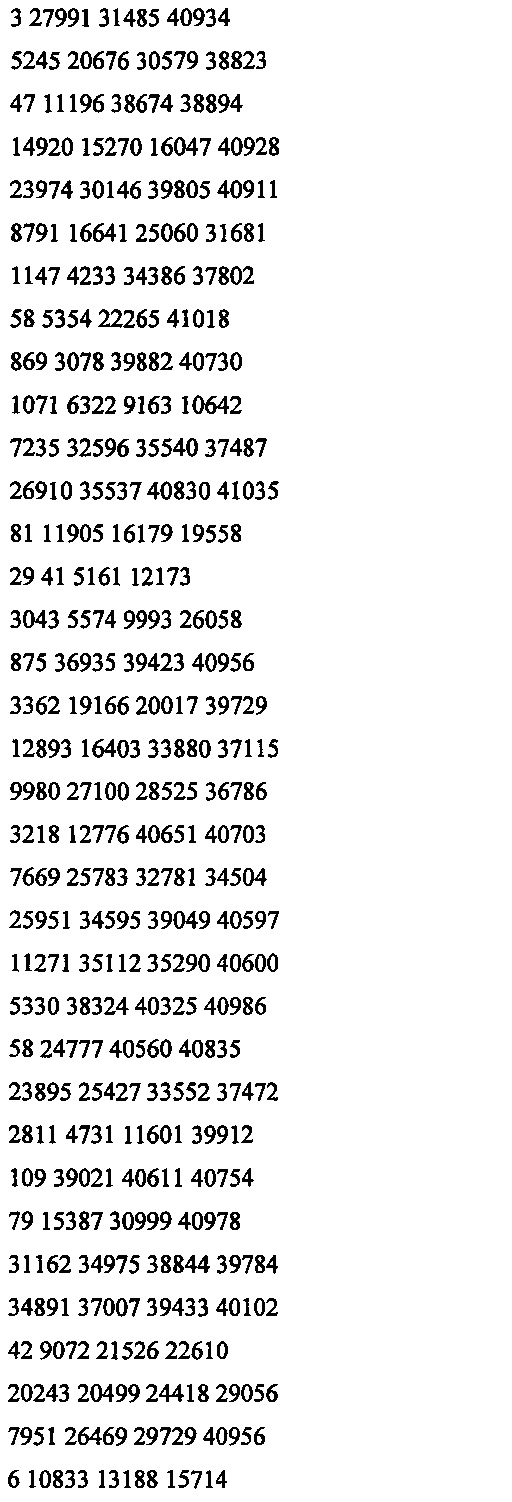

Девятое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 11/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

Десятое устройство обработки данных или способ обработки данных в соответствии с настоящим изобретением включает в себя блок декодирования или этап декодирования для декодирования LDPC-кода с кодовой длиной 64800 битов и скоростью кодирования 11/30, на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность). LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую биту информации, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах и выражается следующим образом

В соответствии с настоящим изобретением, бит информации кодируется в LDPC-коде с кодовой длинной 64800 битов и скоростями кодирования 7/30, 8/30, 9/30, 10/30 или 11/30 на основании матрицы контроля четности LDPC кода (кода с низкой плотностью проверок на четность).

В соответствии с настоящим изобретением LDPC-код с кодовой длиной 64800 битов и скоростями кодирования 7/30, 8/30, 9/30, 10/30 или 11/30 декодируется на основании матрицы контроля четности LDPC-кода (кода с низкой плотностью проверок на четность).

LDPC-код включает в себя бит информации и бит четности. Матрица контроля четности включает в себя часть информационной матрицы, соответствующую информационному биту, и часть матрицы контроля четности, соответствующую биту четности. Часть информационной матрицы показана таблицей начальных значений матрицы контроля четности. Таблица начальных значений матрицы контроля четности представляет собой таблицу, показывающую расположения элементов 1 части информационной матрицы в каждых 360 столбцах.

Таблица начальных значений матрицы контроля четности со скоростью кодирования 7/30 выражается следующим образом

Таблица начальных значений матрицы контроля четности со скоростью кодирования 8/30 выражается следующим образом

Таблица начальных значений матрицы контроля четности со скоростью кодирования 9/30 выражается следующим образом

Таблица начальных значений матрицы контроля четности со скоростью кодирования 10/30 выражается следующим образом

Таблица начальных значений матрицы контроля четности со скоростью кодирования 11/30 выражается следующим образом

Устройство обработки данных может быть независимым устройством и может быть внутренним блоком, образуя одно устройство.

Полезные результаты изобретения

В соответствии с настоящим изобретением можно обеспечить LDPC-код с превосходным значением частоты появления ошибок.

Краткое описание чертежей

Фиг. 1 является иллюстрацией матрицы Н контроля четности LDPC-кода.

Фиг. 2 представляет собой блок-схему алгоритма, иллюстрирующую последовательность декодирования LDPC-кода.

Фиг. 3 является иллюстрацией примера матрицы контроля четности LDPC-кода.

Фиг. 4 является иллюстрацией графа Таннера матрицы контроля четности.

Фиг. 5 является иллюстрацией переменного узла.

Фиг. 6 является иллюстрацией узла проверки.

Фиг. 7 является иллюстрацией примера конфигурации варианта осуществления системы передачи, к которой применяется настоящее изобретение.

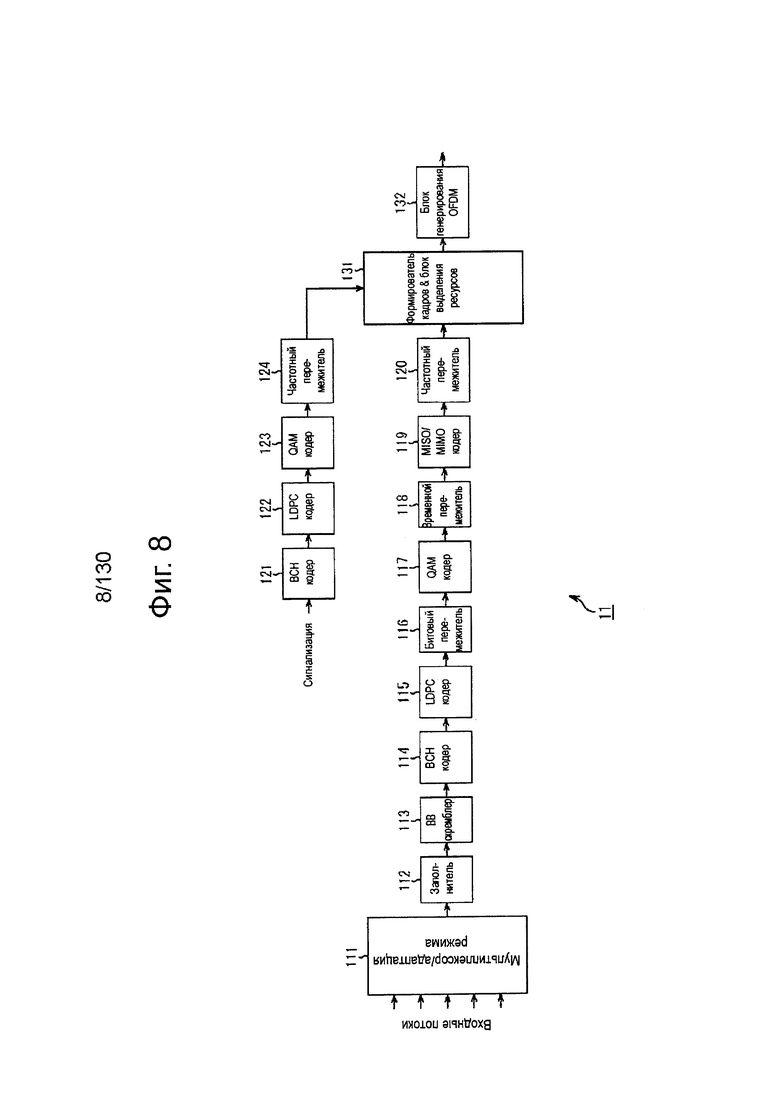

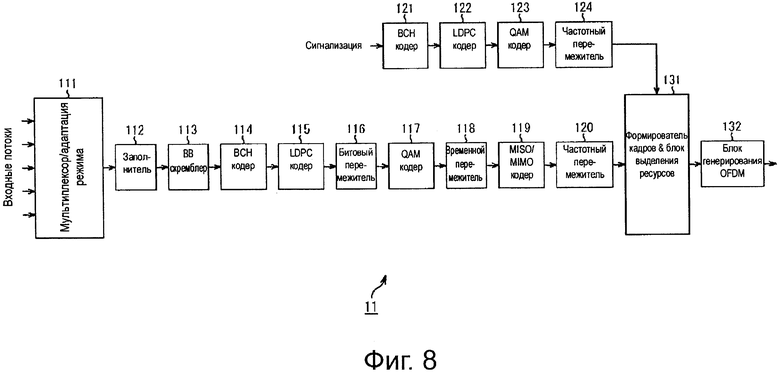

Фиг. 8 является блок-схемой, иллюстрирующей пример конфигурации передающего устройства 11.

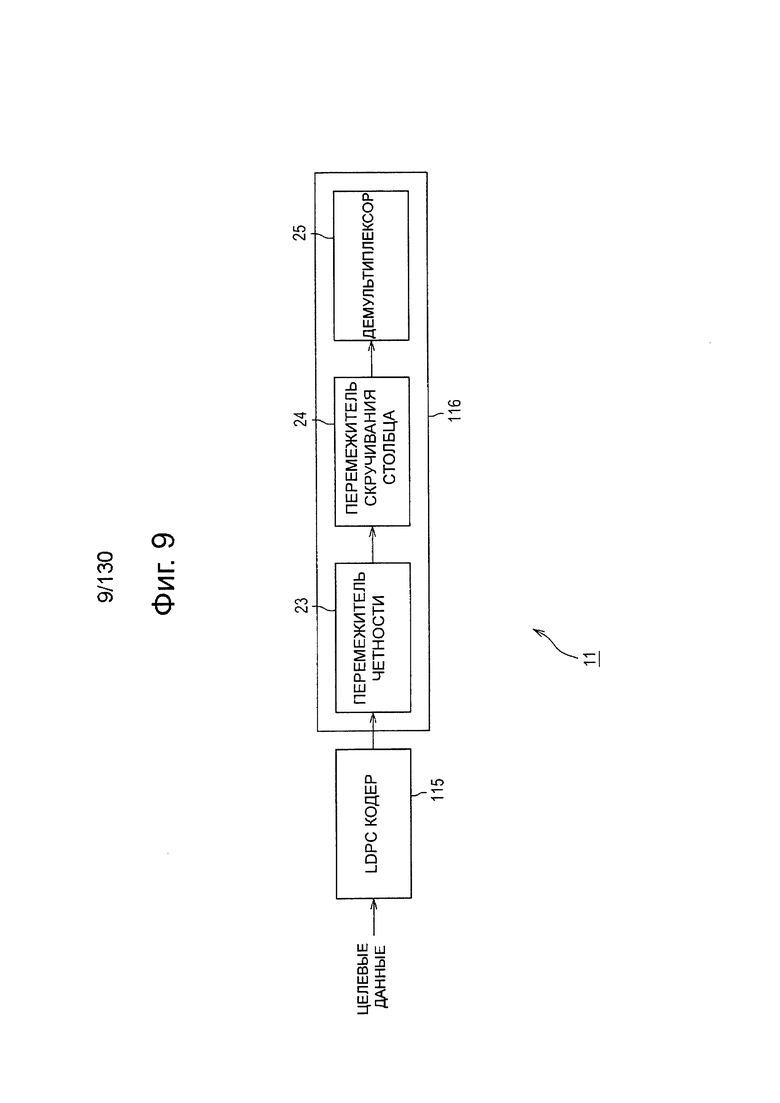

Фиг. 9 показывает блок-схему, иллюстрирующую пример конфигурации битового перемежителя 116.

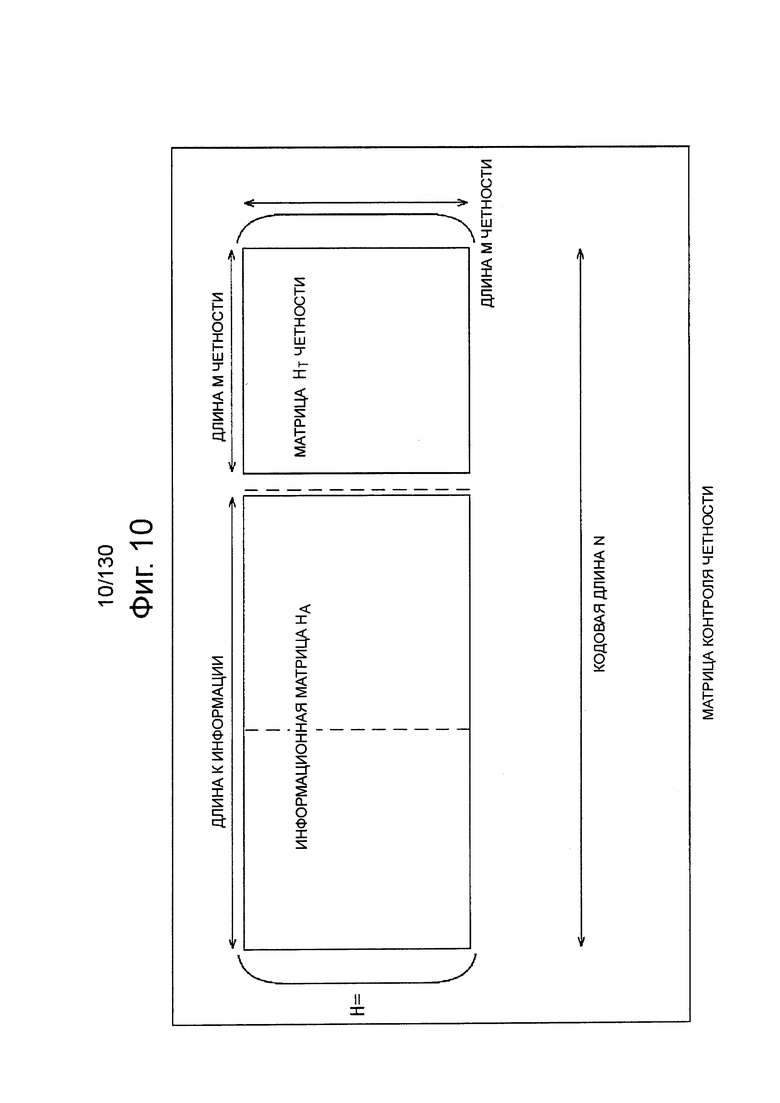

Фиг. 10 является иллюстрацией матрицы контроля четности.

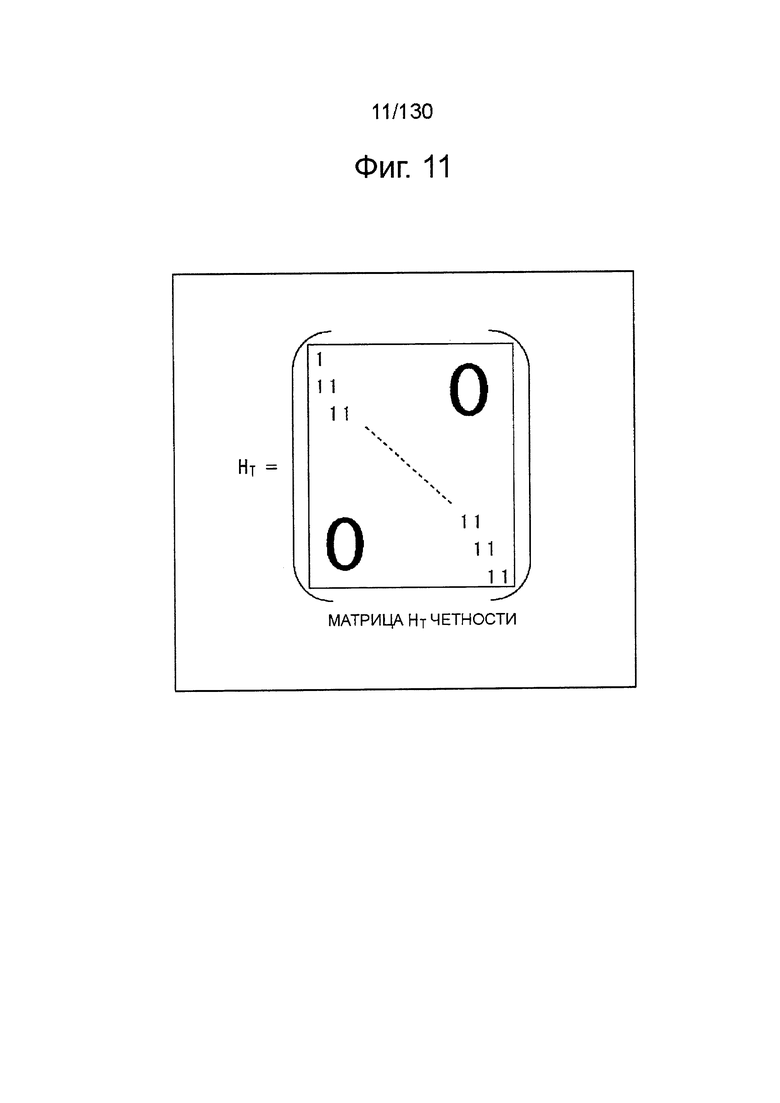

Фиг. 11 является иллюстрацией матрицы контроля четности.

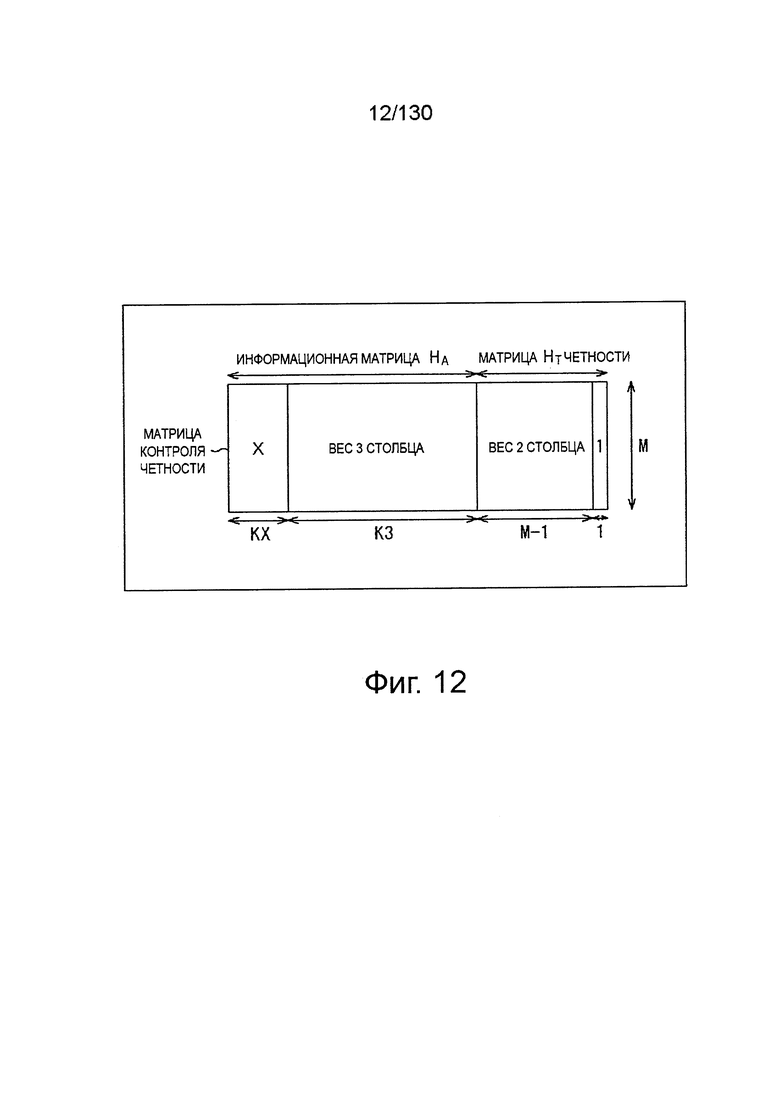

Фиг. 12 является иллюстрацией матрицы контроля четности LDPC-кода, определенного в стандарте DVB-S.2.

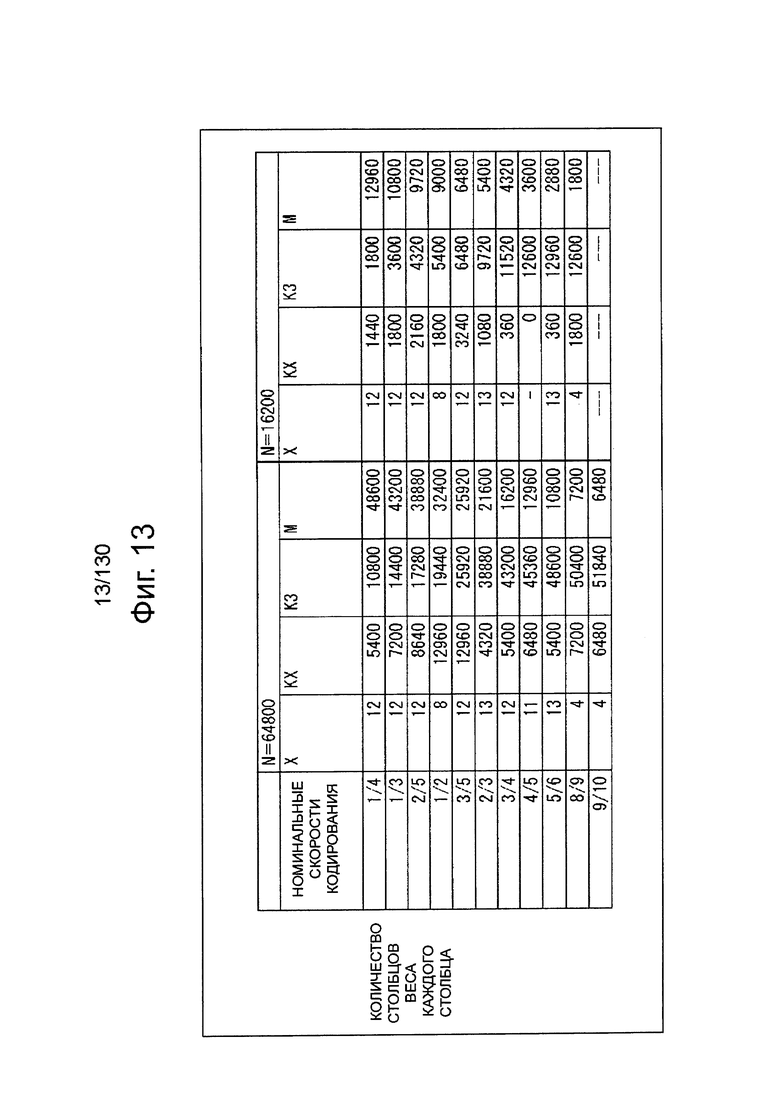

Фиг. 13 является иллюстрацией матрицы контроля четности LDPC-кода, определенного в стандарте DVB-S.2.

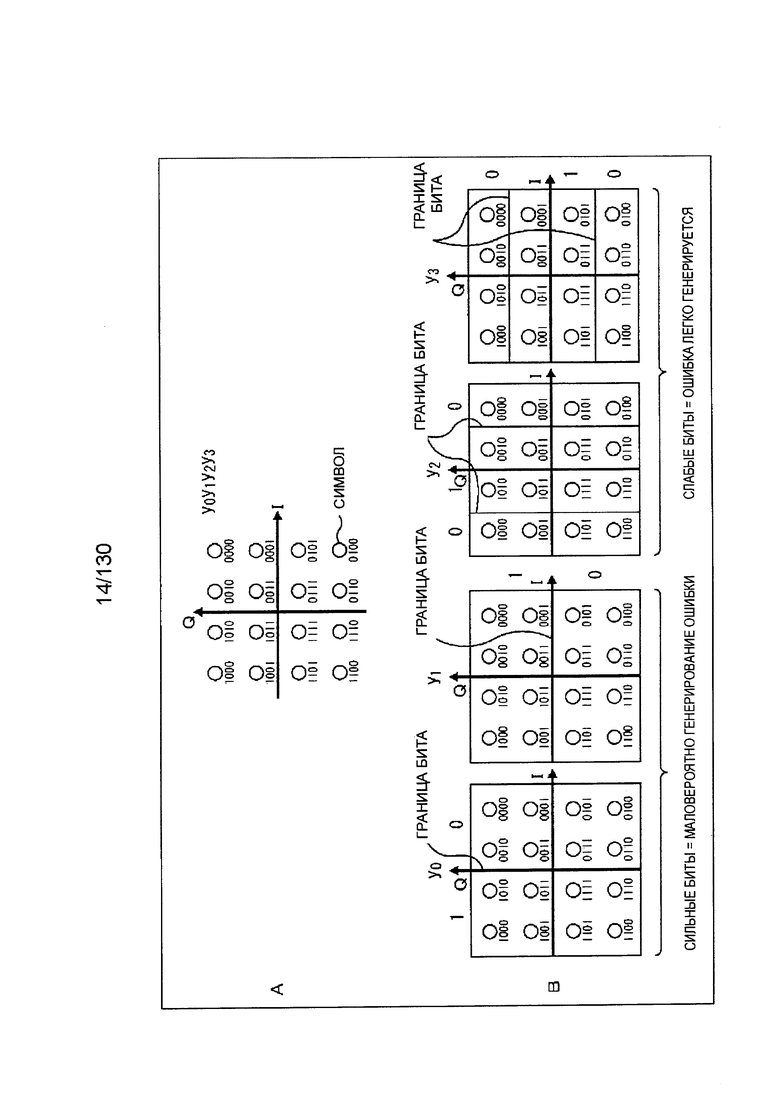

Фиг. 14 является иллюстрацией расположения 16QAM сигнальных точек.

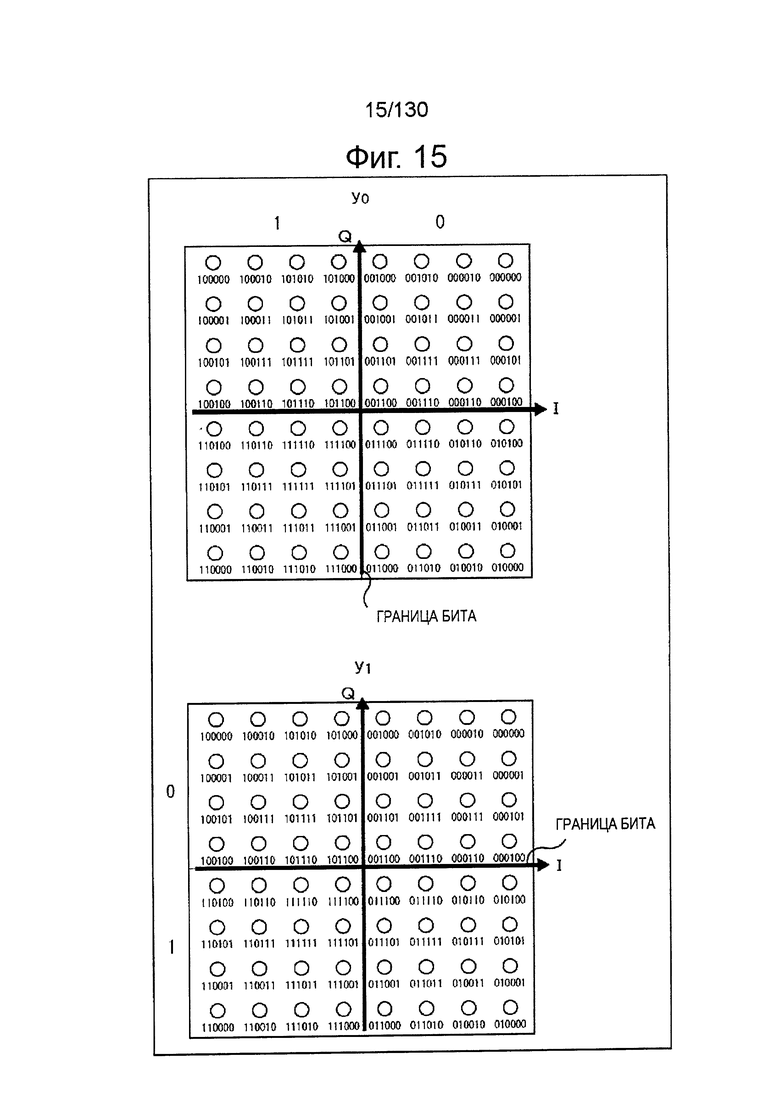

Фиг. 15 является иллюстрацией расположения 64QAM сигнальных точек.

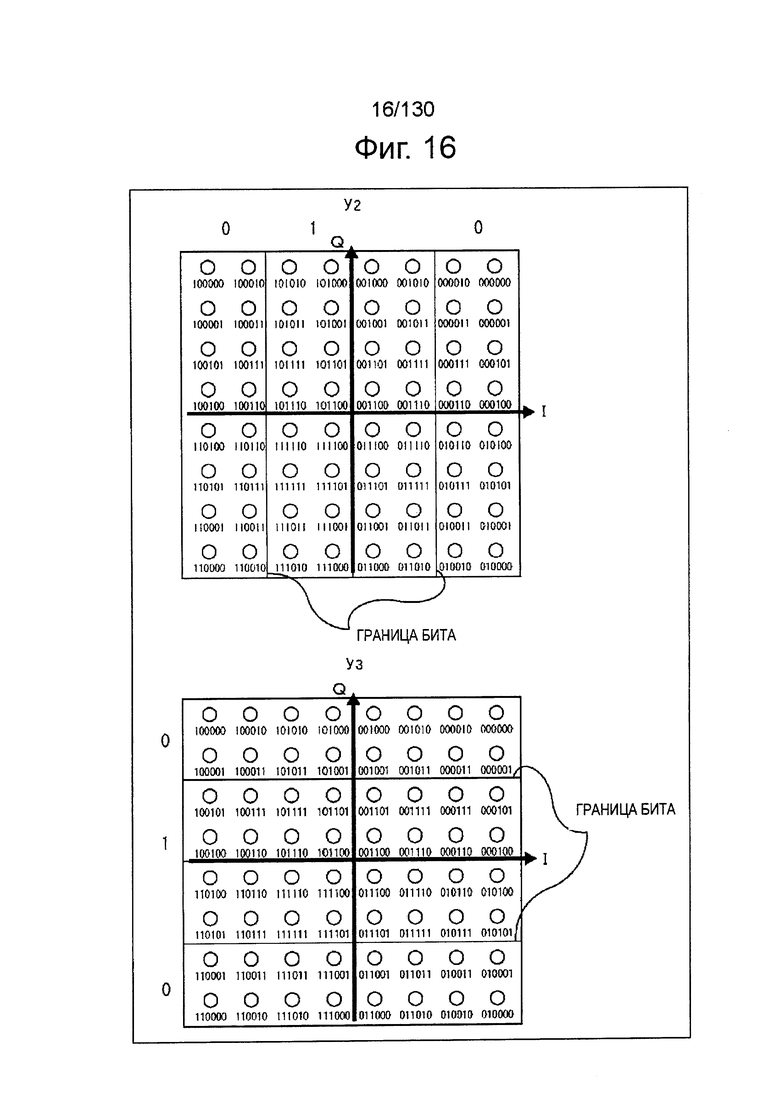

Фиг. 16 является иллюстрацией расположения 64QAM сигнальных точек.

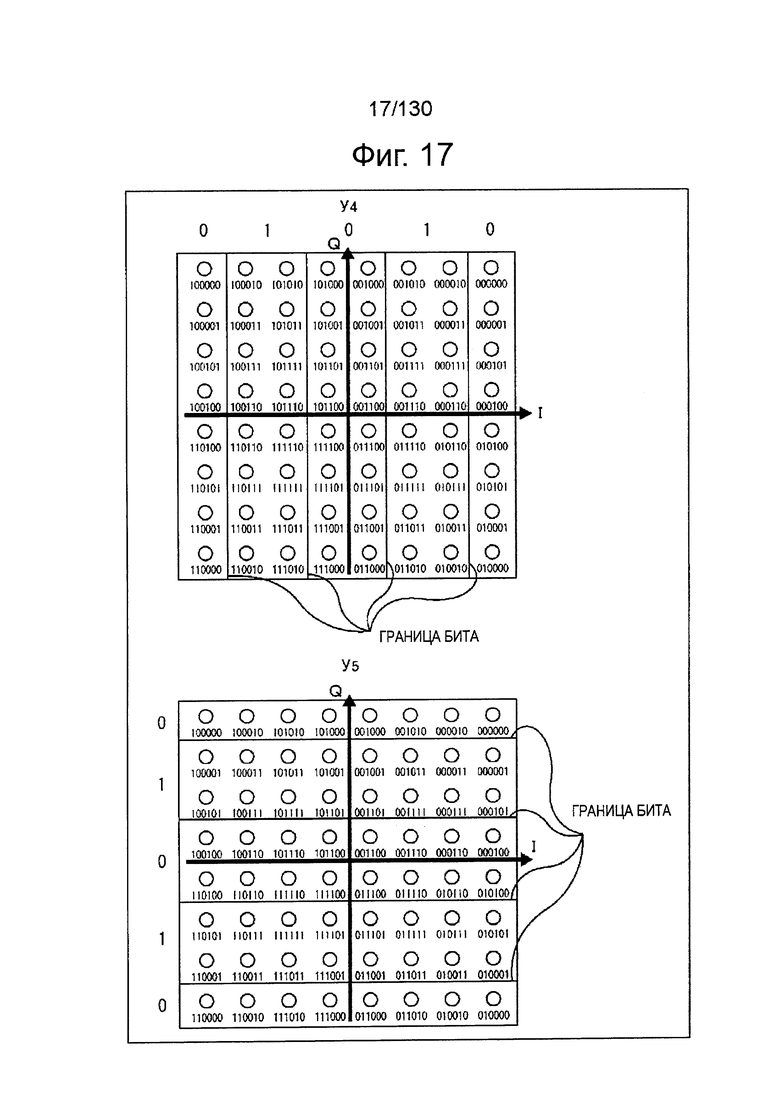

Фиг. 17 является иллюстрацией расположения 64QAM сигнальных точек.

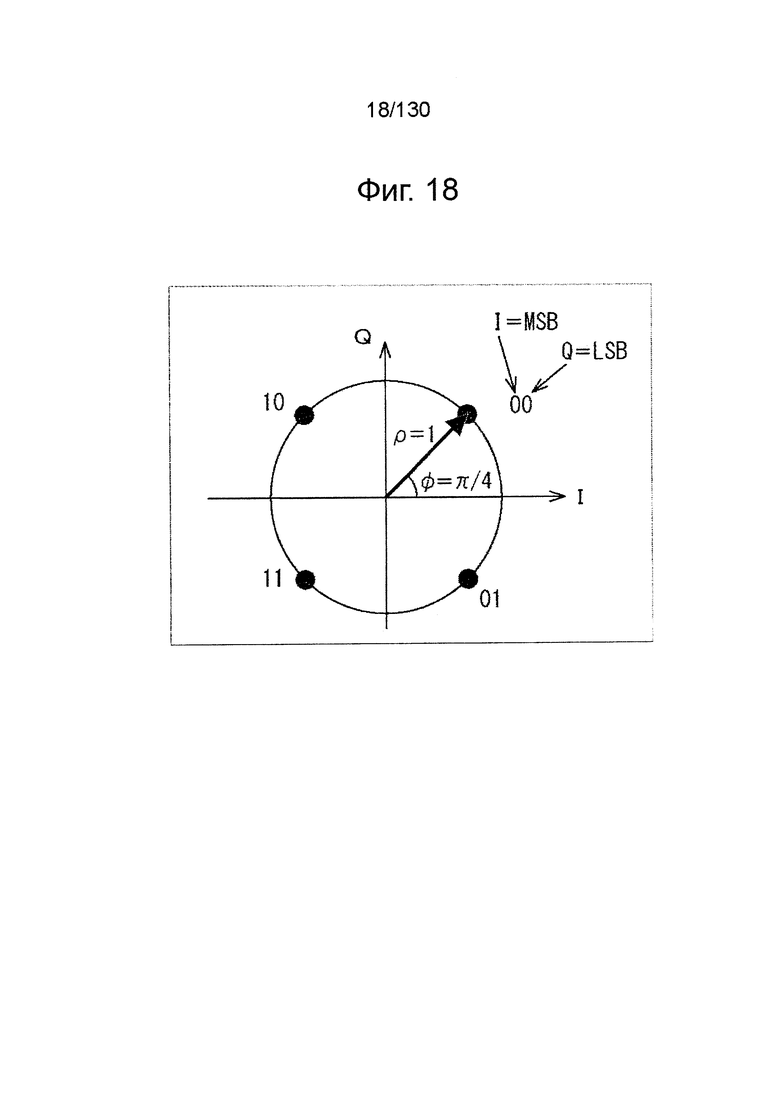

Фиг. 18 является иллюстрацией расположения сигнальных точек, как определено в стандарте DVB-S.2.

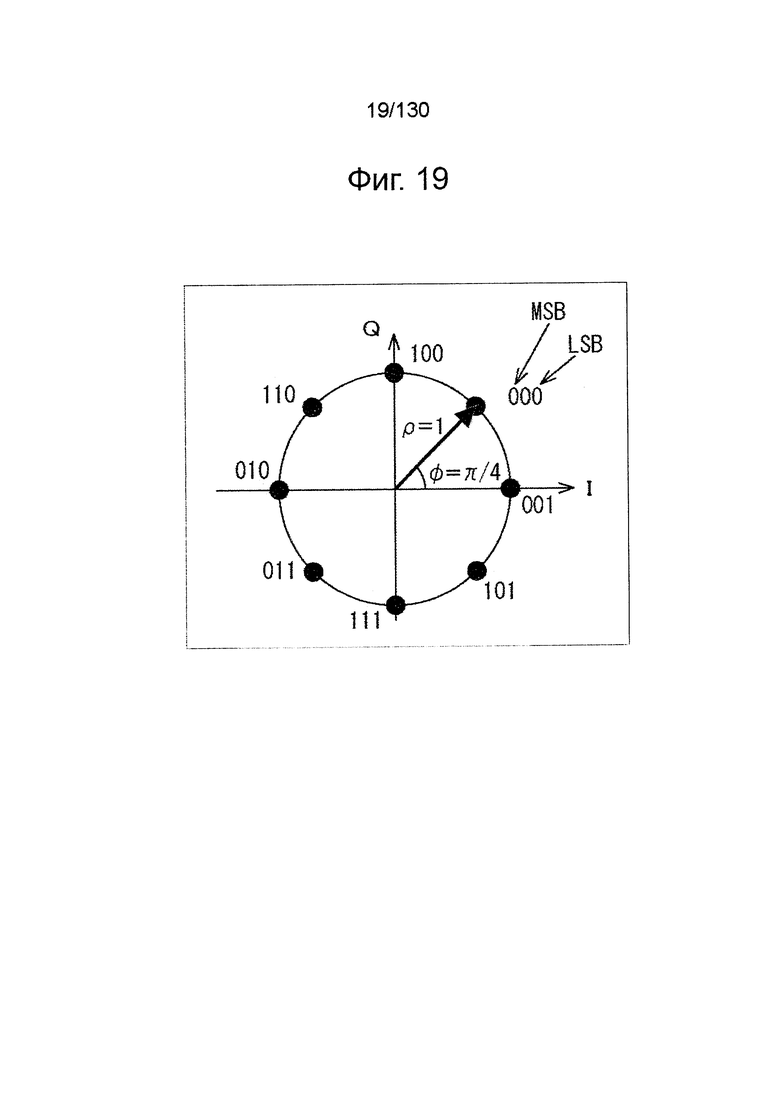

Фиг. 19 является иллюстрацией расположения сигнальных точек, как определено в стандарте DVB-S.2.

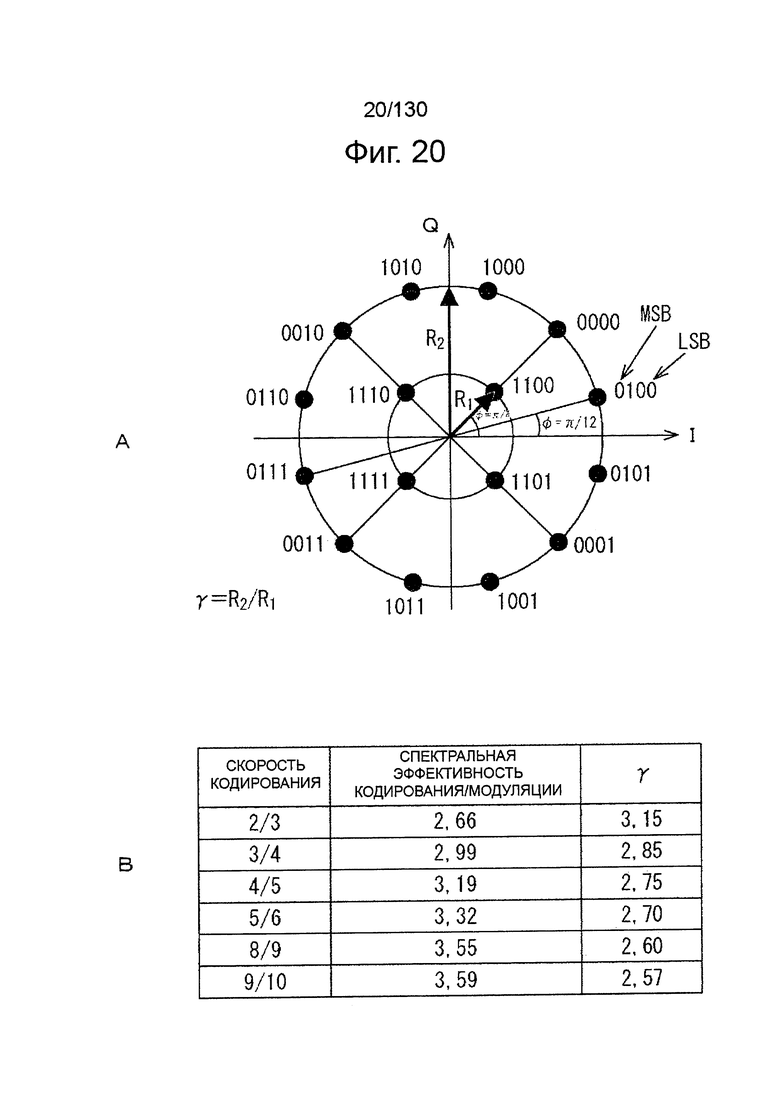

Фиг. 20 является иллюстрацией расположения сигнальных точек, как определено в стандарте DVB-S.2.

Фиг. 21 является иллюстрацией расположения сигнальных точек, как определено в стандарте DVB-S.2.

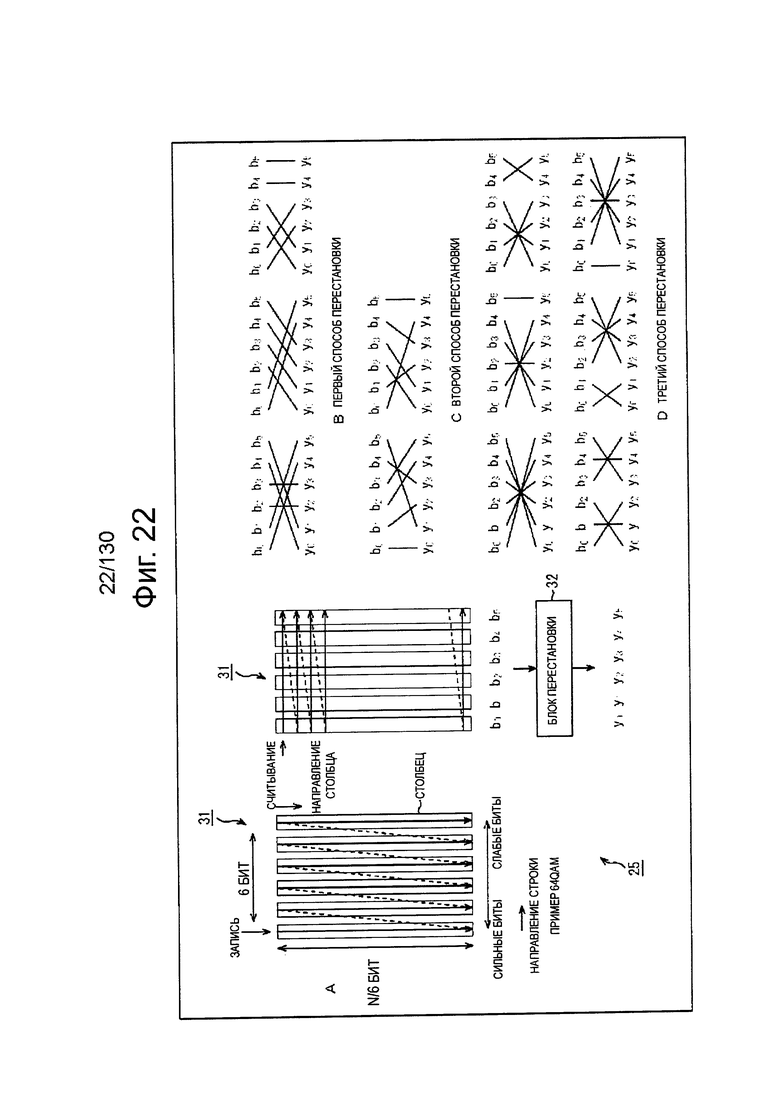

Фиг. 22 является иллюстрацией процесса обработки демультиплексора 25.

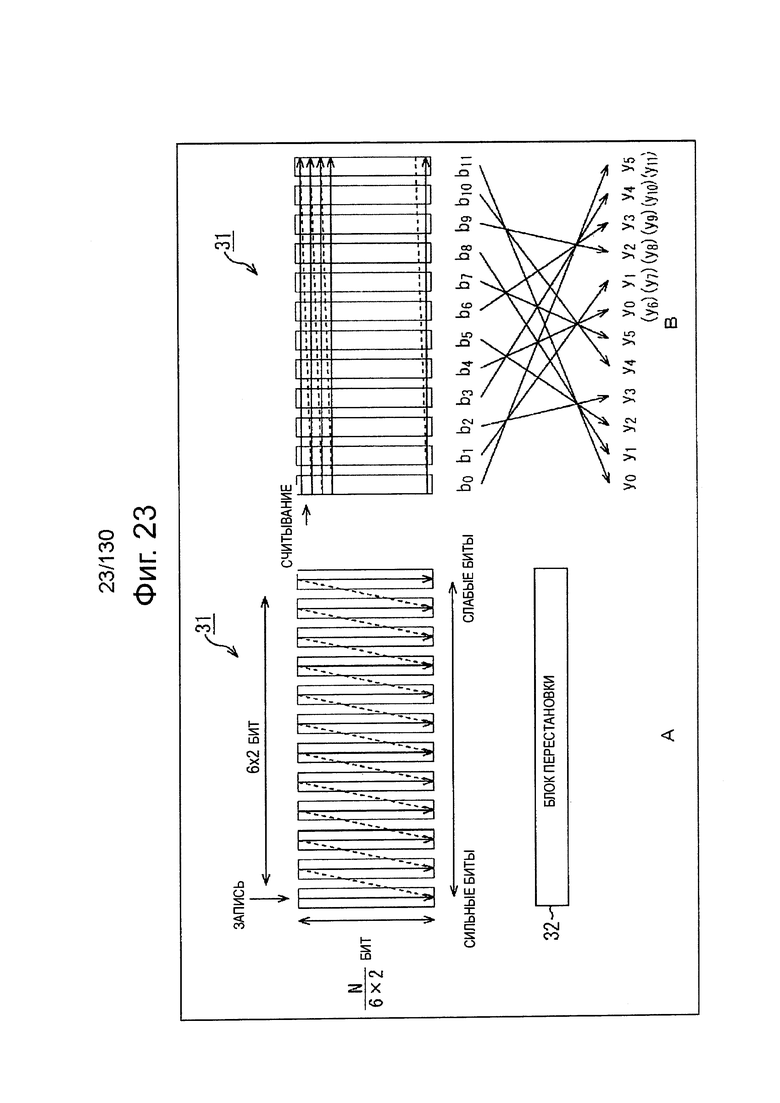

Фиг. 23 является иллюстрацией процесса обработки демультиплексора 25.

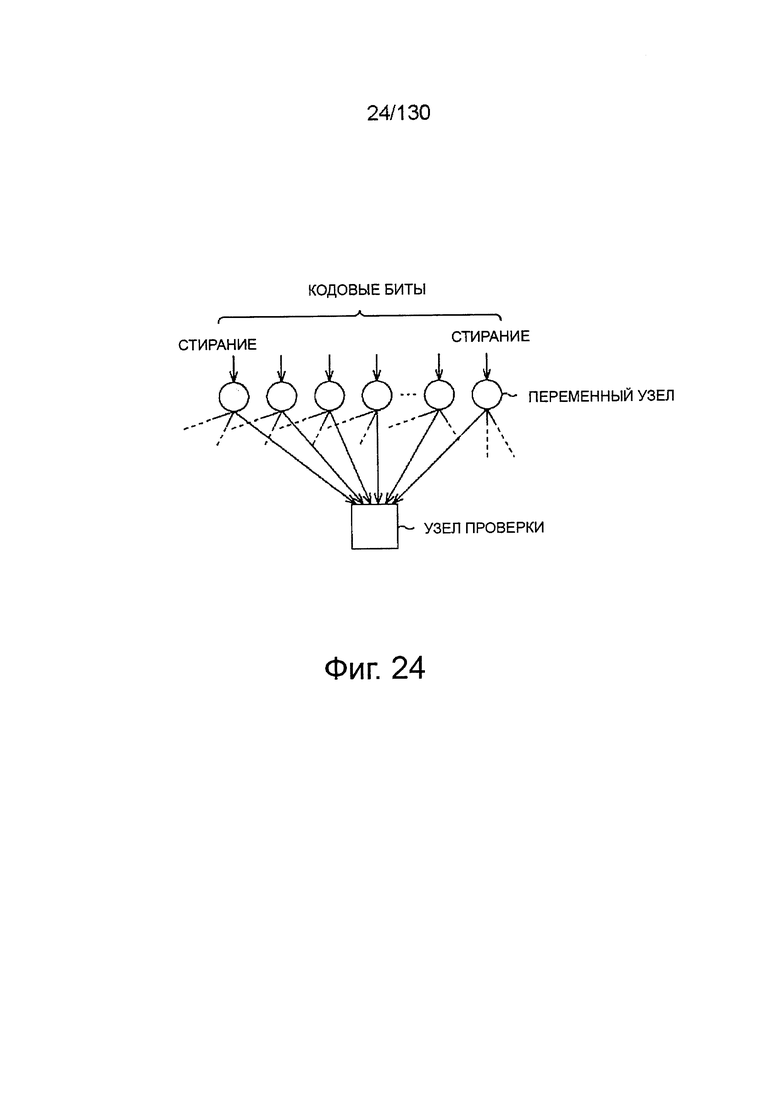

Фиг. 24 является иллюстрацией графа Таннера для декодирования LDPC-кода.

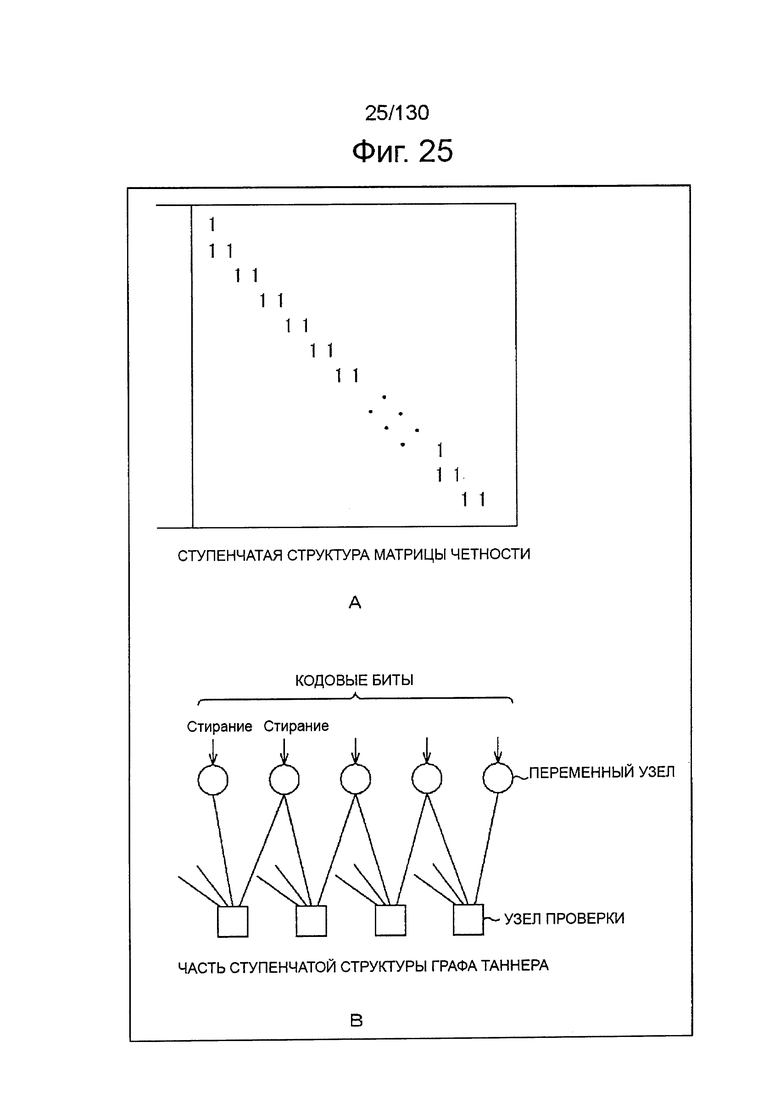

Фиг. 25 является иллюстрацией матрицы Нт четности, которая приобретает ступенчатую структуру, и графа Таннера, соответствующего матрице Нт четности.

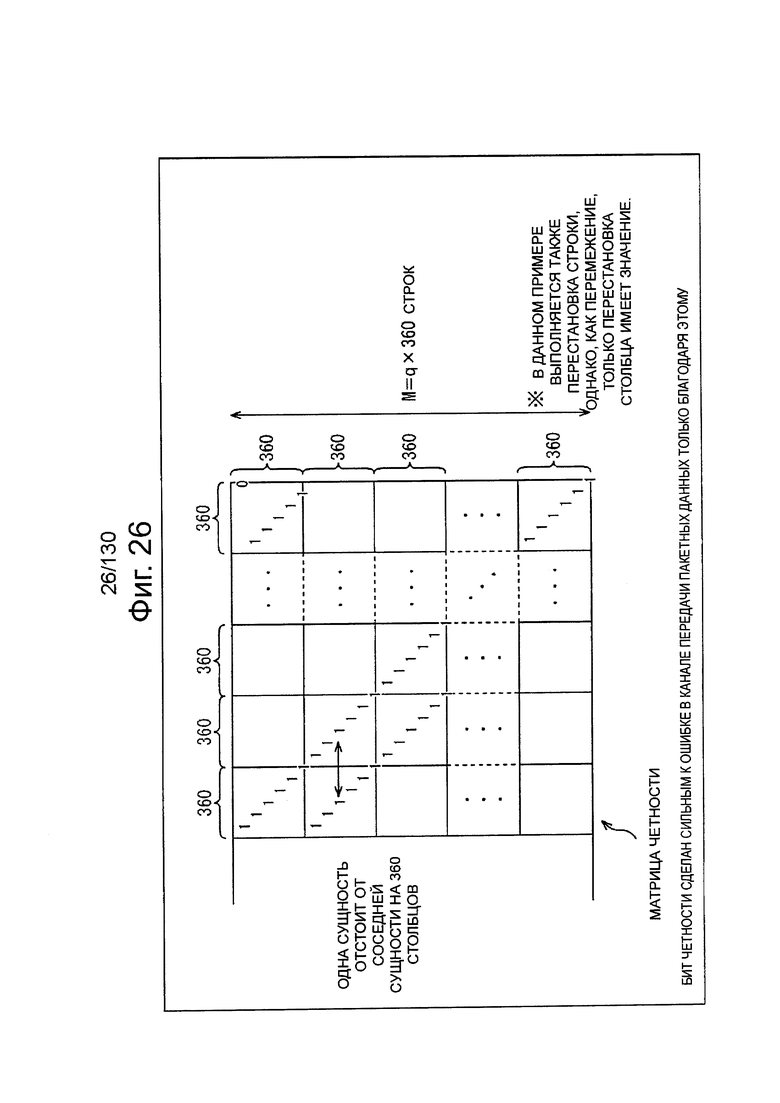

Фиг. 26 является иллюстрацией матрицы Нт четности матрицы H контроля четности, соответствующего LDPC-кода, после перемежения битов четности.

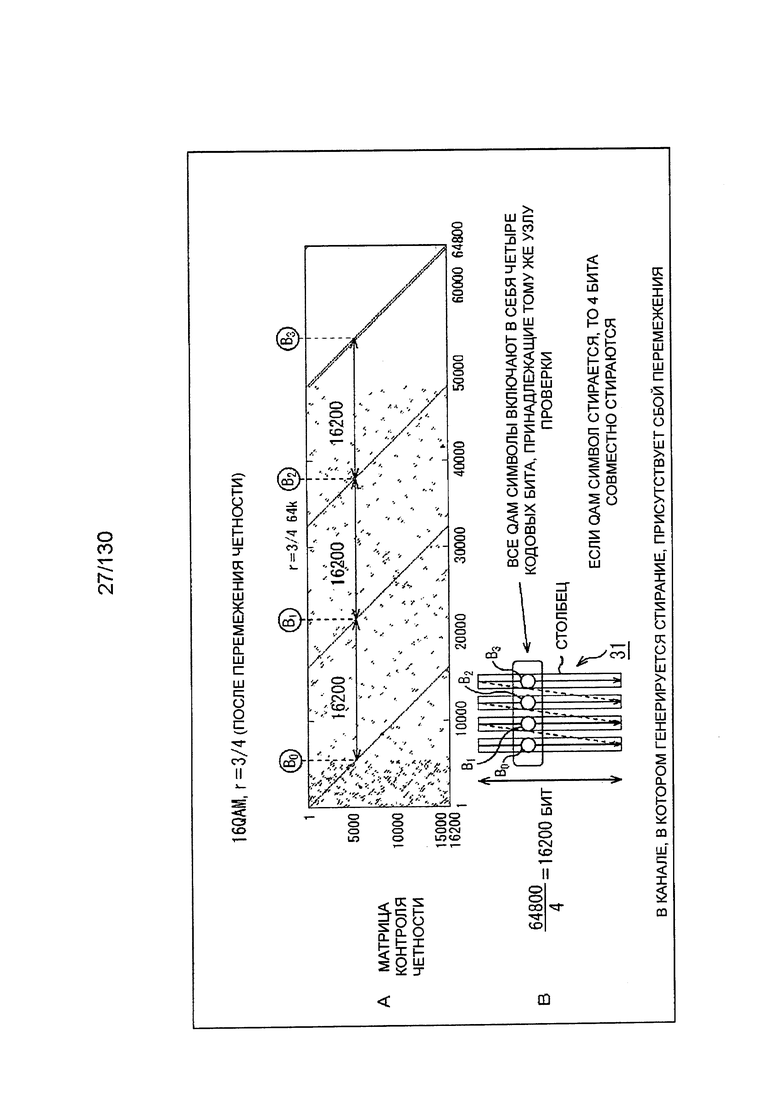

Фиг. 27 является иллюстрацией преобразованной матрицы контроля четности.

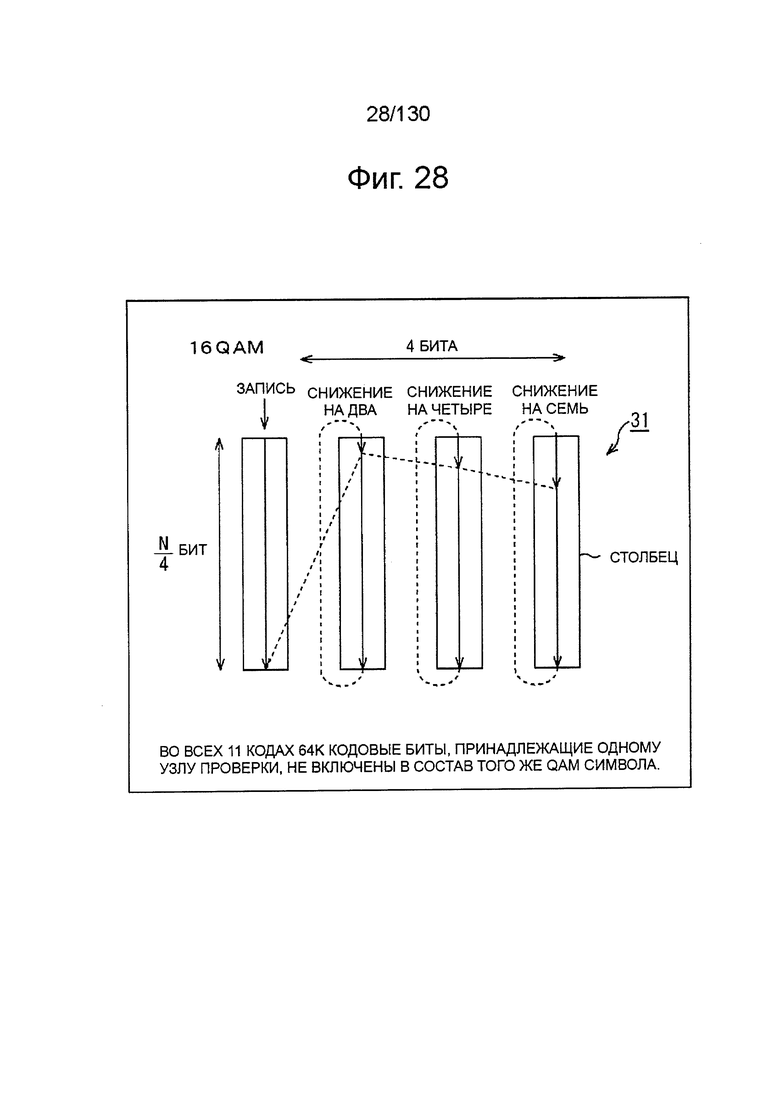

Фиг. 28 является иллюстрацией процесса обработки скручивания столбцов перемежителем 24.

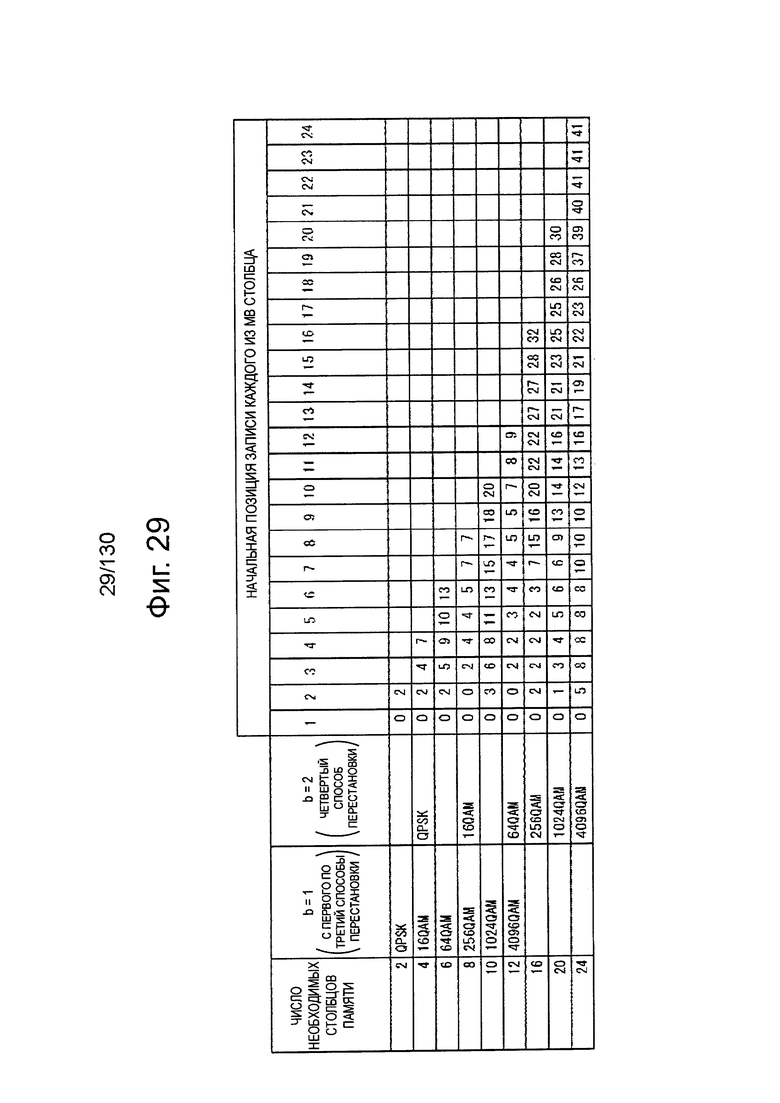

Фиг. 29 является иллюстрацией нумерации колонки памяти 31, что необходимо для скручивания столбцов перемежителем и адреса позиции начала записи.

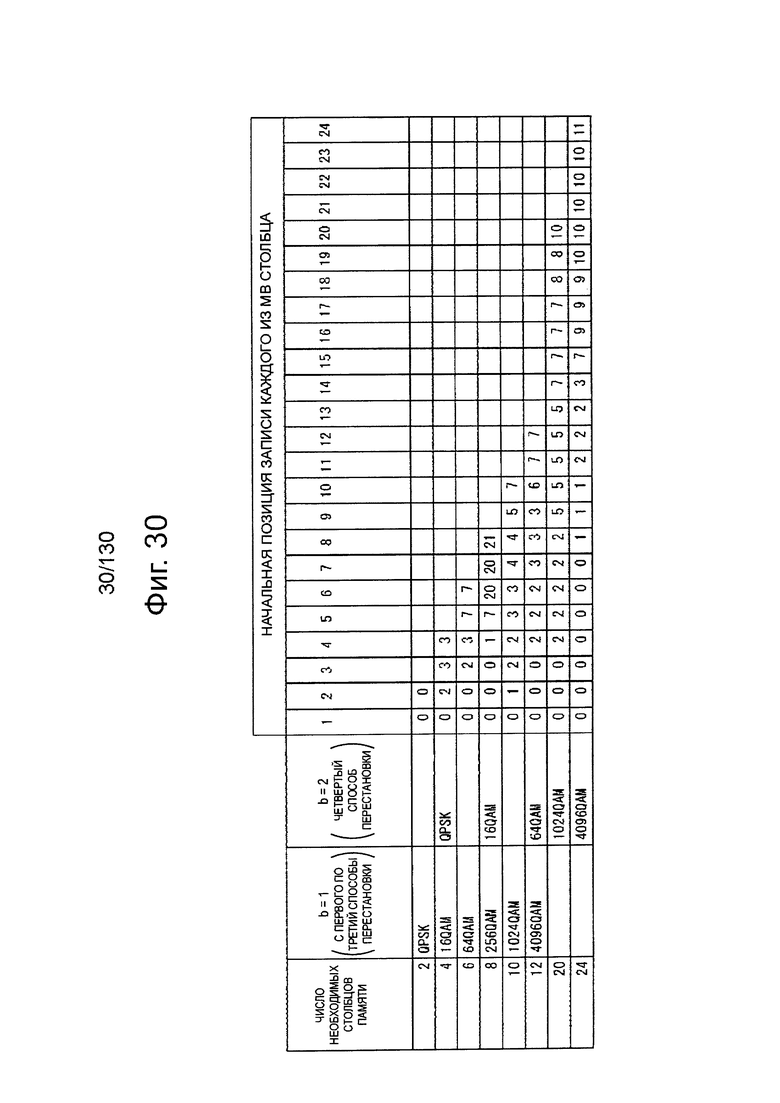

Фиг. 30 является иллюстрацией нумерации столбцов памяти 31, что необходимо для скручивания столбцов перемежителем и адреса позиции начала записи.

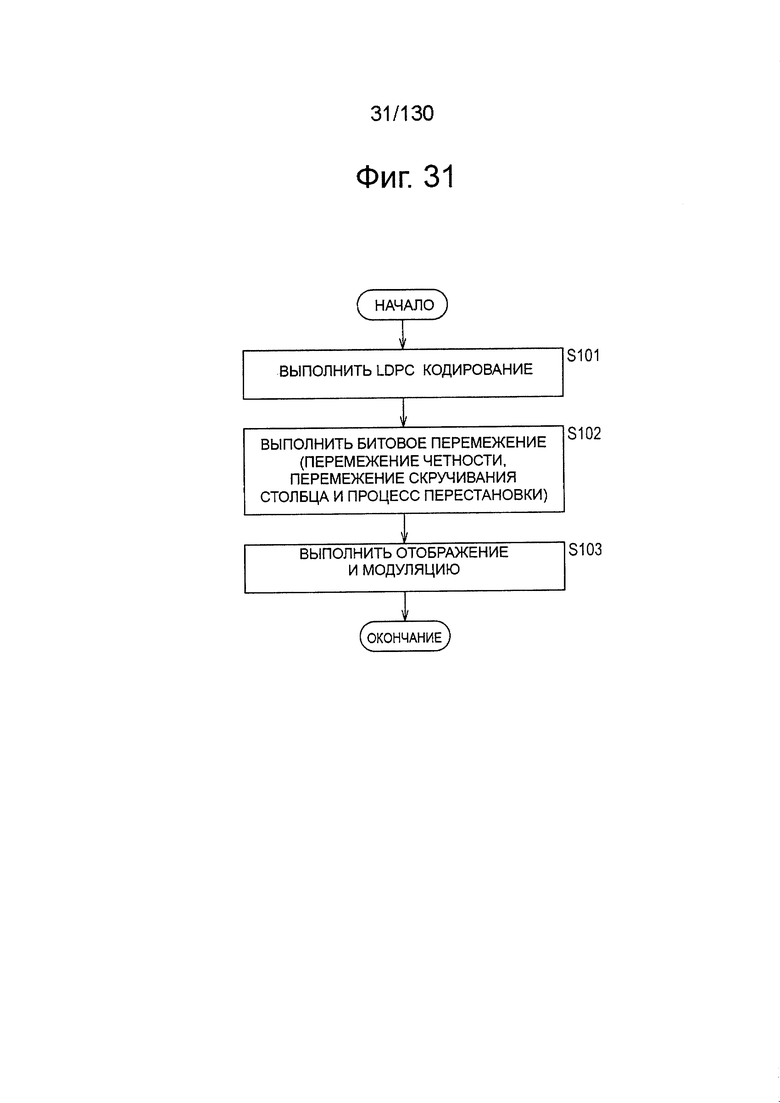

Фиг. 31 является блок-схемой алгоритма, иллюстрирующей процесс обработки, выполняемым битовым перемежителем 116 и QAM кодером 117.

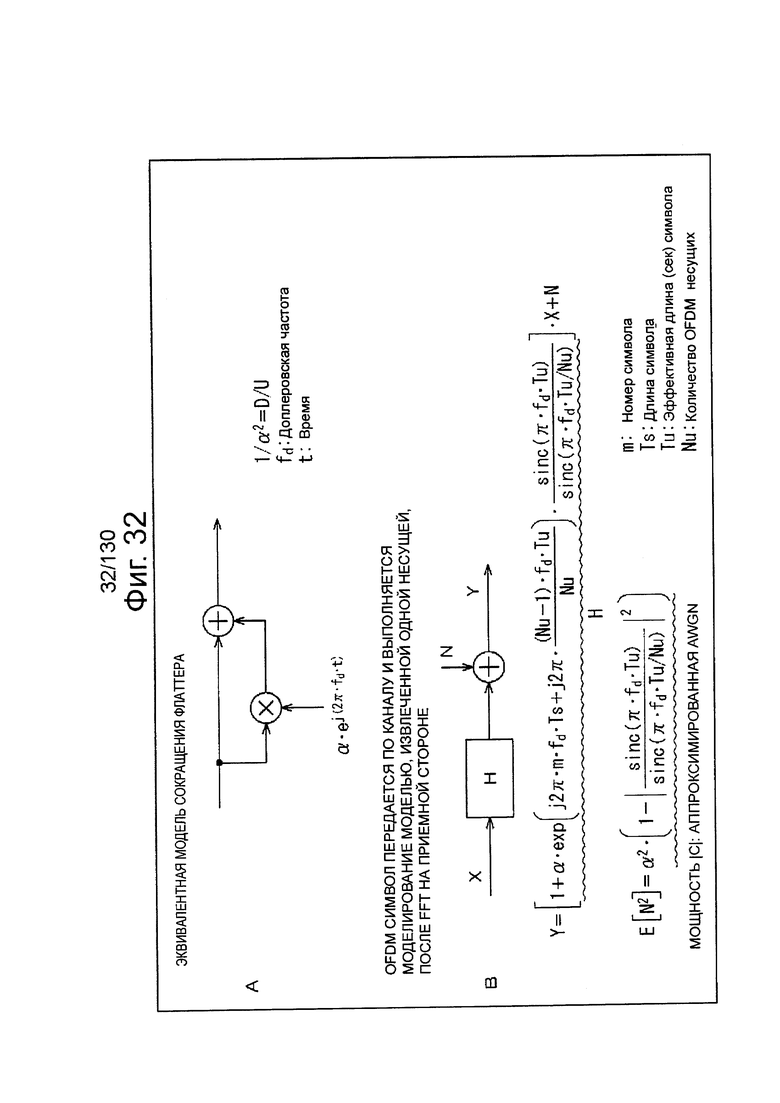

Фиг. 32 является иллюстрацией модели канала связи, принятой посредством моделирования.

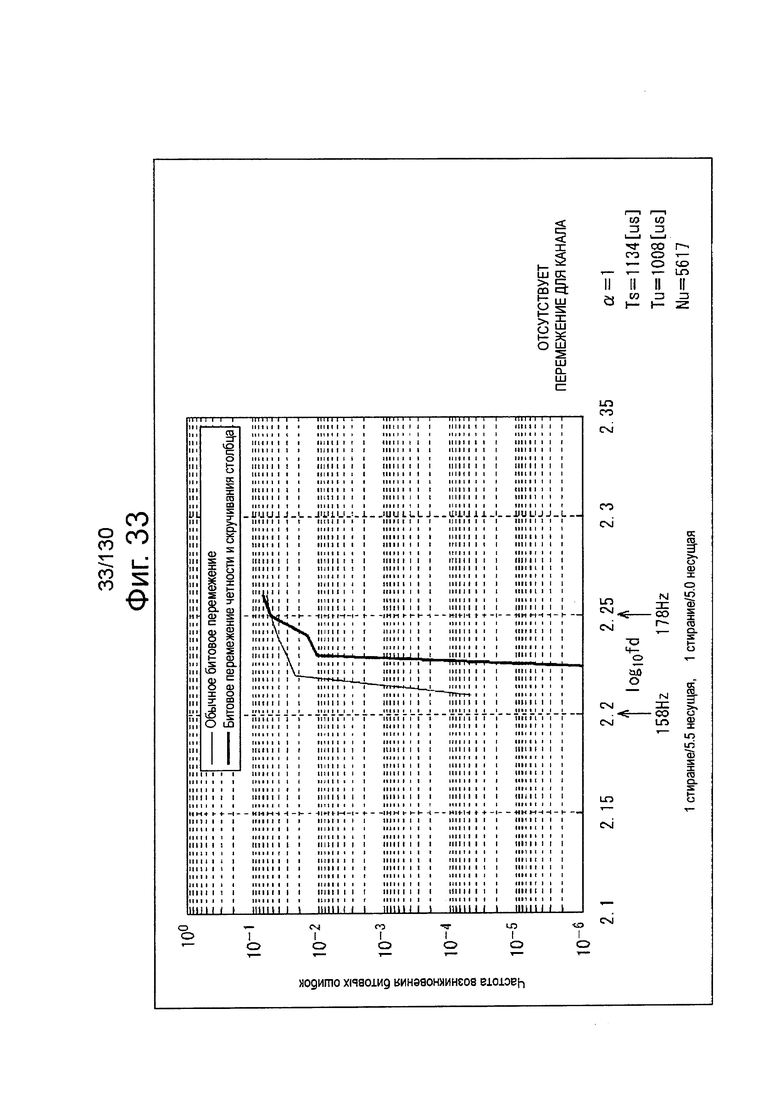

Фиг. 33 является иллюстрацией отношения частоты возникновения ошибок, полученной путем моделирования, и доплеровской частоты fd флаттера.

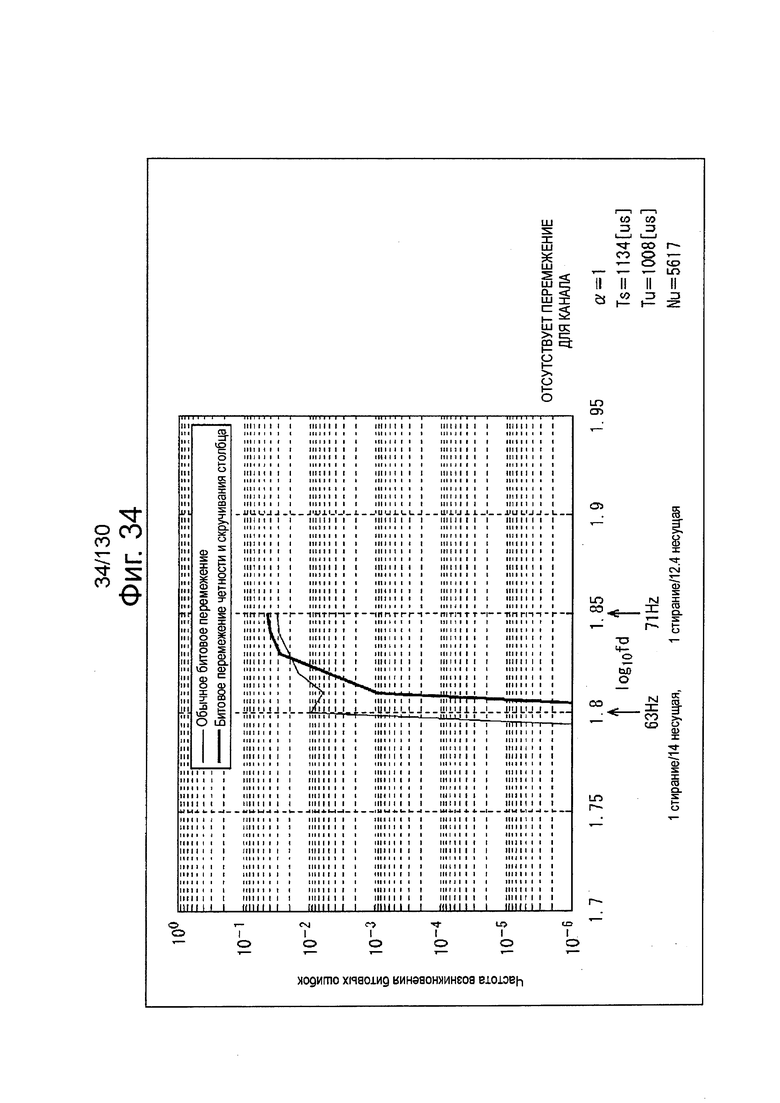

Фиг. 34 является иллюстрацией отношения частоты возникновения ошибок, полученной путем моделирования, и доплеровской частоты fd флаттера.

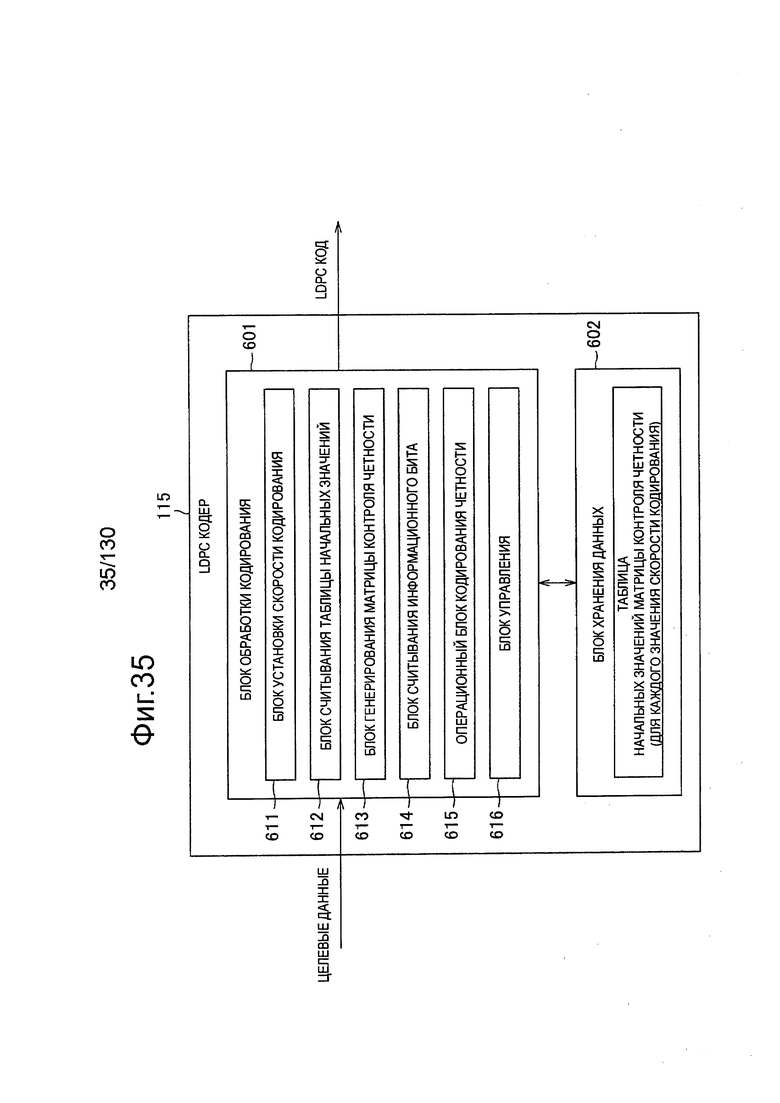

Фиг. 35 является блок-схемой, иллюстрирующей пример конфигурации LDPC-кодера 115.

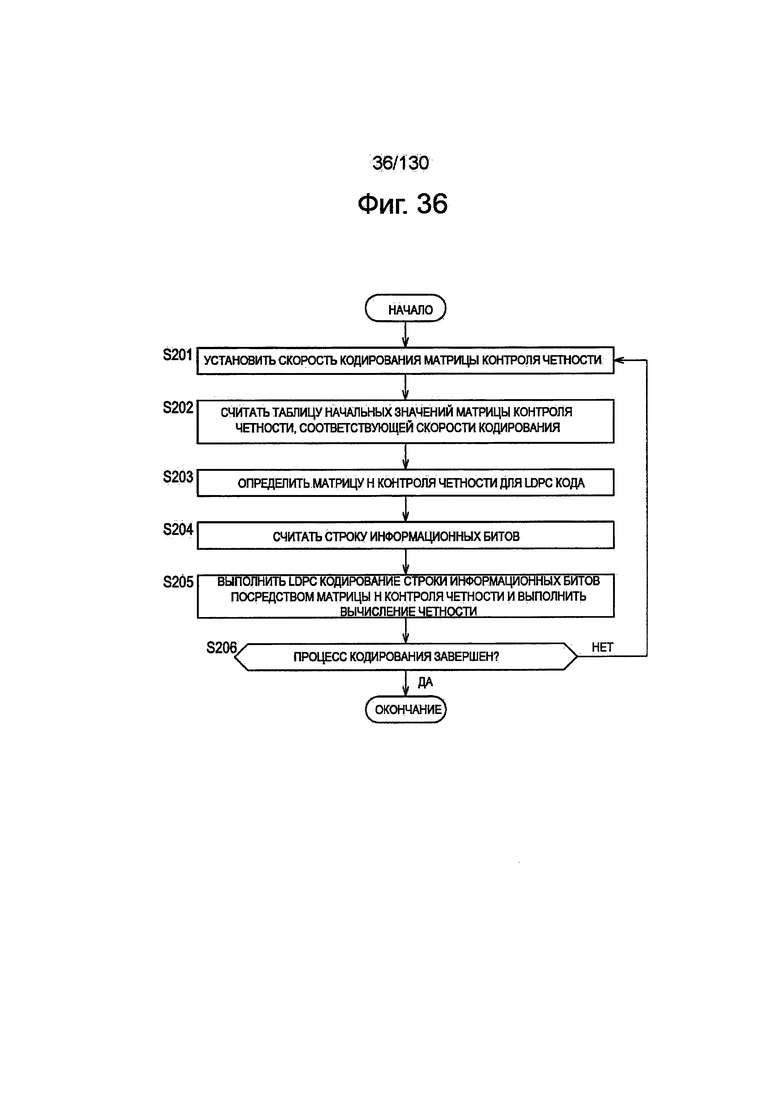

Фиг. 36 является блок-схемой алгоритма, иллюстрирующей процесс обработки LDPC-кодера 115.

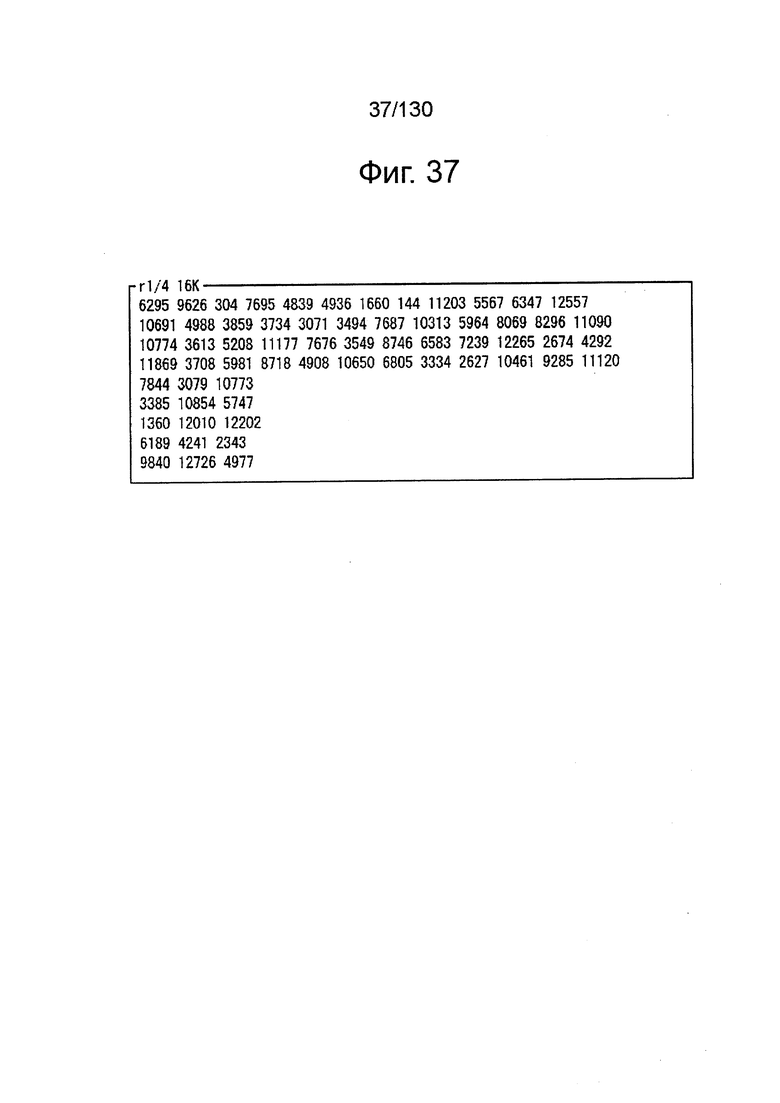

Фиг. 37 является иллюстрацией примера таблицы начальных значений матрицы проверки четности, в которой скорость кодирования равна 1/4 и кодовая длина составляет 16200.

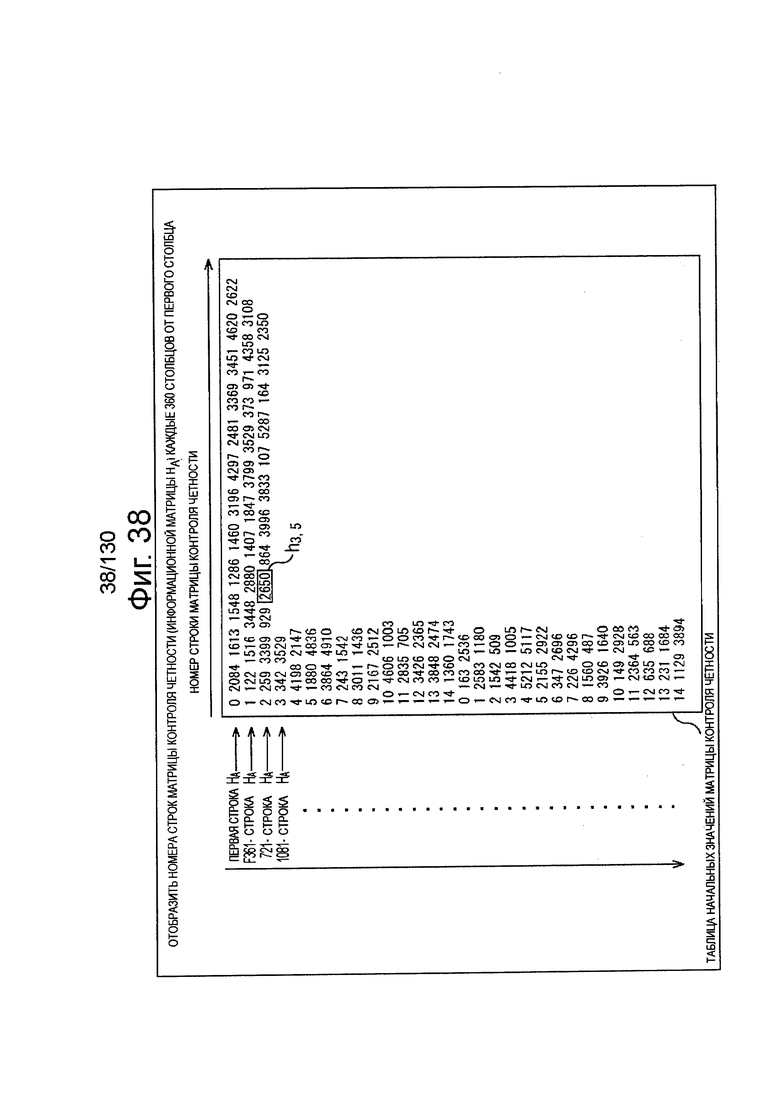

Фиг. 38 является иллюстрацией способа вычисления матрицы H контроля четности таблицы начальных значений матрицы контроля четности.

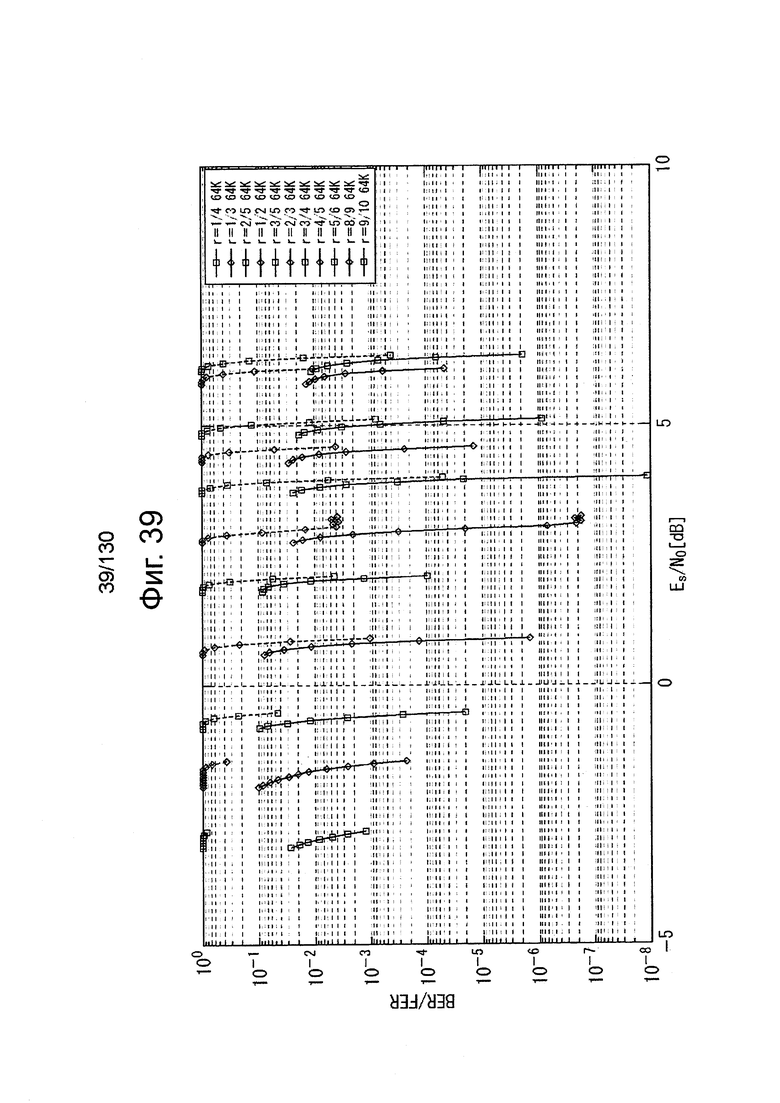

Фиг. 39 является иллюстрацией характеристики BER/FER LDPC-кода, чья кодовая длина определяется в стандарте DVB-S.2 и равна 64800 бит.

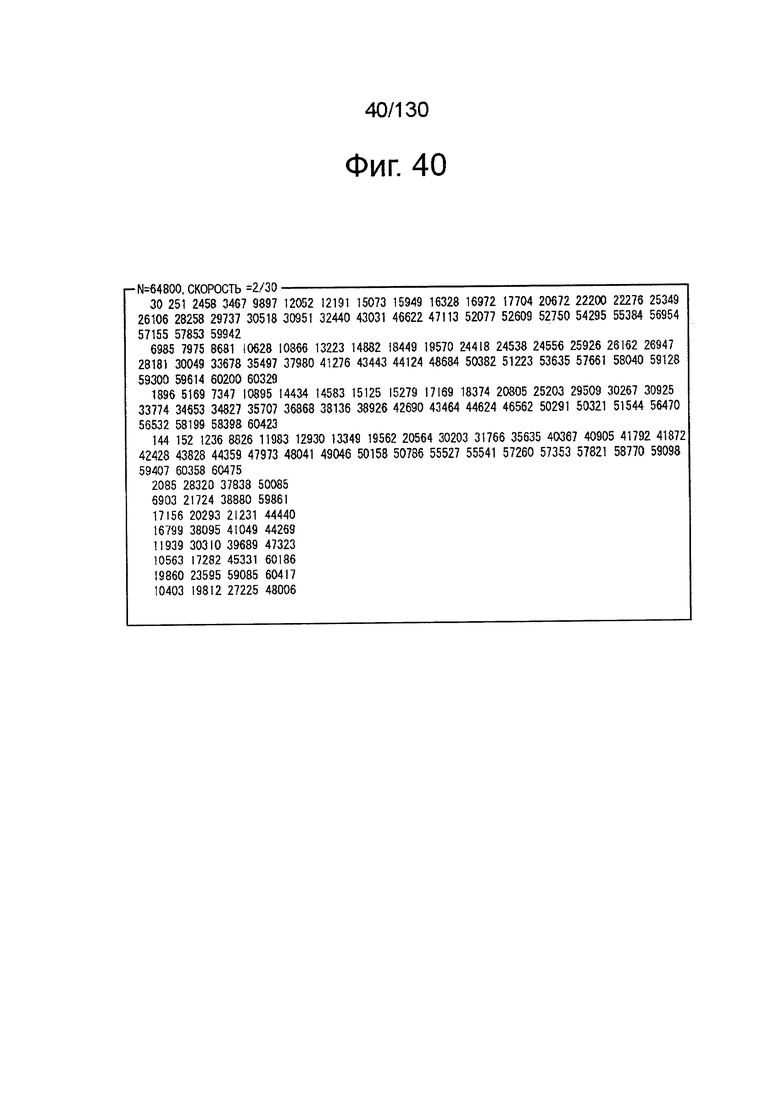

Фиг. 40 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 2/30 и кодовая длина равна 64800.

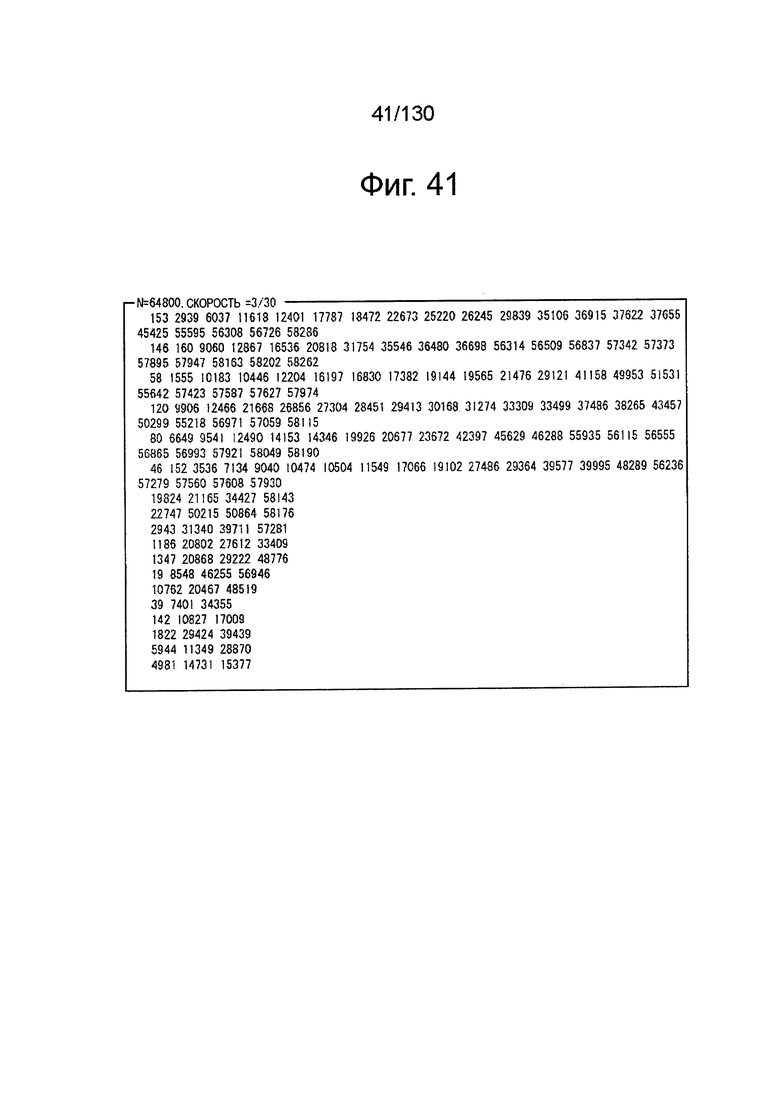

Фиг. 41 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 3/30 и кодовая длина равна 64800.

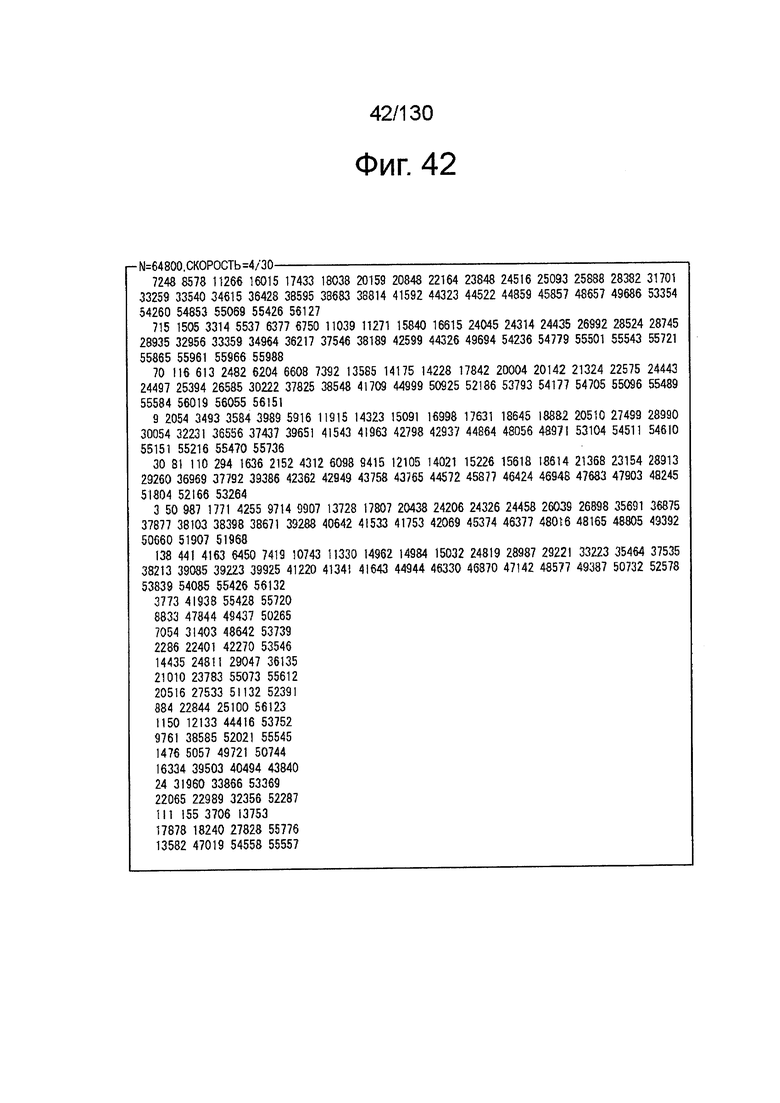

Фиг. 42 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 4/30 и кодовая длина составляет 64800.

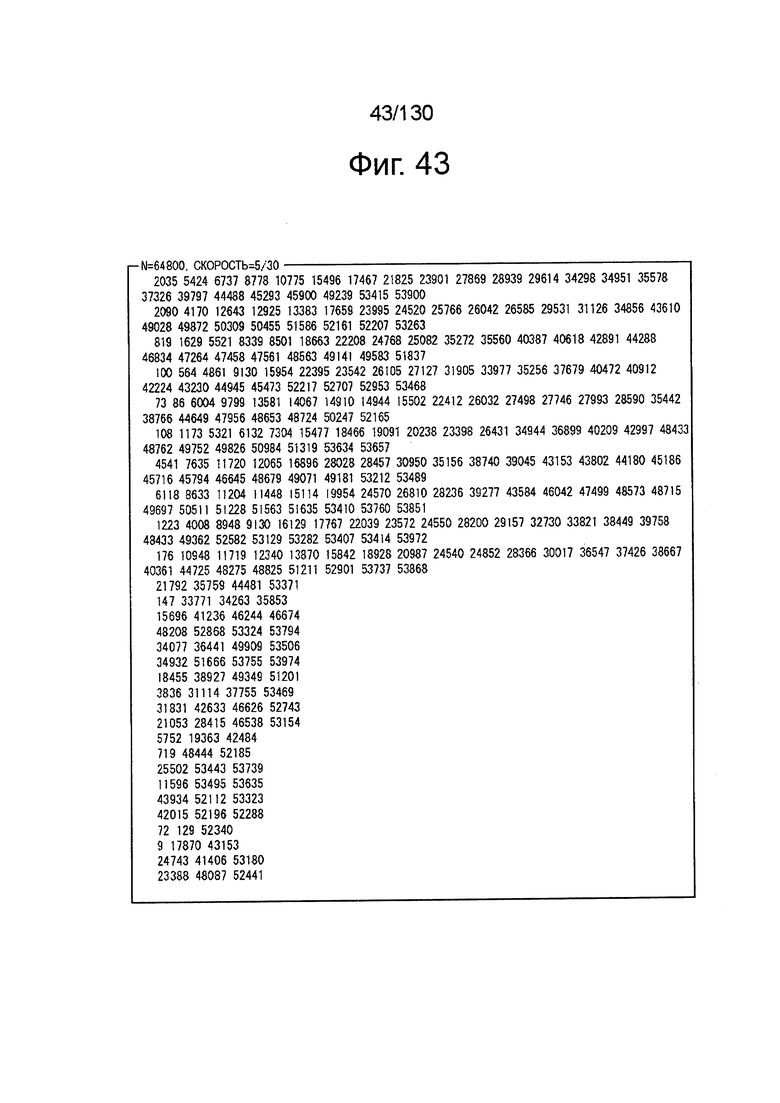

Фиг. 43 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 5/30 и кодовая длина составляет 64800.

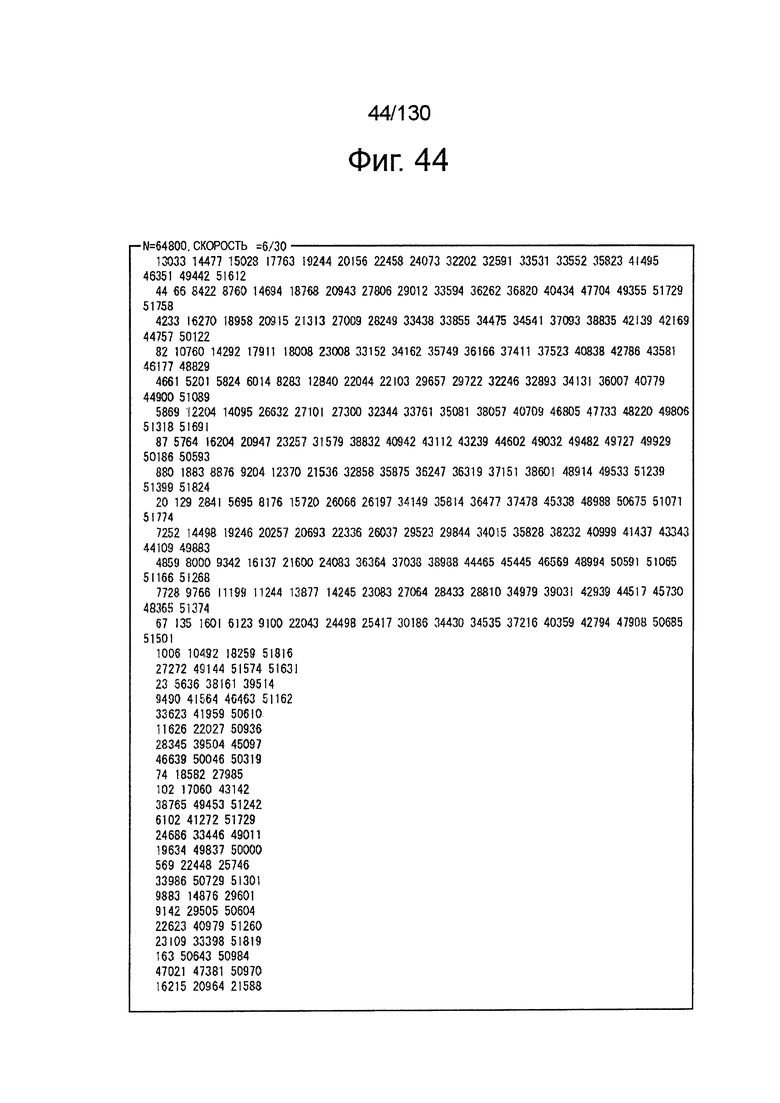

Фиг. 44 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 6/30 и кодовая длина составляет 64800.

Фиг. 45 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 7/30 и кодовая длина составляет 64800.

Фиг. 46 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 8/30 и кодовая длина составляет 64800.

Фиг. 47 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 8/30 и кодовая длина составляет 64800.

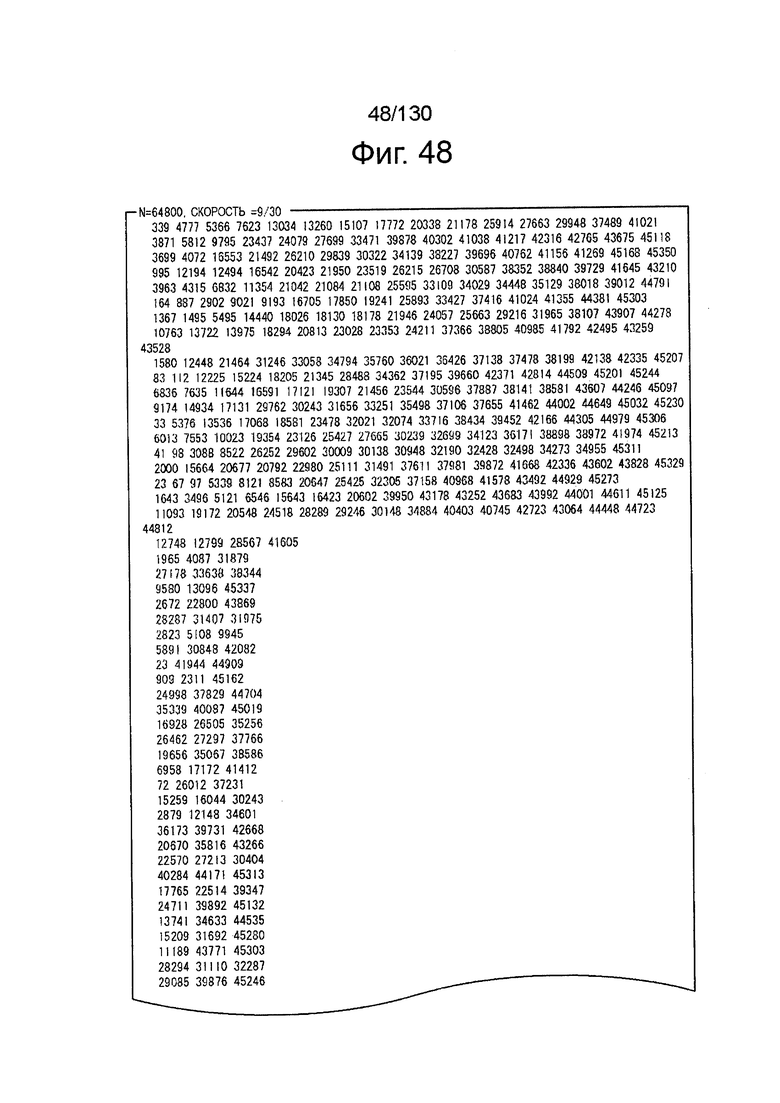

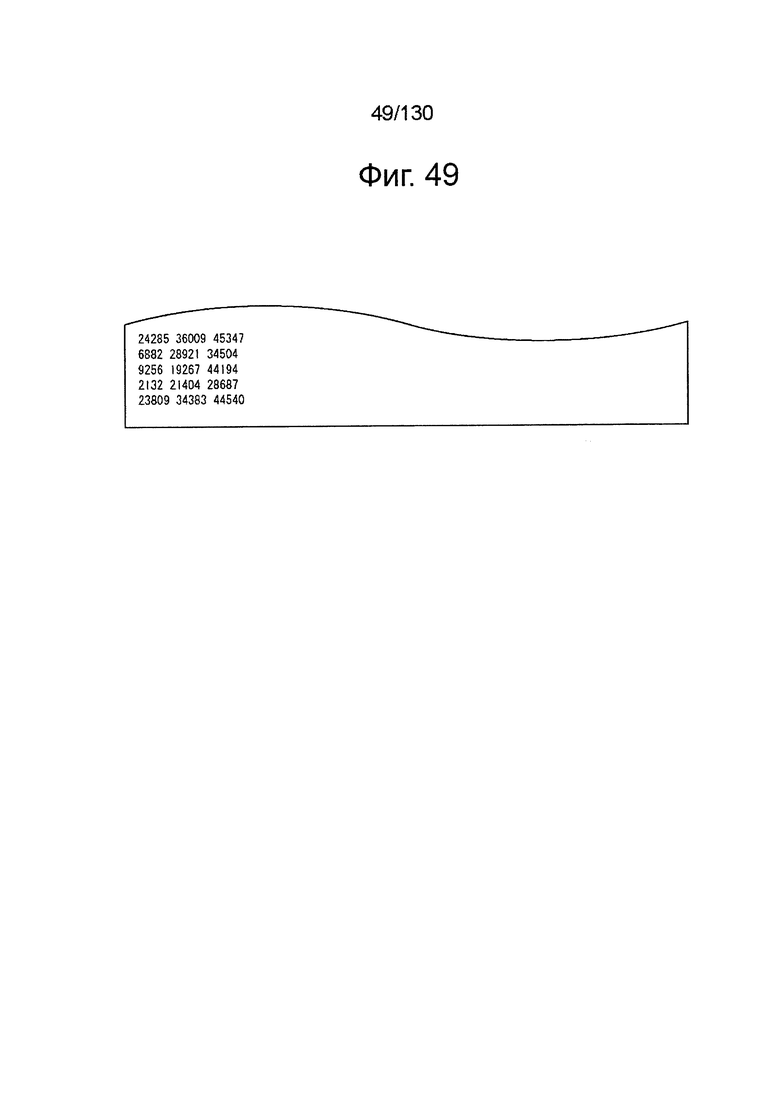

Фиг. 48 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 9/30 и кодовая длина составляет 64800.

Фиг. 49 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 9/30 и кодовая длина составляет 64800.

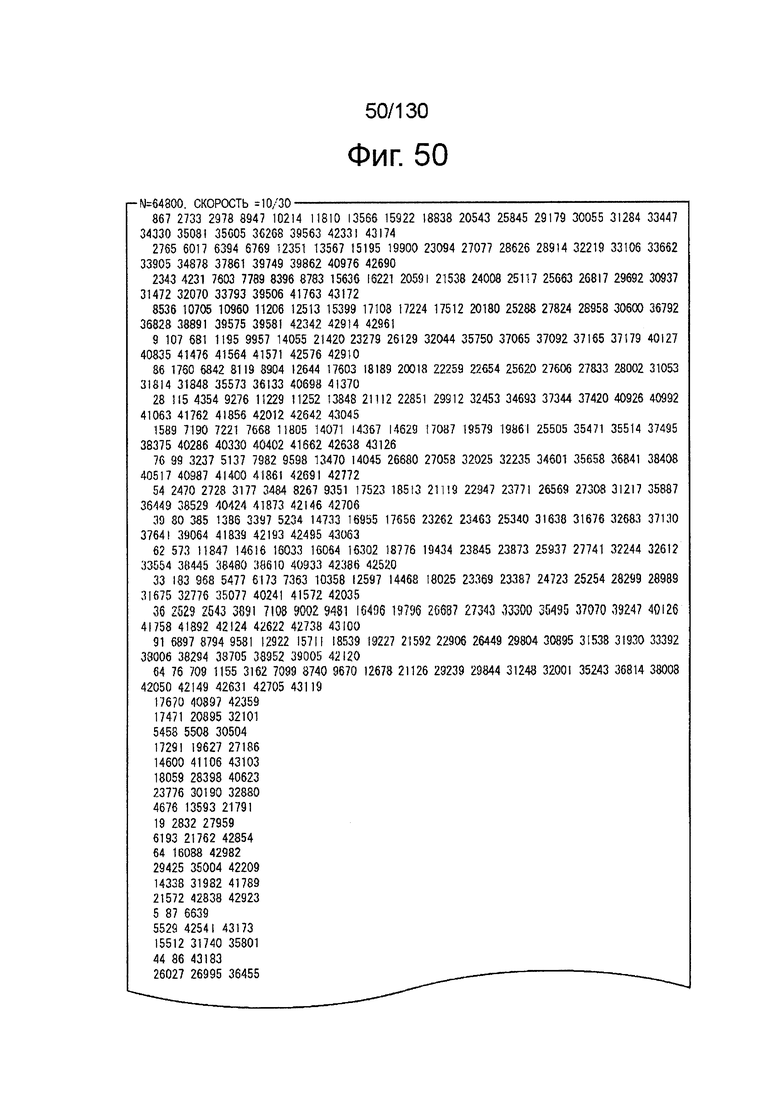

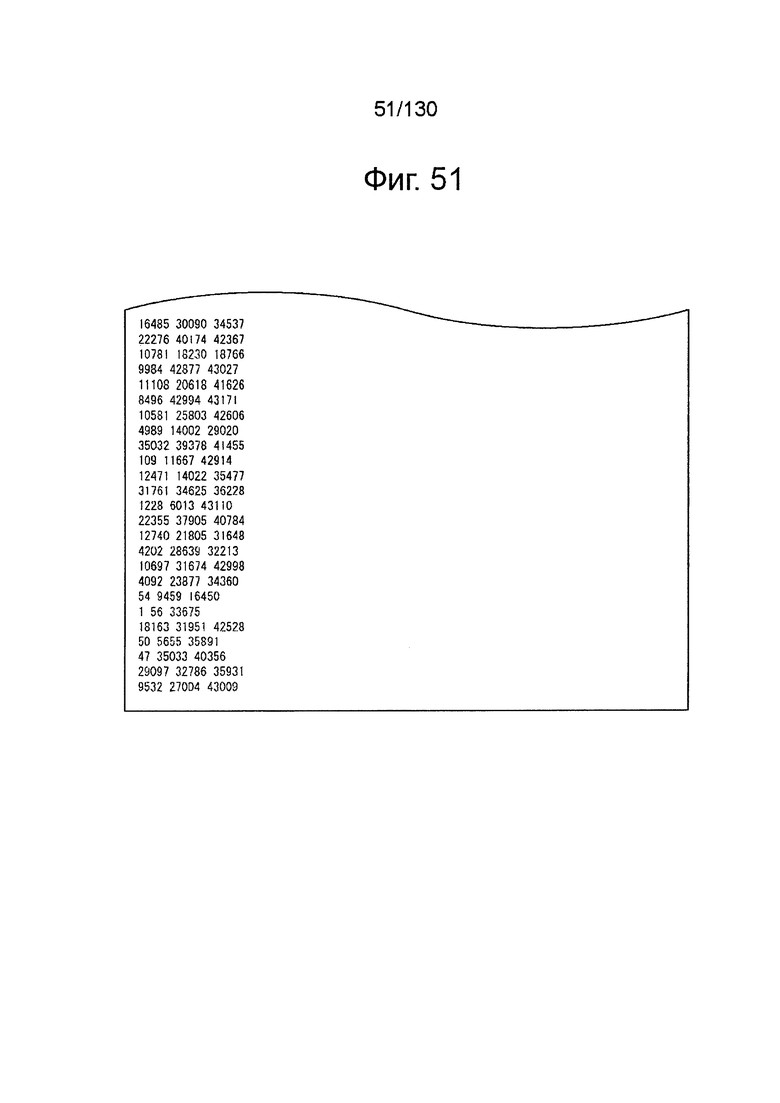

Фит.50 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 10/30 и кодовая длина составляет 64800.

Фиг. 51 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 10/30 и кодовая длина составляет 64800.

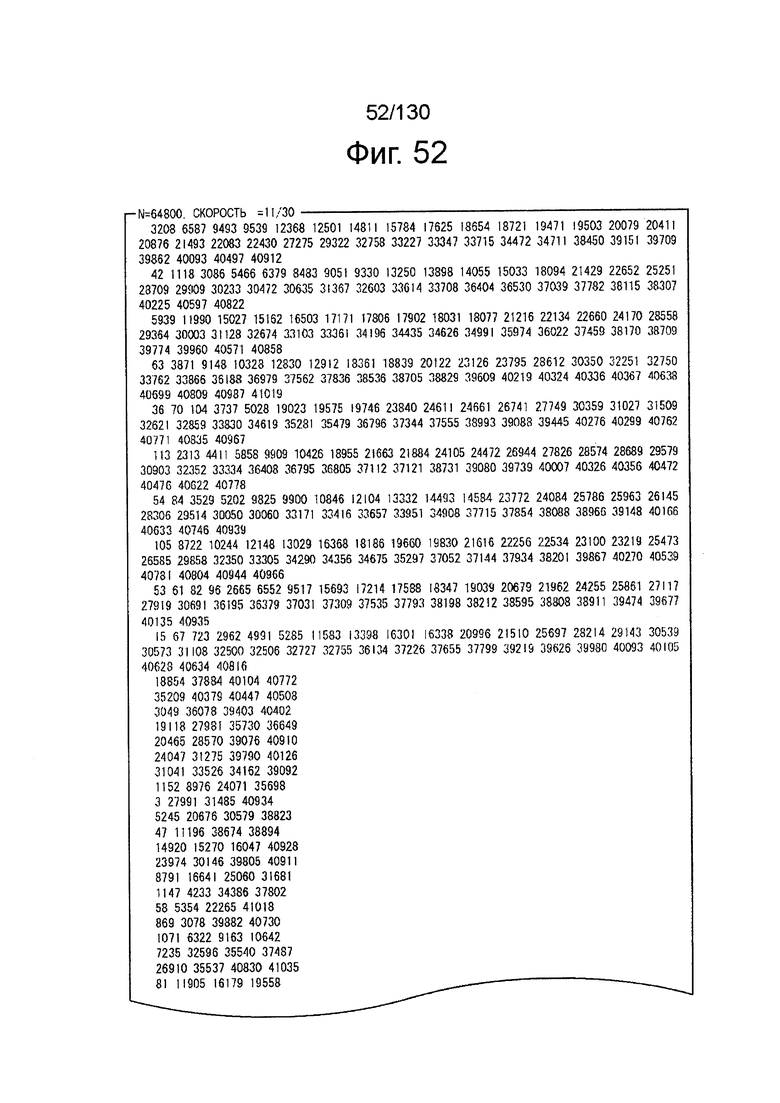

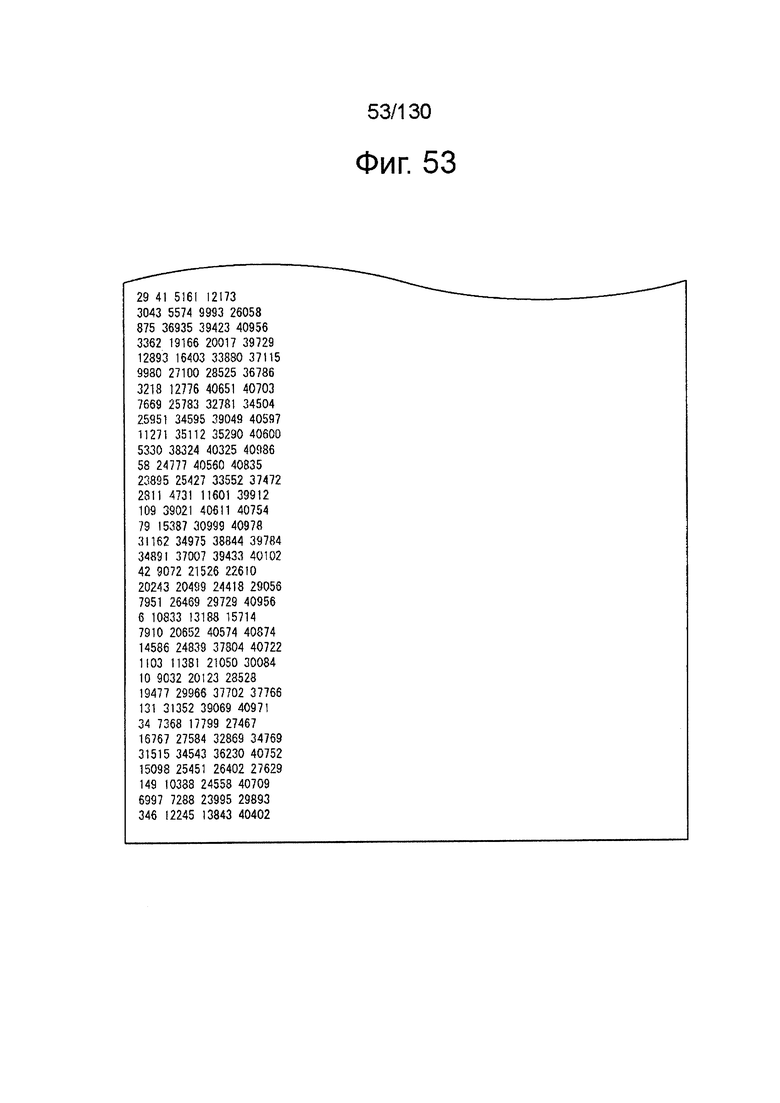

Фиг. 52 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 11/30 и кодовая длина составляет 64800.

Фиг. 53 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 11/30 и кодовая длина составляет 64800.

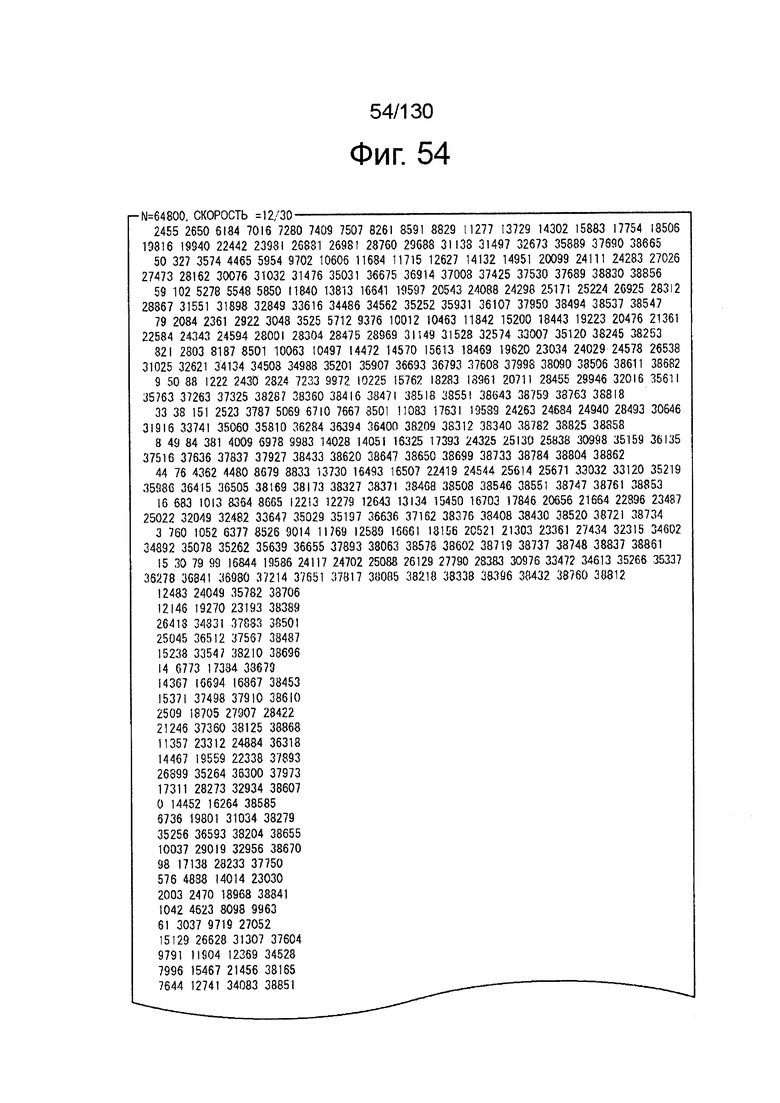

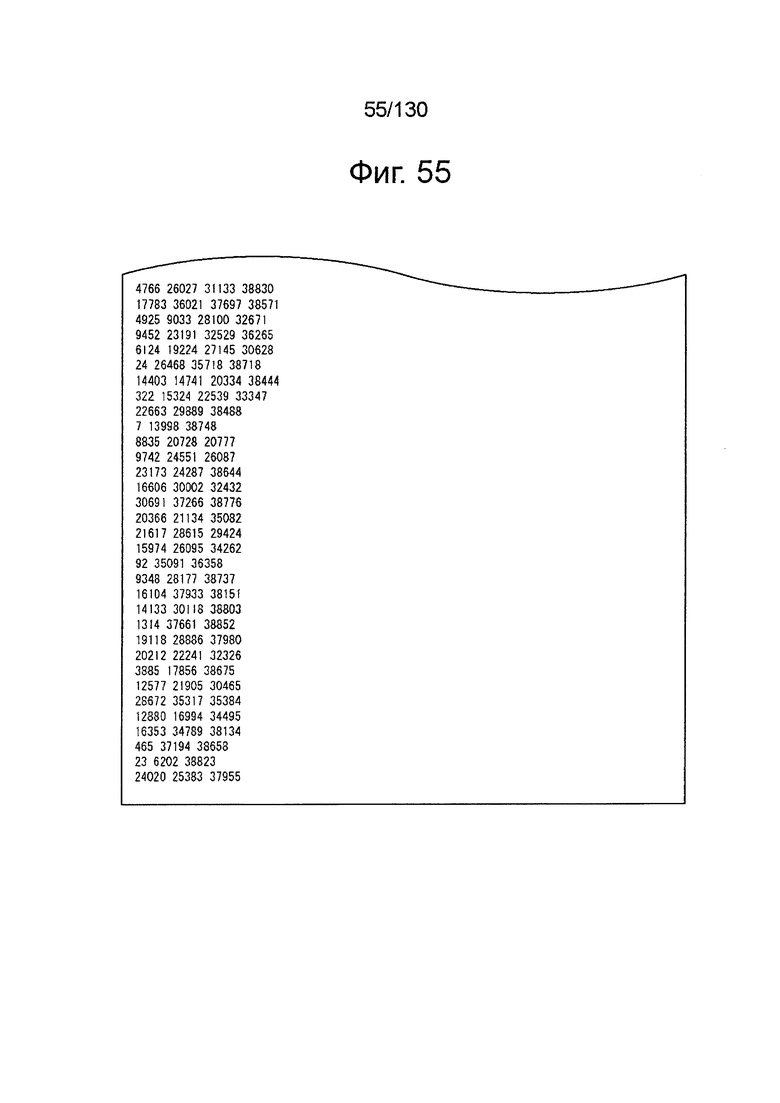

Фиг. 54 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 12/30 и кодовая длина составляет 64800.

Фиг. 55 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 12/30 и кодовая длина составляет 64800.

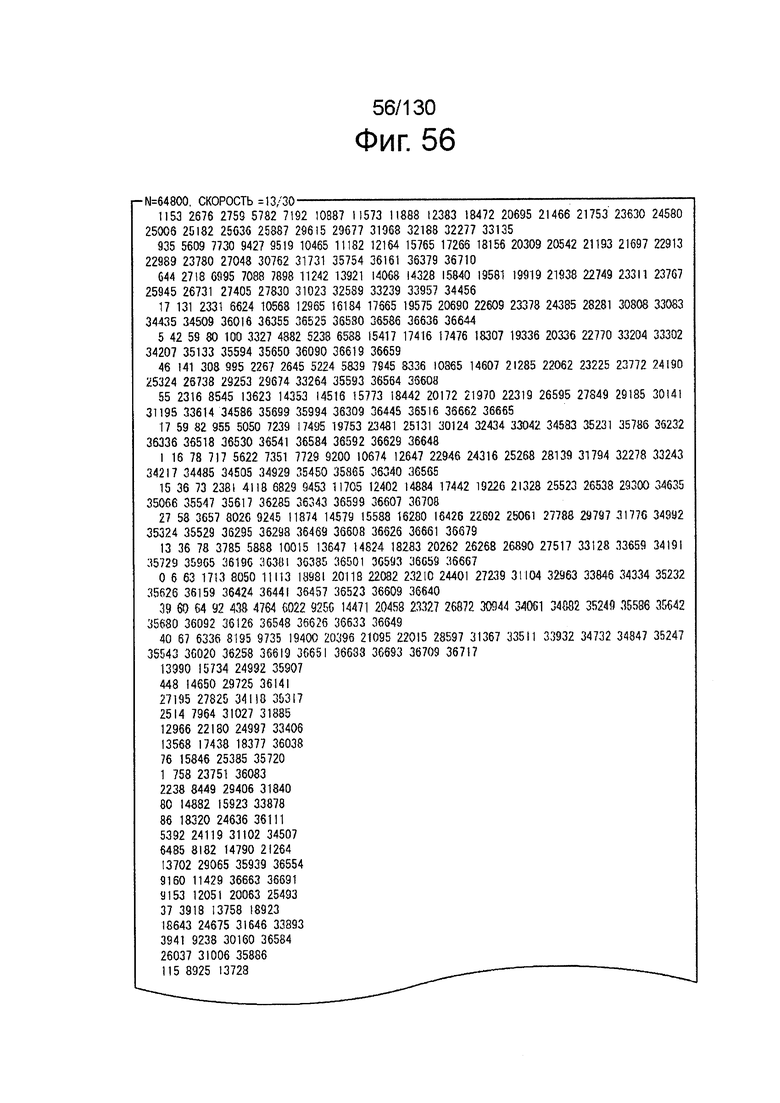

Фиг. 56 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 13/30 и кодовая длина составляет 64800.

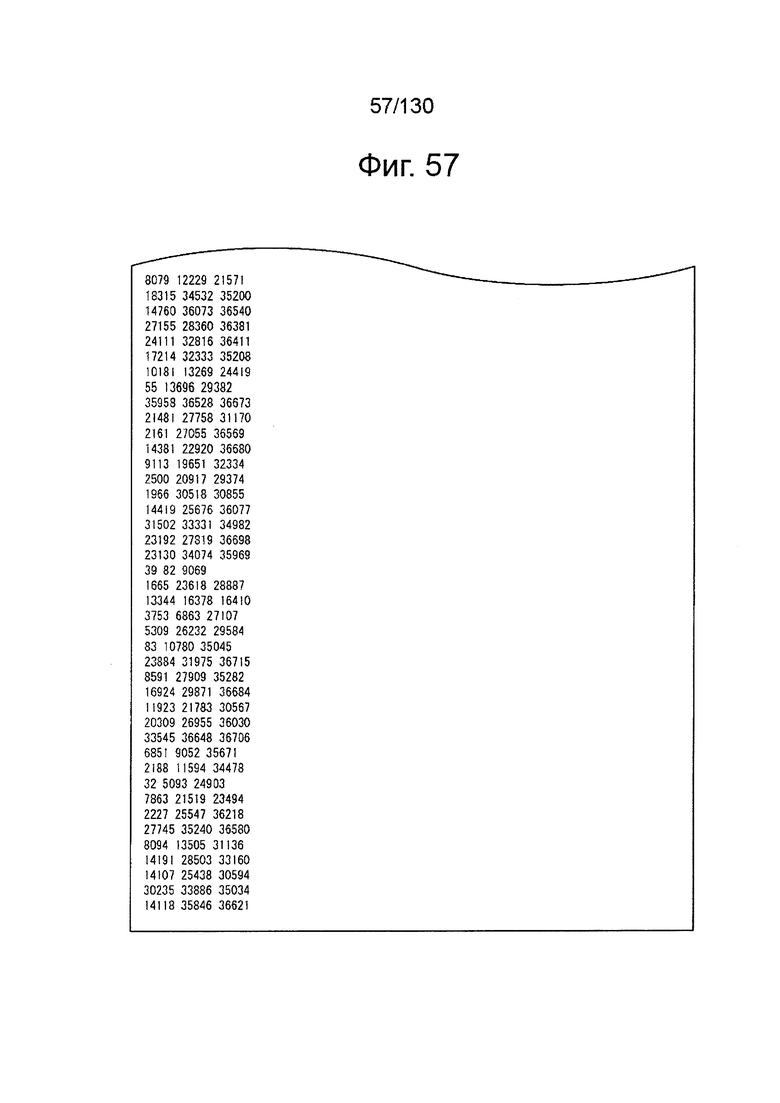

Фиг. 57 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 13/30 и кодовая длина составляет 64800.

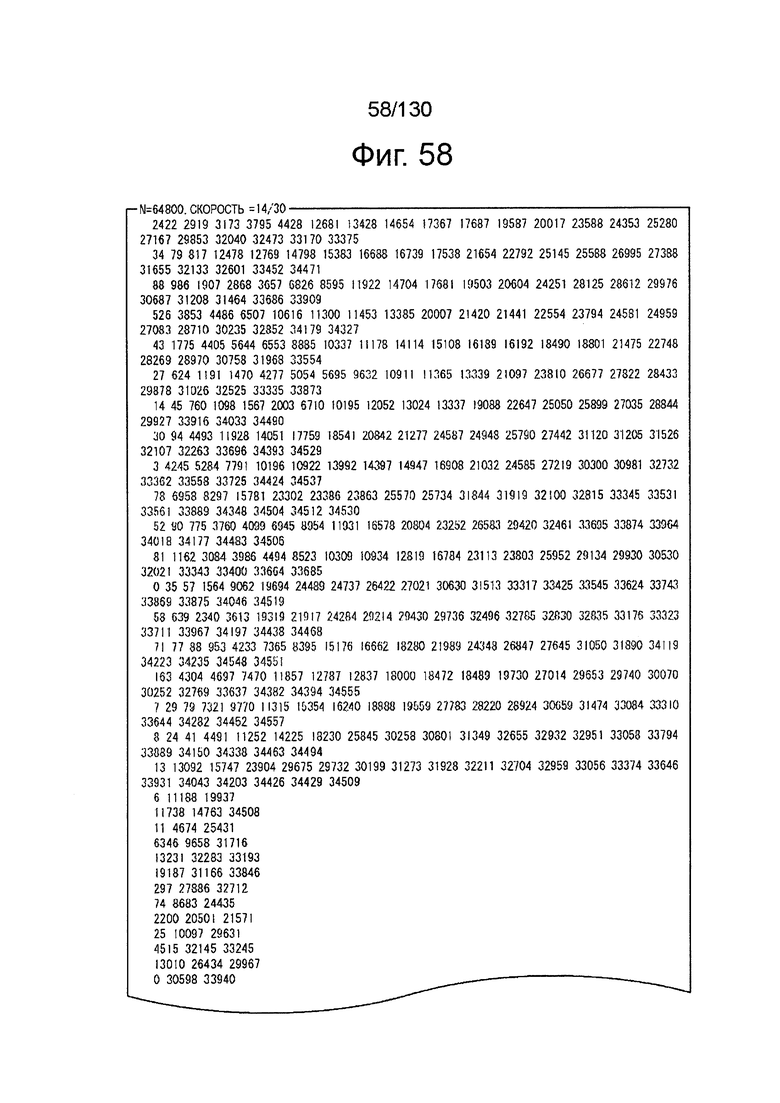

Фиг. 58 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 14/30 и кодовая длина составляет 64800.

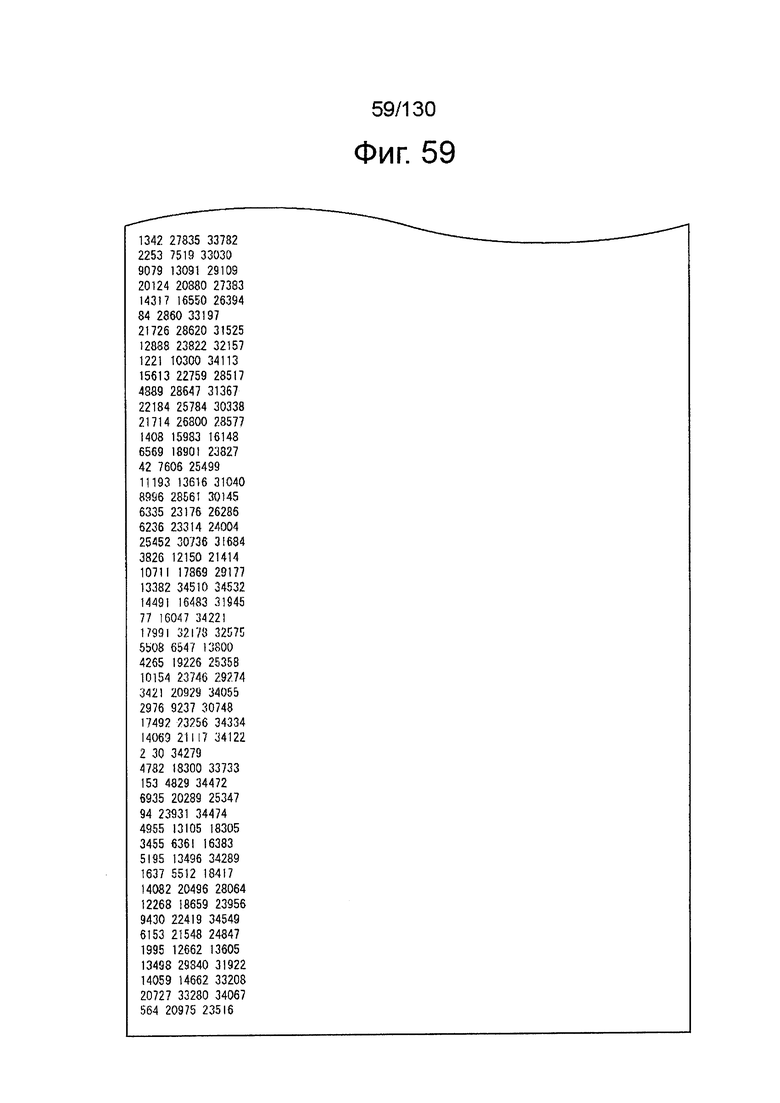

Фиг. 59 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 14/30 и кодовая длина составляет 64800.

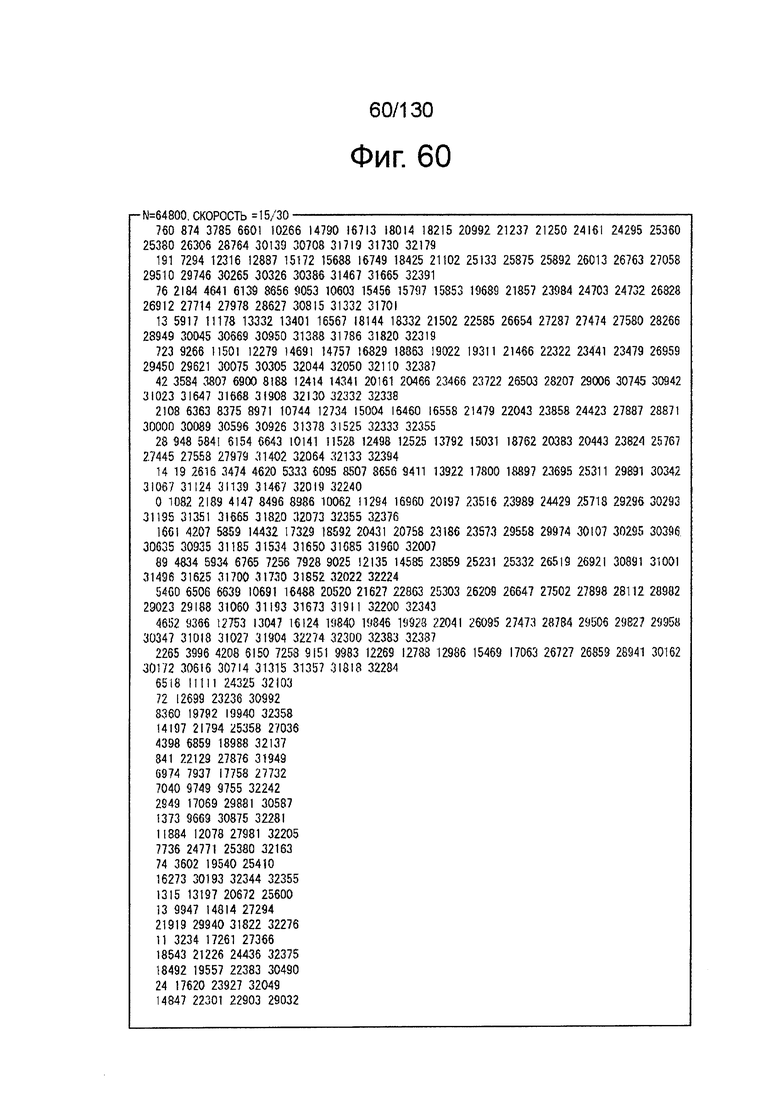

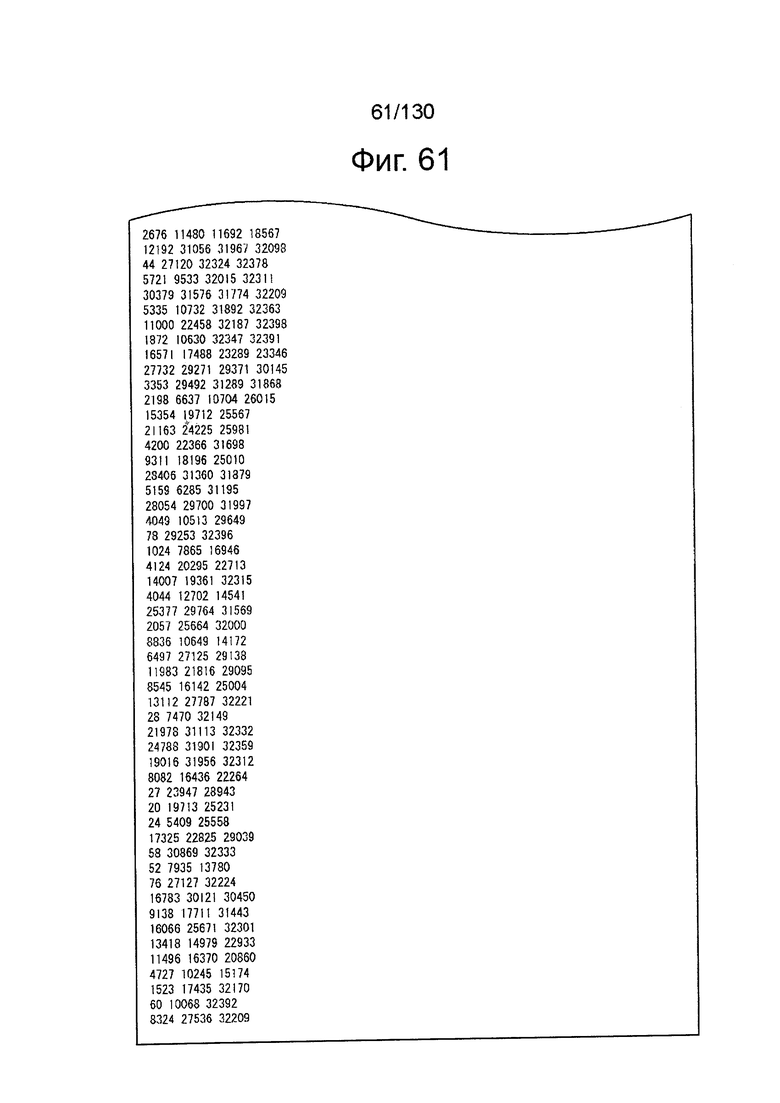

Фиг. 60 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 15/30 и кодовая длина составляет 64800.

Фиг. 61 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 15/30 и кодовая длина составляет 64800.

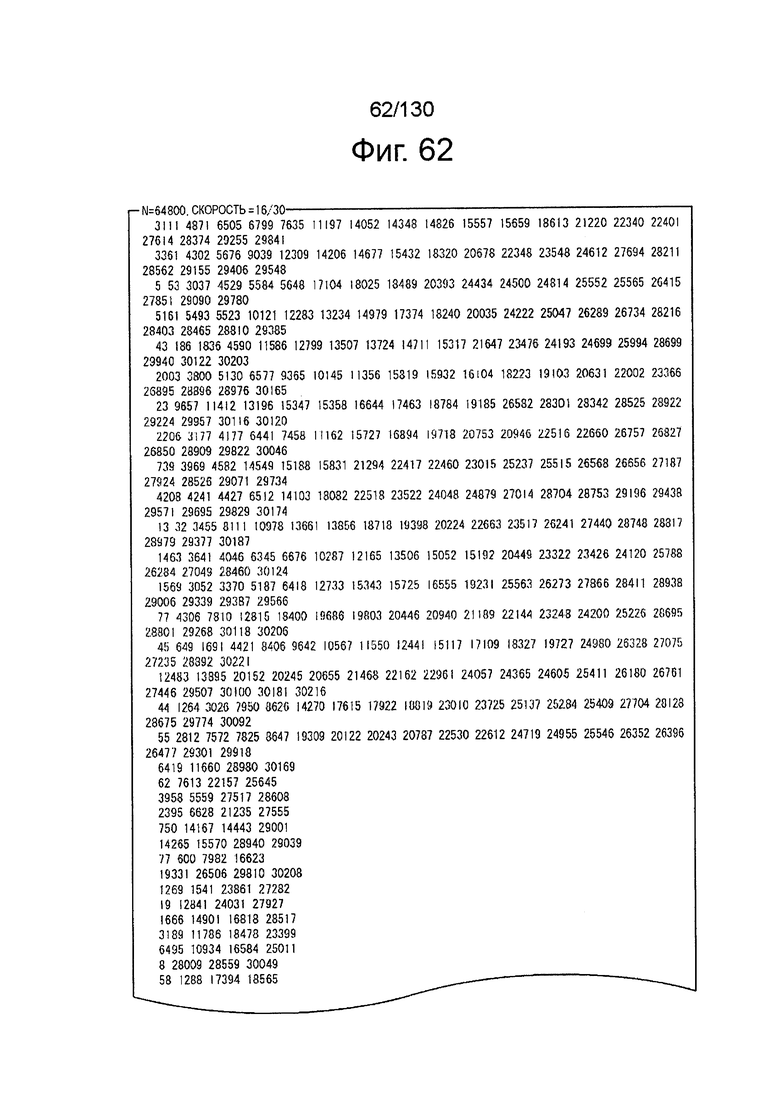

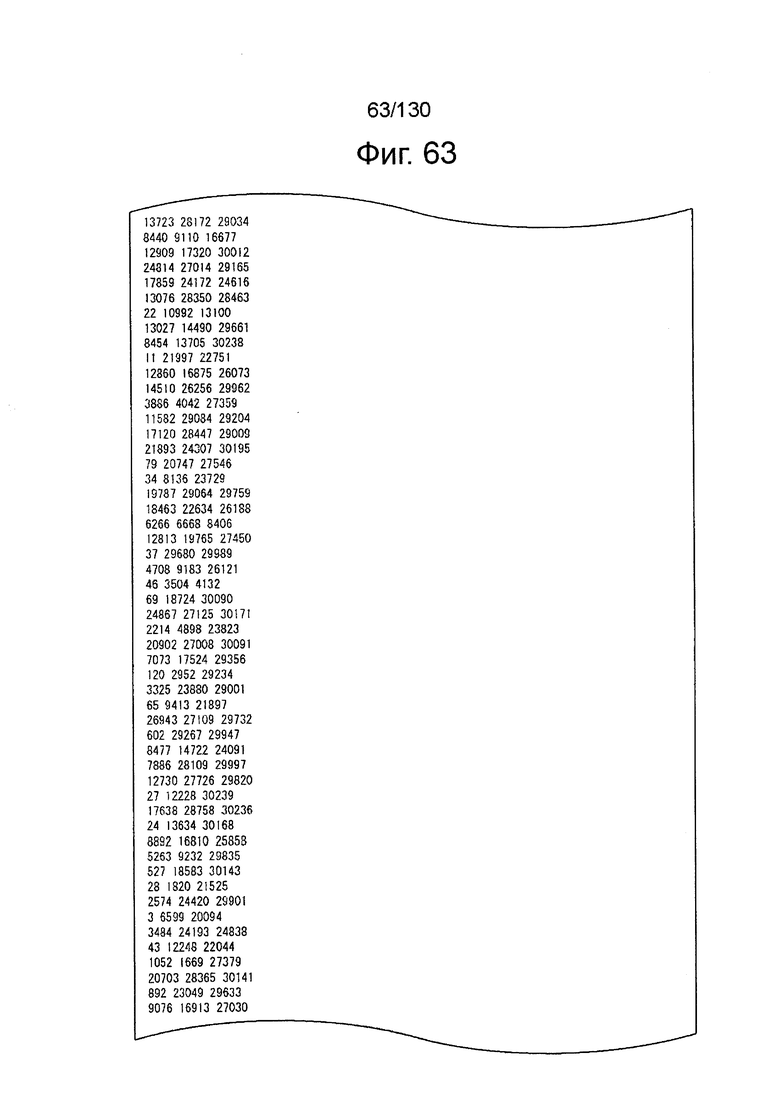

Фиг. 62 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 16/30 и кодовая длина составляет 64800.

Фиг. 63 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 16/30 и кодовая длина составляет 64800.

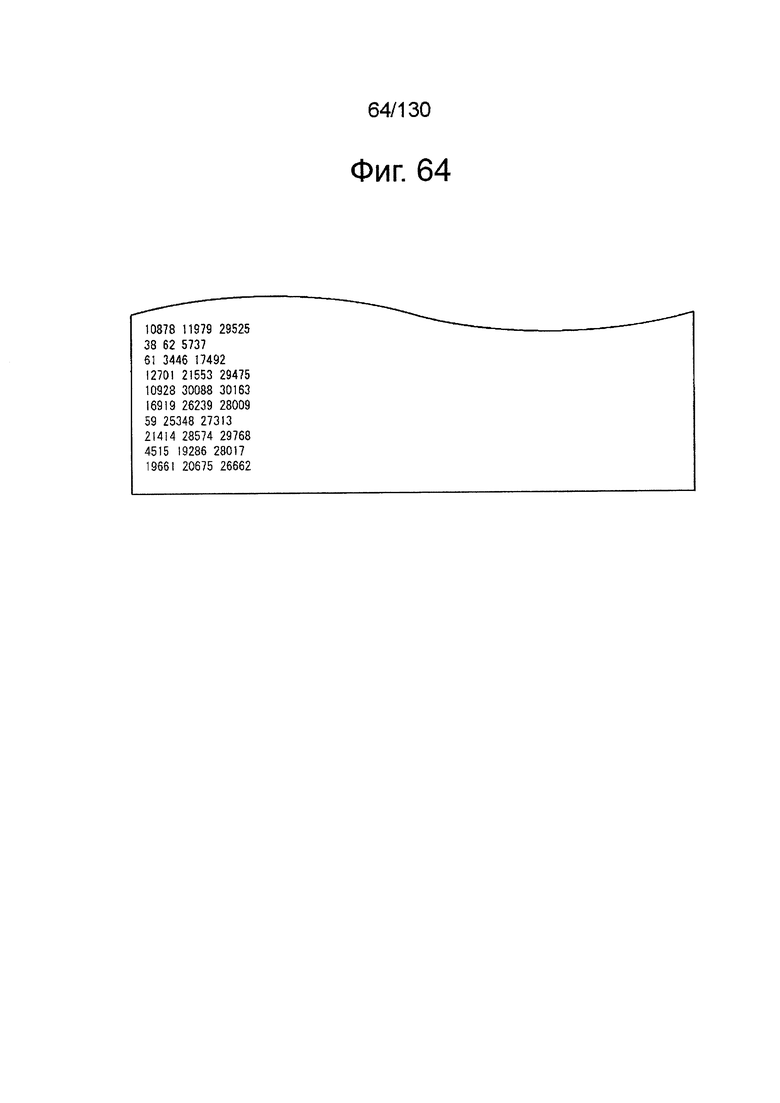

Фиг. 64 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 16/30 и кодовая длина составляет 64800.

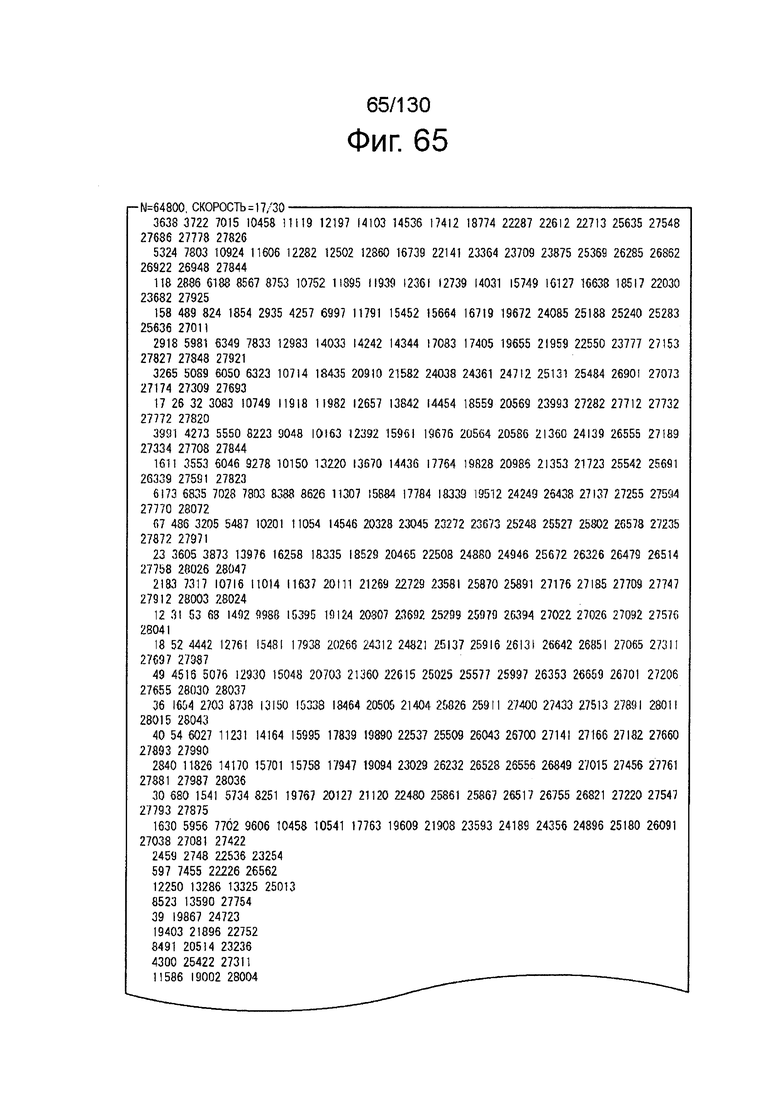

Фиг. 65 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 17/30 и кодовая длина составляет 64800.

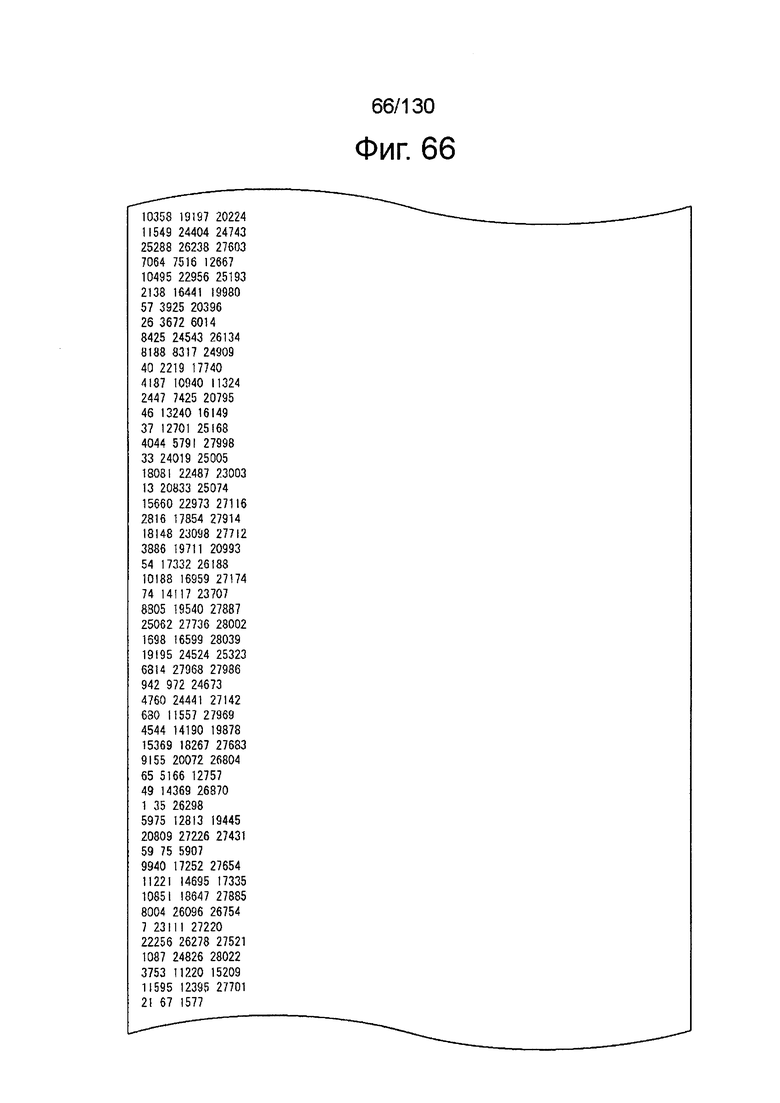

Фиг. 66 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 17/30 и кодовая длина составляет 64800.

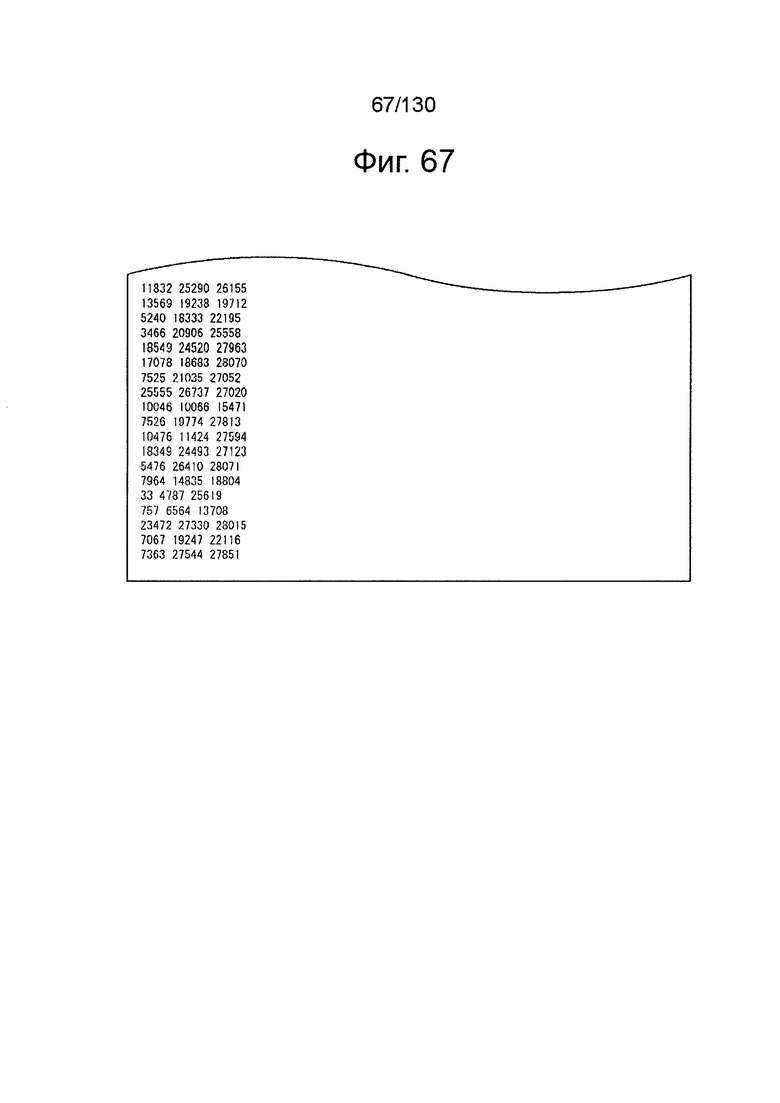

Фиг. 67 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 17/30 и кодовая длина составляет 64800.

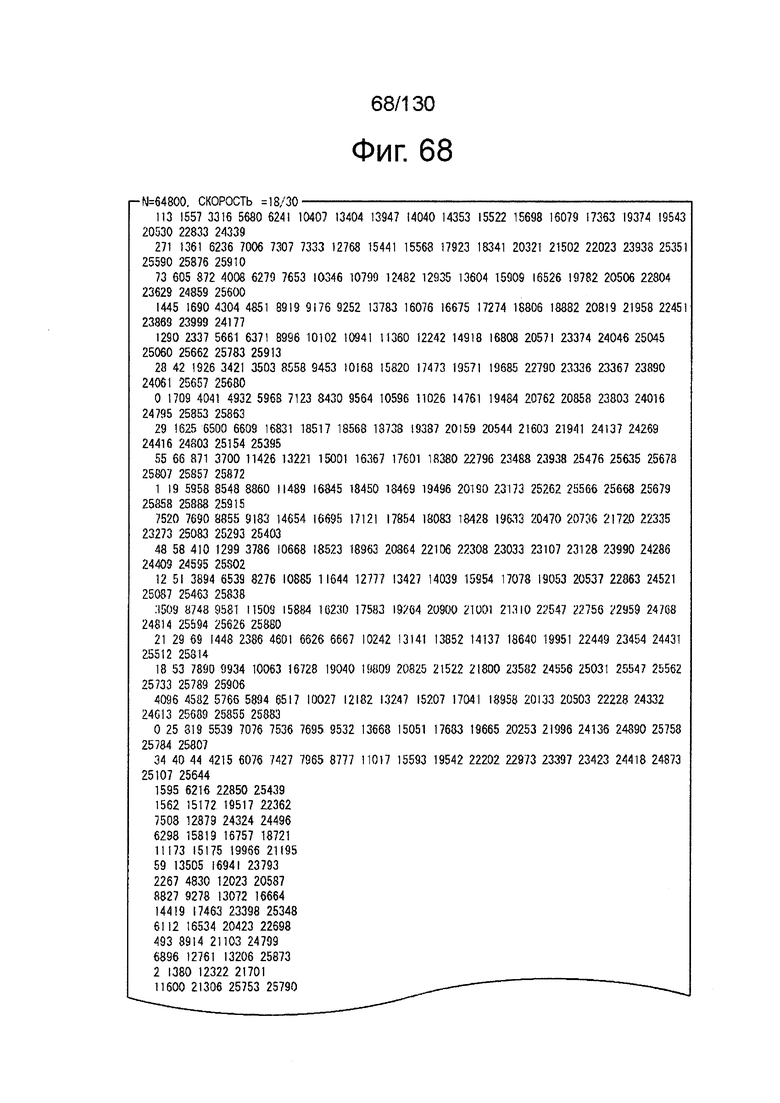

Фиг. 68 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 18/30 и кодовая длина составляет 64800.

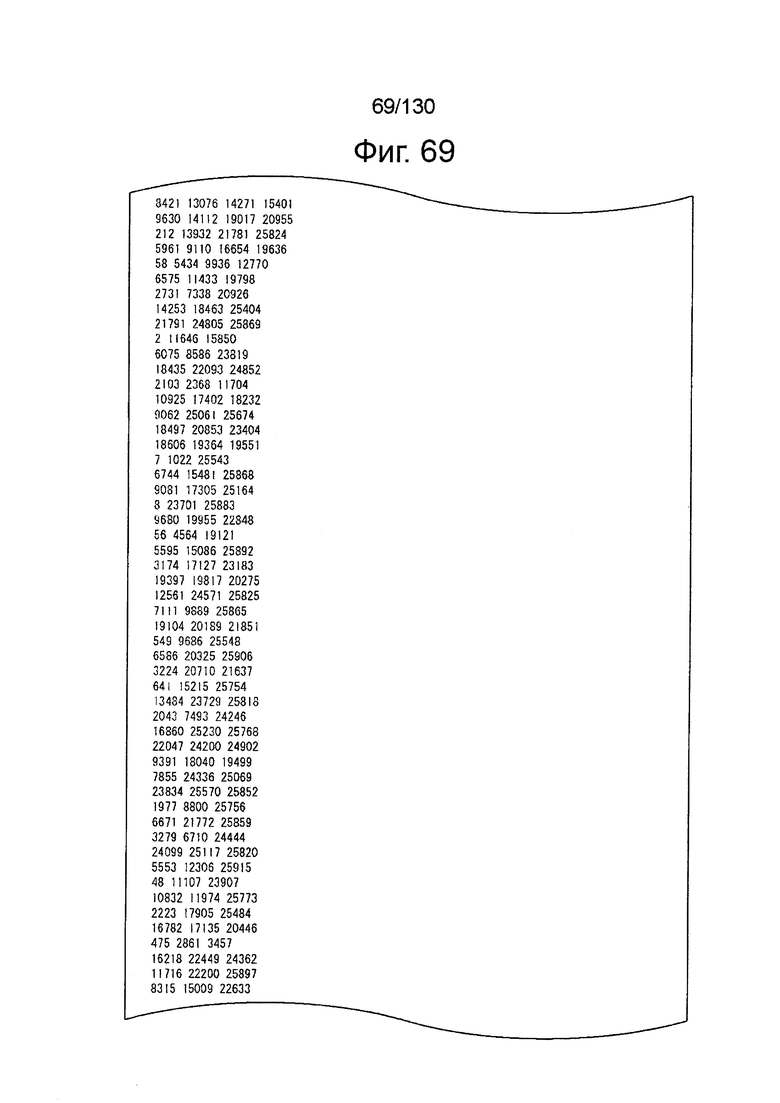

Фиг. 69 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 18/30 и кодовая длина составляет 64800.

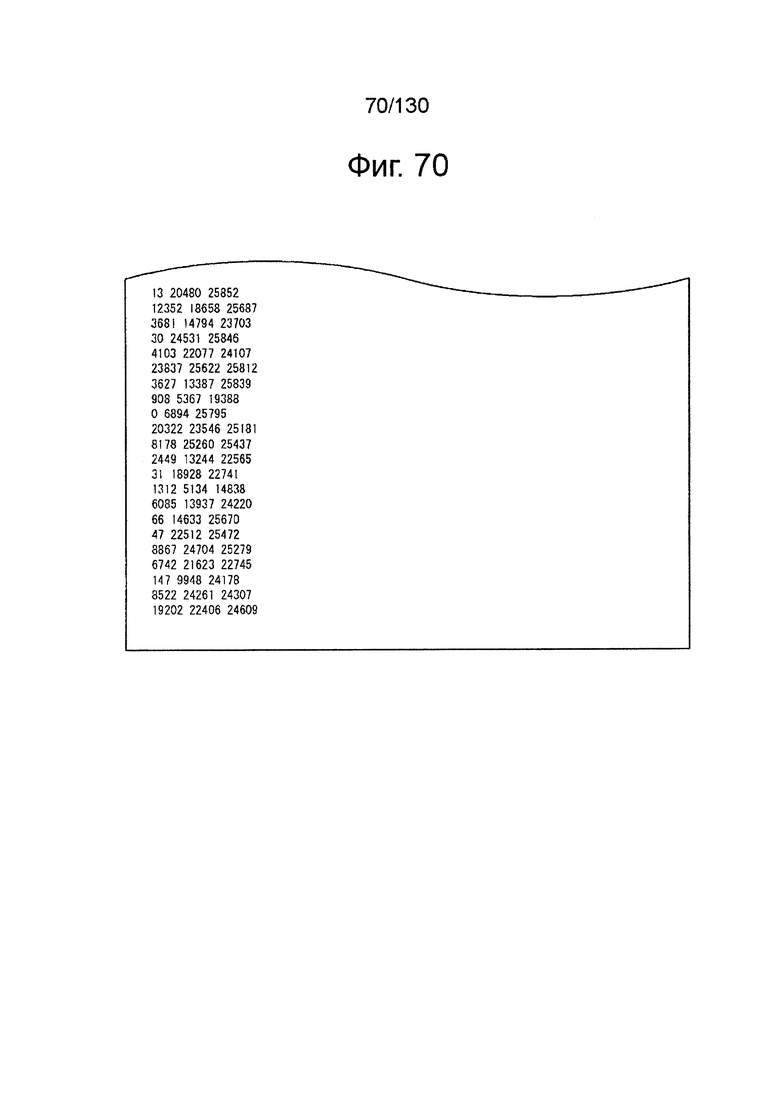

Фиг. 70 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 18/30 и кодовая длина составляет 64800.

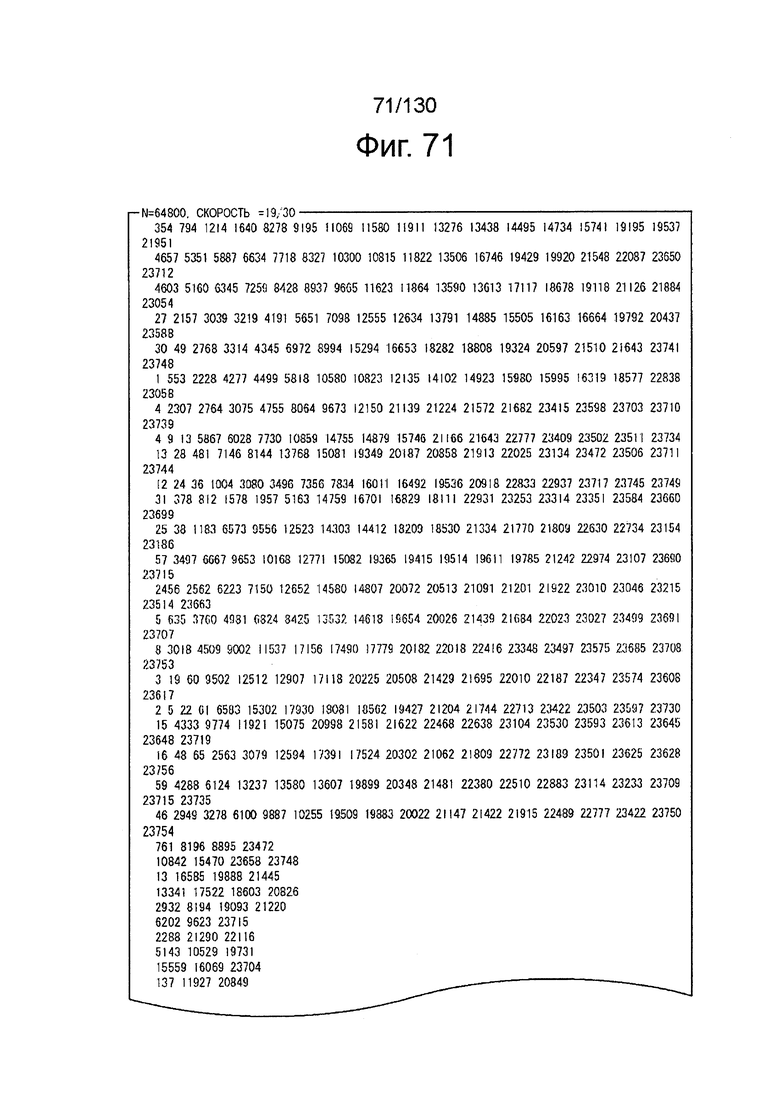

Фиг. 71 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 19/30 и кодовая длина составляет 64800.

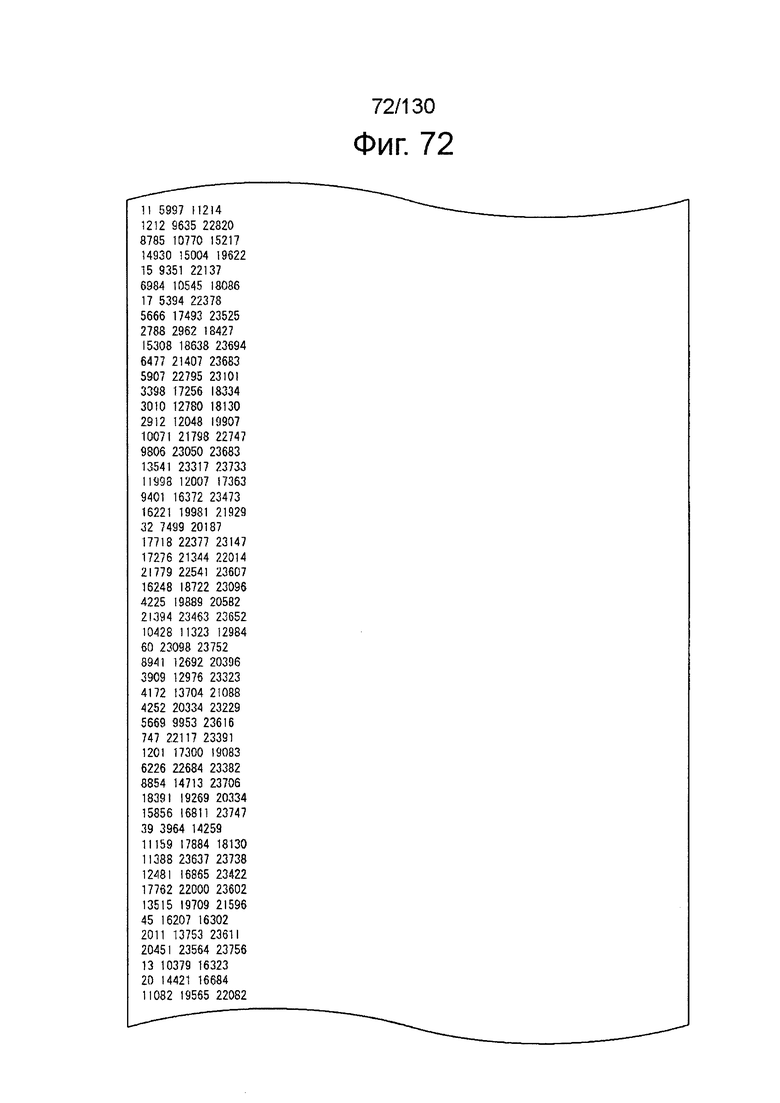

Фиг. 72 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 19/30 и кодовая длина составляет 64800.

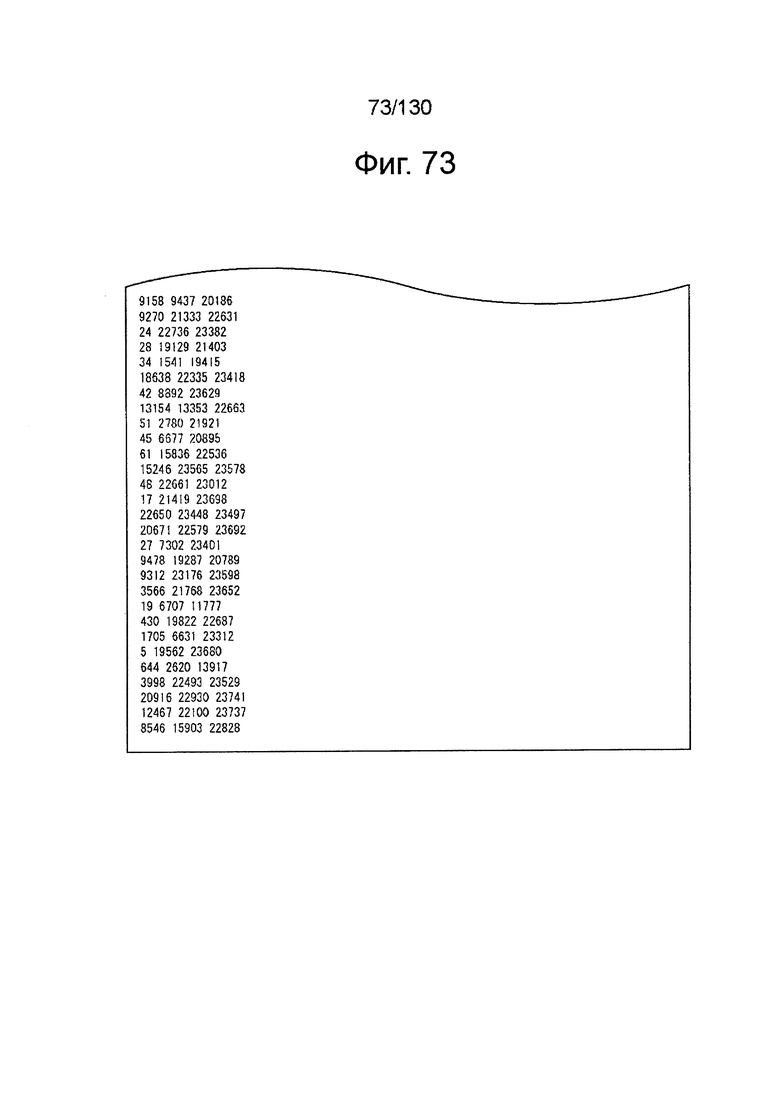

Фиг.73 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 19/30 и кодовая длина составляет 64800.

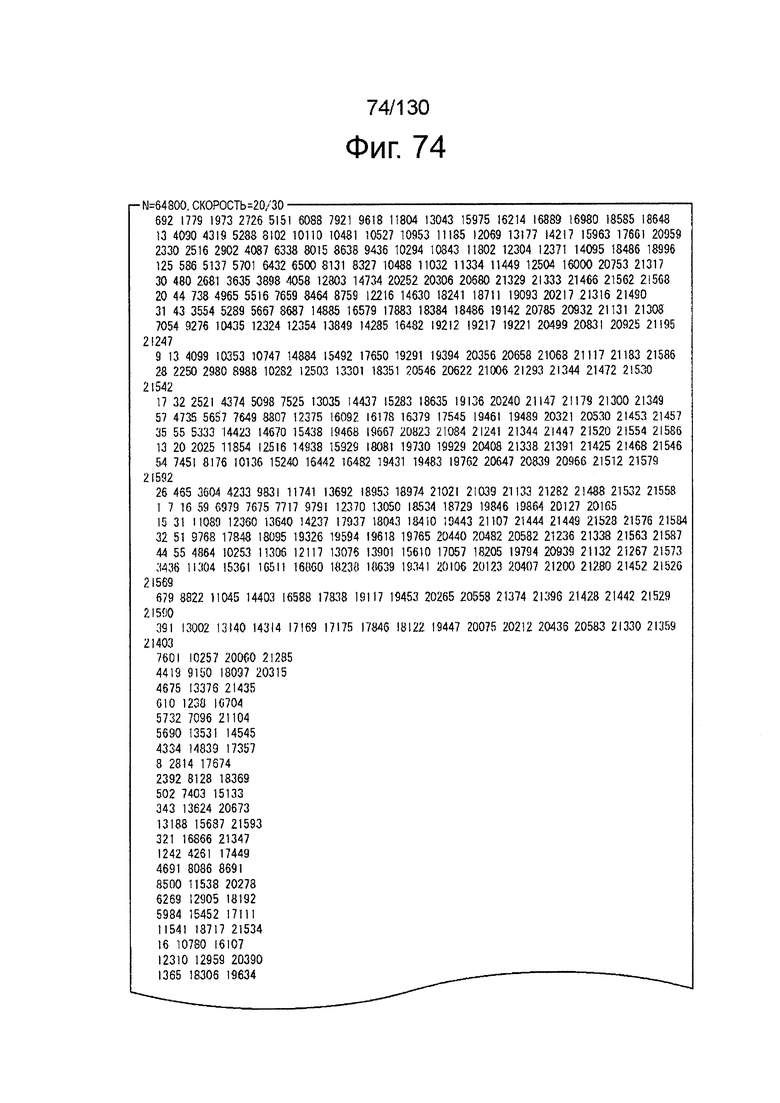

Фиг. 74 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 20/30 и кодовая длина составляет 64800.

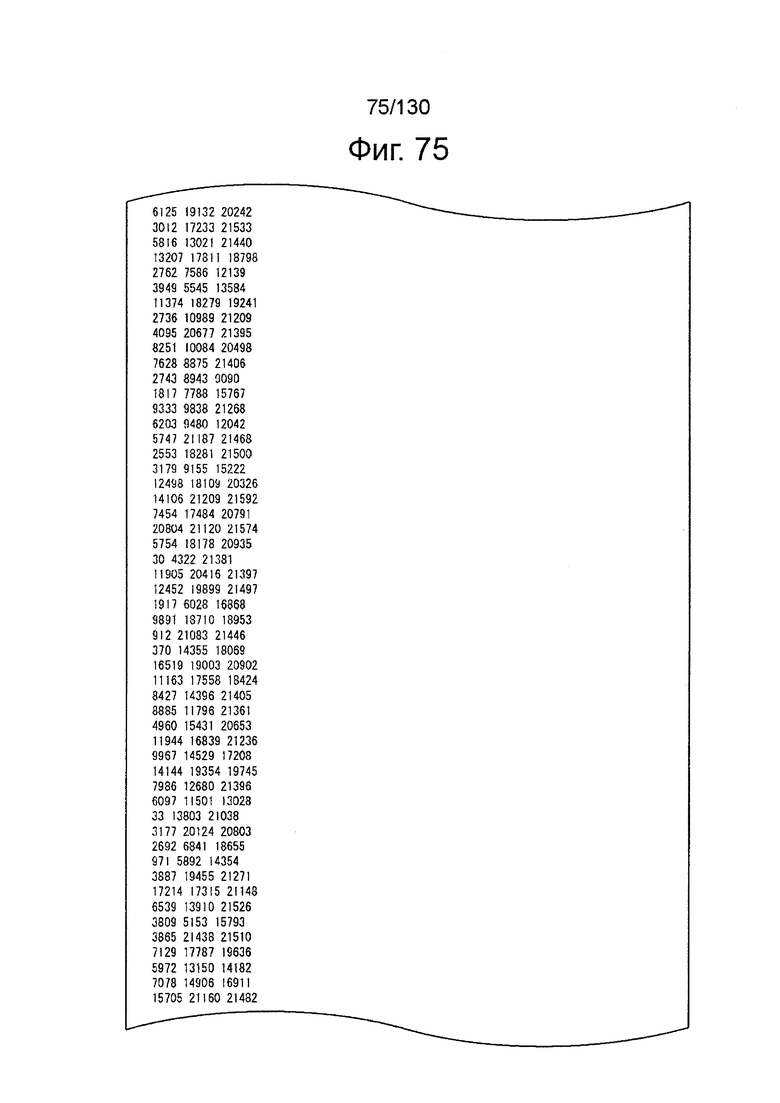

Фиг. 75 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 20/30 и кодовая длина составляет 64800.

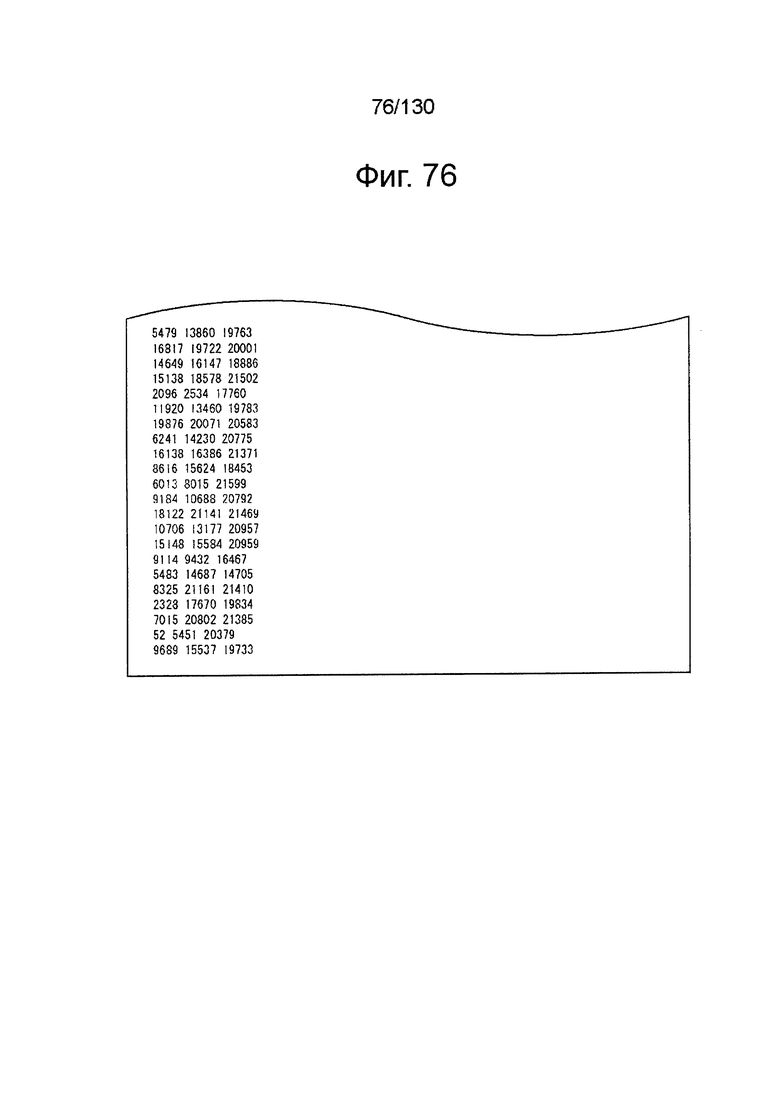

Фиг. 76 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 20/30 и кодовая длина составляет 64800.

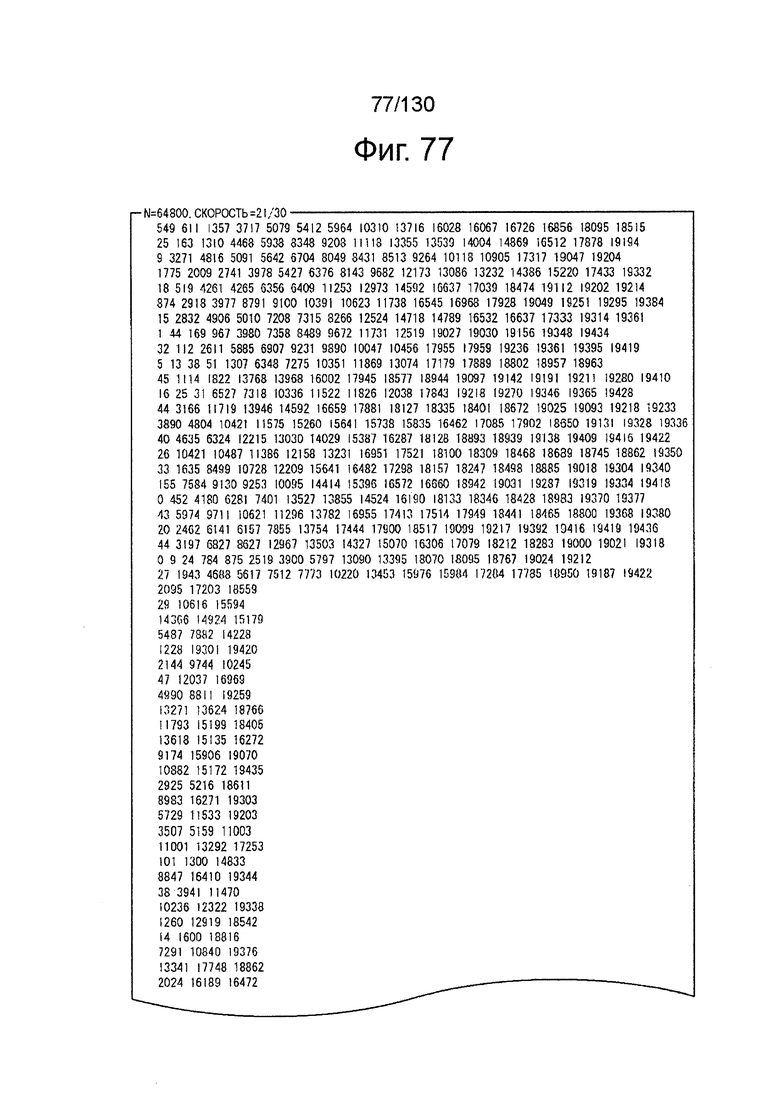

Фиг. 77 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 21/30 и кодовая длина составляет 64800.

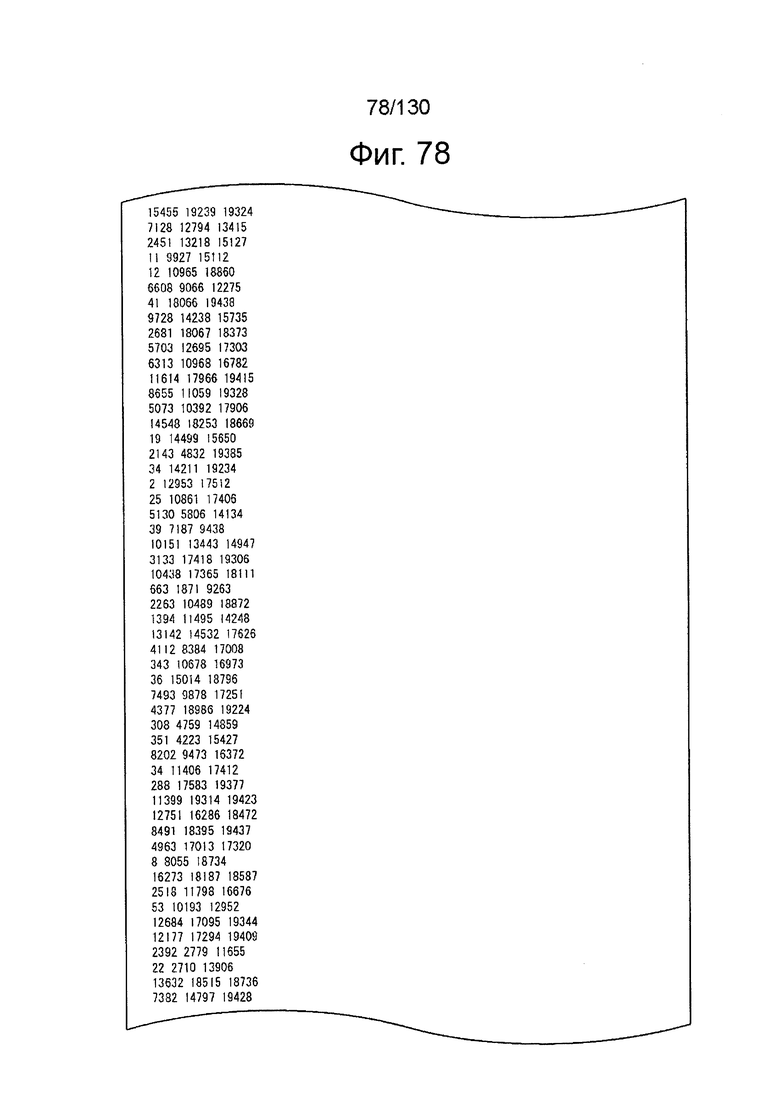

Фиг. 78 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 21/30 и кодовая длина составляет 64800.

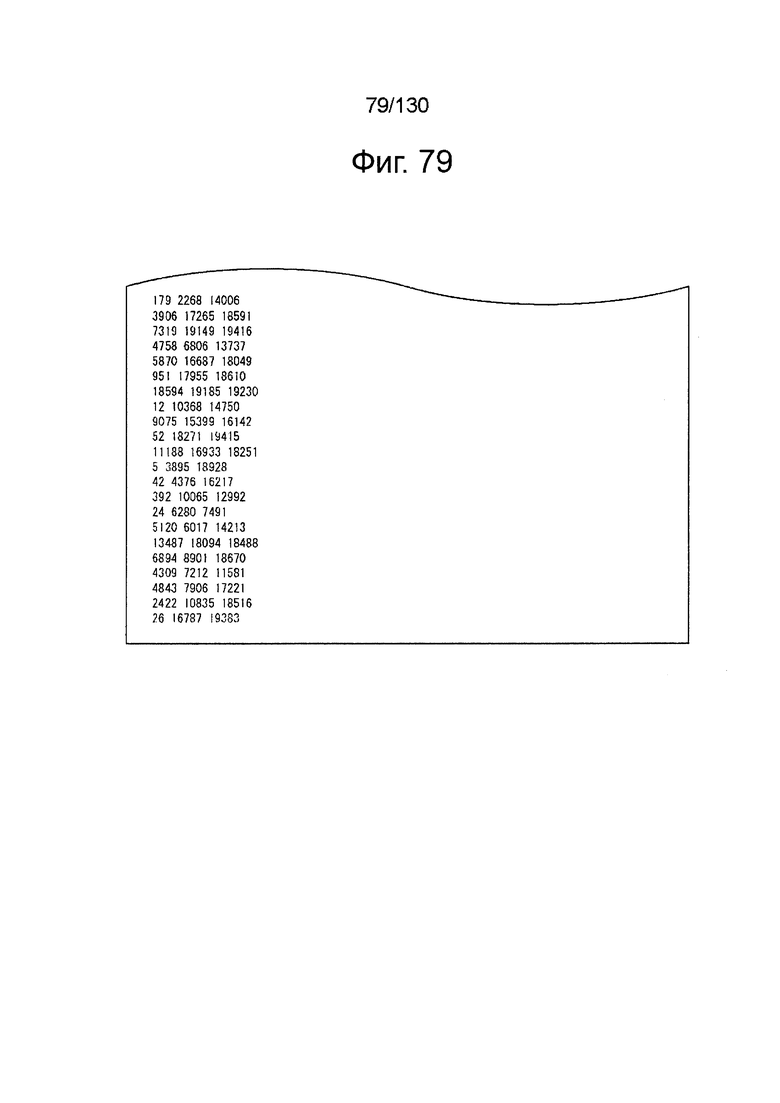

Фиг. 79 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 21/30 и кодовая длина составляет 64800.

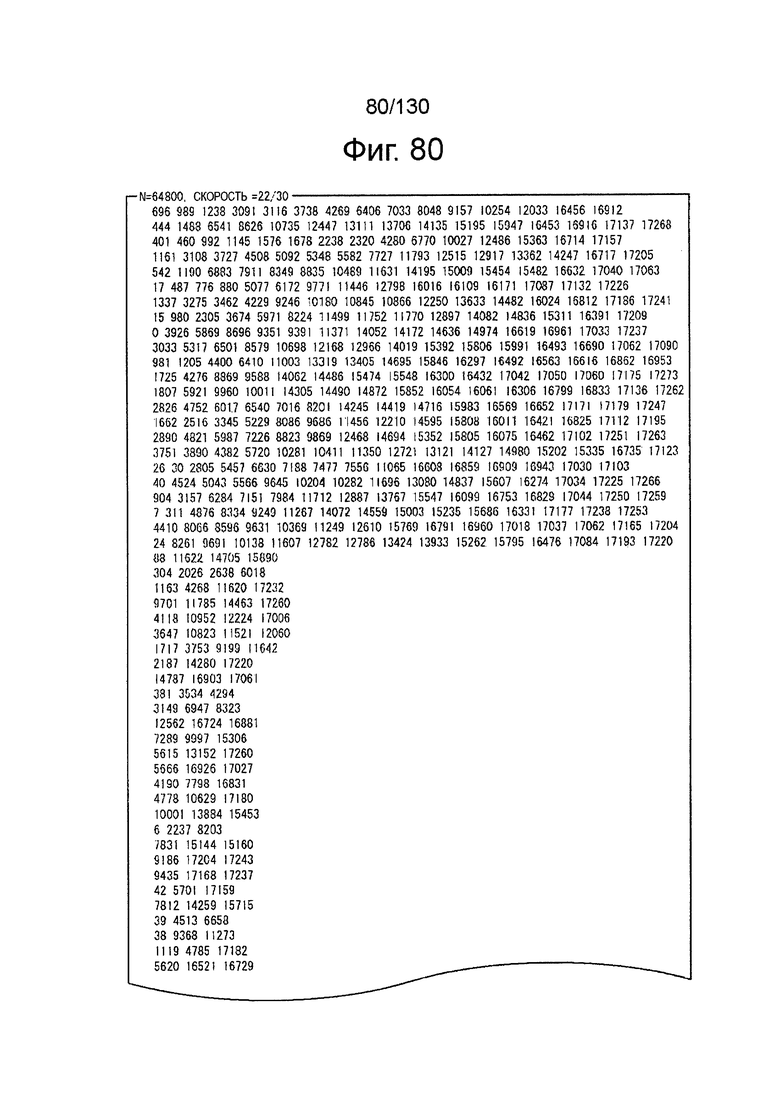

Фиг. 80 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 22/30 и кодовая длина составляет 64800.

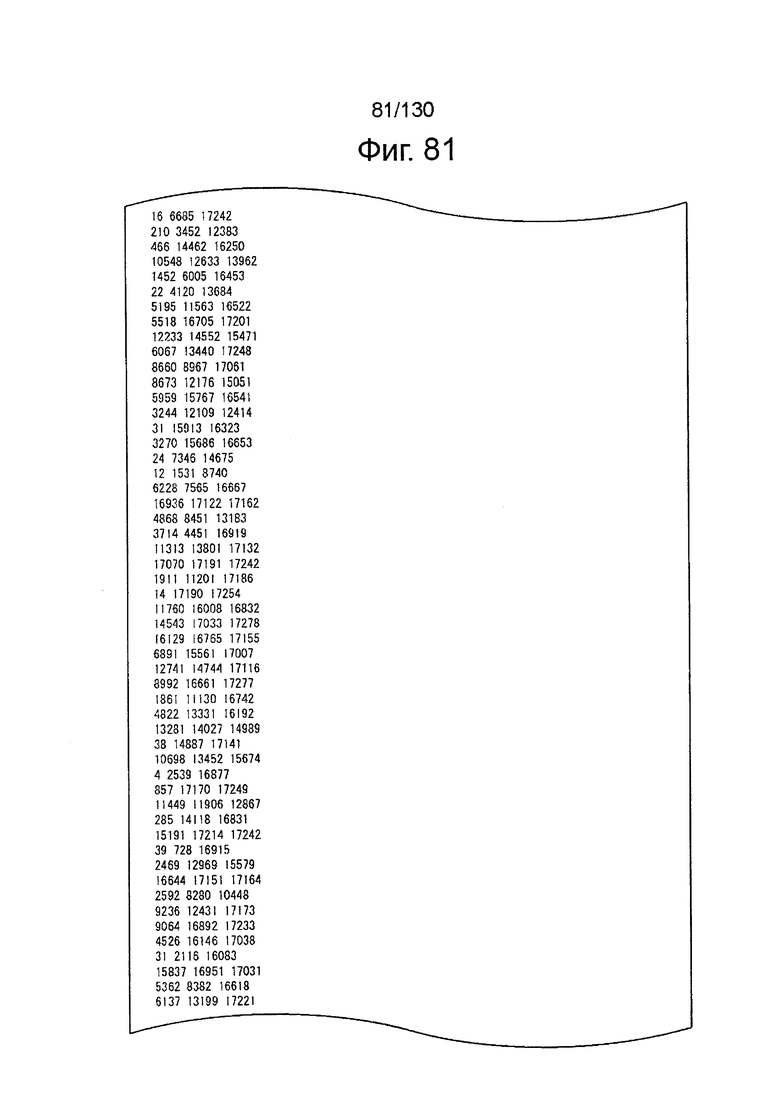

Фиг. 81 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 22/30 и кодовая длина составляет 64800.

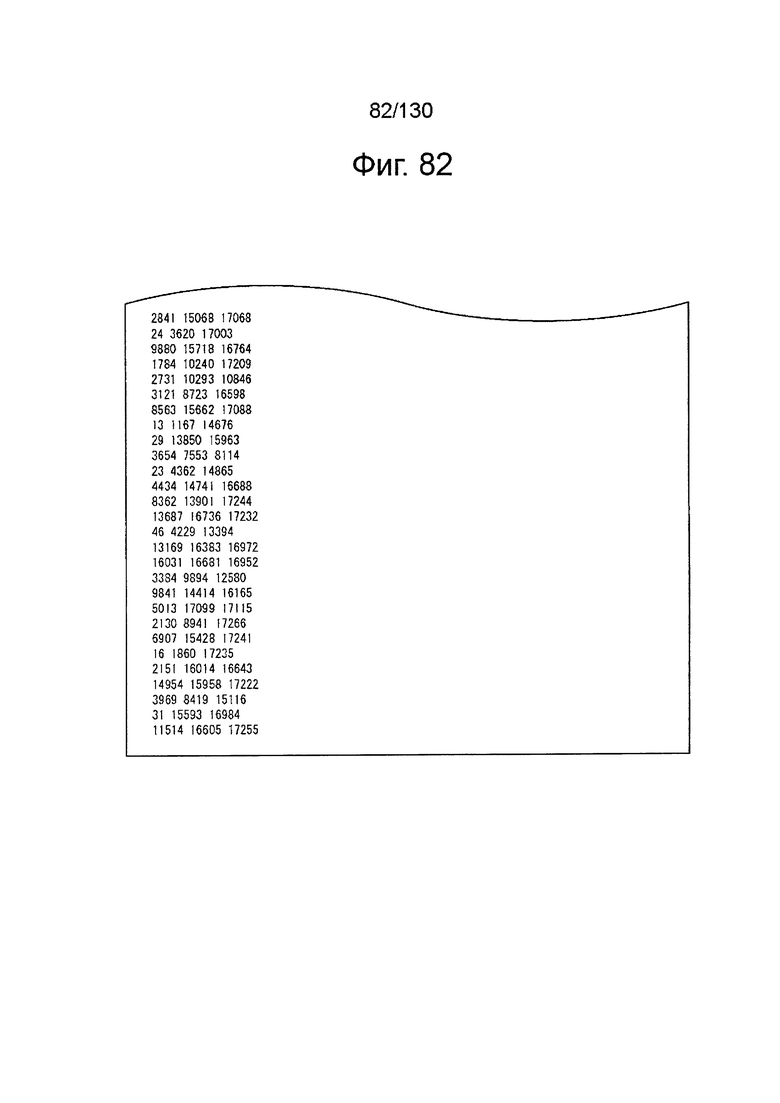

Фиг. 82 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 22/30 и кодовая длина составляет 64800.

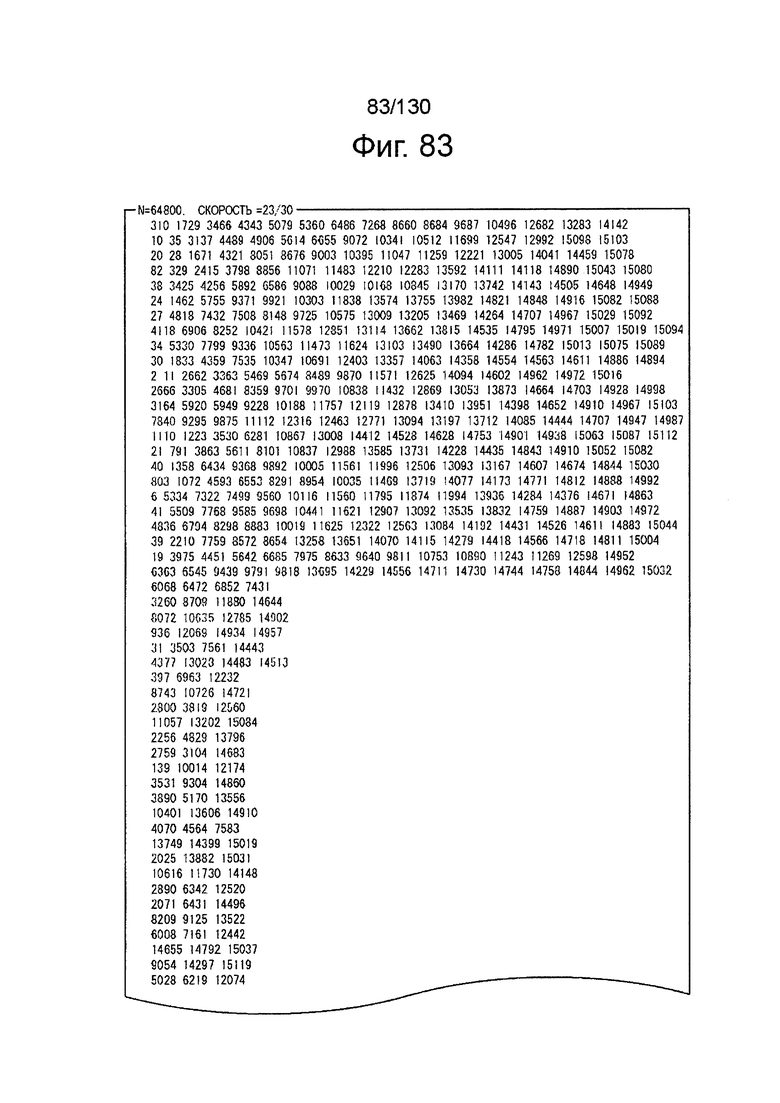

Фиг. 83 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 23/30 и кодовая длина составляет 64800.

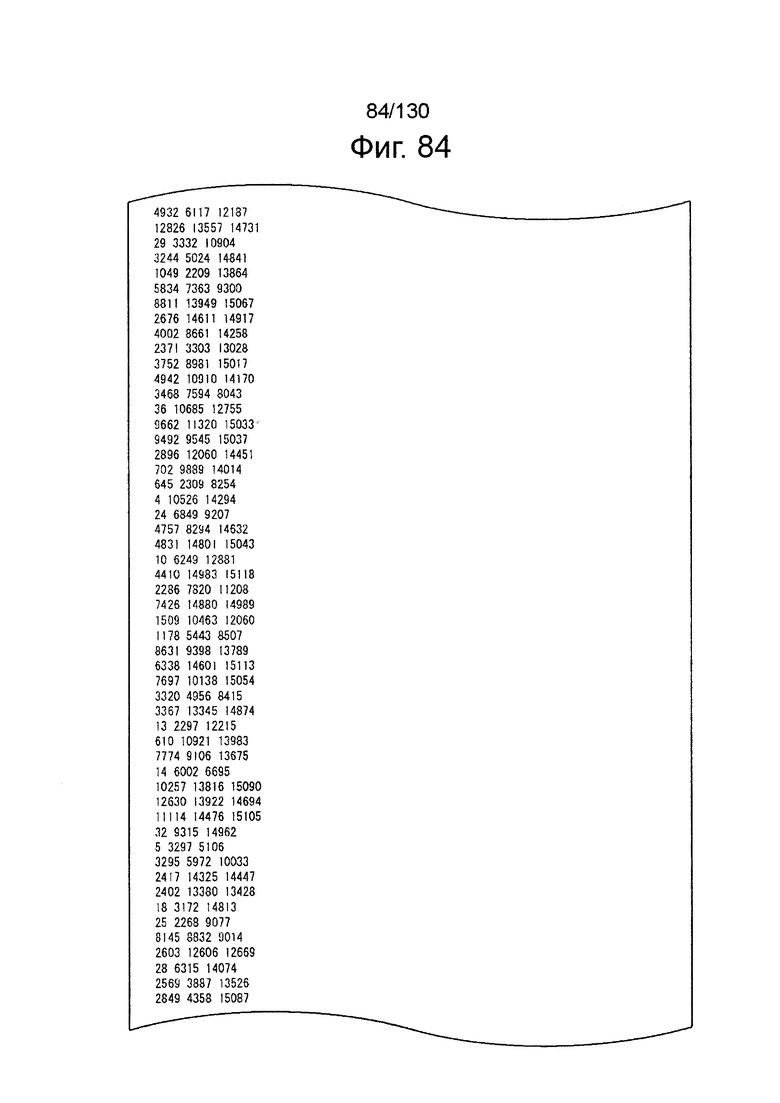

Фиг. 84 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 23/30 и кодовая длина составляет 64800.

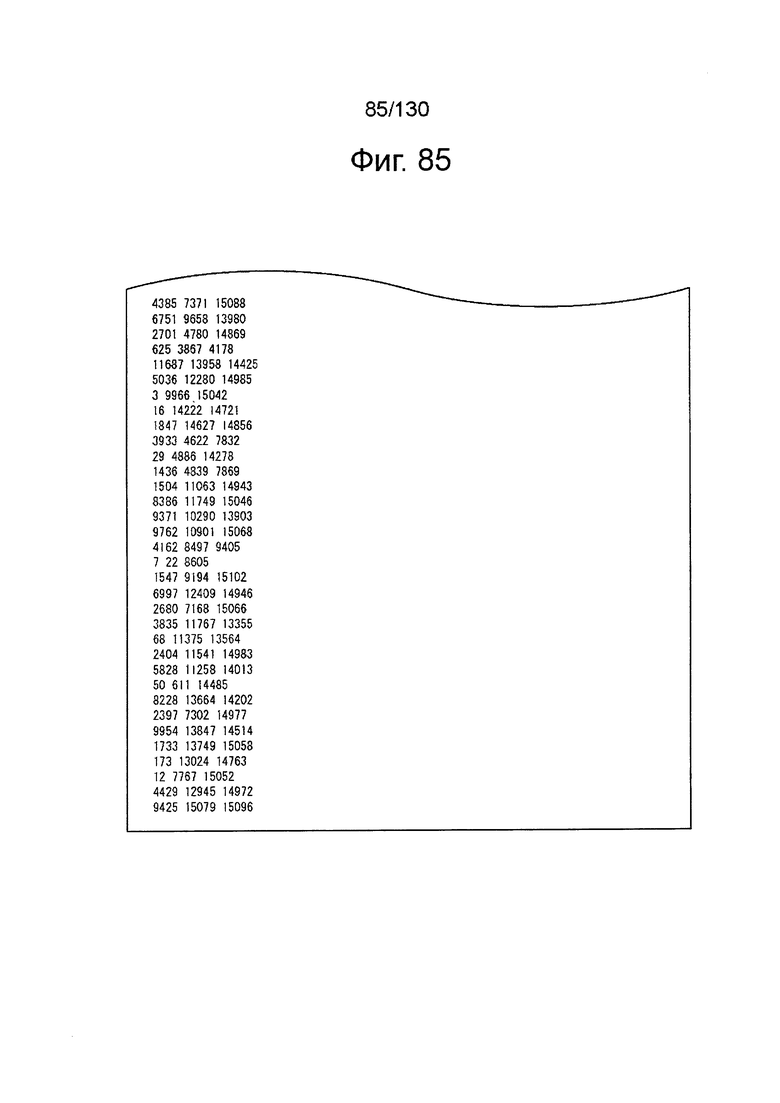

Фиг. 85 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 23/30 и кодовая длина составляет 64800.

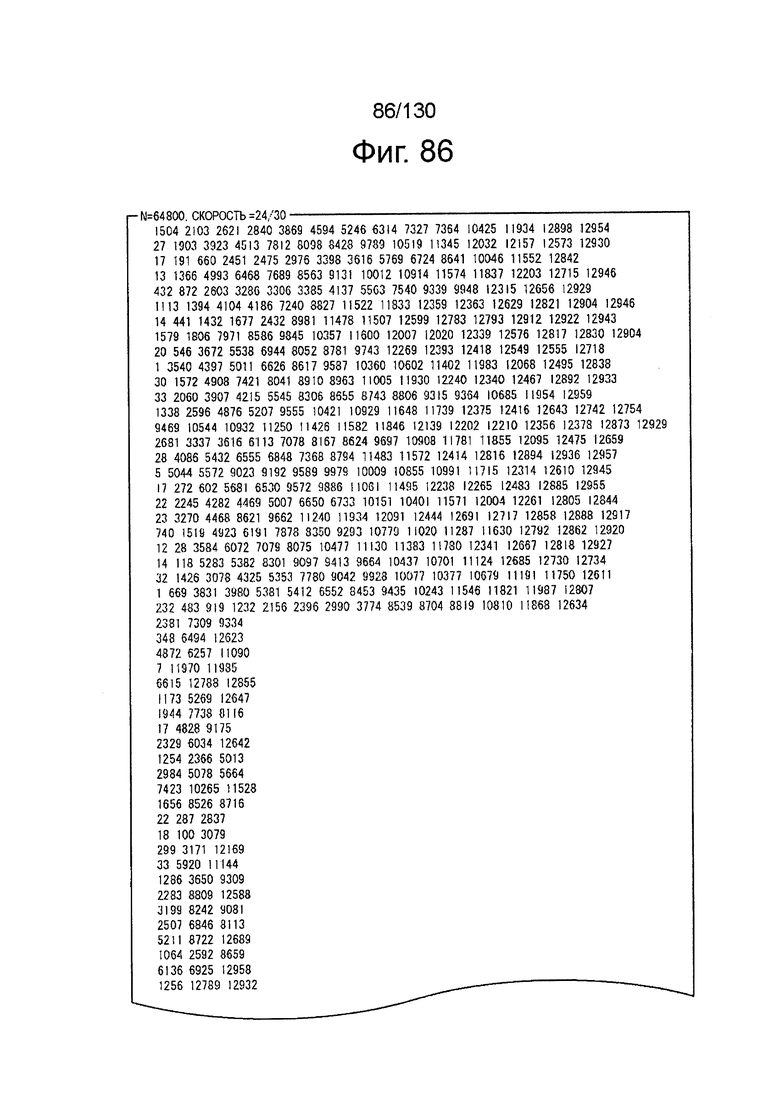

Фиг. 86 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 24/30 и кодовая длина составляет 64800.

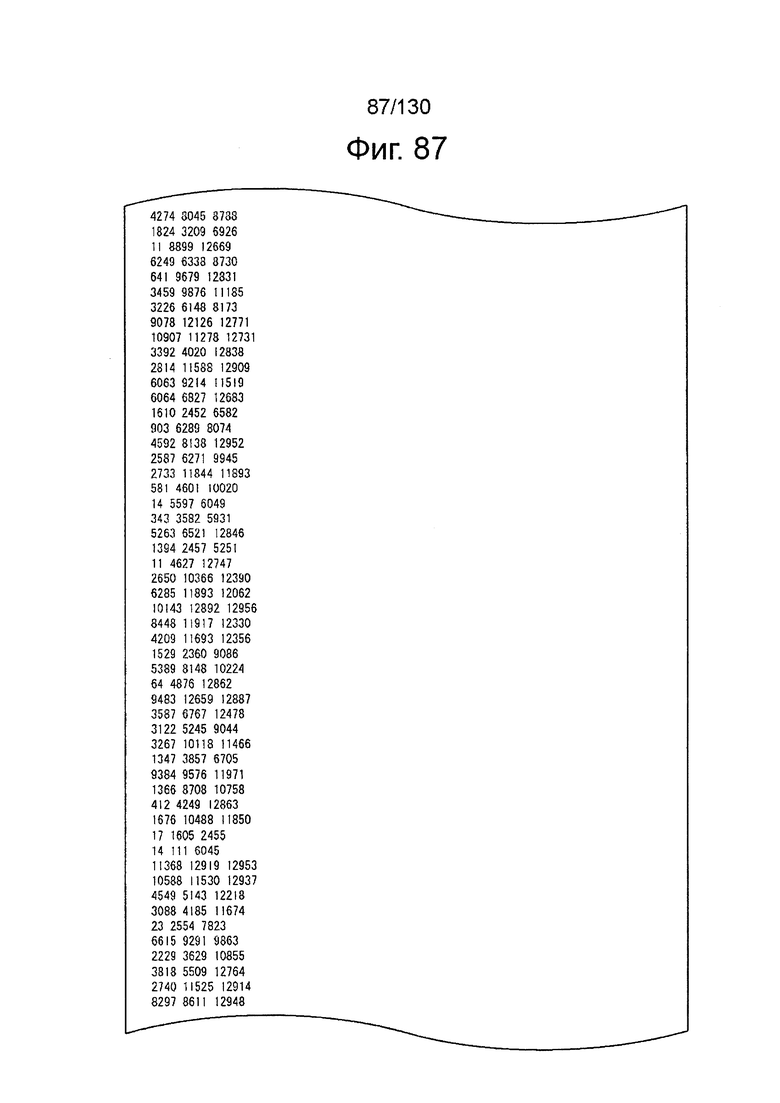

Фиг. 87 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 24/30 и кодовая длина составляет 64800.

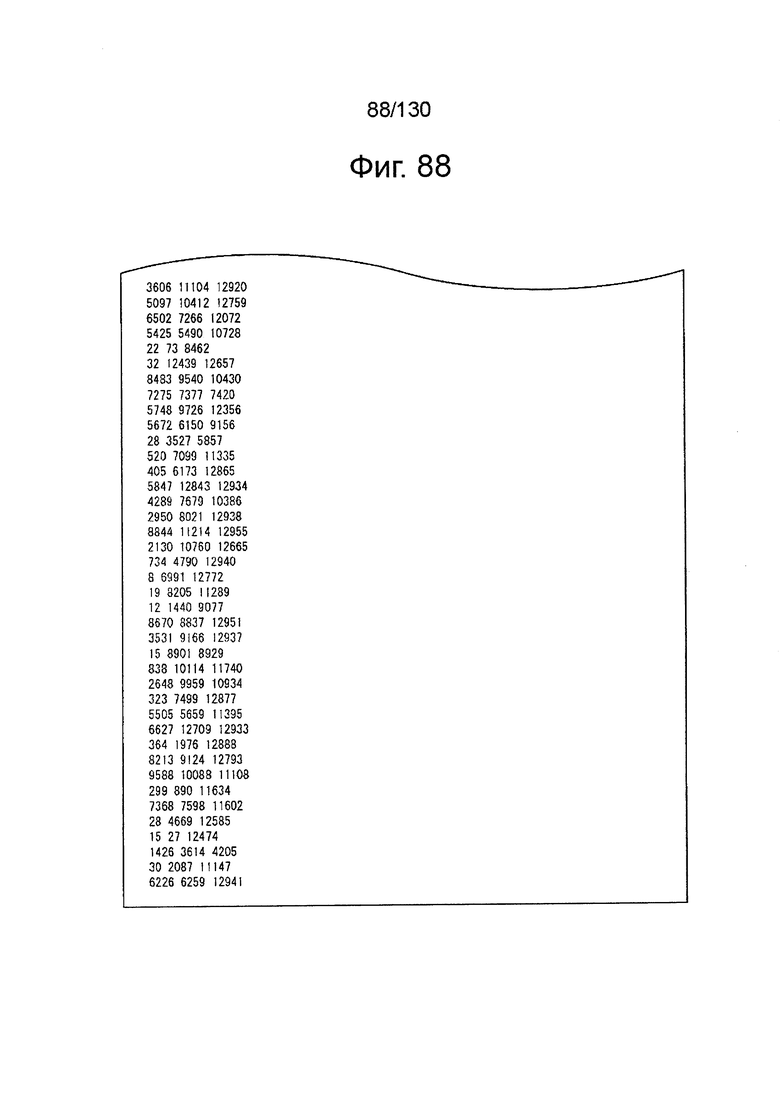

Фиг. 88 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 24/30 и кодовая длина составляет 64800.

Фиг. 89 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 25/30 и кодовая длина составляет 64800.

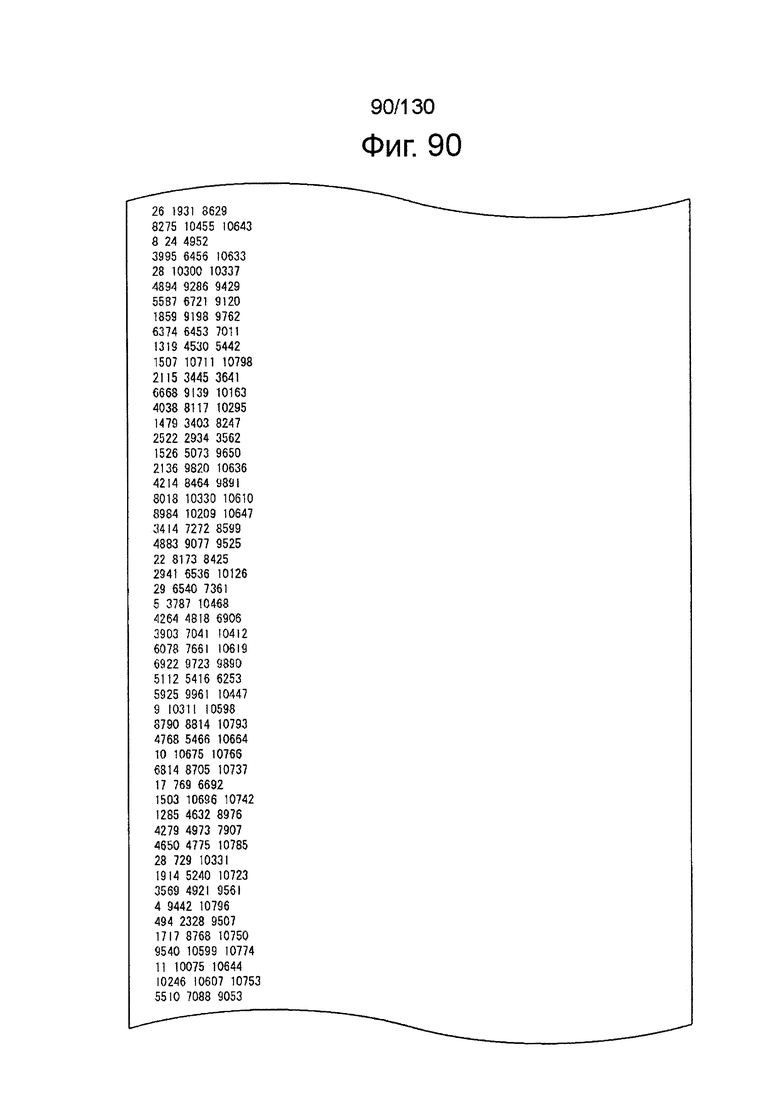

Фиг. 90 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 25/30 и кодовая длина составляет 64800.

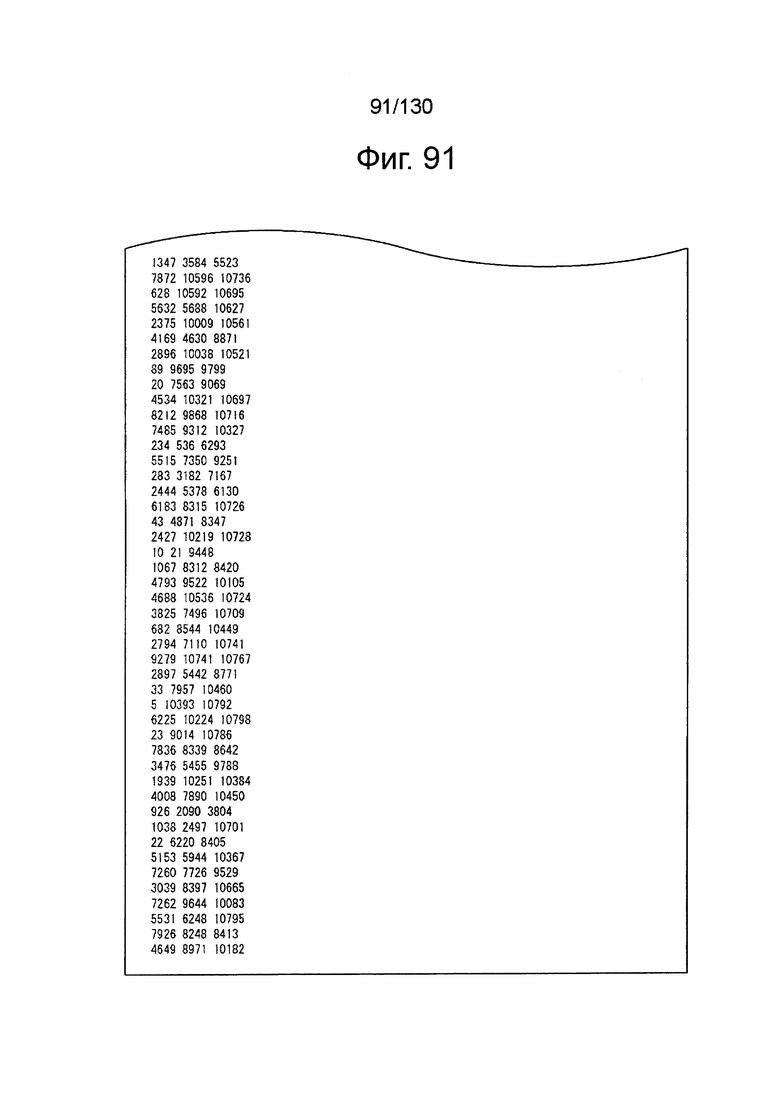

Фиг. 91 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 25/30 и кодовая длина составляет 64800.

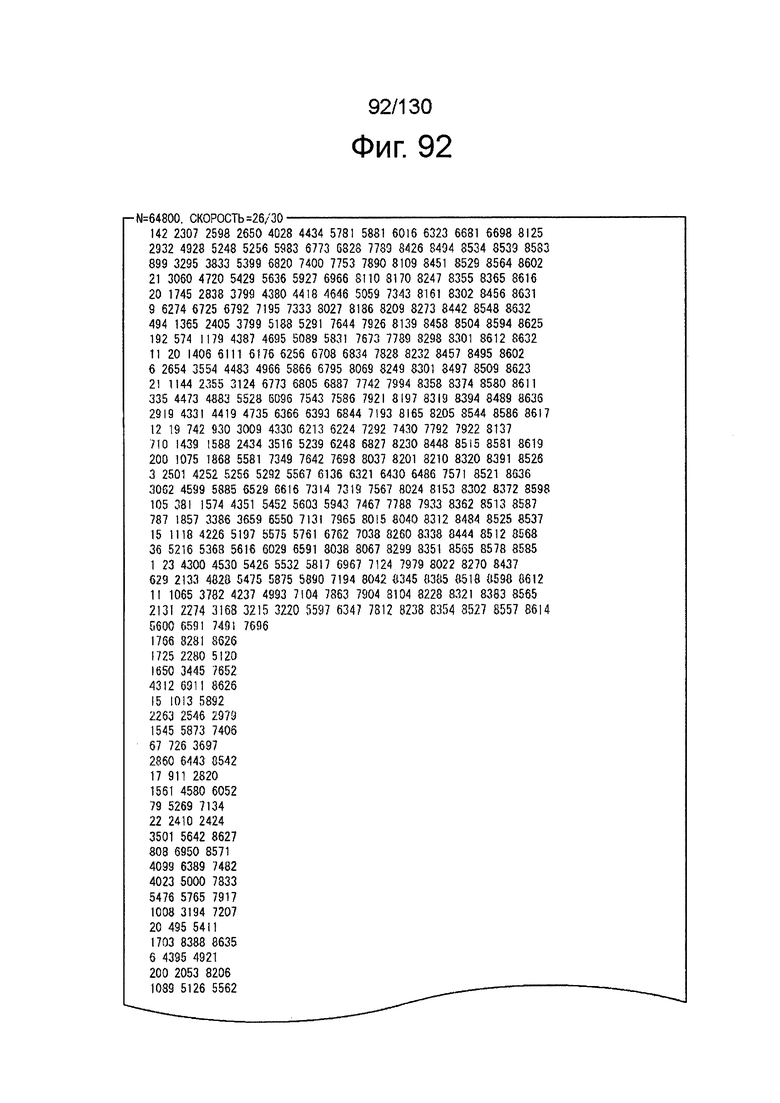

Фиг. 92 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 26/30 и кодовая длина составляет 64800.

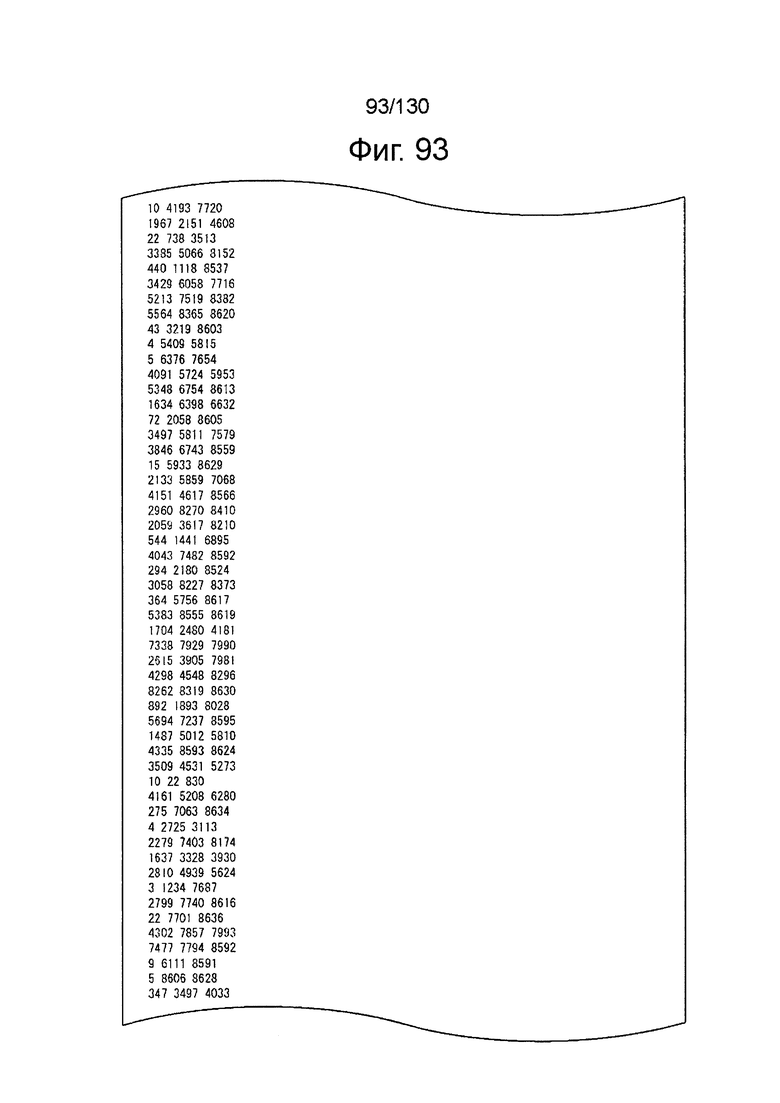

Фиг. 93 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 26/30 и кодовая длина составляет 64800.

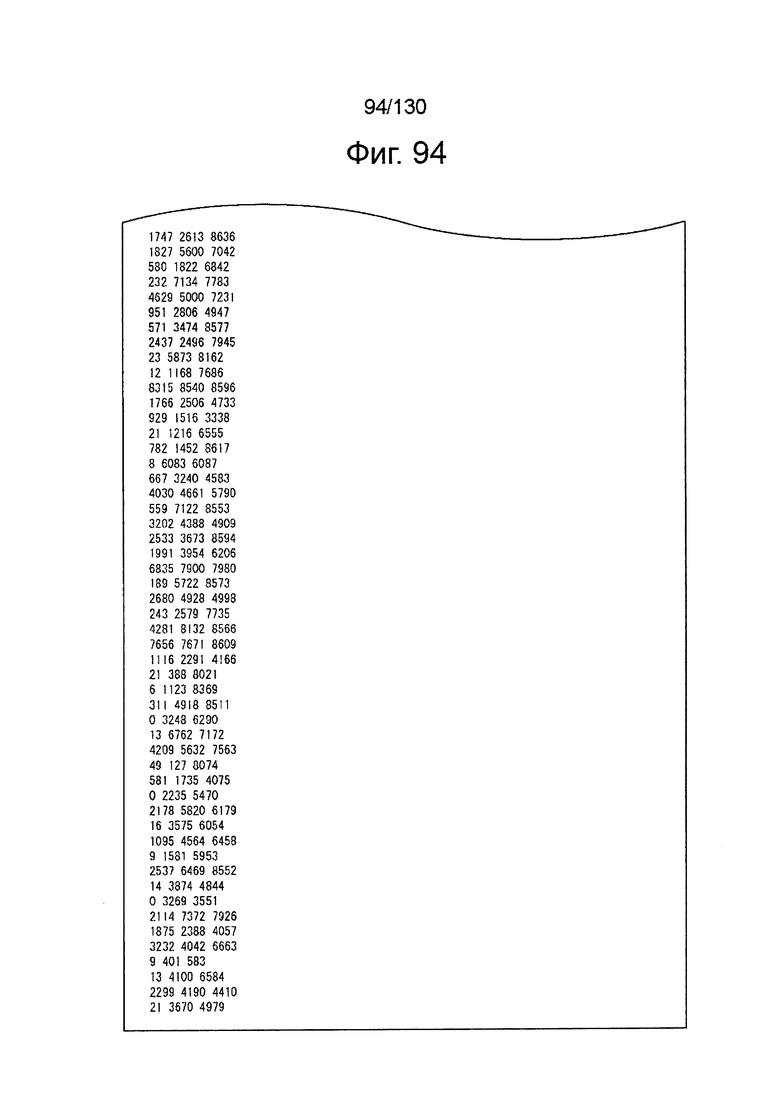

Фиг. 94 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 26/30 и кодовая длина составляет 64800.

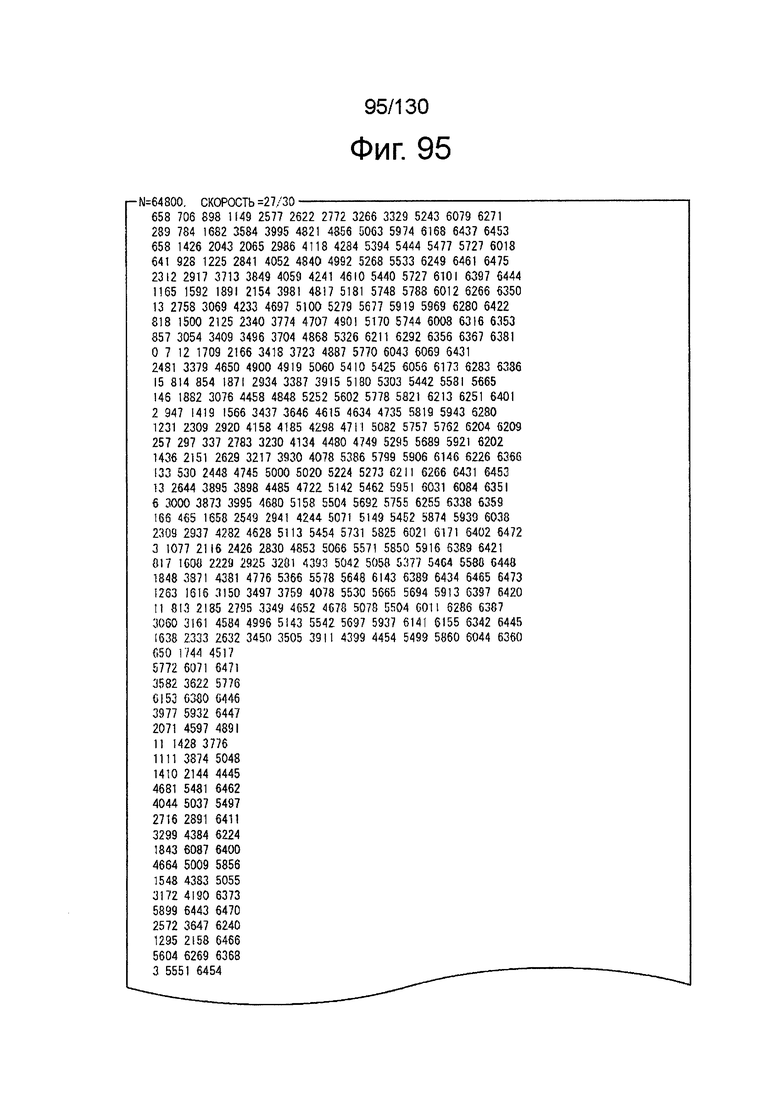

Фиг. 95 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 27/30 и кодовая длина составляет 64800.

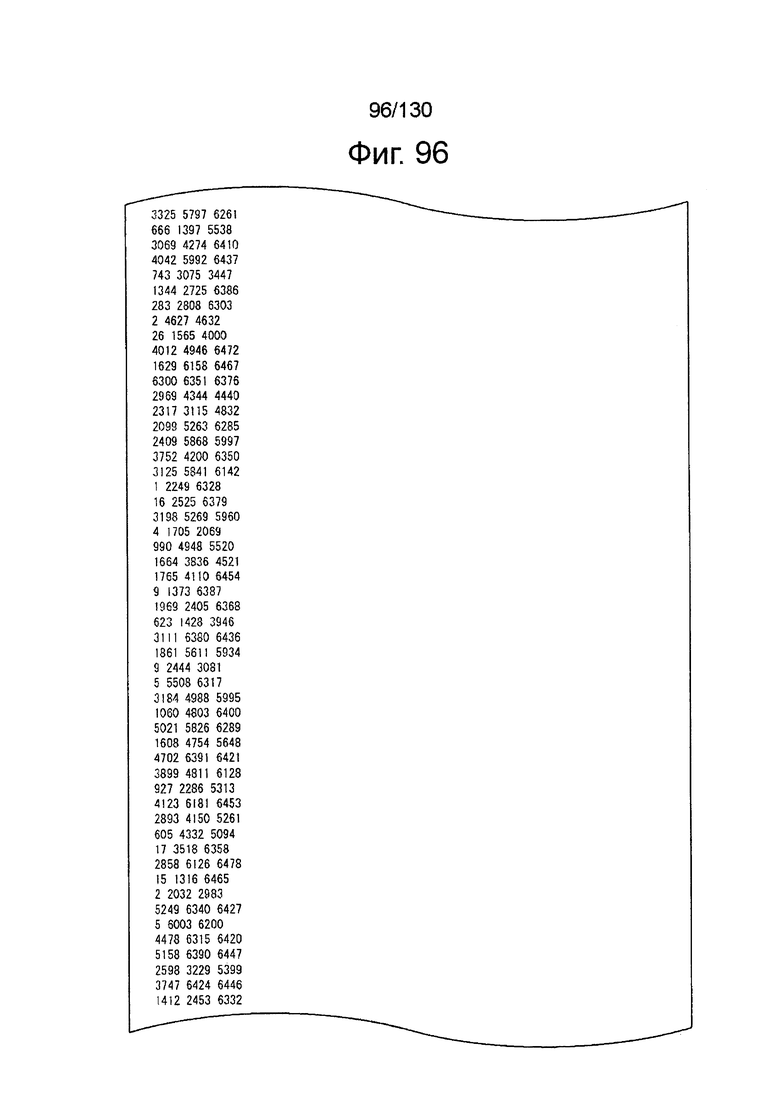

Фиг. 96 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 27/30 и кодовая длина составляет 64800.

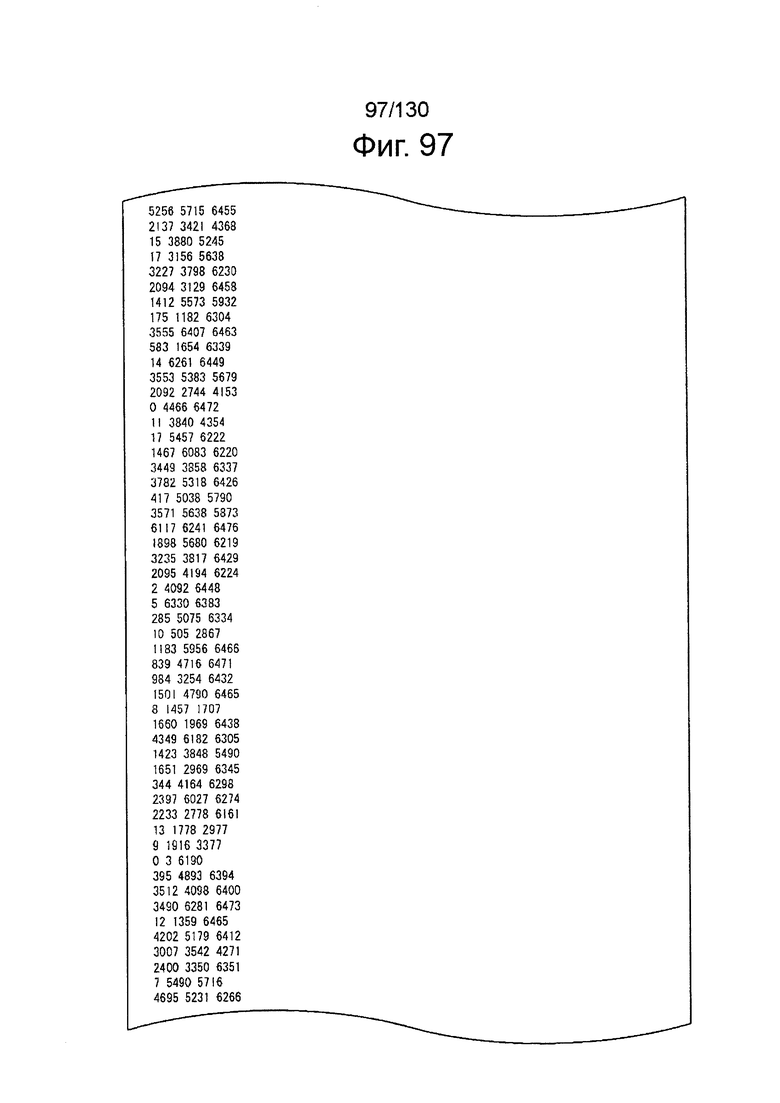

Фиг. 97 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 27/30 и кодовая длина составляет 64800.

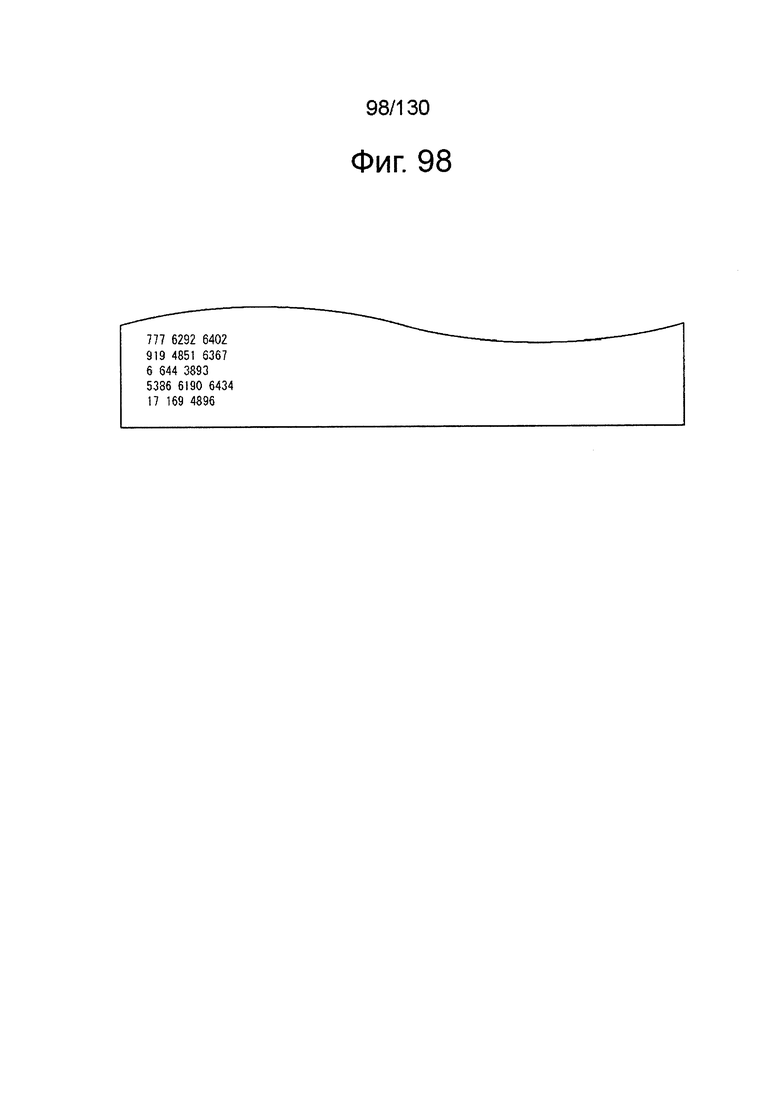

Фиг. 98 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 27/30 и кодовая длина составляет 64800.

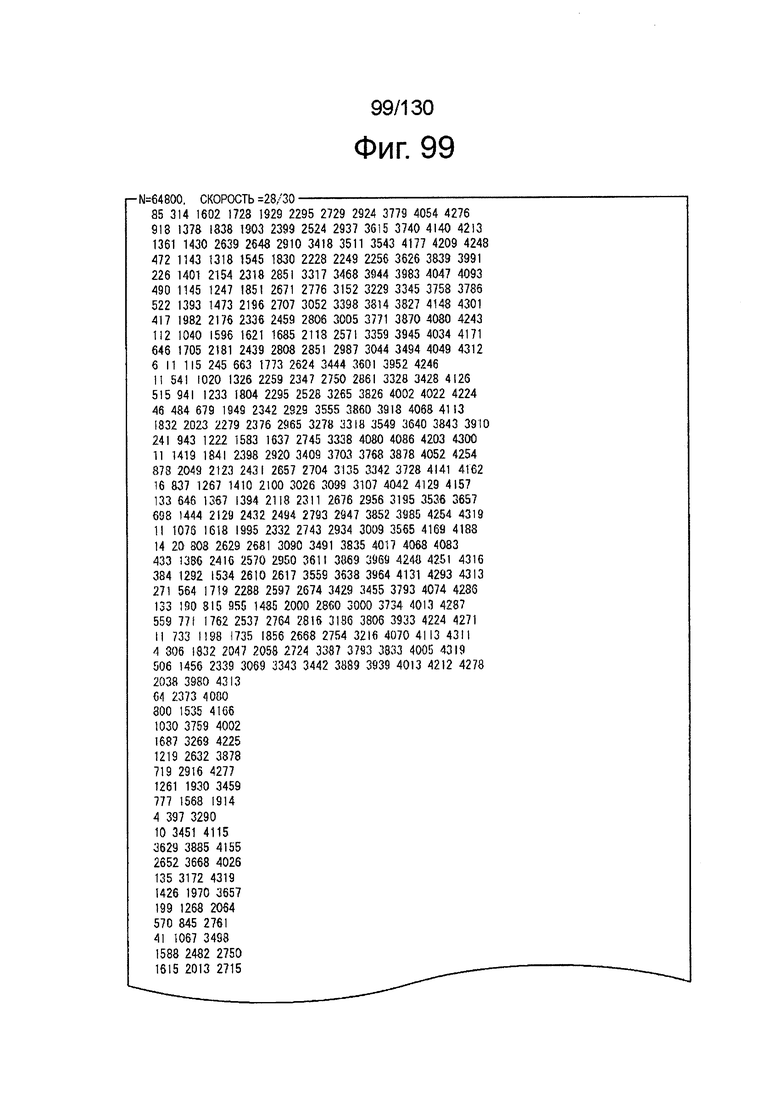

Фиг. 99 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 28/30 и кодовая длина составляет 64800.

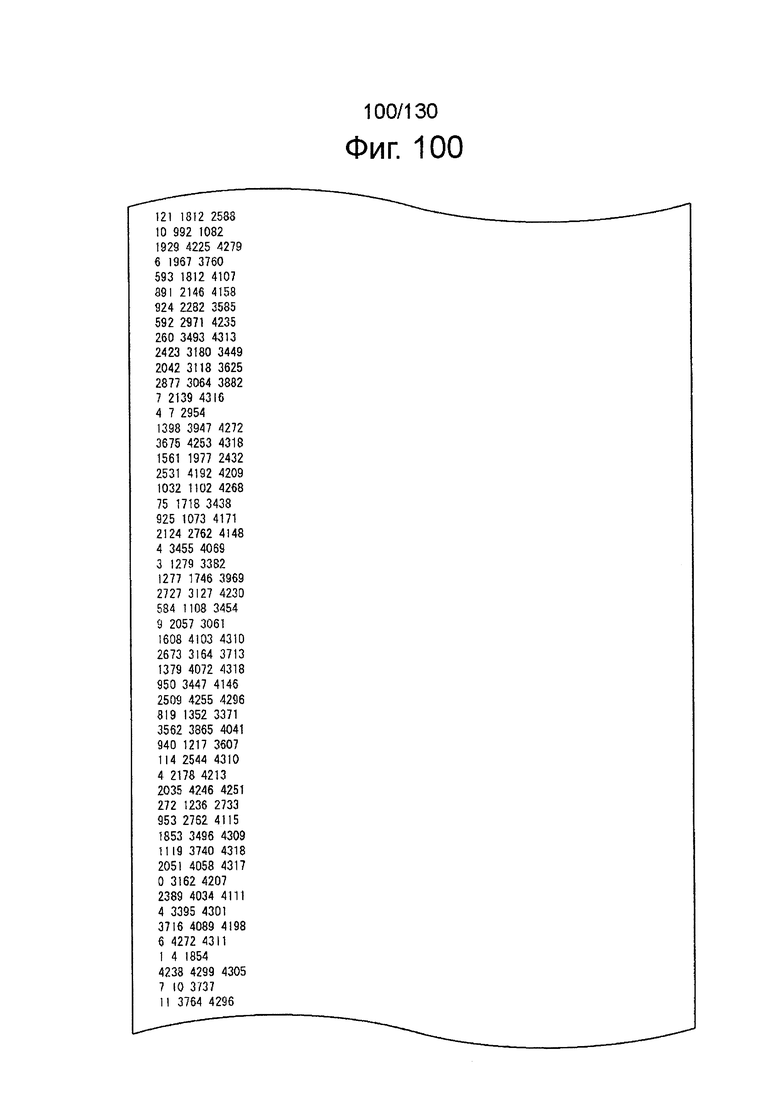

Фиг. 100 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 28/30 и кодовая длина составляет 64800.

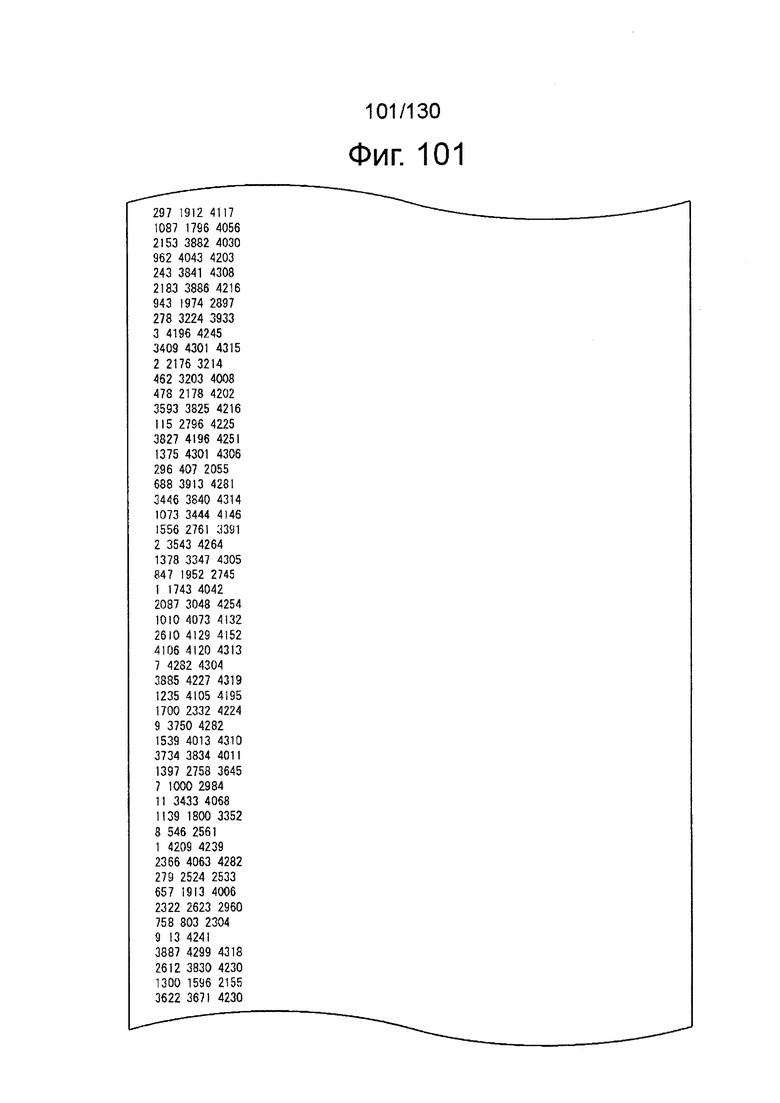

Фиг. 101 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 28/30 и кодовая длина составляет 64800.

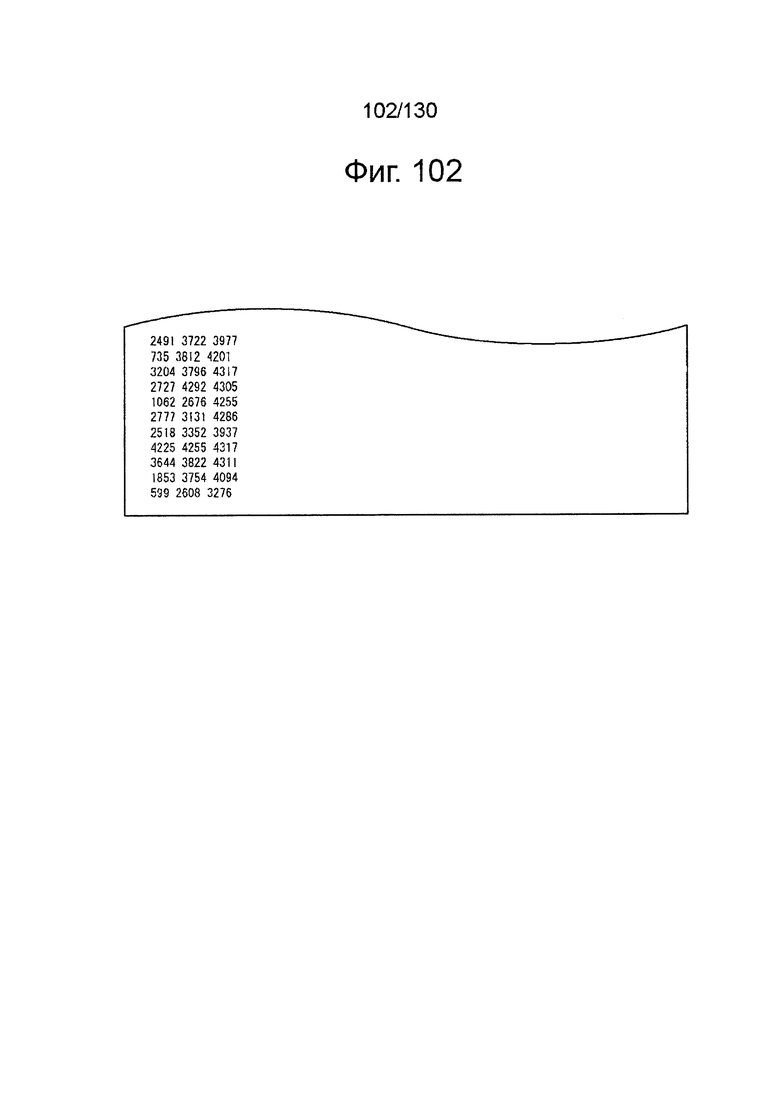

Фиг. 102 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 28/30 и кодовая длина составляет 64800.

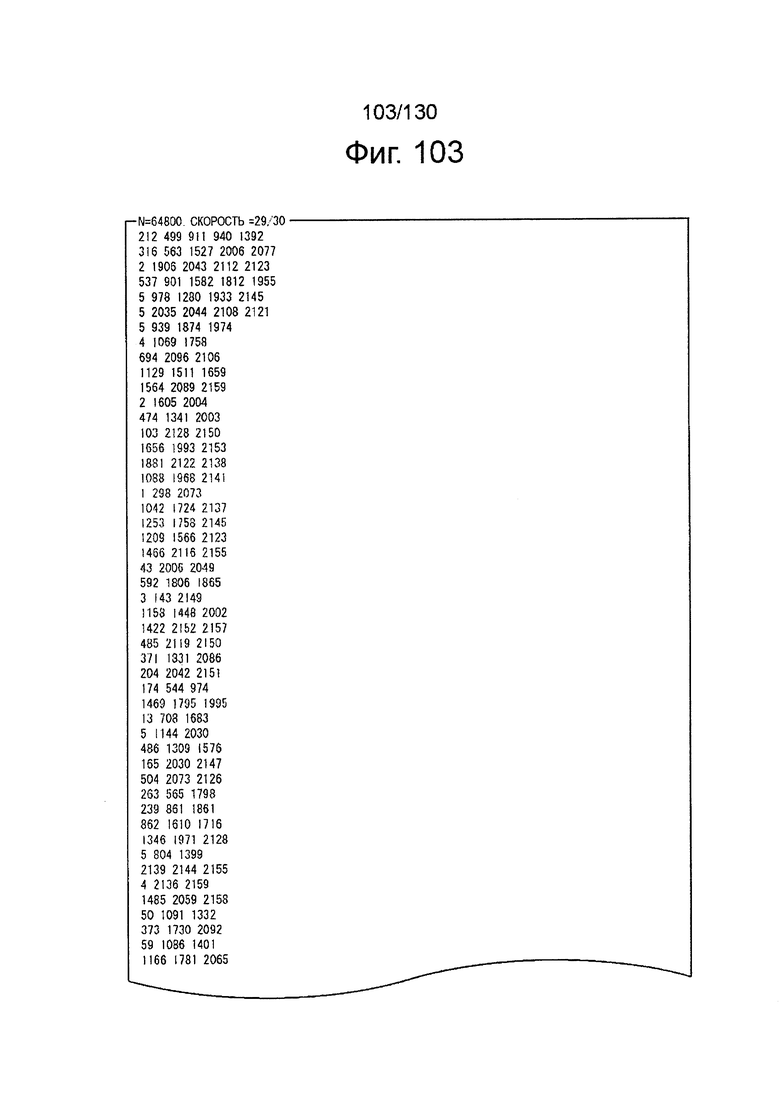

Фиг. 103 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 29/30 и кодовая длина составляет 64800.

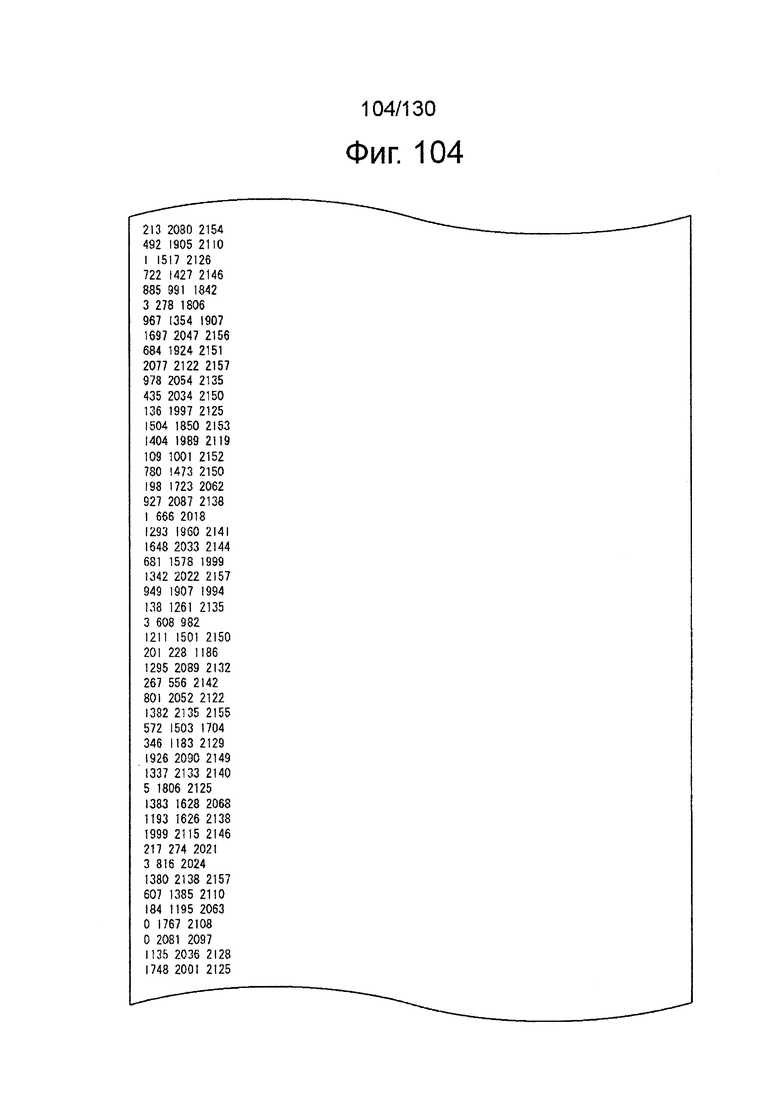

Фиг. 104 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 29/30 и кодовая длина составляет 64800.

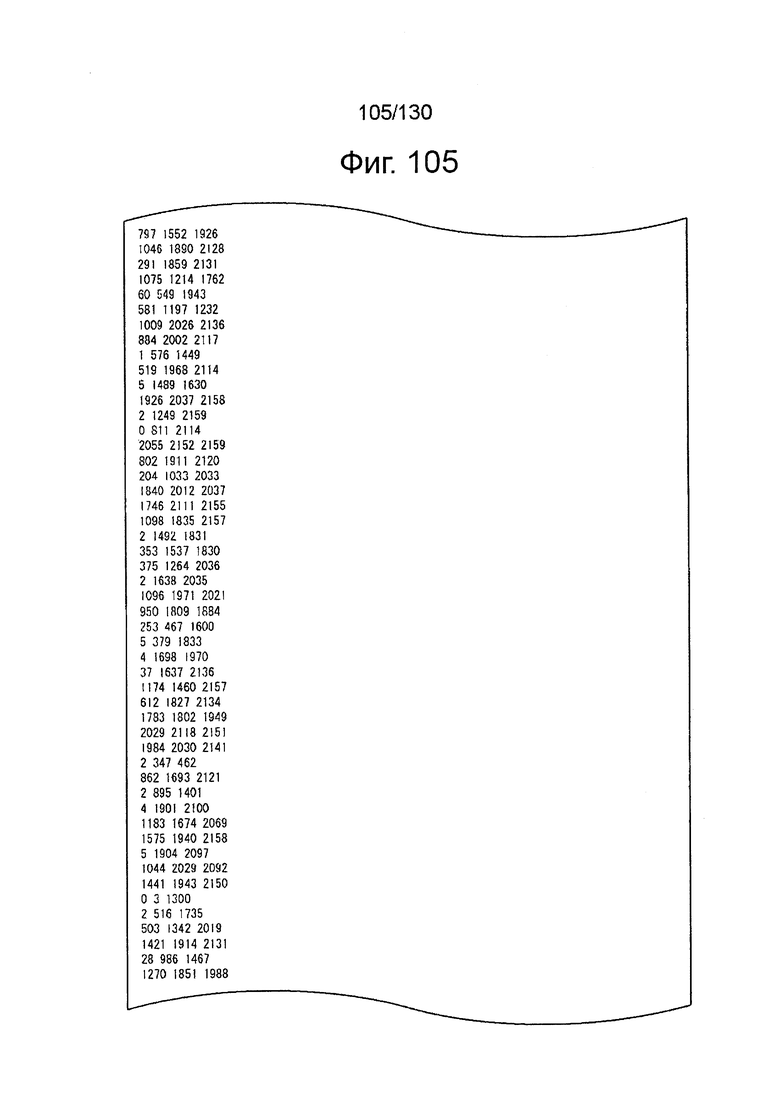

Фиг. 105 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 29/30 и кодовая длина составляет 64800.

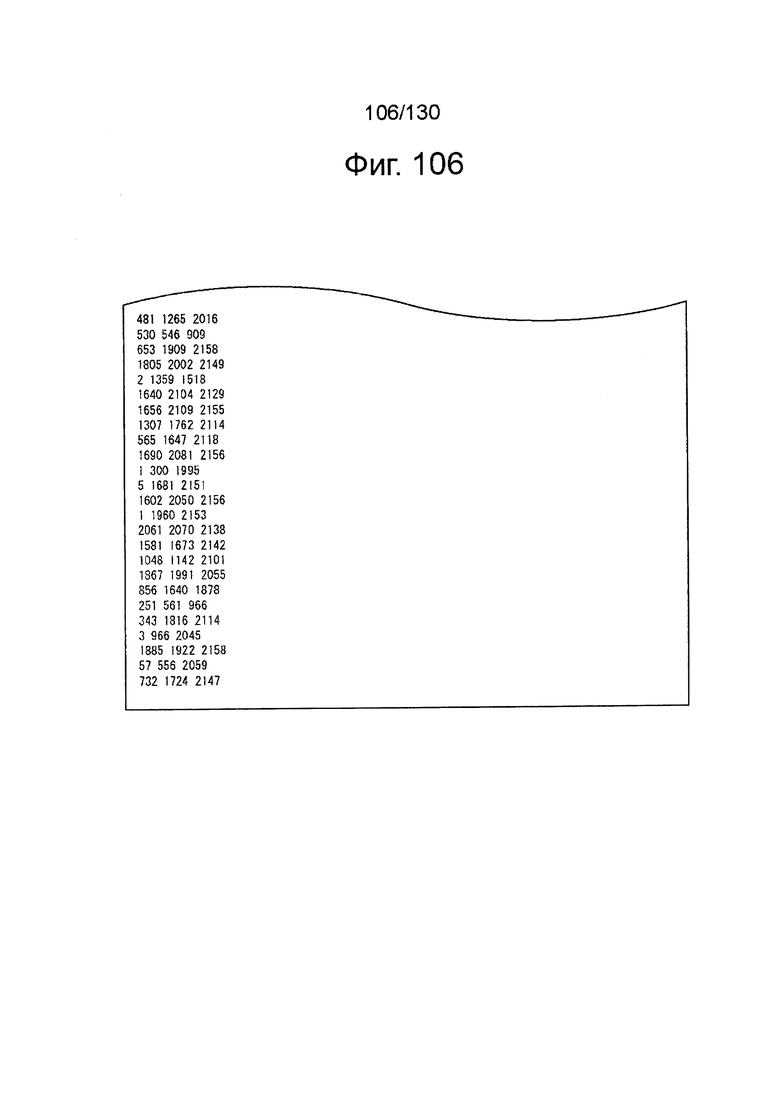

Фиг. 106 является иллюстрацией примера таблицы начальных значений матрицы контроля четности, в которой скорость кодирования равна 29/30 и кодовая длина составляет 64800.

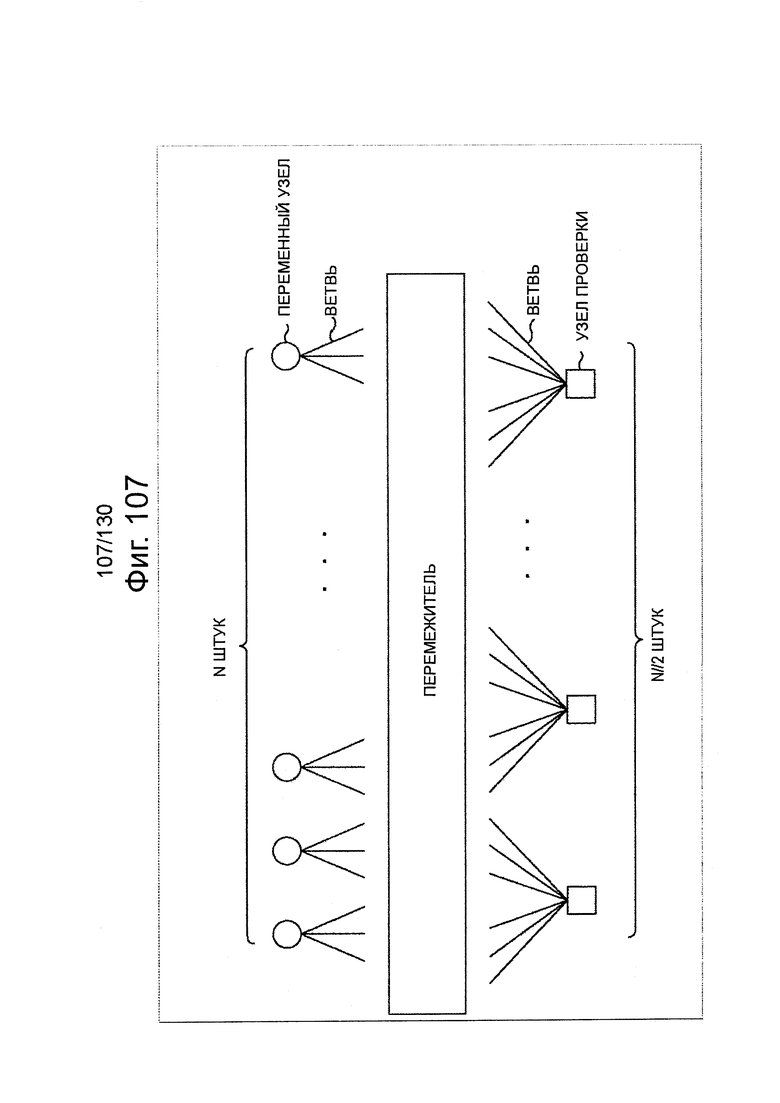

Фиг. 107 является иллюстрацией графа Таннера ансамбля степени последовательности, в которой вес столбца равен 3 и вес строки составляет 6.

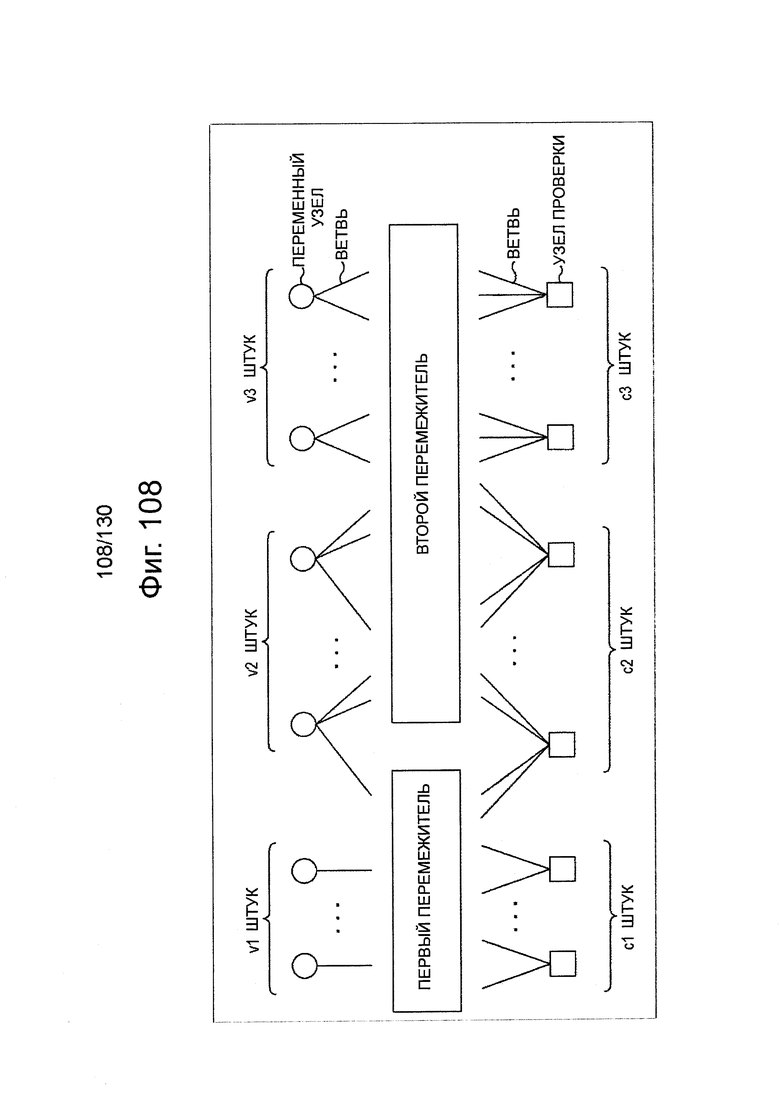

Фиг. 108 является иллюстрацией графа Таннера ансамбля мультиграничного типа.

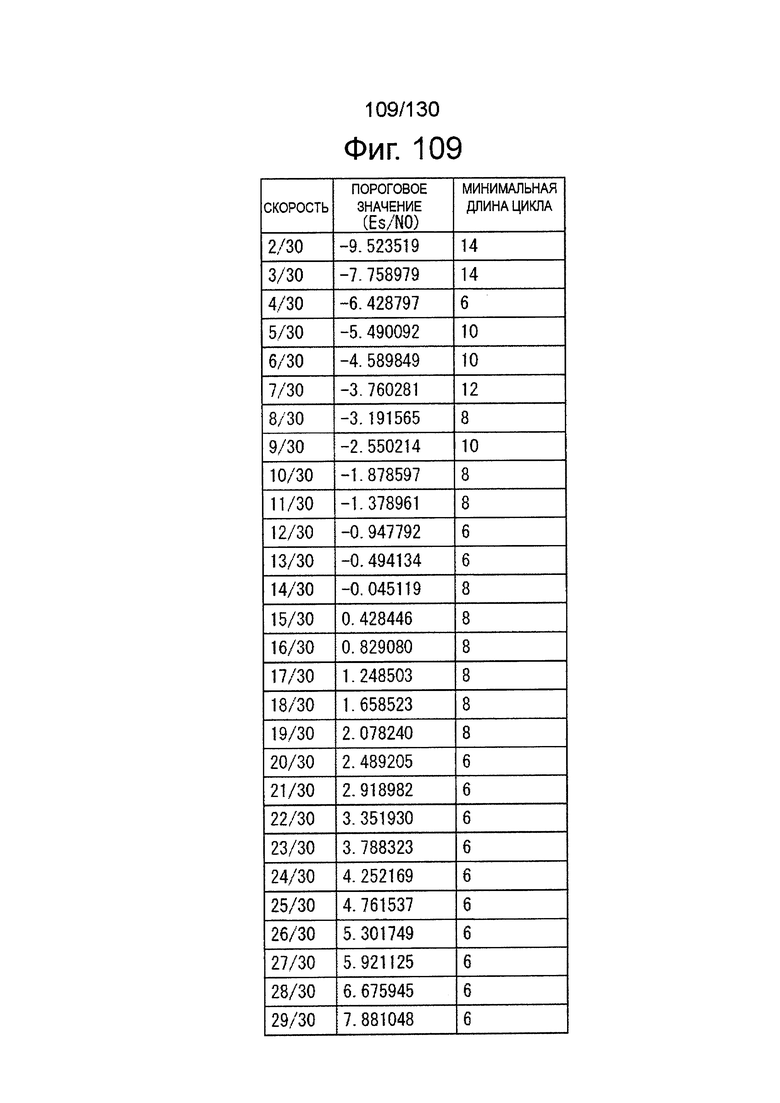

Фиг. 109 является иллюстрацией минимальной длины цикла и порогового значения производительности матрицы контроля четности LDPC-кода с кодовой длиной 64800.

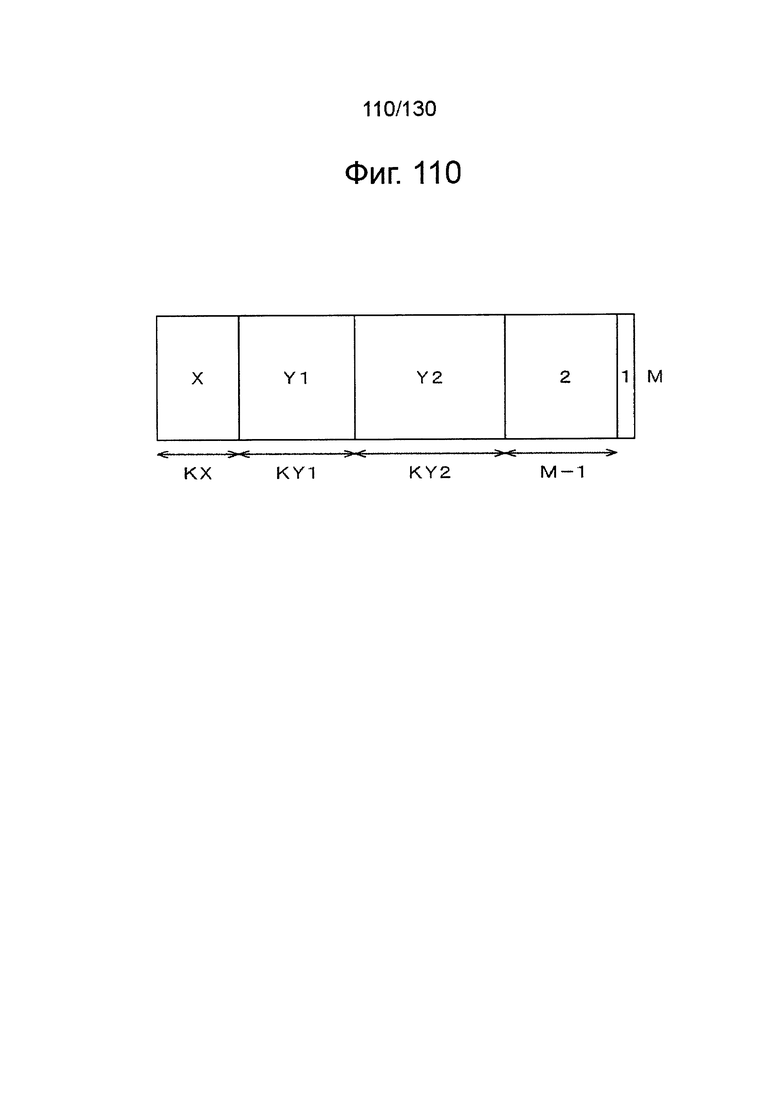

Фиг. 110 является иллюстрацией матрицы проверки четности LDPC-кода с кодовой длиной 64800.

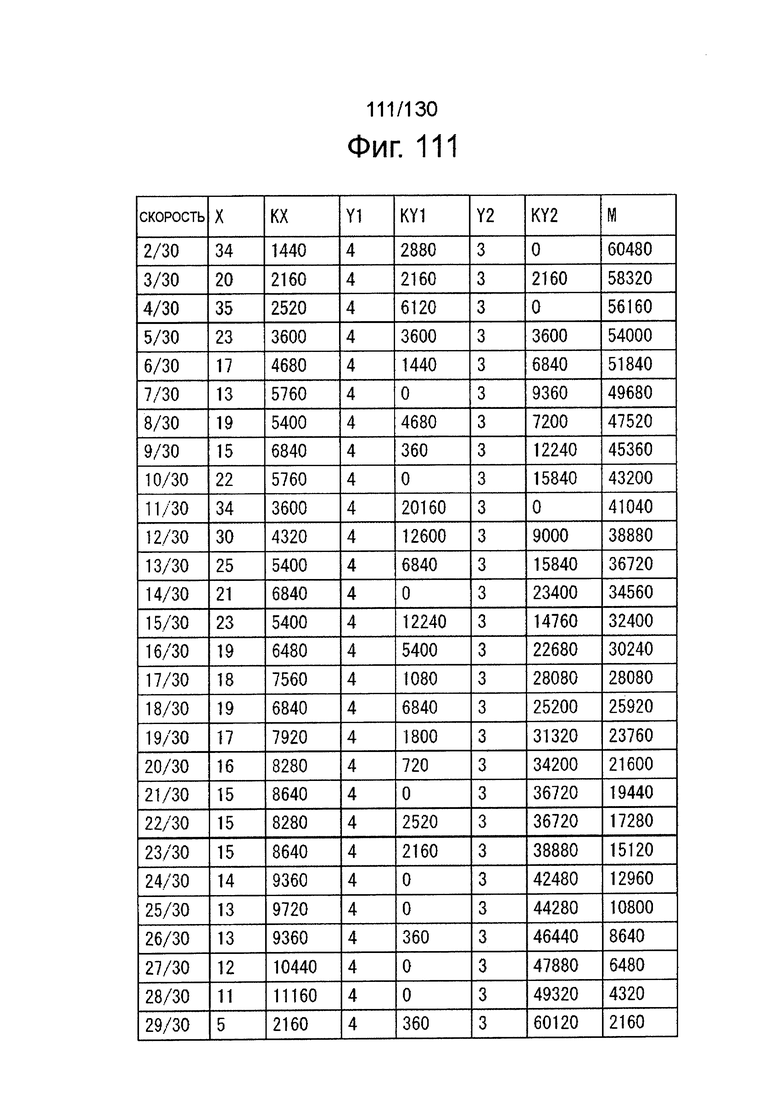

Фиг. 111 является иллюстрацией матрицы контроля четности LDPC-кода с кодовой длиной 64800.

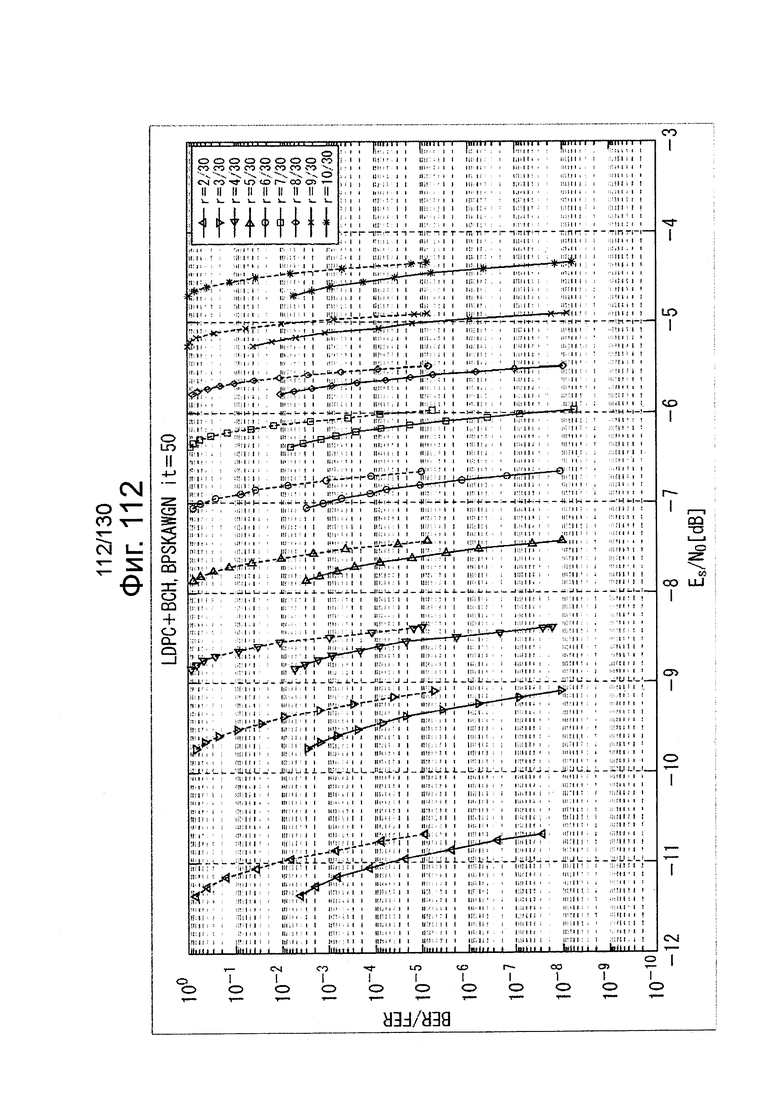

Фиг. 112 является иллюстрацией результата моделирования BER/FER LDPC-кода с кодовой длиной 64800.

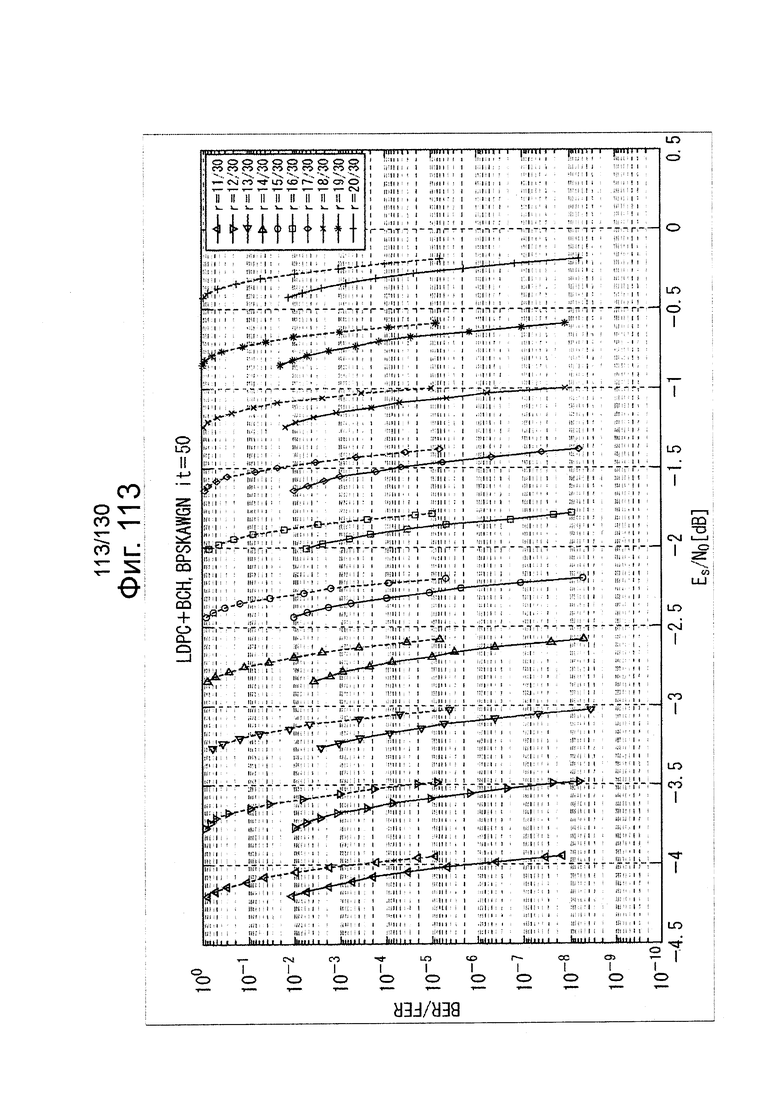

Фиг. 113 является иллюстрацией результата моделирования BER/FER LDPC-кода с кодовой длиной 64800.

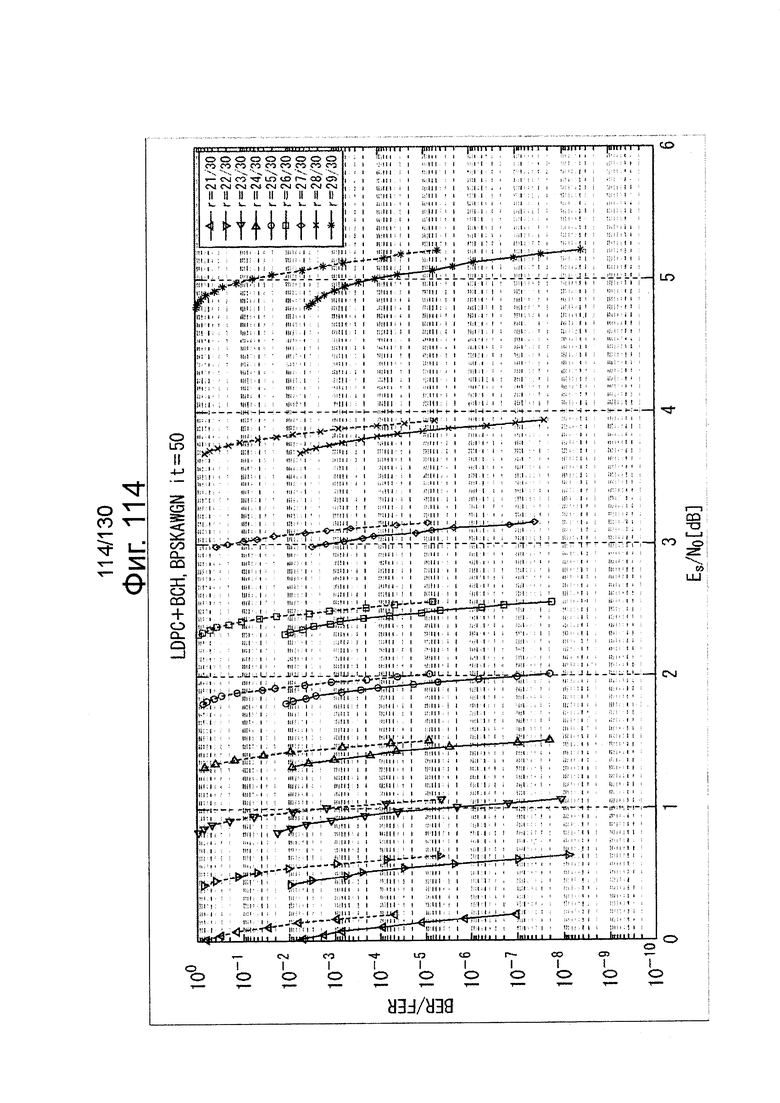

Фиг. 114 является иллюстрацией результата моделирования BER/FER LDPC-кода с кодовой длиной 64800.

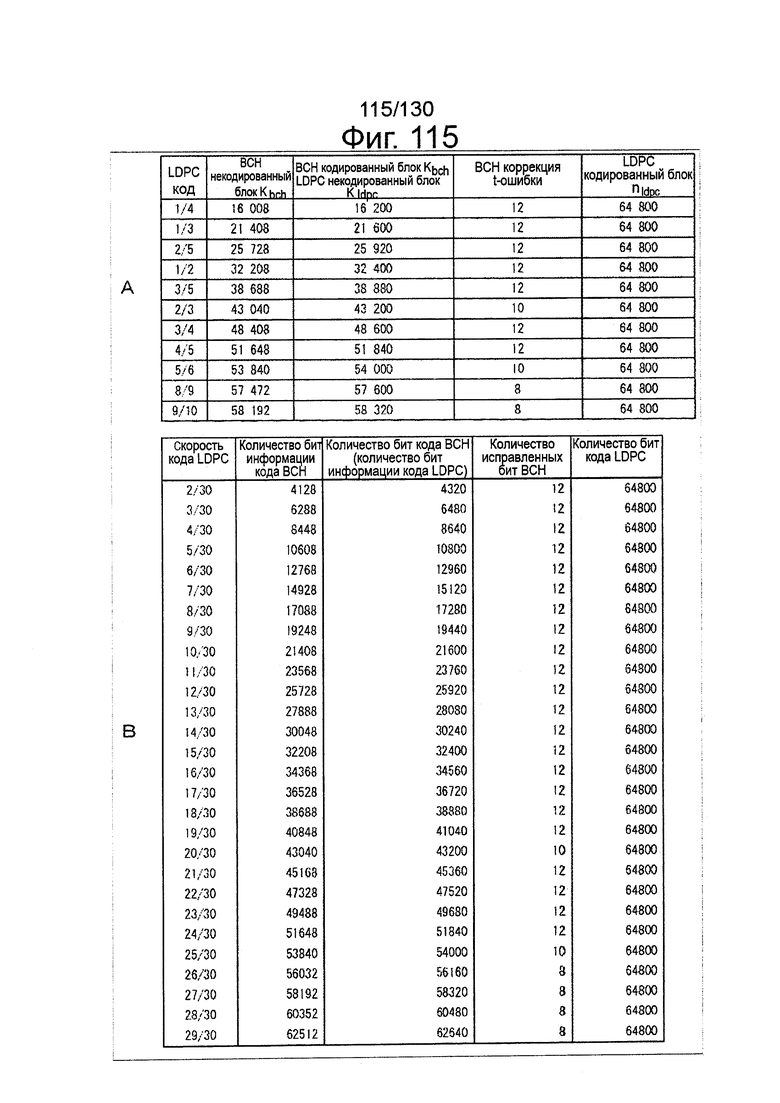

Фиг. 115 является иллюстрацией ВСН кода, используемого для моделирования BER/FER LDPC-кода с кодовой длиной 64800.

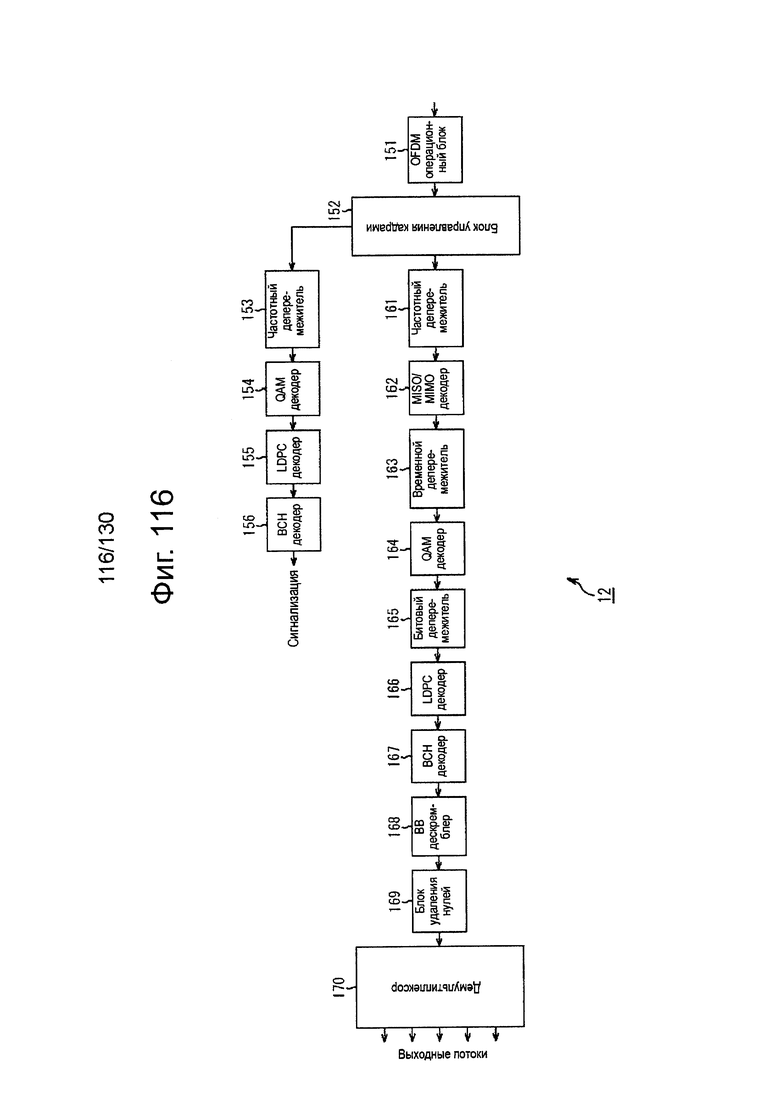

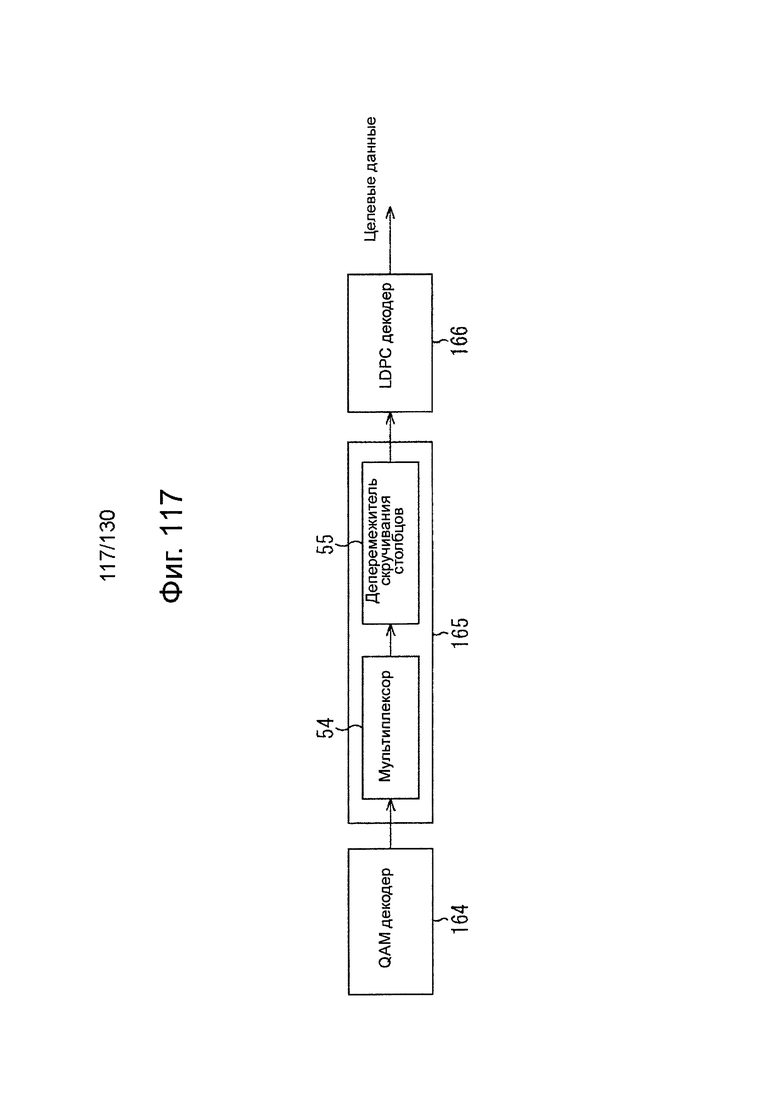

Фиг. 116 представляет собой блок-схему, иллюстрирующую пример конфигурации приемного устройства 12.

Фиг. 117 представляет собой блок-схему, иллюстрирующую пример конфигурации битового деперемежителя 165.

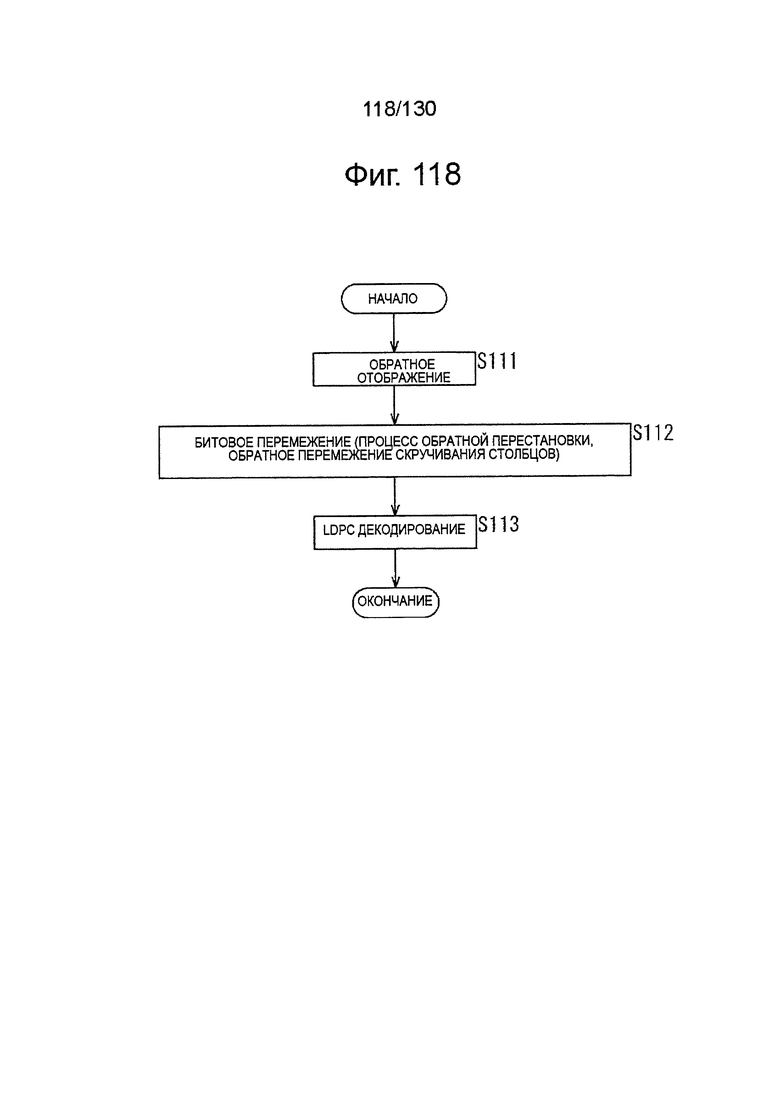

Фиг. 118 является блок-схемой алгоритма, иллюстрирующей процесс обработки, выполняемый QAM декодером 164, битовым деперемежителем 165 и LDPC декодером 166.

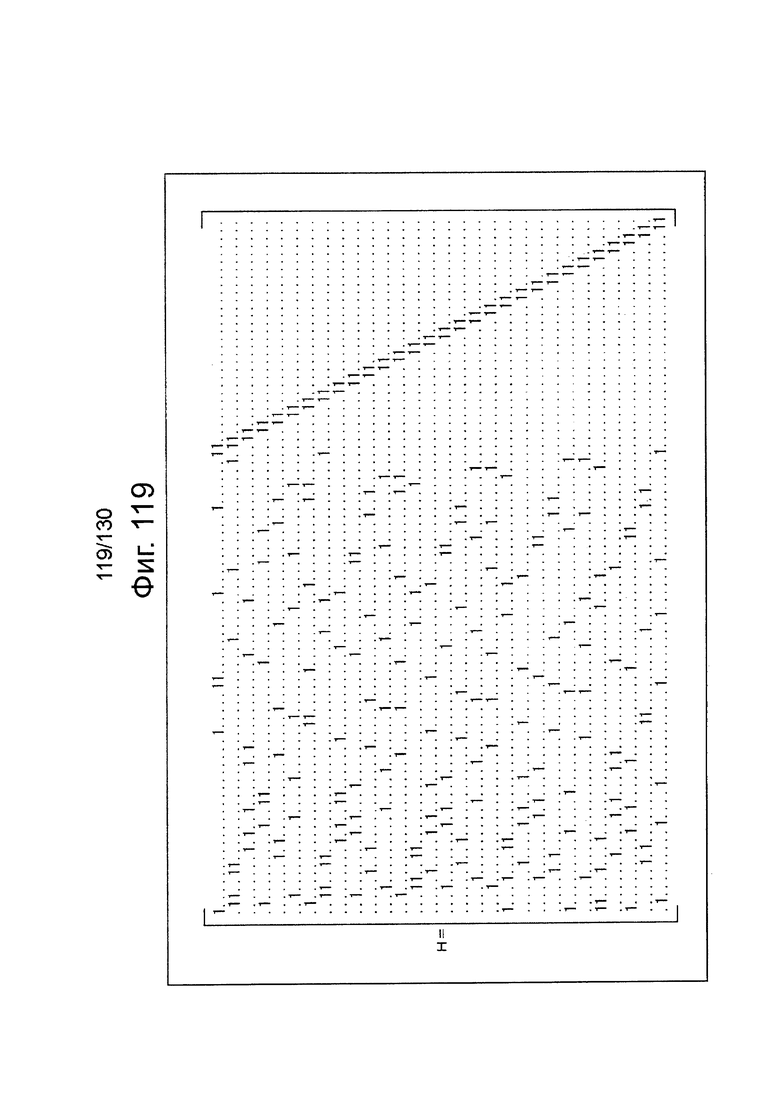

Фиг. 119 является иллюстрацией примера матрицы контроля четности LDPC-кода.

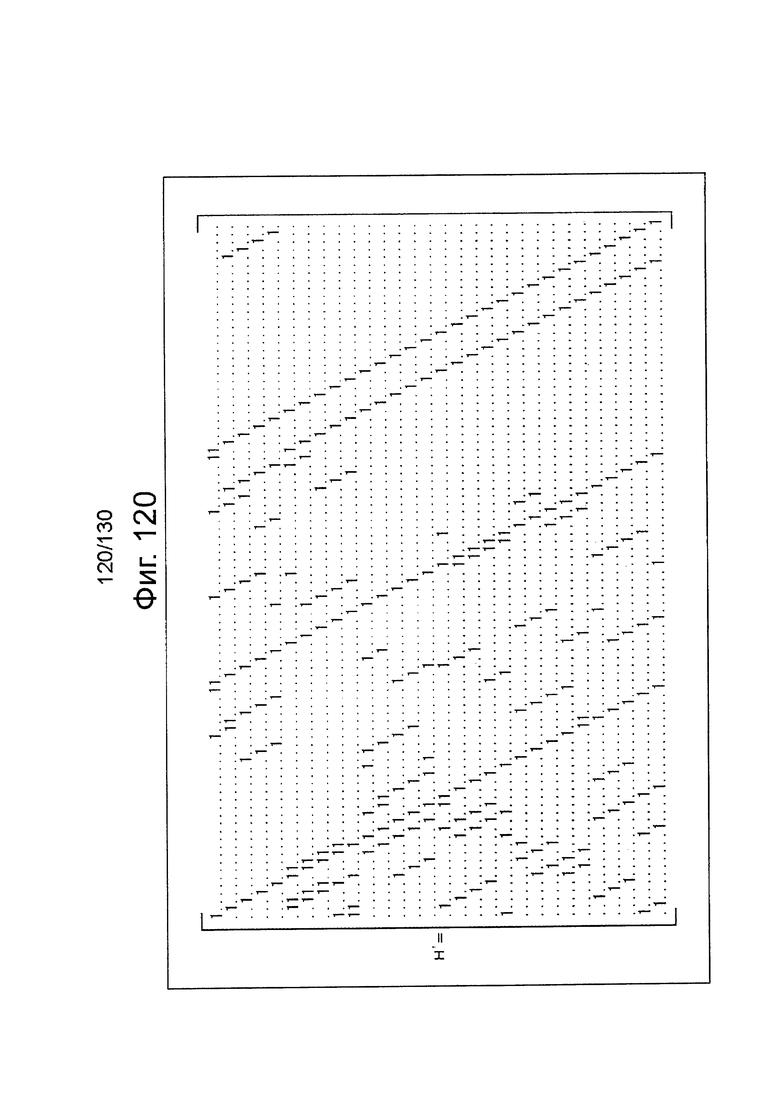

Фиг. 120 является иллюстрацией матрицы (преобразованной матрицы контроля четности), полученной путем выполнения замены строк и столбцов по отношению к матрице контроля четности.

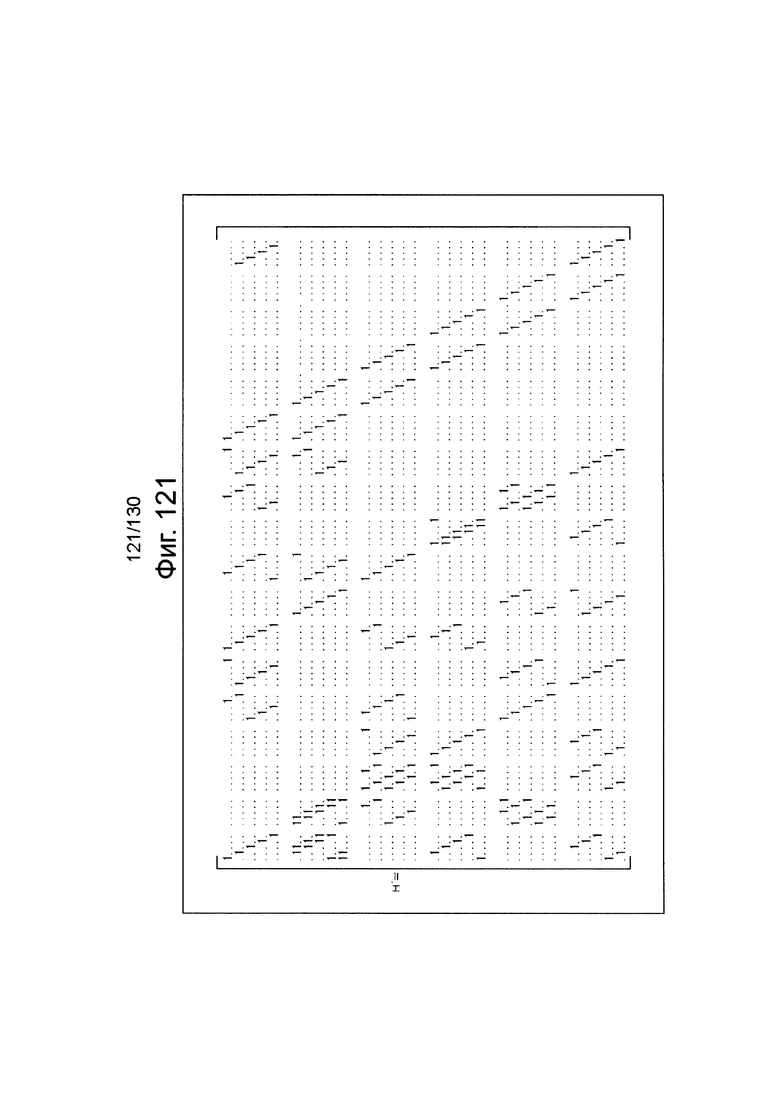

Фиг. 121 является иллюстрацией преобразованной матрицы контроля четности, разделенной на 5×5 блок.

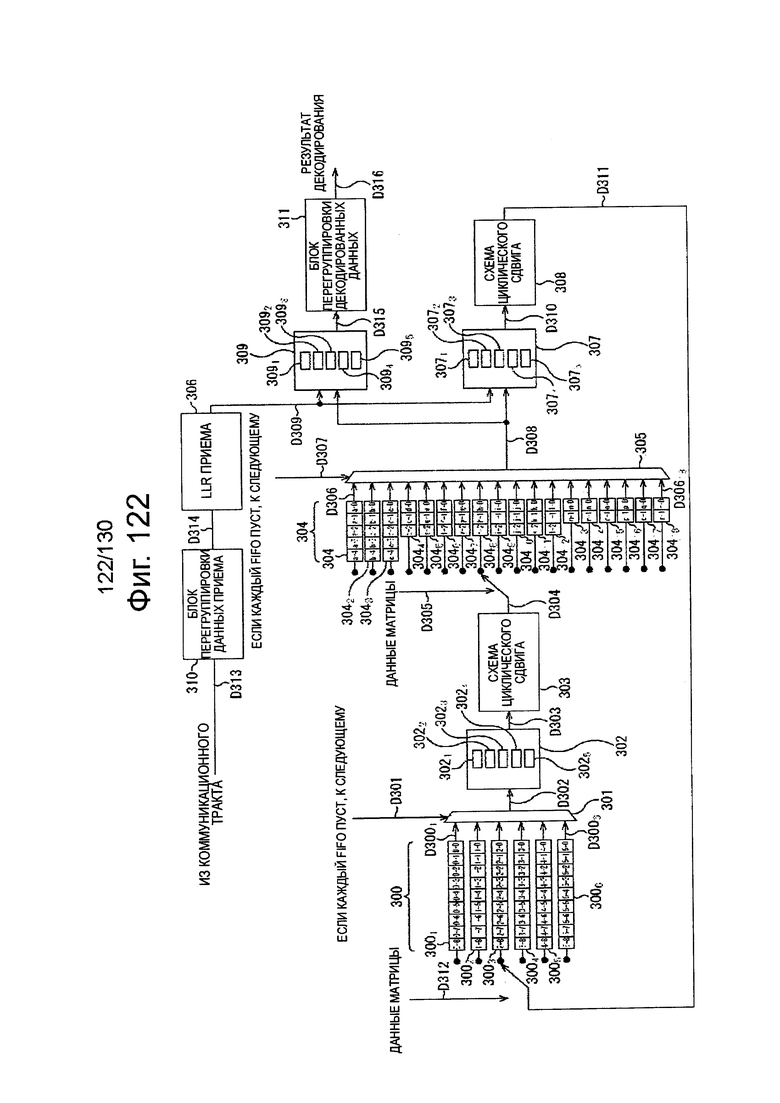

Фиг. 122 представляет собой блок-схему, иллюстрирующую пример конфигурации устройства декодирования, которое в совокупности выполняет операции Ρ узла.

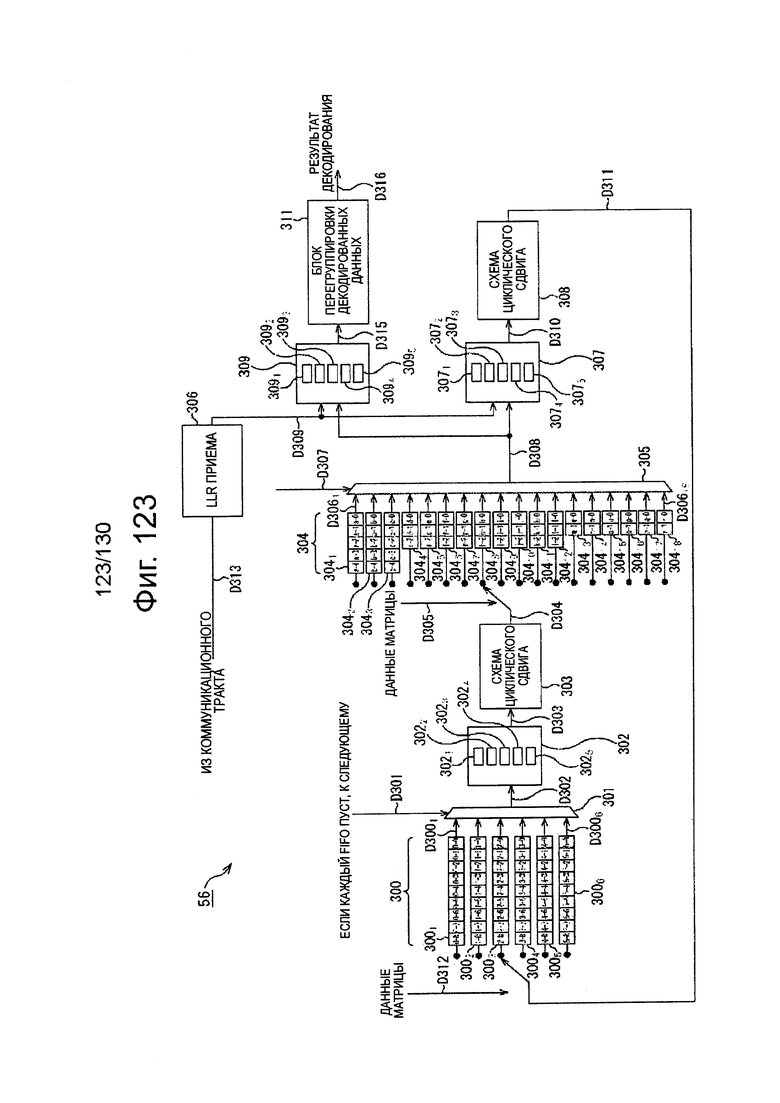

Фиг. 123 представляет собой блок-схему, иллюстрирующую пример конфигурации LDPC декодер 166.

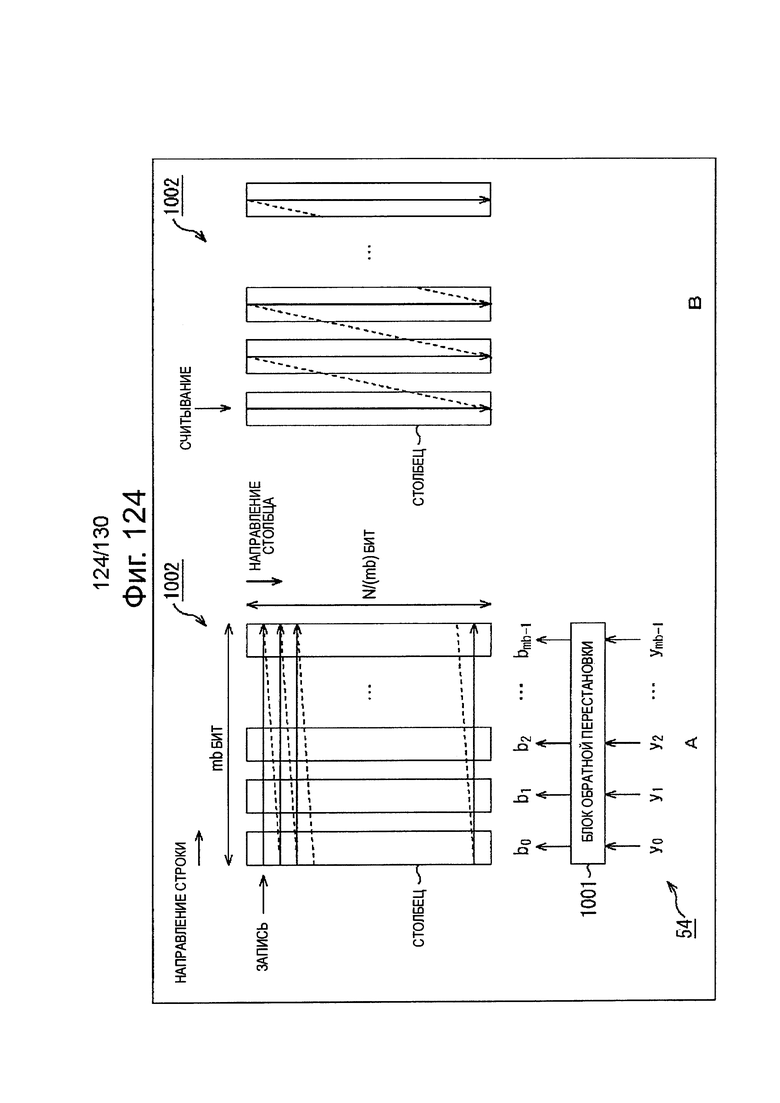

Фиг. 124 является иллюстрацией процесса обработки мультиплексора 54, составляющий битовый перемежитель 165.

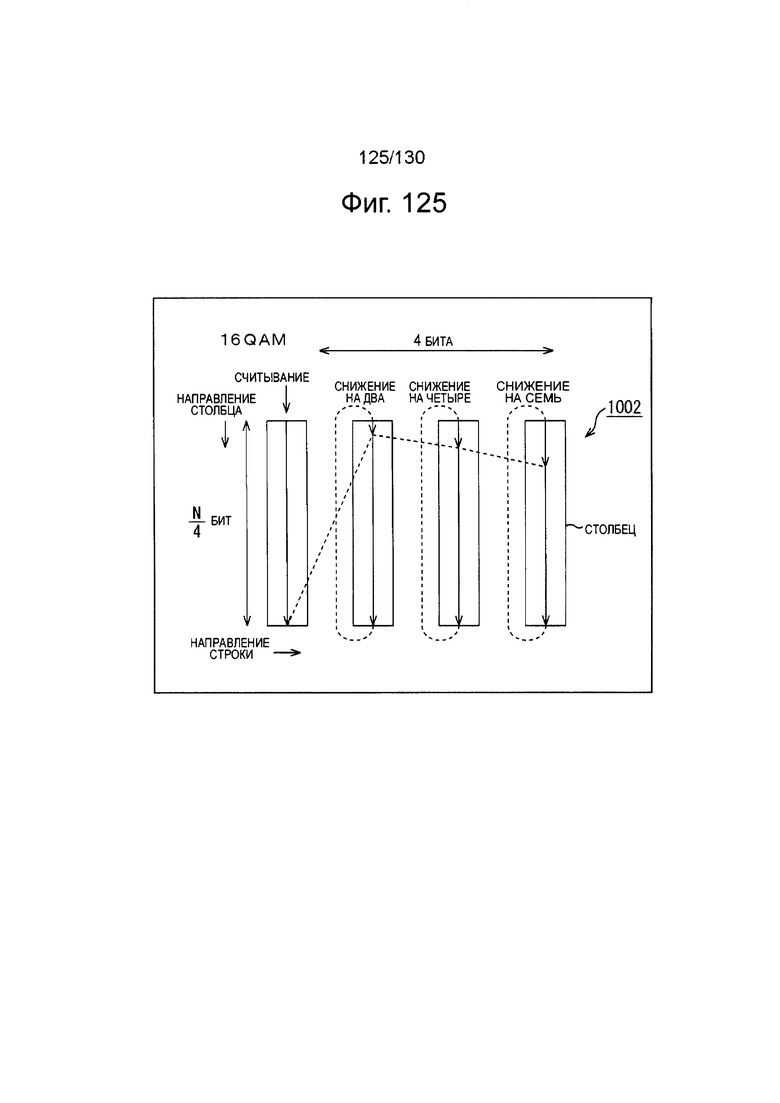

Фиг. 125 является иллюстрацией процесса обработки скручивания столбца деперемежителем 55.

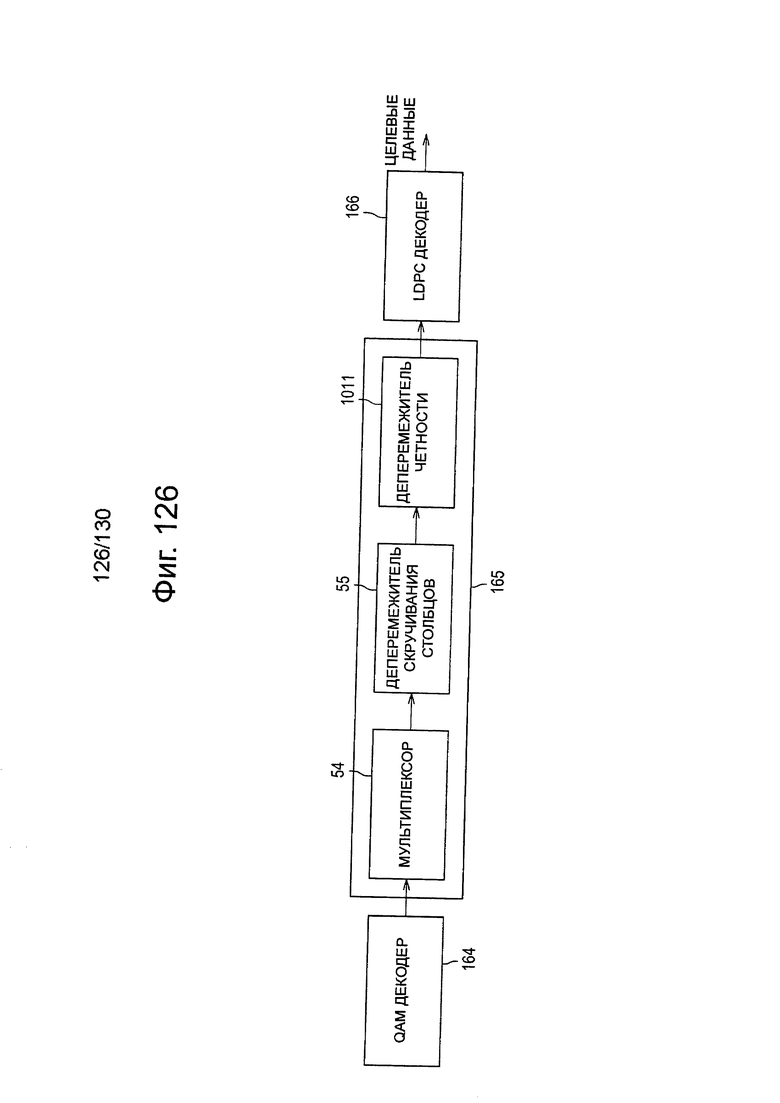

Фиг. 126 представляет собой блок-схему, иллюстрирующую другой пример конфигурации битового деперемежителя 165.

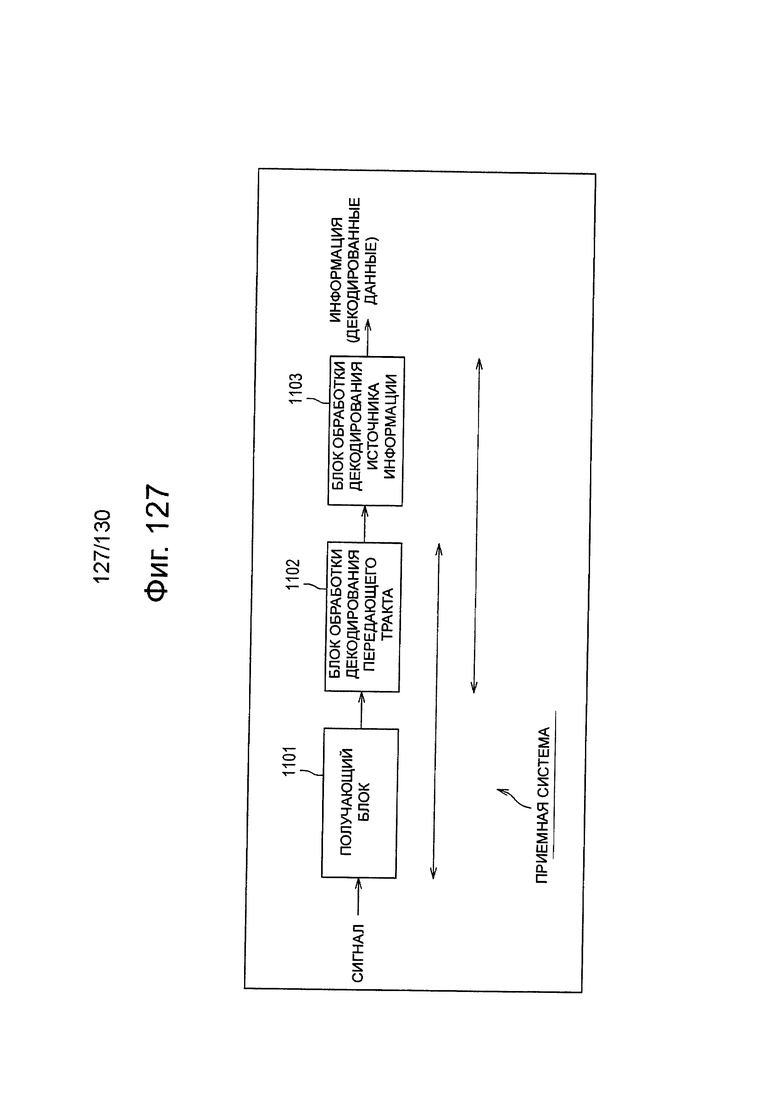

Фиг. 127 представляет собой блок-схему, иллюстрирующую первый пример конфигурации приемной системы, которая может быть применена к приемному устройству 12.

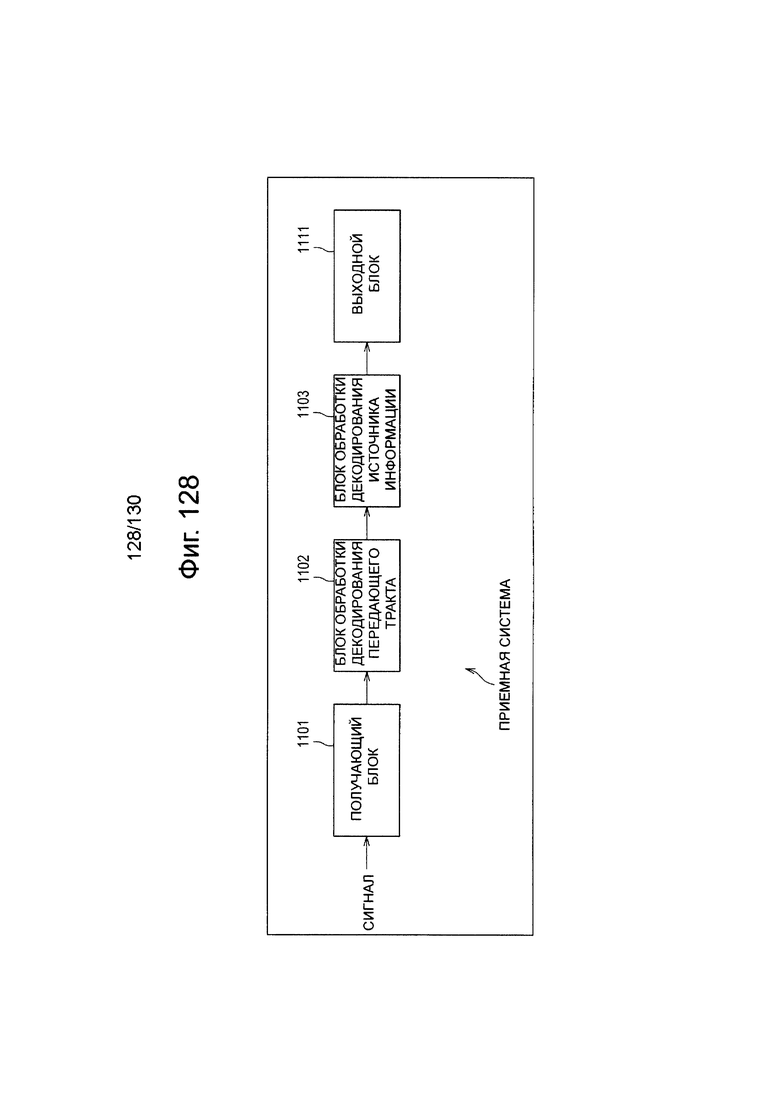

Фиг. 128 представляет собой блок-схему, иллюстрирующую второй пример конфигурации приемной системы, которая может быть применена к приемному устройству 12.

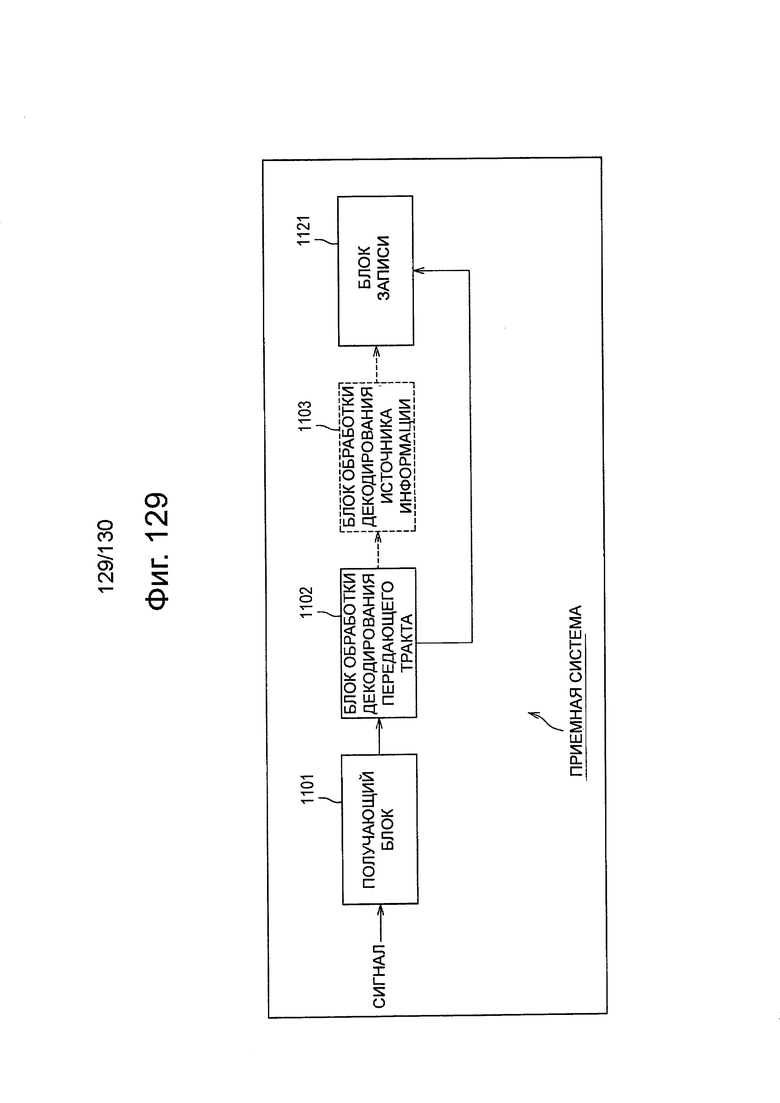

Фиг. 129 представляет собой блок-схему, иллюстрирующую третий пример конфигурации приемной системы, которая может быть применена к приемному устройству 12.

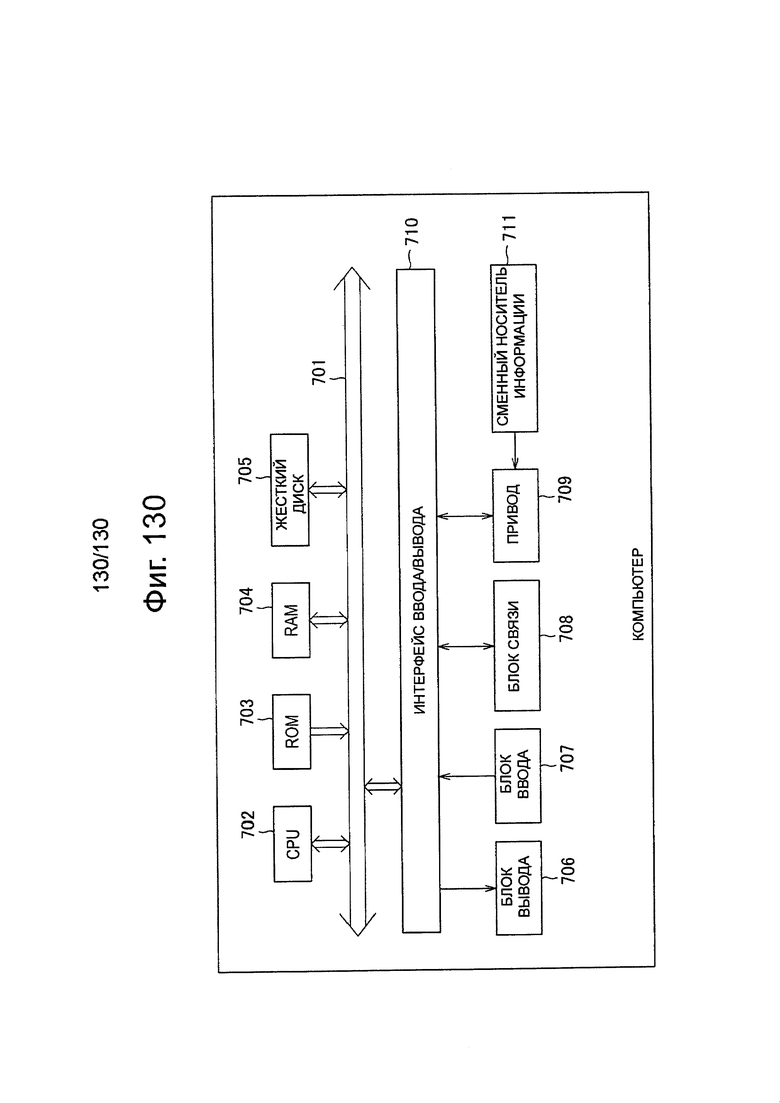

Фиг. 130 представлена блок-схема, иллюстрирующая пример конфигурации варианта осуществления компьютера, в которому применяется настоящее изобретение.

Осуществление изобретения

Пример конфигурации передающей системы, к которой применяется настоящее изобретение

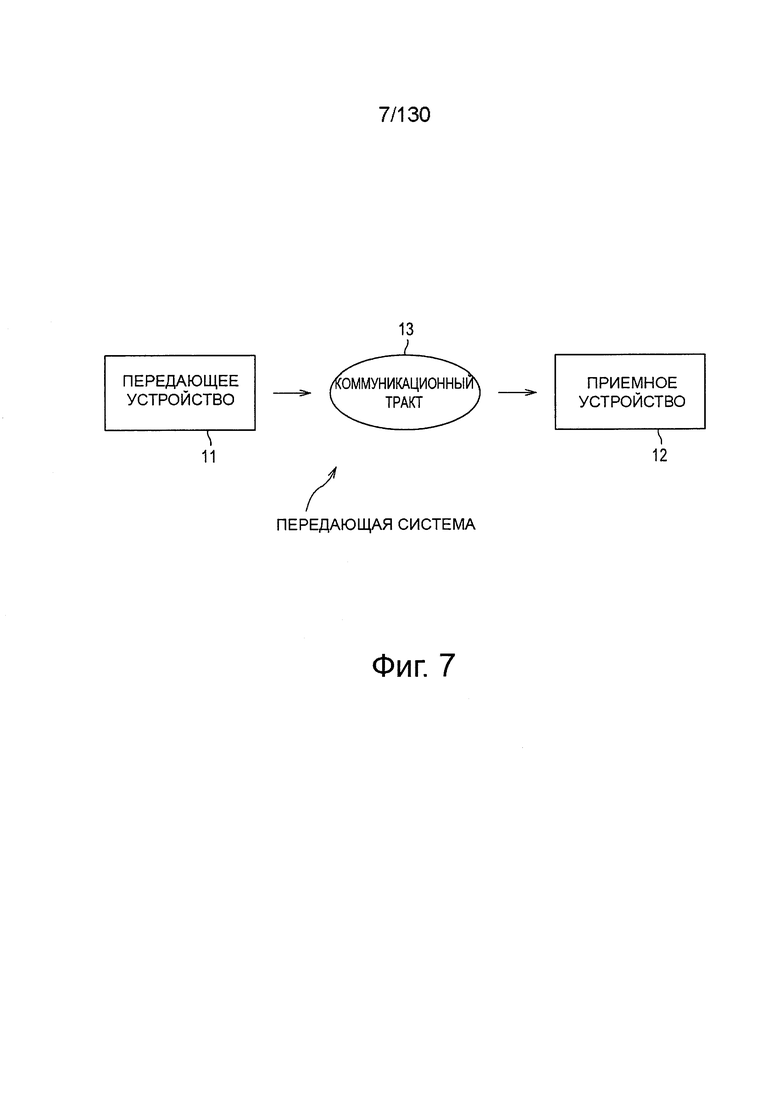

Фиг. 7 иллюстрирует пример конфигурации варианта осуществления передающей системы (системное средство логически объединяет множество устройств, и устройство каждой конфигурации может быть расположено или может быть не расположено в одном корпусе), к которой применяется настоящее изобретение.

Как показано на фиг. 7, передающая система включает в себя передающее устройство 11 и приемное устройство 12.

Например, передающее устройство 11 передает (транслирует) (доставляет) программы телевизионного вещания и так далее. То есть, например, передающее устройство 11 кодирует целевые данные, которые являются целевой передачей, например, данных изображения и аудиоданных в качестве программы в LDPC-кодах и, например, передает их через канал 13 связи, такой как спутниковой канал, посредством поверхностной волны и по кабелю (проводная схема).

Приемное устройство 12 принимает LDPC-код, переданный передающим устройством 11 по каналу 13 связи, декодирует LDPC-код, чтобы получить целевые данные, и выводит целевые данные.

В этом случае известно, что LDPC-код, используемый системой передачи, показанной на фиг. 7, демонстрирует очень высокую способность (аддитивный белый гауссов шум) канала связи.

Между тем, в канале 13 связи может быть сгенерировано внезапное возникновение ошибки или стирание. Особенно в случае, когда канал 13 связи представляет собой поверхностную волну, например, в OFDM (мультиплексирование с ортогональным частотным разделением каналов) системе, мощность конкретного символа может стать равной 0 (стирание) в соответствии с задержкой эха (каналы отличные от основного канала) при наличии многоканальной передачи, в которой D/U (соотношение желаемого и нежелательного) равно 0 дБ (мощность нежелательного сигнала = эхо равна мощности желаемой передачи = основного канала).

Во флаттере (канал связи, в котором задержка равна 0 и добавляется эхо, имеющее частоту Доплера), когда D/U равно 0 дБ, вся мощность символа OFDM в определенное время может становиться равной 0 (стирания) посредством частоты Доплера.

Кроме того, ошибки в канале передачи пакетных данных может быть сгенерирована из-за ситуации в проводной линии связи из приемного блока (не показано на чертежах) стороны приемного устройства 12, например, антенна, принимая сигнал от передающего устройства 11 и передавая его на приемное устройство 12, или при неустойчивости электропитания приемного устройства 12.

Между тем, при декодировании LDPC-кода в переменном узле, соответствующего столбца в матрицы H контроля четности и битового кода LDPC-кода, как показано на фиг. 5 и описано выше, выполняется операция переменного узла согласно выражению (1) с добавлением (приемное значение u0i) битового кода LDPC-кода. По этой причине, если возникает ошибка в битовом коде, используемом для операции переменного узла, то точность вычисленного сообщения снижается.

При декодировании LDPC-кода в узле проверки, операция узла проверки выражения (7) выполняется с использованием сообщения, вычисленного переменным узлом, подключенного к узлу проверки. По этой причине, если увеличивается количество узлов проверки, в которых генерируется ошибка (в том числе стирания) одновременно во (соответствующий битовых кодах LDPC-кодов) множестве подключенных переменных узлах, то производительность декодирования снижается.

То есть если два или более переменных узлов переменных узлов, соединенных с узлом проверки, одновременно подвержены стиранию, то узел проверки возвращает сообщение, в котором вероятность значения равно 0 и вероятность значения, равного 1, равны друг другу для всех переменных узлов. В этом случае, узел проверки, который возвращает сообщение равных вероятностей, не способствуют процессу декодирования (один набор операции переменного узла и операции узла проверки). В результате, необходимо увеличить количество повторений выполнения процесса декодирования, что вызывает снижение производительности декодирования и потребляемая мощность приемного устройства 12, которое выполняет декодирование LDPC-кода, увеличивается.

Таким образом, в системе передачи, показанной на фиг. 7, устойчивость к возникновению ошибки в канале передачи пакетных данных или стирания может быть повышена, при этом поддерживается производительность AWGN канала связи.

Пример конфигурации передающего устройства 11

Фиг. 8 является блок-схемой, иллюстрирующей пример конфигурации передающего устройства 11, показанного на фиг. 7.

В передающем устройстве 11, один или более входных потоков, соответствующих целевым данным, поставляются в адаптер/мультиплексор 111 для передачи данных в пакетном режиме.

Адаптер/мультиплексор 111 для передачи данных в пакетном режиме выполняет выбор режима и обработку, например, мультиплексирование одного или более входных потоков подаваемые в него, по мере необходимости, и поставляет данные, полученные как результат, в заполнитель 112.

Заполнитель 112 выполняет необходимую операцию дополнения нулями (вставку нулей) по отношению к данным, поставляемые из адаптера/мультиплексора 111 для передачи данных в пакетном режиме, и поставляет данные, полученные в результате в ВВ скремблер 113.

ВВ скремблер 113 выполняет скремблирование основной полосы частот (ВВ скремблирование) по отношению к данным, поставляемые из подстроечного конденсатора, и поставляет данные, полученные в результате в ВСН кодер 114.

ВСН кодер 114 выполняет ВСН кодирование по отношению к данным, поставленным из ВВ скремблера 113, и поставляет данные, полученные в результате, как LDPC целевые данные процесса кодирования LDPC, в LDPC-кодер 115.

LDPC-кодер 115 выполняет LDPC-кодирование согласно матрице контроля четности, в которой матрица четности является частью, соответствующей битовой четности LDPC-кода, приобретает ступенчатую структуру по отношению к LDPC целевым данным, поставленным из ВСН кодера 114, и выводит LDPC-код, в котором целевые данные LDPC являются информационными битами.

То есть, LDPC-кодер 115 выполняет кодирование LDPC для кодирования LDPC целевых данных с LDPC, такие как LDPC-код (соответствующий матрице контроля четности), определенные в заданном стандарте DVB-S.2, DVB-T 0,2, DVB-C.2 или тому подобное, и выводит полученный в результате заданный LDPC-код (соответствующий матрице контроля четности) или т.п.

LDPC-код, определенный в стандарте DVB-S.2, DVB-T.2 и DVB-C.2 является (Нерегулярный повторяющийся код накопления) IRA кодом и матрица четности матрицы контроля четности LDPC-кода приобретает ступенчатую структуру. Матрица четности и ступенчатая структура будет описана ниже. IRA код описан в протоколах "Нерегулярные повторяющиеся коды накопления", Н. Jin, A. Khandekar и R.J. McEliece 2-го Международного симпозиума по турбо кодам и смежным вопросам, стр. 1-8, сентябрь 2000 года, например.

LDPC-код, который вырабатывается LDPC-кодером 115, поставляется в битовый перемежитель 116.

Битовый перемежитель 116 выполняет перемежение бит, процесс которого будет описан позже, по отношению к LDPC-коду, поставленному из LDPC-кодера 115, и поставляет LDPC-код после перемежения битов в QAM кодер 117.

QAM кодер 117 отображает LDPC-код, подаваемый из битового перемежителя 116, в сигнальную точку, представляющую один символ ортогональной модуляции в блоке (символ блока) кодовых битов одного или нескольких битов LDPC-кода, и выполняет ортогональную модуляцию (многоуровневую модуляцию).

То есть, QAM кодер 117 выполняет отображение LDPC-кода, поставленного из битового перемежителя 116, на сигнальную точку, определенную с помощью способа модуляции, выполняющего ортогональную модуляцию LDPC-кода на IQ плоскости (IQ созвездие), определенной I осью, представляющая I составляющую той же фазы, что и несущая, Q осью, представляющая Q составляющую, ортогонально к несущей, и выполняет ортогональную модуляцию.

В этом случае, в качестве способа модуляции ортогональной модуляции, выполняемой QAM кодером 117, есть способы модуляции, включающие в себя способ модуляции, определенный стандартом DVB-S.2, DVB-T.2, DVB-C.2 или тому подобное, и другой способ модуляции, то есть, BPSK (двоичная фазовая манипуляция), QPSK (квадратурная фазовая манипуляция), 16APSK (Амплитудная фазовая манипуляция), 32APSK, 16QAM (квадратурная амплитудная модуляция), 64QAM, 256QAM, 1024QAM, 4096QAM, 4PAM (Амплитудно-импульсная модуляция) или тому подобное. В QAM кодере 117 выполняется ортогональная модуляция на основании способа модуляции, предварительно установленного в соответствии с операцией оператора передающего устройства 11.

Данные (отображаемый символ на сигнальной точке), полученные в результате обработки в QAM кодере 117, поступают на временной перемежитель 118.

Временной перемежитель 118 выполняет временное перемежение (чередование во временном направлении) в блоке символа по отношению к данным (символ), поставленным из QAM кодера 117, и поставляет полученные в результате данные в MISO/MIMO кодер (MISO/MIMO кодер) 119.

MISO/ΜIΜΟ кодер 119 выполняет пространственно-временное кодирование относительно данных (символ), поступающих из временного перемежителя 118, и поставляет данные в частотный перемежитель 120.

Частотный перемежитель 120 выполняет частотное перемежение (чередование в частотной области) в блоке символа по отношению к данным (символ), поставленным из MISO/MIMO кодера 119, и поставляет эти данные в блок 131 выделения ресурсов/компоновщик кадра.

С другой стороны, например, данные управления (сигнализация) для управления передачей, такие как ВВ сигнализация (сигнализация основной полосы) (ВВ заголовка), подается на ВСН кодер 121.

ВСН кодер 121 выполняет кодирование ВСН по отношению к сигнализации, поставленной на него, и поставляет данные, полученные в результате в LDPC-кодер 122, аналогично ВСН кодеру 114.

LDPC-кодер 122 устанавливает данные, поставленные из ВСН кодера 121, как LDPC целевые данные, выполняет процесс LDPC-кодирования по отношению к данным, и поставляет LDPC-код, полученный в результате, в QAM кодер 123, аналогично LDPC-кодеру 115.

QAM кодер 123 отображает LDPC-код, поставленный из LDPC-кодера 122, на сигнальную точку, представляющую один символ ортогональной модуляции в блоке (блок символа) кодовых битов одного или нескольких битов LDPC-кода, выполняет ортогональную модуляцию и поставляет данные (символ), полученные в результате, в частотный перемежитель 124, аналогично QAM кодеру 117.

Частотный перемежитель 124 выполняет частотное перемежение в блоке символа по отношению к данным (символ), поставленным из QAM кодера 123, и поставляет эти данные в блок 131 выделения ресурсов/компоновщик кадра, аналогично частотному перемежителю 120.

Блок 131 выделения ресурсов/компоновщик кадра вставляет символы пилот-сигналов на необходимые позиции данных (символов), поставленных из частотных перемежителей 120 и 124, конфигурирует кадр (например, кадр физического уровня (PL), Т2 кадр, С2 кадр и так далее), включающий в себя символы заданного количества, из данных (символов), полученных в результате, и поставляет кадр в блок 132 OFDM генерирования.

Блок 132 OFDM генерирования генерирует OFDM сигнал, соответствующий кадру, из кадра, поставленного из блока 131 выделения ресурсов/компоновщик кадра, и передает OFDM сигнал по каналу 13 связи (фиг. 7).

Здесь, например, передающее устройство 11 может быть выполнено с возможностью не включать в себя часть блоков, показанных на фиг. 8, таких как, временной перемежитель 118, MISO/MIMO кодер 119, частотный перемежитель 120 и частотный перемежитель 124.

Фиг. 9 иллюстрирует пример конфигурации битового перемежителя 116, показанного на фиг. 8.

Битовый перемежитель 116 является устройством обработки данных, которое перемежает данные и включает в себя перемежитель 23 четности, перемежитель 24 скрещивания столбцов и демультиплексор (DEMUX) 25. Здесь битовый перемежитель 116 может быть выполнен с возможностью не включать в себя один или оба перемежитель 23 четности и перемежитель 24 скрещивания столбцов.

Перемежитель 23 четности осуществляет перемежение четности для перемежения битов четности LDPC-кода, поставленного из LDPC-кодера 115, на позициях других битов четности и поставляет LDPC-код после перемежения четности в перемежитель 24 скрещивания столбцов.

Перемежитель 24 скрещивания столбцов осуществляет перемежение скрещивания столбцов по отношению к LDPC-коду, поступающего из перемежителя 23 четности, и подает LDPC-код после перемежения скрещивания столбцов на демультиплексор 25.

То есть, в QAM кодере 117, показанном на фиг. 8, кодовые биты одного или нескольких битов LDPC-кода сопоставляются на сигнальную точку, представляющая один символ ортогональной модуляции, и передаются.

В перемежителе 24 скрещивания столбцов выполняется перемежение скрещивания столбцов, процесс которого будет описан позже, как процесс обработки переупорядочения для перестановки кодовых битов LDPC-кода, поставленного из перемежителя 23 четности, так, что множество кодовых битов LDPC-кода, соответствующие 1 в любой одной строке матрицы контроля четности, используемой LDPC-кодером 115, не включены в состав одного символа.

Демультиплексор 25 выполняет процесс перестановки для перестановки позиций двух или более кодовых битов LDPC-кода для формирования символа по отношению к LDPC-коду, поставленного из перемежителя 24 скрещивания столбцов, и получает LDPC-код, в котором увеличена устойчивость к возникновению AWGN. Кроме того, демультиплексор 25 поставляет два или более кодовых битов LDPC-кода, полученные путем обработки обмена как символ, в QAM кодер 117 (фиг. 8).

Далее, фиг. 10, иллюстрирует матрицу H контроля четности, которая используется для LDPC-кодирования LDPC-кодером 115, как показано на фиг. 8.

Матрица H контроля четности становится LDGM (генераторная матрица низкой плотности) структурой и может быть представлена выражением H=[HA|HT] (матрица, в которой элементы информационной матрицы HA установлены слева от элементов и элементы матрицы HT контроля четности установлены справа от элементов), с использованием информационной матрицы HA части, соответствующей информационным битам среди кодовых битов LDPC-кода, и матрицы HT контроля четности, соответствующей битам четности.

В этом случае, количество битов информационных битов среди кодовых битов одного LDPC-кода (одно кодовое слово) и количество битов четности называют длиной К информации и длиной M четности, соответственно, и количество битов кодовых битов одного LDPC-кода называют длиной N (=К+М) кода.

Длина К информации и длина M четности LDPC-кода, имеющего определенную длину N кода, определяются скоростью кодирования. Матрица H контроля четности становится матрицей, в которой строка × столбец составляет Μ×N. Информационная матрица HA становится матрицей Μ×К и матрица HT четности становится матрицей Μ×M.

Фиг. 11 иллюстрирует матрицу HT четности в матрице H контроля четности LDPC-кода, определенного в стандарте DVB-S.2, DVB-T.2 и DVB-C.2.

Матрица HT четности матрицы H контроля четности LDPC-кода, определенного в стандарте DVB-T.2 и т.п., преобразовывается в матрицу ступенчатой структуры, в которой элементы 1 расположены ступенчато, как показано на фиг. 11. Вес строки матрицы HT четности становится равным 1 по отношению к первой строке и становится равным 2 по отношению к остальным строкам. Вес столбца становится равным 1 по отношению к последнему столбцу и становится равным 2 относительно остальных столбцов.

Как описано выше, LDPC-код матрицы H контроля четности, в которой матрица HT четности становится ступенчатой структурой, может легко генерироваться с использованием матрицы H контроля четности.

То есть, LDPC-код (одно кодовое слово) представлен вектором с строки и вектором столбца, полученного путем перестановки вектора строки, представленным CT. Кроме того, часть информационных битов вектора с строки, чтобы быть LDPC-кодом, представлена вектором А строки и часть битов четности представлена вектором Τ строки.

Вектор с строки может быть представлен выражением c=[А|Т] (вектор строки, в котором элементы вектора А строки, установлены слева от элементов и элементы вектора Τ строки установлены справа от элементов), используя вектор строки, соответствующий информационным битам, и вектор Τ строки, соответствующий битам четности.

В матрице Η контроля четности и вектор с=[А|Т] строки, соответствующий LDPC-коду, необходимо выполнить выражение HcT=0. Вектор Τ строки, который соответствует битам четности, составляющие вектор c=[А|Т] строки, удовлетворяющий выражению HcT=0, может быть последовательно вычислен путем установки элементов каждой строки на 0, последовательно (в порядке) из элементов первой строки вектора HcT столбца в выражении HcT=0, когда матрица HT четности матрицы Н=[НА|HT] контроля четности становится ступенчатой структурой, как показано на фиг. 11.

Фиг. 12 является иллюстрацией матрицы Η контроля четности LDPC-кода, определенного в стандарте DVB-T.2 или тому подобное.

Вес столбца становится равным X относительно КХ столбцов из первого столбца матрицы Η контроля четности LDPC-кода, определенного в стандарте DVB-T.2 или тому подобное, становится равным 3 по отношению к следующим K3 столбцам, становится равным 2 по отношению к следующим (М-1) столбцам и становится равным 1 по отношению к последнему столбцу.

В этом случае, KX+К3+М-1+1 равно кодовой длине N.

Фиг. 13 является иллюстрацией числа KX, К3 и M столбцов и веса X столбца по отношению к каждому значению скорости r кодирования LDPC-кода, определенного в стандарте DVB-T.2 или тому подобное.

В стандарте DVB-T.2 или т.п., определены LDPC-коды, которые имеют кодовые длины N из 64800 бит и 16200 бит.

Что касается LDPC-кода, имеющего кодовую длину N из 64800 битов, определены 11 скоростей кодирования (номинальные скорости) 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6, 8/9 и 9/10. Что касается LDPC-кода, имеющего кодовую длину N из 16200 бит, определены 10 скоростей кодирования 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 5/6 и 8/9.

Далее, кодовая длина N из 64800 битов упоминается как 64 кбит и кодовая длина N из 16200 упоминается как 16 кбит.

Что касается LDPC-кода, то известно, что частота возникновения ошибок низка в бите кода, соответствующего столбцу, вес которого велик в матрице H контроля четности.

В матрице H контроля четности, которая проиллюстрирована на фиг. 12 и 13, и определена в стандарте DVB-T.2 и т.п., вес столбца стороны заголовка (левая сторона) имеет тенденцию к увеличению. Таким образом, по отношению к LDPC-коду, соответствующему матрице H контроля четности, бит кода стороны заголовка имеет устойчивую тенденцию противостоять возникновению ошибок (способность противостоять возникновению ошибок) и кодовый бит стороны завершения, как правило, обладает слабой устойчивостью к возникновению ошибок.

Далее, фиг. 14 иллюстрирует пример компоновки (соответствующие сигнальные точки) 16 символов на IQ плоскости, когда выполняется 16QAM посредством QAM кодера 117, показанного на фиг. 8.

То есть, часть А фиг. 14 иллюстрирует символы 16QAM в DVB-T.2.

В 16QAM присутствует один символ, представленный 4 битами и 16 символами (=24). 16 символов расположены таким образом, что I направление × Q направление становится 4×4 квадратной формой, на основании оригинальной точки IQ плоскости.

Если (i+1)-й бит из старшего бита в битовой строке, представленный одним символом, представлен в виде бита yi, 4 бита, представленные одним символом 16QAM, могут быть представлены в виде битов y0, y1, y2 и y3 соответственно последовательно из самого старшего бита. Когда способ модуляции является 16QAM, 4 бита кодовых битов LDPC-кода становятся символом (значение символа) 4 бит с y0 по y3 (представлены в виде символов).

Часть В на фиг. 14 иллюстрирует битовую границу по отношению к каждому из 4 битов (в дальнейшем называется как символ битов) с y0 по y3, представленные символом 16QAM.

В этом случае, битовая граница по отношению к символу бита yi (на фиг. 14, i=0, 1, 2 и 3) означает границу символа, где символ бита yi становится равным 0, и символа, где символ бита yi становится равным 1.

Как показано на части В фиг. 14, только одно место Q оси IQ плоскости становится битовой границей по отношению к старшему символу бита y0 4 символов битов с y0 по y3, как представлено символом 16QAM, и только одно место I оси IQ плоскости становится битовой границей по отношению ко второму (второй от старшего бита) символу бита y1.

Что касается третьего символа бита y2, то два места из местоположения между первым и вторым столбцами с левой стороны, и место между третьим и четвертым столбцами среди 4×4 символов, становятся битовыми границами.

Что касается четвертого символа бита y3, то два места в месте между первой и второй строчками на верхней стороне, и место между третьей и четвертой строками, среди 4×4 символов, становятся битовыми границами.

В символе бита yi, который представлен символами, когда число символов, отдаленный от битовых границ, велико, то генерирование ошибки затрудненно (вероятность возникновения ошибки невелика), и когда число символов, приближенных к битовым границам, велико, то ошибка легко генерируется (вероятность возникновения ошибки высока).

Биты (имеющие высокую защищенность от возникновения ошибок), в которых возникновение ошибки затруднено, называются "сильными битами", и биты (имеющие слабую защищенность от возникновения ошибки), в которых ошибка легко генерируется, называются "слабыми битами" по отношению к 4 символам битов с y0 по y3 символа 16QAM, старший символ бита y0 и второй символ бита y1 становятся сильными битами и третий символ бита y2 и четвертый символ бита уз становятся слабыми битами.

Фиг. 15 до 17 иллюстрируют пример компоновки (соответствующие сигнальные точки) 64 символов на IQ плоскости, то есть, символы 16QAM в DVB-T.2, когда выполняется 64-QAM посредством QAM кодера 117, показанного на фиг. 8.

В 64QAM, один символ представляет 6 бит, и присутствуют 64 символов (=26). 64 символа расположены таким образом, что I направление × Q направление становится 8×8 квадратной формы, на основании исходной точки IQ плоскости.

Символ битов одного символа 64QAM может быть представлен как y0, y1, y2, y3, y4, и y5, последовательно от самого старшего бита. Когда способ модуляции является 64QAM, 6 битов кодовых битов LDPC-кода становятся символом символа битов с y0 по y5 6 битов.

В этом случае, фиг. 15 иллюстрирует битовую границу по отношению к каждому из старшего символа бита y0 и второму символу бита y1 среди символа битов с y0 по y5 символа 64QAM. Фиг. 16 иллюстрирует битовую границу по отношению к каждому третьему символу бита y2 и четвертому символа бита y3, и на фиг. 17 иллюстрирует битовую границу по отношению к каждому пятому символу бита y4 и шестому символу бита y5.

Как показано на фиг. 15, битовая граница по отношению к каждому старшему символу бита y0 и второму символу бита y1 занимает одно место. Как показано на фиг. 16, битовые границы по отношению к каждому третьему символу бита y2 и четвертому символу бита y3 занимают два места. Как показано на фиг. 17, битовые границы по отношению к каждому пятому символу бита y4 и шестому символу бита y5 занимают четыре места.

Таким образом, по отношению к символу битов с y0 по y5 символа 64QAM, старший символ бита y0 и второй символ бита y1 становятся сильными битами и третий символ бита y2 и четвертый символ бита y3 становятся следующими сильными битами. Кроме того, пятый символ бита y4 и шестой символ бита y5 становятся слабыми битами.

Как показано на фигурах 14ис 15 до 17, очевидно, что по отношению к символу битов символа ортогональной модуляции, верхние биты имеют тенденцию становиться сильными битами и нижние биты имеют тенденцию становиться слабыми битами.

Фиг. 18 является иллюстрацией примера расположения на IQ плоскости (соответствующие сигнальные точки) 4 символов в случае, когда используется спутниковое вещание в качестве канала 13 связи (фиг. 7), и QPSK выполняется в QAM кодере 117, показанного на фиг. 8, то есть, например, является иллюстрацией символов QPSK в DVB-S.2.

В QPSK DVB-S.2, символ отображается на любой из 4 сигнальных точках на окружности, где радиус p центрируется на исходной IQ плоскости.

Фиг. 19 является иллюстрацией примера расположения на плоскости IQ 8 символов в случае, когда используется спутниковое вещание в качестве канала 13 связи (фиг. 7) и 8PSK выполняется в QAM кодере 117, показанного на фиг. 8, то есть, например, иллюстрацией символов 8PSK в DVB-S.2.

В 8PSK в DVB-S.2, символ отображается на любой из 8 сигнальных точках на окружности, где радиус p центрируется на исходной IQ плоскости.

Фиг. 20 показывает пример расположения на плоскости IQ 16 символов в случае, когда используется спутниковое вещание в качестве канала 13 связи (фиг. 7) и 16APSK выполняется в QAM кодере 117, показанного на фиг. 8, то есть, например, иллюстрацией символов 16APSK DVB-S.2.

Часть А фиг. 20 показывает пример расположения сигнальных точек 16APSK DVB-S.2.

В 16APSK из DVB-S.2, символ отображается на любой из 16 сигнальных точках 4 сигнальных точек на окружности, радиус которой центрирования на исходной IQ плоскости равен R1, и на 12 сигнальных точках окружности, радиус которой является R2 (>R1).

Часть В на фиг. 20 иллюстрирует γ=R2/R1, что являются отношением радиусов R2 и R1 в компоновке сигнальных точек 16APSK из DVB-S.2.

В схеме расположения сигнальных точек 16APSK DVB-S.2, коэффициент γ радиусов R2 и R1 изменяется в зависимости от скорости кодирования.

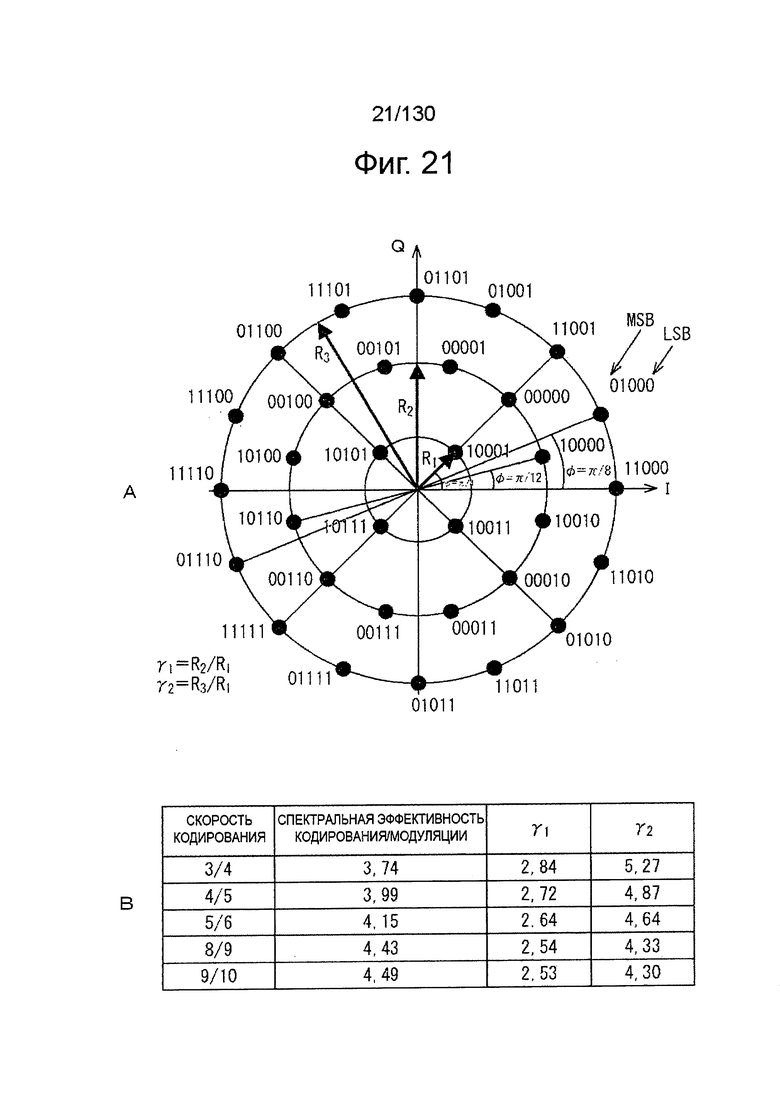

Фиг. 21 показывает пример расположения на плоскости IQ 32 символов в случае, когда используется спутниковое вещание в качестве канала 13 связи (фиг. 7) и 32APSK выполняется в QAM кодере 117, показанного на фиг. 8, то есть, например, иллюстрацией символов 32APSK в DVB-S.2.

Часть А фиг. 21 показывает расположение сигнальных точек 32APSK DVB-S.2.

В 32APSK DVB-S.2, символ отображается на любой из всех 32 сигнальных точек 4 сигнальных точек на окружности, радиус которой центрирован на исходной IQ плоскости и равен R1, 12 сигнальных точек на окружности круга с радиусом R2 (>R1) и 16 сигнальных точек на окружности, радиус которой равен R3 (>R2).

Часть В на фиг. 21 иллюстрирует γ1=R2/R1, что является соотношением радиусов R2 и R1 в схеме расположения сигнальных точек 32APSK DVB-S.2 и γ2=R3/R1, что является соотношением радиусов R3 и R1.

В схеме расположения сигнальных точек 32APSK DVB-S.2, коэффициент γ1 радиусов R2 и R1, и коэффициент γ2 радиусов R3 и R1 варьируются в зависимости от скорости кодирования.

Даже для символов битов из символов каждой квадратурной модуляции (QPSK, 8PSK, 16APSK и 32APSK) DVB-S.2, как показано расположение сигнальных точек на фигурах с 18 по 21, аналогичен случаям, показанным на фигурах с 14 по 17, есть сильные биты и слабые биты.

Как описано на фигурах 12 и 13, по отношению к LDPC-коду, вырабатываемого LDPC-кодером 115 (фиг. 8), присутствуют сильные кодовые биты и слабые кодовые биты.

Как показано на фигурах с 14 по 21, по отношению к символу битов символа ортогональной модуляции, выполненной QAM кодером 117, присутствуют сильные биты и слабые биты.

Поэтому, если кодовые биты LDPC-кода, являющиеся сильными по отношению ошибки, выделяются на слабый символ битов символа ортогональной модуляции, то толерантность по отношению к ошибке снижается в целом.

Таким образом, предлагается, чтобы перемежитель, который перемежает кодовые биты LDPC-кода так, чтобы кодовые биты LDPC-кода, являющиеся слабыми по отношению к ошибке, были выделены на сильные биты (символ битов) символа ортогональной модуляции.

Демультиплексор 25, показанный на фиг. 9, можно выполнить процесс обработки перемежителя.

Фиг. 22 является иллюстрацией процесса обработки демультиплексора 25, показанного на фиг. 9.

То есть, часть А фиг. 18 иллюстрирует пример функциональной конфигурации демультиплексора 25.

Демультиплексор 25 включает в себя память 31 и блок 32 перестановки.

LDPC-код поставляется из LDPC-кодера 115 в память 31.

Память 31 имеет емкость для хранения мб битов в строке (поперечное направление) и хранит N / (Мб) битов в столбце (продольное направление). Память 31 записывает поставленные кодовые биты LDPC-кода в направлении столбцов, считывает кодовые биты в направлении строк, и поставляет кодовые биты в блок 32 перестановки.

В этом случае, N (= длина К информации + длина M четности) представляет собой кодовую длину LDPC-кода, как описано выше.

Кроме того, m представляет собой число бита кодовых битов LDPC-кода, которое становится одним символом, и b представляет собой коэффициент, который является заранее определенным положительным целым числом, и используется для выполнения интегрального умножения m. Как описано выше, демультиплексор 25 отображает в символической форме кодовые биты LDPC-кода. Однако множитель b представляет собой количество символов, полученных с помощью одноразовой символизации демультиплексора 25.

Часть А фиг. 22 иллюстрирует пример конфигурации демультиплексора 25 в случае, когда способ модуляции является 64QAM или тому подобное, в котором отображение выполняется на любую из 64 сигнальных точек и, следовательно, номер m бита кодовых битов LDPC-кода становятся одним символом, равным 6 битам.

В части А фиг. 22, множитель b становится 1. Таким образом, память 31 имеет емкость, где направление столбца × направление строки равно N/(6×1)×(6×1) бит.

В этом случае область хранения памяти 31, где направление строки равно 1 бит и проходит в направлении столбцов, соответственно называют как столбец. В части А на фиг. 22, память 31 включает в себя 6 (=6×1) столбцов.

В демультиплексоре 25, написание кодовых битов LDPC-кода в направлении вниз (направление столбца) из верхней части столбцов, составляющих память 31, выполняется в направлении столбцов в правом направлении с левой стороны.

Если запись кодовых битов заканчивается в нижней части правого столбца, то кодовые биты считываются в блоке из 6 битов (МБ бит) в направлении строки из первой строки всех столбцов, составляющих память 31, и подается в блок 32 перестановки.

Блок 32 перестановки выполняет перестановку позиций кодовых битов из 6 бит из памяти 31, и выводит 6 битов, полученных в результате, как 6 символов бит y0, y1, y2, y3, y4 и y5, представляя один символ 64QAM.

То есть, кодовые биты из mb битов (в данном случае, 6 бит) считываются из памяти 31 в направлении строк. Однако, если i-й (i=0, 1, … и mb - 1) бит от старшего бита кодовых битов mb битов, считанных из памяти 31, представлен как бит bi, то кодовые биты 6 битов, которые считываются из памяти 31 в направлении строк, могут быть представлены как биты b0, b1, b2, b3, b4 и b5 последовательно от самого старшего бита.

С учетом весов столбцов, описанных на фиг. 12 и 13, кодовый бит в направлении бита b0 становится кодовым битом сильным для ошибок и кодовый бит в направлении бита b5 становится кодовым битом слабым для ошибки.

В блоке 32 перестановки, выполняется процесс перестановки позиций кодовых битов с b0 go b5 из 6 битов памяти 31, таким образом, что кодовые биты слабые для ошибки среди кодовых битов с b0 по b5 6 битов памяти 31, выделяются на сильные биты среди символа битов с y0 по y5 одного символа 64QAM.

В этом случае, как способы перестановки кодовых битов с b0 по b5 из 6 битов из памяти 31, и выделения кодовых битов с b0 по b5 6 битов на символ 6 битов с y0 по y5, представляя символ 64QAM, отдельные компании предлагают различные способы.

Часть В на фиг. 22 иллюстрирует первый способ перестановки, часть С на фиг. 22 иллюстрирует второй способ перестановки и часть D на фиг. 22 иллюстрирует третий способ перестановки.

С части В на фиг. 22 по часть D на фиг. 22 (и на фиг. 23, которая будет описана позже), сегмент соединительной линии битов bi и yi означает, что кодовый бит bi выделен на символ бита yj символа (перестановленный с позиции символа бита yj).

В качестве первого способа перестановки, показанного на части В на фиг. 22, предлагается применять любой один из трех способов перестановки. В качестве второго способа перестановки, показанного на части С на фиг. 22, предлагается применять любой из двух способов перестановки.

В качестве третьего способа перестановки, показанного на части D на фиг. 22, предлагается последовательно выбирать шесть видов способа перестановки и использовать способ перестановки.

Фиг. 23 иллюстрирует пример конфигурации демультиплексора 25 в случае, когда способ модуляции представляется собой 64QAM или тому подобное и четвертый способ перестановки, в котором отображение выполняется на любую из 64 сигнальных точек (таким образом, число m кодового бита кодовых битов LDPC-кода, отображенного на один символ равно 6 битам, как также показано на фиг. 22) и множитель b равен 2.

Когда множитель b равен 2, то память 31 имеет емкость, в которой направление столбец × направление строки равно N/(6×2)×(6×2) битов и включает в себя 12 (=6×2) столбцов.

Часть А фиг. 23 иллюстрирует последовательность написания LDPC-кода в память 31.

В демультиплексоре 25, как показано на фиг. 22, написание кодовых битов LDPC-кода в направлении вниз (направлении столбца) из верхней части столбцов, составляющие память 31, выполняется в направлении столбцов в правом направлении с левой стороны.

Если запись кодовых битов заканчивается в нижней части самого правого столбца, то кодовые биты считываются в блок из 12 битов (МБ бит) в направлении строки из первой строки всех столбцов, составляющих память 31, и подаются в блок 32 перестановки.

Блок 32 перестановки выполняет перестановку позиций кодовых битов 12 битов из памяти 31 с помощью четвертого способа перестановки, и выдает 12 битов, полученные в результате, как 12 битов, представляющие два символа (b символы) 64QAM, т.е., шесть символов бит y0, y1, y2, y3, y4 и y5, представляя один символ 64QAM, и шесть символа битов y0, y1, y2, y3, y4 и y5, представляющие следующий один символ.

В этом случае, часть В на фиг. 23 иллюстрирует четвертый способ перестановки, осуществляемый блоком 32 перестановки, как показано на части А фиг. 23.

Когда множитель b равен 2 (или 3 и более) при выполнении процесса перестановки, кодовые биты mb битов выделяются на символ битов мб битов b последовательных символов. В последующем описании, включающее в себя описание фиг. 23, (i+1)-й бит из старшего бита символа битов mb битов b последовательных символов, представлен как бит (символ бита) yi, для удобства объяснения.

Кодовые биты, которые являются подходящими для перестановки, то есть, для улучшения частоты появления ошибок в AWGN коммуникационном тракте, отличается в зависимости от скорости кодирования или кодовой длины LDPC-кода и способа модуляции.

Перемежение битов четности

Далее будет приведено описание процесса перемежения битов четности посредством перемежителя 23 четности, показанного на фиг. 9, со ссылкой на фигуры с 24 по 26.

Фиг. 24 иллюстрирует (часть) графа Таннера матрицы контроля четности LDPC-кода.

Как показано на фиг. 24, если множество, например, два переменные узла среди (соответствующие кодовые биты) переменных узлов, соединенных с узлом проверки, одновременно имеют ошибку, такую как стирание, то узел проверки возвращает сообщение, в котором значение вероятности равно 0, и вероятность того, что значение составляет 1, равны друг другу, во все переменные узлы, соединенные с узлом проверки. По этой причине, если множество переменных узлов, подключенных к тому же узлу проверки, одновременно стираются, производительность процесса декодирования снижается.

Между тем, LDPC-код, который выводится LDPC-кодером 115, показанным на фиг. 8, и определен в стандарте DVB-S.2 или тому подобное, является IRA кодом и матрица HT четности матрицы H контроля четности приобретает ступенчатую структуру, как показано на фиг. 11.

Фиг. 25 иллюстрирует матрицу HT четности со ступенчатой структурой и граф Таннера, соответствующий матрицу HT четности.

То есть, часть А на фиг. 25 иллюстрирует матрицу HT четности со ступенчатой структурой и часть В на фиг. 25 иллюстрирует граф Таннера, соответствующий матрице HT четности на части А фиг. 25.

В матрице HT четности со ступенчатой структурой, элементы 1 расположены рядом в каждой строке (за исключением первой строки). Таким образом, в графе Таннера матрицы HT четности два соседних переменных узла, соответствующие столбцу двух соседних элементов, в которых значение матрицы HT четности равно 1, подключены к тому же узлу проверки.

Поэтому, когда биты четности, соответствующие двух вышеупомянутых смежным переменным узлам, имеют ошибки одновременно ошибку в канале передачи пакетных данных и стирания и так далее, узел проверки, подключенный к двум переменным узлам (переменные узлы обнаруживают сообщение посредством использования битов четности), соответствующие этим двум битами четности, которые имеют ошибки, возвращает сообщение о том, что вероятность со значением 0 и вероятность со значением 1 равны, на переменные узлы, связанные с узлом проверки, и, следовательно, производительность декодирования снижается. Кроме того, когда длина пакета (номер бита битов четности, которые постоянно имеют ошибки) становится большой, число узлов проверки, которые возвращают сообщение равных вероятностей, увеличивается и производительность декодирования снижается.

Таким образом, перемежитель 23 четности (фиг. 9) выполняет перемежение четности битов четности LDPC-кода из LDPC-кодера 115 на позиции других битов четности, чтобы предотвратить снижение эффективности процесса декодирования.

Фиг. 26 иллюстрирует матрицу HT четности матрицы H контроля четности, соответствующей LDPC-коду после перемежения четности, выполняемой перемежителем 23 четности, показанного на фиг. 9.

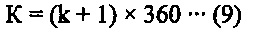

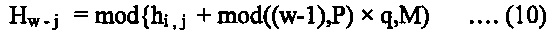

В этом случае, информационная матрицы НА матрицы H контроля четности, соответствующая LDPC-коду, который вырабатывается LDPC-кодером 115, и определена в стандарте DVB-S.2 и т.п. становится циклической структурой.