Изобретение относится к области вычислительной технике, а именно к микропроцессорам и микроконтроллерам для встраиваемых приложений.

В микропроцессорах или микроконтроллерах для встраиваемых приложений при прерывании программы или переходе к подпрограмме требуется полное или частичное сохранение и последующее восстановление контекста вычислительного процесса, характеризующегося ресурсами ядра процессора.

Контекст вычислительного процесса включает такие ресурсы как значения счетчика команд, регистра состояния процессора, регистров общего назначения и ряда других регистров.

Известен процессор КР1878ВЕ1 «ТЕСЕЙ» (КР1878ВЕ1. 8-разрядный RISC-микроконтроллер. Техническое описание. Система программирования и отладки. ОАО «Ангстрем») с поддержкой возможности переключения контекста вычислительного процесса.

Процессор «ТЕСЕЙ» содержит арифметико-логическое устройство, счетчик команд, память команд, память данных, регистр состояния процессора, контроллер прерываний и исключительных ситуаций, блок выборки, дешифрации и исполнения команд, файлы виртуальных регистров.

Данный процессор использует четыре сегмента адресации памяти данных, позволяющие, в частности, реализовать относительно простое сохранение переменных прерванной или вызывающей программы. При этом процессор обрабатывает данные из ряда собственных файлов виртуальных регистров, отображающих соответствующий ряд сегментов памяти данных. Адресуемыми регистрами контекста являются, в частности, регистры адресов указанных сегментов памяти данных.

Переключение контекста вычислительного процесса обеспечивается использованием отдельного аппаратного стека для хранения адресов возврата из подпрограмм и прерываний. Для сохранения значений служебных регистров адресации операндов и регистра состояния процессора используется отдельный аппаратный стек данных.

Способ переключения контекста вычислительного процесса в процессоре «ТЕСЕЙ» при прерывании программы или переходе к подпрограмме характеризуется тем, что при прерывании или поступлении команды перехода к подпрограмме сохраняют текущее значение счетчика команд процессора, текущее значение регистра состояния процессора и значения адресуемых регистров контекста, а восстановление контекста вычислительного процесса осуществляют в обратной последовательности.

Однако для сохранения адресов всех сегментов памяти данных активного процесса необходимо подать процессору ряд команд для сохранения каждого сегмента в отдельности. Так как каждая команда требует выборки, дешифрации и исполнения, то ресурсы процессора при переключении контекста вычислительного процесса используются с излишними затратами.

Задачей заявленного изобретения является оптимизация использования ресурсов процессора при переключении контекста вычислительного процесса.

Технический результат при этом заключается в увеличении скорости переключения контекста задач и процедур при меньшем количестве использованных аппаратных ресурсов.

Данный технический результат обеспечивается способом переключения контекста вычислительного процесса при прерывании программы или переходе к подпрограмме реализующим данный способ процессором с переключением вычислительного процесса и способом сохранения и восстановления регистров процессора при переключении контекста вычислительного процесса.

Технический результат достигается за счет того, что согласно способу переключения контекста вычислительного процесса в процессоре при прерывании программы или переходе к подпрограмме процессор выполнен с возможностью обработки данных из ряда собственных файлов виртуальных регистров, отражающих соответствующий ряд сегментов памяти данных. Причем при прерывании или поступлении команды перехода к подпрограмме сохраняют текущее значение счетчика команд процессора, текущее значение регистра состояния процессора и значения адресуемых регистров контекста. Восстановление контекста вычислительного процесса осуществляют в обратной последовательности. Адресуемые регистры контекста сохраняют или восстанавливают группами, причем регистры базовых адресов всех файлов виртуальных регистров входят в одну группу.

Процессор с переключением контекста вычислительного процесса содержит арифметико-логическое устройство (АЛУ), счетчик команд, память команд, память данных, регистр состояния процессора, контроллер прерываний и исключительных ситуаций, блок выборки, дешифрации и исполнения команд, файлы виртуальных регистров. Причем данный процессор также содержит стек контекста, выполненный с возможностью хранения полного контекста вычислительного процесса. Стек контекста связан своими входами-выходами со счетчиком команд, регистром состояния процессора, входом-выходом файлов виртуальных регистров. Каждый регистр стека контекста выполнен с возможностью хранения значений регистров любой из групп регистров, характеризующих контекст или значения счетчика команд процессора и значения регистра состояния процессора. Процессор выполнен с возможностью дешифрации и исполнения команды с кодом 00001010000000NN как команды для сохранения регистров, характеризующих контекст, и с возможностью дешифрации и исполнения команды с кодом 0000101001MMMMNN как команды для восстановления ранее сохраненных регистров, характеризующих контекст, где каждое N и М имеет значение логического 0 или 1.

В части способа сохранения и восстановления регистров процессора при переключении контекста вычислительного процесса процессор выполнен с возможностью дешифрации и исполнения команды с кодом 00001010000000NN как команды для сохранения разрядов регистров процессора, содержащих элементы контекста вычислительного процесса, и с возможностью дешифрации и исполнения команды с кодом 0000101001MMMMNN как команды для восстановления разрядов ряда ранее сохраненных регистров процессора, содержащих элементы контекста вычислительного процесса, где каждое N и М имеет значение логического 0 или 1. Для сохранения или восстановления ряда регистров процессора, характеризующих контекст вычислительного процесса, процессору подают команды с кодом 00001010000000NN или 0000101001MMMMNN соответственно.

В частных случаях своей реализации заявленное изобретение дополнительно характеризуется тем, что в способе переключения контекста вычислительного процесса в процессоре при прерывании программы или при переходе к подпрограмме адресуемыми регистрами контекста являются, в частности, регистры указания адресов файлов виртуальных регистров, регистры режимов работы и регистры данных.

При этом регистрами указания адресов файлов виртуальных регистров являются, в частности, регистр базового адреса первого файла виртуальных регистров (WA), регистр базового адреса второго файла виртуальных регистров (WB), регистр базового адреса третьего файла виртуальных регистров (WC), регистр младшего байта адреса регистра косвенной адресации памяти данных (DP1L), регистр старшего байта адреса регистра косвенной адресации памяти данных (DP1H), регистр номера страницы памяти регистра косвенной адресации памяти данных (DP1P), регистр младшего байта адреса регистра косвенной адресации памяти данных/памяти команд (DP2L), регистр старшего байта адреса регистра косвенной адресации памяти данных/памяти команд (DP2H), регистр номера страницы памяти регистра косвенной адресации памяти данных/памяти команд (DP2P), регистр младшего байта указателя стека данных (SPL), регистр старшего байта указателя стека данных (SPH), регистр младшего байта индекса стека данных (IDXL) и регистр старшего байта индекса стека данных (IDXH). Регистрами режимов работы являются, в частности, регистр режима работы третьего файла виртуальных регистров (WCMODE) и регистр режимов косвенной адресации (DPMODE). Регистрами данных являются, в частности, регистр счетчика циклов (LC) и регистр старшего байта результата умножения (MRH).

В еще одном частном случае данного способа адресуемые регистры контекста образуют четыре группы.

Причем регистры нулевой группы в частном случае характеризуют адреса файлов виртуальных регистров и режимы косвенной адресации, регистры первой группы характеризуют адреса внутри страницы памяти регистров косвенной адресации, регистры второй группы характеризуют указатель и индекс программного стека данных. Регистры третьей группы характеризуют номера страниц памяти регистров косвенной адресации или являются регистрами данных.

При этом регистры WA, WB, WC, DPMODE и WCMODE образуют нулевую по счету группу. Регистры DP1L, DP1H, DP2L и DP2H образуют первую по счету группу. Регистры SPL, SPH, IDXL и IDXH вторую по счету группу. Регистры DP1P, DP2P, LC и MRH образуют третью по счету группу.

Способ в частном случае характеризуется также тем, что сохранение/восстановление контекста вычислительного процесса осуществляют в/из стека контекста.

При этом стек контекста выполнен как аппаратный регистровый стек.

Каждый регистр стека контекста выполнен с возможностью хранения значений адресуемых регистров контекста любой одной группы или значения счетчика команд процессора и значения регистра состояния процессора.

Способ также характеризуется тем, что команда сохранения адресуемых регистров контекста имеет код 00001010000000NN, где NN - номер группы регистров в двоичном виде. Команда восстановления адресуемых регистров контекста имеет код 0000101001MMMMNN. Причем NN - номер группы регистров в двоичном виде, а ММММ - маска восстановления регистров в двоичном виде.

В частном случае процессор с переключением контекста вычислительного процесса характеризуется тем, что стек контекста выполнен с возможностью хранения полного контекста вычислительного процесса в своих пяти регистрах.

В частном случае способа сохранения и восстановления регистров процессора при переключении контекста вычислительного процесса процессор выполнен с возможностью единовременного сохранения ряда регистров процессора, характеризующих контекст вычислительного процесса, образующих одну группу, причем NN - номер группы регистров в двоичном виде.

При этом регистры процессора, характеризующие контекст вычислительного процесса, образуют четыре группы.

В состав нулевой группы входят регистры WA, WB, WC, DPMODE и WCMODE. В состав первой группы входят регистры DP1L, DP1H, DP2L и DP2H. В состав второй группы входят регистры SPL, SPH, IDXL и IDXH. В состав третьей группы входят регистры DP1P, DP2P, LC и MRH.

В еще одном частном случае способ характеризуется тем, что для восстановления части сохраненных регистров процессора, характеризующих вычислительный процесс, задают маску восстановления регистров в команде восстановления, где ММММ - маска восстановления в двоичном виде.

Приведенные совокупности признаков обеспечивают получение указанного технического результата во всех случаях, на которые распространяется испрашиваемый объем правовой охраны.

Сущность изобретения поясняют следующие схемы:

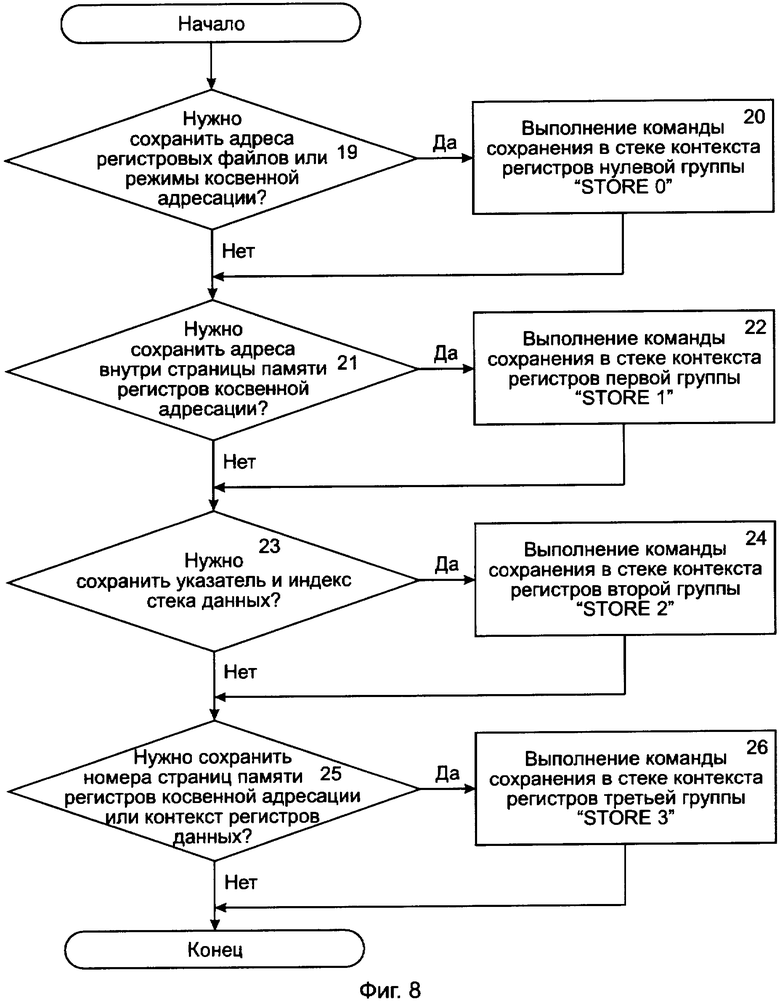

фиг.1: упрощенная структурная схема ядра процессора UNC80XX;

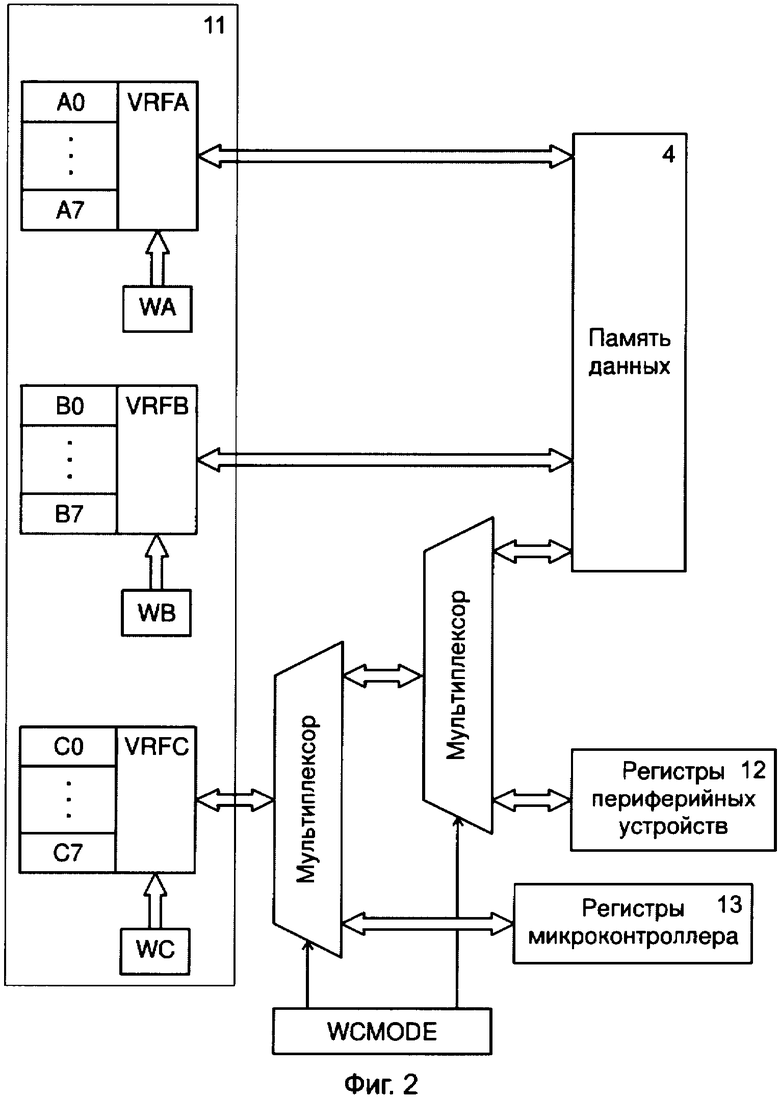

фиг.2: схема организации файлов виртуальных регистров и их связи с физическими устройствами памяти;

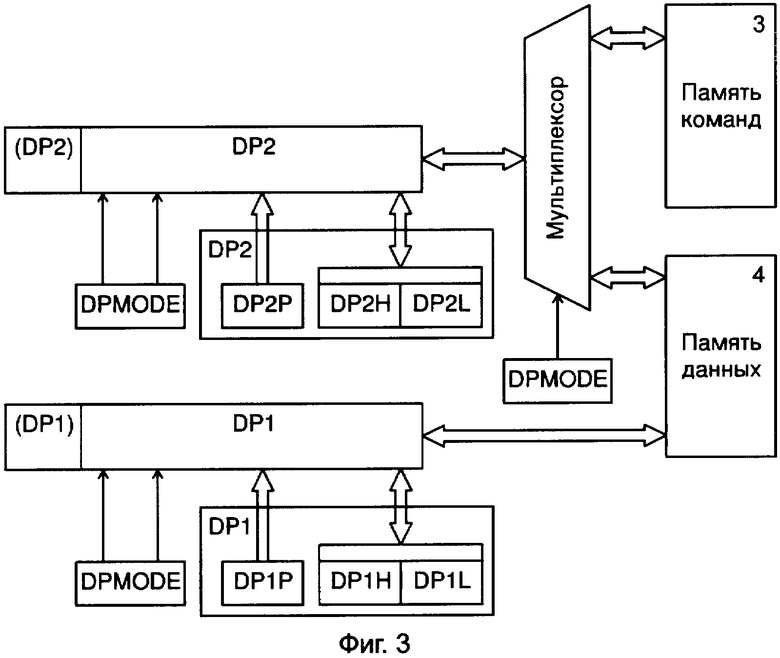

фиг.3: схема организации регистров косвенной адресации и их связи с памятью данных и памятью команд;

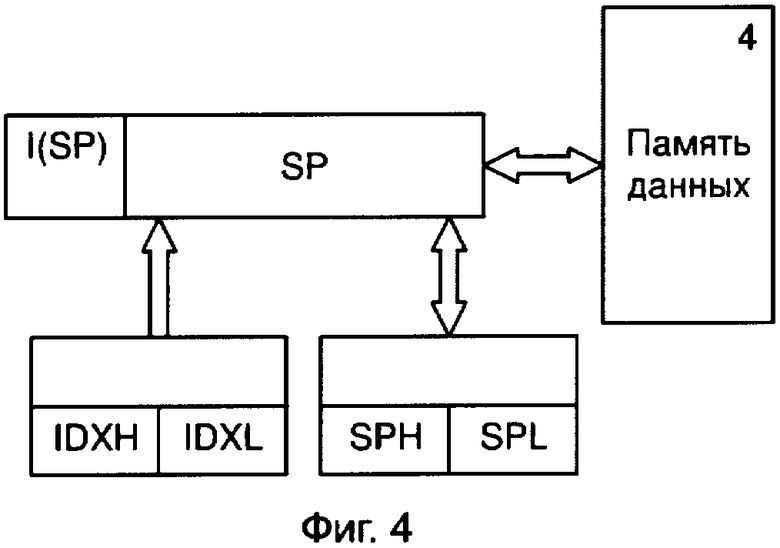

фиг.4: схема организации регистра индексной адресации стека данных и его связи с памятью данных;

фиг.5: таблица групп адресуемых регистров контекста;

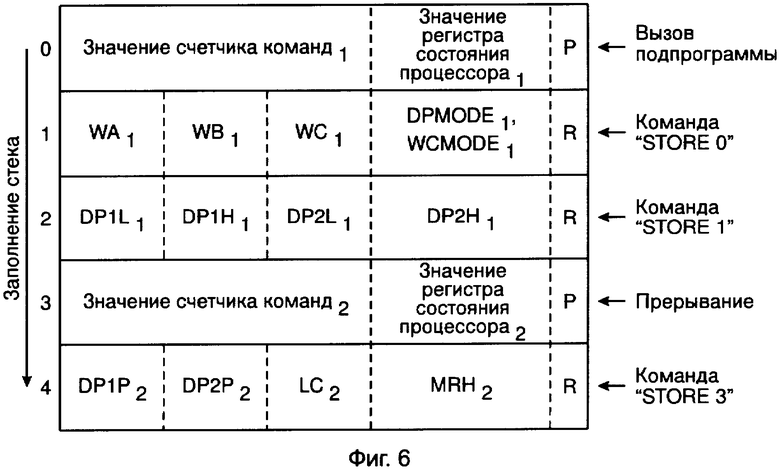

фиг.6: пример заполнения стека контекста;

фиг.7: общая схема алгоритма сохранения контекста;

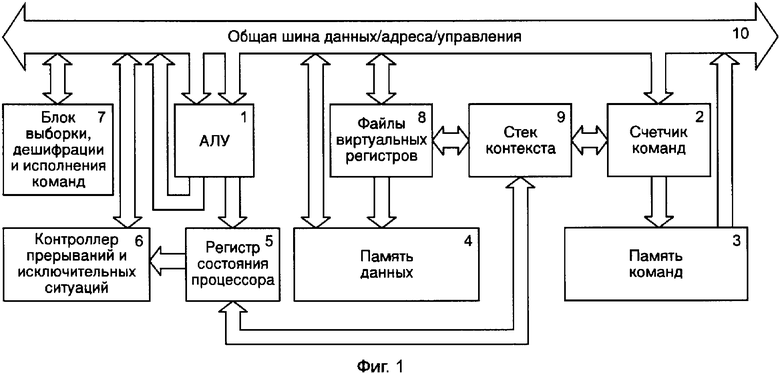

фиг.8: схема алгоритма программного сохранения значений адресуемых регистров контекста.

Осуществление изобретения поясняется на примере процессора с ядром UNC80XX.

UNC80XX относится к RISC процессорам с гарвардской архитектурой.

Упрощенная структурная схема UNC80XX представлена на фиг.1. Процессор содержит АЛУ (1), счетчик команд (2), память команд (3), память данных (4), регистр состояния процессора (5), контроллер прерываний и исключительных ситуаций (6), блок выборки, дешифрации и исполнения команд (7), файлы виртуальных регистров (8) и стек контекста (9).

Стек контекста связан своими входами-выходами со счетчиком команд (3), регистром состояния процессора (5) и первым входом-выходом файлов виртуальных регистров (8). Файлы виртуальный регистров (8) своим вторым входом/выходом связаны с общей шиной данных/адреса/управления (10), а выходом с памятью данных (4). Память данных (4) связана с общей шиной (10) через входы/выходы. Выход памяти команд (3) связан с входом общей шины (10), а вход памяти команд (3) связан с общей шиной (10) через счетчик команд (2). Регистр состояния (5) связан с общей шиной (10) через выход АЛУ (1) и вход контроллера прерываний и исключительных ситуаций (6). АЛУ (1), контроллер прерываний и исключительных ситуаций (6) и блок выборки, дешифрации и исполнения команд (7) связаны с общей шиной (10) своими входами/выходами.

В UNC80XX не используются аппаратные регистры общего назначения. Процессор обрабатывает данные из сегментов памяти данных (4). Для адресации указанных сегментов используется ряд служебных регистров. Сегментная адресация памяти данных (4) поясняется фиг.2-4.

Файлы виртуальных регистров (11) образованы первым файлом виртуальных регистров (VRFA), вторым файлом виртуальных регистров (VRFB) и третьим файлом виртуальных регистров (VRFC). Указанные файлы содержат по 8 регистров каждый - А0...А7, В0...В7 и С0...С7, отражающих 8 последовательно расположенных в памяти байтов. Для указания начала каждого файла виртуальных регистров в памяти данных использованы регистры указания базового адреса WA, WB и WC. Для каждого выполняющегося процесса выделяют уникальные файлы виртуальных регистров. Благодаря тому что виртуальные регистры разбиты на несколько групп, возможно осуществлять межпроцессное взаимодействие сохраняя только часть указанных файлов.

Файл VRFC выполнен с возможностью отображения нескольких областей памяти, включая регистры периферийных устройств (12) и некоторые другие регистры микроконтроллера (13). Для выбора режима работы VRFC используется регистр WCMODE.

Архитектура UNC80XX включает в себя регистр косвенной адресации памяти данных (DP1) и регистр косвенной адресации памяти данных/памяти команд (DP2). Данные регистры обеспечивают расширенную (24-разрядную) адресацию памяти данных/памяти команд. Виртуальные регистровые файлы адресуют первые 2 кбайта нулевой страницы памяти данных, стека данных - всю нулевую страницу памяти данных, остальная память данных может адресоваться только регистрами косвенной адресации. Адреса отображаемых регистрами байтов памяти определяются содержимым указателей адреса DP1, состоящего из регистров DP1P, DP1H, DP1L и DP2, состоящего из DP2P, DP2H, DP2L. В регистрах DP1P и DP1P содержатся адреса страниц памяти, в регистрах DP1H и DP2H - старшие байты адресов внутри страницы памяти, а в регистрах DP1L и DP2L - младшие байты адресов внутри страницы памяти. Режимы работы регистров косвенной адресации определяются содержимым регистра DPMODE. В зависимости от содержимого регистра режимов косвенной адресации DPMODE после выборки данных из этих регистров может осуществляться автоинремент/автодекремент адреса отображаемого регистром байта памяти. Автоинремент/автодекремент адреса действует в пределах страницы памяти. Регистр DPMODE также позволяет дополнительно определить будет ли DP2 адресовать память команд или память данных. Регистры косвенной адресации, кроме того, могут быть использованы в качестве аргументов команд.

Все адресуемые регистры разделены на четыре группы для удобства сохранения и восстановления контекста. Таблица группировки показана на фиг.5

Архитектура UNC80XX включает в себя также стек данных общего назначения, размещаемый в памяти данных. Стек данных управляется четырьмя регистрами: регистрами старшего и младшего байтов указателя вершины стека SP (SPH и SPL соответственно), а также регистрами IDXH и IDXL. Доступ к стеку данных осуществляется командами записи в стек данных и чтения из стека данных, а также через регистр индексной адресации стека I (SP).

В UNC80XX регистр состояния процессора содержит признаки результата выполненной операции и режимы работы процессора.

Стек контекста предназначен для сохранения и последующего восстановления контекста программы при обработке прерываний и вызове подпрограмм. Каждая запись стека контекста содержит либо значение счетчика команд и значение регистра состояния процессора, либо значения содержимого группы адресуемых регистров сохранения контекста программы. Если при возврате из прерывания в вершине стека контекста находится запись с содержимым группы регистров или при восстановлении содержимого группы регистров из стека контекста в его вершине находится запись с содержимым счетчика команд и слова состояния, то формируется прерывание при возникновении системных ошибок. Для этого каждая запись стека контекста содержит специальное поле с флагом «Р» или «R», характеризующими вид записи.

Пример заполнения стека контекста показан на фиг.6, где «STORE» является командой сохранения адресуемых регистров контекста группы указанного номера.

Переключение контекста осуществляют следующим образом (фиг.7).

При возникновении прерывания или вызове подпрограммы (14) командами вызова подпрограмм, косвенного вызова подпрограммы, косвенного вызова пользовательской подпрограммы и программного прерывания процессором в стек контекста сохраняется (15) текущее значение счетчика команд и регистра состояния процессора. Восстановление регистра состояния из стека контекста производятся командами возврата из прерывания, возврата из подпрограммы и возврата из подпрограммы с установкой признака переноса. Группы адресуемых регистров контекста программы, если требуется (16), могут быть сохранены (17) программно командой «STORE». Для полного сохранения контекста необходимо подать четыре команды «STORE». После этого сохранение контекста вычислительного процесса завершено (18).

В команде «STORE» необходимо указать номер группы сохраняемых регистров.

Алгоритм программного сохранения значений адресуемых регистров показан на фиг.8. При этом, если требуется (19) сохранение адреса регистровых файлов или режимов косвенной адресации, выполняют (20) команду «STORE 0», обрабатываемую процессором как сохранение в стеке контекста регистров WA, WB, WC, DCMODE и WCMODE. Затем, если требуется (21) сохранение адреса внутри страницы памяти регистров косвенной адресации, выполняют (22) команду «STORE 1», обрабатываемую процессором как сохранение в стеке контекста регистров DP1L, DP1H, DP2L и DP2H. Затем, если требуется (23) сохранить указатель и индекс стека данных, выполняют (24) команду «STORE 2», обрабатываемую процессором как сохранение в стеке контекста регистров SPL, SPH, IDXL и IDXH. Затем, если требуется (25) сохранить номера страниц памяти регистров косвенной адресации или контекст регистров данных, выполняют (26) команду «STORE 3», обрабатываемую процессором как сохранение в стеке контекста регистров DP1P, DP2P, LC и MRH.

Команды восстановления регистров из стека контекста должны следовать в порядке, обратном порядку предшествующих команд сохранения регистров в стеке контекста.

Причем, для команды восстановления следует указать маску восстановления регистров. Регистры, чей разряд в маске установлен в 1, будут восстановлены, а регистры, чей разряд сброшен в 0, останутся без изменений.

Процессор UNC80XX характеризуется также тем, что команда сохранения адресуемых регистров контекста имеет машинный код 00001010000000NN, а команда восстановления адресуемых регистров контекста имеет код 0000101001MMMMNN, где NN - номер группы регистров в двоичном виде, а ММММ - маска восстановления регистров в двоичном виде.

| название | год | авторы | номер документа |

|---|---|---|---|

| Связанное с выбранными архитектурными функциями администрирование обработки | 2015 |

|

RU2665243C2 |

| УВЕЛИЧЕНИЕ ЧИСЛА ДОСТУПНЫХ ДЛЯ КОМАНД РЕГИСТРОВ ОБЩЕГО НАЗНАЧЕНИЯ | 2010 |

|

RU2562430C2 |

| ОПРЕДЕЛЕНИЕ ФОРМАТОВ ТРАНСЛЯЦИИ ДЛЯ ФУНКЦИЙ АДАПТЕРА ВО ВРЕМЯ ВЫПОЛНЕНИЯ | 2010 |

|

RU2556418C2 |

| ТРАНСЛЯЦИЯ АДРЕСОВ ВВОДА-ВЫВОДА В АДРЕСА ЯЧЕЕК ПАМЯТИ | 2010 |

|

RU2547705C2 |

| КОНФИГУРАЦИЯ АРХИТЕКТУРНОГО РЕЖИМА В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ | 2015 |

|

RU2664413C2 |

| СРЕДСТВО РАЗДЕЛЕННОЙ ЗАГРУЗКИ/СОХРАНЕНИЯ И КОМАНДА ДЛЯ НЕГО | 2010 |

|

RU2554546C2 |

| ОБЩАЯ ПОСЛЕДОВАТЕЛЬНОСТЬ ЗАГРУЗКИ ДЛЯ УПРАВЛЯЮЩЕЙ СЕРВИСНОЙ ПРОГРАММЫ, СПОСОБНОЙ К ИНИЦИАЛИЗАЦИИ ВО МНОЖЕСТВЕННЫХ АРХИТЕКТУРАХ | 2015 |

|

RU2665238C2 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| СОХРАНЕНИЕ/ВОССТАНОВЛЕНИЕ ВЫБРАННЫХ РЕГИСТРОВ ПРИ ТРАНЗАКЦИОННОЙ ОБРАБОТКЕ | 2012 |

|

RU2562424C2 |

| Вычислительная система | 1977 |

|

SU692400A1 |

Изобретение относится к области вычислительной техники, а именно к микропроцессорам и микроконтроллерам. Техническим результатом является увеличение скорости переключения контекста задач и процедур при меньшем количестве использованных аппаратных ресурсов. Сохранение и восстановление контекста вычислительного процесса в процессоре осуществляется в два этапа. На первом этапе в стеке контекста процессора автоматически сохраняются значение счетчика команд и значение регистра состояния процессора. На втором этапе программно сохраняют требуемое число групп адресуемых регистров контекста. Процессор работает с сегментами памяти данных посредством собственных регистров виртуальных файлов. Причем сохранение базовых адресов всех файлов виртуальных регистров производится подачей лишь одной команды. 3 н. и 15 з.п. ф-лы, 8 ил.

| Траверса | 1984 |

|

SU1447747A1 |

| СПОСОБ И УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ ДЛЯ СОХРАНЕНИЯ ВОЗВРАТНОГО СОСТОЯНИЯ | 2001 |

|

RU2275679C2 |

| МЕХАНИЗМ ОБРАБОТКИ ПРЕРЫВАНИЙ В КОМПЬЮТЕРНЫХ СИСТЕМАХ, ПОДДЕРЖИВАЮЩИХ ОДНОВРЕМЕННОЕ ИСПОЛНЕНИЕ МНОЖЕСТВА ПОТОКОВ | 2002 |

|

RU2280272C2 |

| JP 5035502, 12.02.1993. | |||

Авторы

Даты

2008-12-10—Публикация

2006-10-19—Подача