Изобретение относится к области цифровой вычислительной техники и автоматики.

Известен счетный триггер (далее СТ), содержащий RS-триггер, первый и второй элементы И, первый и второй элементы НЕ и два элемента временной задержки. Схема приведена в книге И.Н.Букреев и др. «Микроэлектронные схемы цифровых устройств», 1973, стр.62, рис 2.18. Недостатком этого СТ является наличие двух элементов задержки сигналов.

Наиболее близким, принятым за прототип, является СТ по патенту RU №2278468. Этот СТ выполнен только на элементах И, ИЛИ, НЕ. Недостатком прототипа является то, что СТ выполняет только две элементарные операции (ЭО) - счет импульсов и установку в нуль RS-триггера.

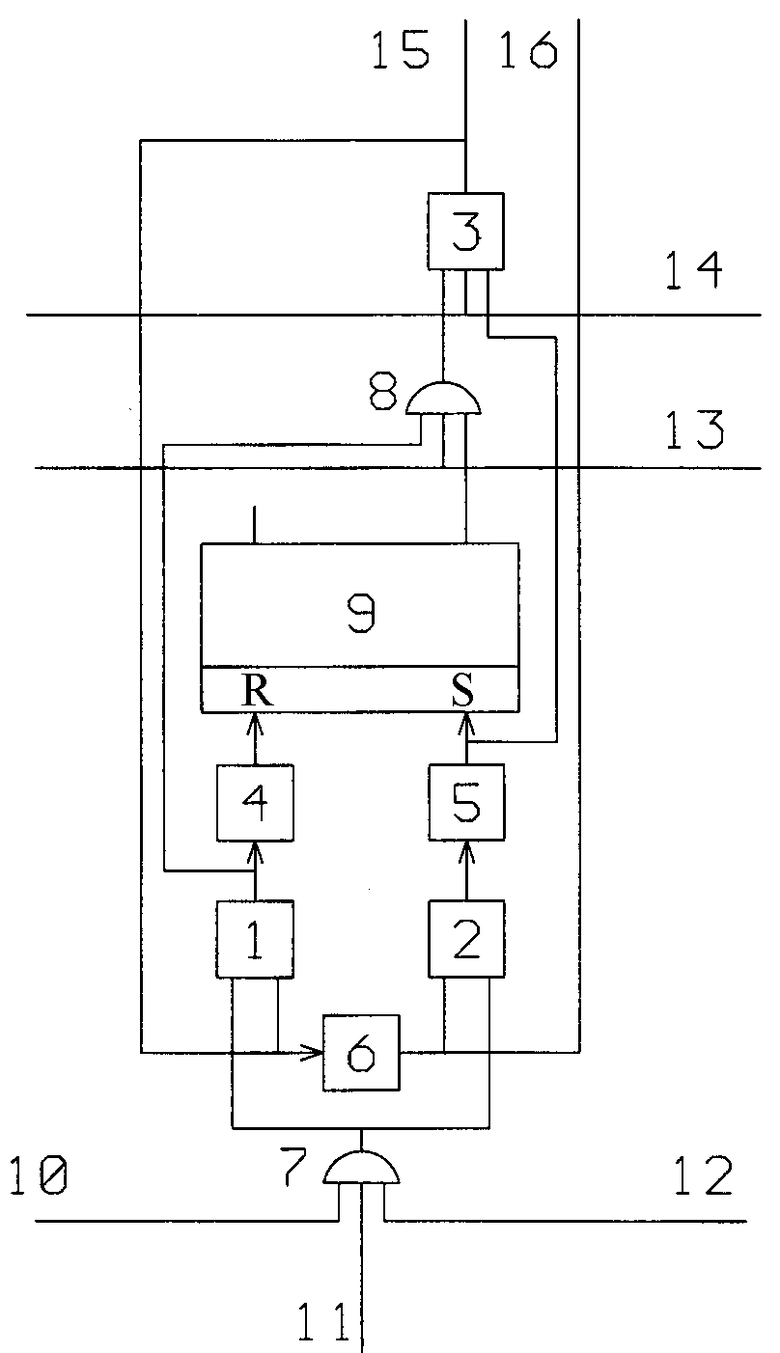

Целью предлагаемого СТ является расширение перечня выполняемых ЭО. Для этого предложен СТ, содержащий RS-триггер, первый, второй и третий элементы И, первый и второй элементы ИЛИ, первый и второй элементы НЕ, вход счетных импульсов, причем выход первого элемента И соединен с входом первого элемента НЕ и с первым входом второго элемента ИЛИ, второй вход которого подключен к единичному выходу RS-триггера, выход второго элемента ИЛИ соединен с первым входом третьего элемента И, второй вход которого соединен с S-входом RS-триггера и с выходом второго элемента НЕ, выход третьего элемента И является единичным выходом счетного триггера, который подключен к первому входу первого элемента И, второй вход которого соединен с вторым входом второго элемента И, нулевой выход счетного триггера подключен к первому входу второго элемента И, выход первого элемента НЕ соединен с R-входом RS-триггера, а выход второго элемента И соединен с входом второго элемента НЕ, отличающийся тем, что он дополнительно содержит третий элемент НЕ, вход которого соединен с первым входом первого элемента И, а выход третьего элемента НЕ соединен с первым входом второго элемента И, с первого по третий входы первого элемента ИЛИ подключены соответственно к первому и второму входам для выполнения элементарных операций и к входу счетных импульсов, выход первого элемента ИЛИ подключен к вторым входам первого и второго элементов И, первый и второй входы управления счетного триггера подключены к третьим входам соответственно второго элемента ИЛИ и третьего элемента И.

Предлагаемый СТ позволяет расширить перечень выполняемых ЭО по сравнению с прототипом в четыре раза. Дополнительно выполняются ЭО приема прямого и инверсного кодов, установки триггера в единицу и в нуль, логического сложения, логического умножения, инвертирования и сложения по модулю два без увеличения оборудования, определяемого по суммарному числу входов логических элементов. В таблице 1 приведены основные технические характеристики СТ.

Для пояснения принципа работы на чертеже приведена функциональная схема предлагаемого СТ. На схеме приняты следующие обозначения: элементы И 1-3, элементы НЕ 4-6, элементы ИЛИ 7-8, RS-триггер 9, счетный вход 12, входы управления Вып. ЭО 10, 11, первый и второй ВУ СТ 13, 14, единичный выход СТ 15, инверсный выход СТ - 16.

Предложенный объект осуществляется следующим образом.

Первый и второй входы выполнения ЭО и счетных импульсов (СИ) 10-12 подключены к входам ИЛИ 7. Выход ИЛИ 7 связан с вторыми входами И 1, 2. Первые входы этих элементов И соединены с входом и выходом НЕ 6 соответственно. Выходы И 1, 2 через НЕ 4, 5 подключены к R и S входам RS-триггера. Входы ИЛИ 8 связаны с выходом И 1, единичным выходом RS-триггера и с первым входом управления 13. Выход ИЛИ 8 связан с первым входом И 3, второй его вход соединен с выходом НЕ 5, а третий вход соединен с вторым входом управления 14. Выход И 3 является единичным выходом СТ и соединен с входами НЕ 6 и И 1.

Рассмотрим работу объекта при выполнении ЭО счета импульсов, инвертирования, приема прямого и обратного кода, установки нуля и единицы, логического умножения и сложения и сложения по модулю два.

В исходном положении (в статике) СТ и RS-триггер установлен в нуль. На входах 10, 11, 12, 13, отсутствуют высокие потенциалы. На входе 14 и выходах НЕ 4, 5, 6 присутствует высокий потенциал.

1. ЭО счета импульсов. Счет каждого импульса выполняется за два временных такта. По первому такту (t1) счетный импульс (СИ) по входу 12, ИЛИ 7, поступает на вторые входы И 1, 2. Так как И 2 будет открыт за счет высокого потенциала с НЕ 6, то СИ через И 2, НЕ 5 поступит на S-вход RS-триггера и установит его в единицу. Одновременно с поступлением СИ на S-вход запрещается работа И 3 на время длительности этого импульса. После переключения RS-триггера в единицу и прекращения действия запрещающего сигнала на входе И 3 высокий потенциал с единичного выхода RS-триггера через ИЛИ 8, И 3 поступит на единичный выход СТ 15 и на вход НЕ 6, выход с которого запретит прохождение следующего СИ через И 2, а высокий потенциал выхода И 3 разрешит работу И 1, что позволит второму СИ по цепи вход 12, ИЛИ 7, И 1, НЕ 4 поступить на R-вход RS-триггера и установит его в нуль. При этом единичное значение с выхода И 3 будет искусственно поддерживаться независимо от переключения RS-триггера на время длительности СИ за счет связи с выхода И 1 с входом ИЛИ 8. По t2, равному паузе между СИ, все элементы СТ готовятся к приходу второго СИ, при этом полагаем, что t1=t2=tn (tn - длительность паузы между импульсами).

2. ЭО сложения по модулю 2 выполняется аналогично ЭО счета импульсов, но импульс второго слагаемого поступает на вход 11. В таблице 2 приведена последовательность выполнения дополнительных ЭО.

3. ЭО инвертирования. Выполняется аналогично п.1. Отличие состоит в том, что исполнительный импульс (ИИ) выполнения этой ЭО поступает на вход 10.

4. ЭО логического сложения. Операция выполняется за счет снятия высокого потенциала с ВУ 14 и поступления по входу 11 импульса прямого кода второго слагаемого. Если код второго слагаемого равен единице, то исполнительный импульс по цепи вход 11, ИЛИ 7 поступит на входы И 1, 2 и через открытый элемент И 2, через НЕ 5 поступит на S-вход триггера 9 и установит его в единицу. Если код второго слагаемого равен нулю, то значение кода триггера 9 не меняется. На этом операция завершается. Результат операции будет храниться в триггере 9. Второй временной такт (пауза) используется для подготовки СТ к выполнению последующей ЭО.

5. ЭО логического умножения. Операция выполняется за два временных такта. Для ее выполнения на ВУ 13 подается высокий потенциал, а на вход 11 подается импульс инверсного кода второго сомножителя. Если код второго сомножителя равен нулю, то импульс по цепи вход 11, ИЛИ 7, И 1, НЕ 4 поступает на R-вход триггера 9 и устанавливает его в нуль. Если второй сомножитель равен единице, то триггер 9 не меняет своего значения. На этом операция завершается. Второй такт используется для подготовки СТ к выполнению следующей ЭО.

6. ЭО установки нуля. Для выполнения этой ЭО на ВУ 13 подается высокий потенциал, разрешающий прохождение ИИ на R-вход триггера 9.

Исполнительный импульс по цепи вход 10, ИЛИ 7, И 1, НЕ 4 поступает на R-вход и устанавливает триггер 9 в нуль. На этом выполнение операции заканчивается.

7. ЭО установки единицы. Для ее выполнения с ВУ 14 снимается высокий потенциал, а на вход 10 подается ИИ. Исполнительный импульс по цепи вход 10, ИЛИ 7, И 2, НЕ 5 поступит на S-вход триггера и установит его в единицу.

На этом выполнение операции завершается.

8. ЭО приема прямого кода. Операция выполняется за четыре временных такта. По t1 и t2 выполняется подготовительная ЭО установки нуля триггера (п.6). По t3 исполнительный импульс, соответствующий коду единицы принимаемого числа, по цепи вход 11, ИЛИ 7, И 2, НЕ 5 поступает на S-вход триггера 9. Если код принимаемого числа равен нулю, то триггер 9 не меняет своего значения. Четвертый такт используется для подготовки СТ к выполнению следующей ЭО.

9. ЭО приема инверсного кода. Операция выполняется за четыре временных такта. По t1 и t2 выполняется ЭО приема в триггер 9 кода единицы (п.7). По t3, если код принимаемого числа соответствует единице, по входу 11 поступает ИИ и инвертирует код, хранящейся в триггере 9, что соответствует инверсному коду принимаемого числа. Четвертый такт отводится для подготовки СТ к выполнению последующей ЭО.

Таким образом, предлагаемый СТ построен на одном RS-триггере, трех элементах И, двух элементах ИЛИ и трех элементах НЕ, обеспечивает расширение перечня выполняемых ЭО в четыре раза по сравнению с прототипом при увеличении оборудования только на 5%.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТЧИК ИМПУЛЬСОВ | 2006 |

|

RU2308801C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2010 |

|

RU2419200C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2004 |

|

RU2284653C2 |

| УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2381547C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ | 2005 |

|

RU2308073C2 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ДВОИЧНЫХ КОДОВ | 2010 |

|

RU2410746C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

Изобретение относится к вычислительной технике. Техническим результатом является расширение перечня выполняемых элементарных операций (ЭО). Счетный триггер содержит RS-триггер, два элемента ИЛИ, вход счетных импульсов, два входа для выполнения элементарных операций, первый и второй входы управления счетным триггером, три элемента И и три элемента НЕ. 1 ил., 2 табл.

Счетный триггер, содержащий RS-триггер, первый, второй и третий элементы И, первый и второй элементы ИЛИ, первый и второй элементы НЕ, вход счетных импульсов, причем выход первого элемента И соединен с входом первого элемента НЕ и с первым входом второго элемента ИЛИ, второй вход которого подключен к единичному выходу RS-триггера, выход второго элемента ИЛИ соединен с первым входом третьего элемента И, второй вход которого соединен с S-входом RS-триггера и с выходом второго элемента НЕ, выход третьего элемента И является единичным выходом счетного триггера, который подключен к первому входу первого элемента И, второй вход которого соединен с вторым входом второго элемента И, нулевой выход счетного триггера подключен к первому входу второго элемента И, выход первого элемента НЕ соединен с R-входом RS-триггера, а выход второго элемента И соединен с входом второго элемента НЕ, отличающийся тем, что он дополнительно содержит третий элемент НЕ, вход которого соединен с первым входом первого элемента И, а выход третьего элемента НЕ соединен с первым входом второго элемента И, с первого по третий входы первого элемента ИЛИ подключены соответственно к первому и второму входам для выполнения элементарных операций и к входу счетных импульсов, выход первого элемента ИЛИ подключен к вторым входам первого и второго элементов И, первый и второй входы управления счетного триггера подключены к третьим входам соответственно второго элемента ИЛИ и третьего элемента И.

| СЧЕТНЫЙ ТРИГГЕР ВЛАСОВА | 2005 |

|

RU2278468C1 |

| БУКРЕЕВ И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| - М.: Советское радио, 1973, с.62, рис.2.18 | |||

| СЧЕТНЫЙ ТРИГГЕР | 1993 |

|

RU2047938C1 |

| Счетный триггер | 1978 |

|

SU729820A1 |

| DE 4133472 A1, 15.04.1993. | |||

Авторы

Даты

2009-06-27—Публикация

2007-06-04—Подача