Изобретение относится к области вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики.

Известны сумматоры накапливающего типа, см., например, книгу М.А.Карцев, Арифметика цифровых машин, М., Наука 1969, стр. 247-252, а также накапливающий сумматор по а.с. № 1418701. Недостатками противопоставляемых устройств являются наличие в каждом разряде трех RS-триггеров и выполнение только одной операции - сложения (вычитания).

Наиболее близким аналогом, принятым за прототип, является объект по а.с. № 1291968. Прототип выполнен на основе трех логических элементов И, ИЛИ, НЕ и содержит только один RS-триггер в каждом разряде. Недостатком прототипа являются большая задержка сигнала в цепях переноса, равная 2nτ (здесь n - число разрядов, τ - задержка сигнала на элементе И (ИЛИ) и ограниченный перечень выполняемых операций.

Задачей изобретения является устранение указанных недостатков известных сумматоров. Для этого предложен объект, содержащий в каждом разряде один RS-триггер, шесть элементов И, четыре элемента ИЛИ, три элемента НЕ и пять шин управления, при этом в каждом четном разряде выход первого элемента И подключен к второму входу четвертого элемента ИЛИ, выходы первого и второго элементов И через первый элемент ИЛИ соединены с первыми входами третьего и четвертого элементов И, выходы которых через первый и второй элементы НЕ связаны с "нулевым" и "единичным" входами RS-триггера, вход первого элемента НЕ соединен с третьими входами второго и третьего элементов ИЛИ, выход второго элемента НЕ связан с третьим входом пятого элемента И, выход этого элемента соединен с первым входом четвертого элемента ИЛИ, выходы третьего и четвертого элементов ИЛИ подключены к первому и третьему входам шестого элемента И, выход которого соединен с третьим и четвертым входами третьего и четвертого элементов ИЛИ, "единичный" выход триггера подключен к первому входу третьего элемента ИЛИ, выход которого соединен с первым входом пятого элемента И, первая шина управления подключена к первому входу второго элемента И, вторая шина управления соединена с первым входом второго элемента И, третья шина управления соединена с вторым входом второго элемента ИЛИ, четвертая шина подключена к второму входу пятого элемента И, выход этого элемента соединен с вторым входом третьего элемента И и с входом третьего элемента НЕ, вход которого подключен к второму входу четвертого элемента И, к второму входу первого элемента И подключена информационная шина данного разряда, а пятая шина соединена с вторым входом шестого элемента И, отличающийся тем, что в каждый нечетный разряд введен седьмой элемент И, первый вход которого подключен к пятой шине управления, второй его вход связан с выходом третьего элемента ИЛИ данного разряда и вторыми входами второго элемента И и третьего элемента ИЛИ старшего разряда, второй вход третьего элемента ИЛИ связан с выходом седьмого элемента И, третий выход упомянутого элемента ИЛИ подключен к выходу третьего элемента И, выход первого элемента И соединен с вторым входом четвертого элемента ИЛИ, первый вход этого элемента связан с выходом пятого элемента И, а выход четвертого элемента ИЛИ подключен к третьему входу шестого элемента И, первый и второй входы которого соединены с выходами третьего и четвертого элементов ИЛИ младшего (четного) разряда, выход шестого элемента И подключен к первым входам третьих элементов ИЛИ данного и старшего (четного) разрядов, введена шестая шина управления, подключенная к второму входу первого элемента ИЛИ каждого разряда.

Отметим основные отличительные признаки объекта и покажем что позволяет получить каждый из признаков.

1. Введенный в каждый нечетный разряд седьмой элемент И с соответствующими информационными связями обеспечивает "хранение" сквозного или поразрядного переносов, выработанных в данном разряде, что обеспечивает распространение сигнала переноса с момента поступления исполнительного импульса на первую шину управления до снятия управляющего сигнала с пятой шины.

2. Введение информационных связей с выхода шестого элемента И нечетного разряда с первым входом третьего элемента ИЛИ четного разряда обеспечивает прохождение сигнала переноса только через один логический элемент И в нечетном разряде и один логический элемент ИЛИ в четном разряде, что позволяет сократить суммарную временную задержку сигнала переноса в два раза, т.е. повысить быстродействие выполнения операции сложения (вычитания).

3. Подключение шестой управляющей шины к второму входу первого элемента ИЛИ обеспечивает инвертирование кода в RS-триггерах, их установку в нуль, прием во все разряды кода "единиц", сдвига кода влево, т.е. расширяет функциональные возможности объекта.

Указанные отличия объекта от прототипа повышают быстродействие выполнения операции сложения (вычитания) за счет сокращения временных задержек сигналов в цепи переноса, расширяют перечень выполняемых операций (сдвиг влево, инвертирование, прием "единиц" во все разряды, установка в нуль RS-триггеров), повышают надежность работы, снижают потребление электроэнергии за счет снижения числа триггеров в каждом разряде объекта. Указанные преимущества обеспечиваются при минимальных затратах оборудования.

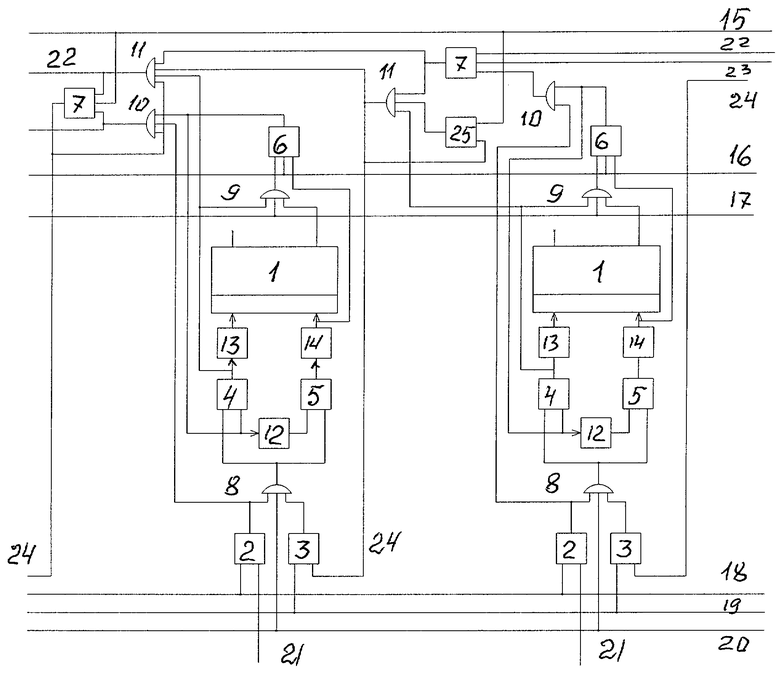

Для пояснения работы объекта на чертеже приведена функциональная схема его двух разрядов. Каждый разряд содержит RS-триггер 1, элементы И 2-7, 25, элементы ИЛИ 8-11, элементы НЕ 12-14, шину гашения переносов 15, шину управления выполнением операции логического сложения 16, шину управления выполнением операции логического умножения 17, шину управления первым сложением по модулю два 18, шину управления вторым сложением по модулю два 19, шину управления выполнением операций сдвига кода влево, инвертирования, приема всех единиц и установки в ноль триггеров 20, информационную шину поступления кода в разряд 21, информационные шины переноса в старший разряд 22-24. Рассмотрим работу объекта при выполнении арифметических (сложение, вычитание) и логических операций.

1. Операция сложения. Операция выполняется за три временных такта. (Под тактом будем понимать исполнительный импульс длительностью tи). Будем считать, что код первого слагаемого (Ai) хранится в триггерах 1 как результат выполнения предыдущей операции, а код второго слагаемого (Bi) поступает по шине 21. По t1 одновременно выполняются элементарные операции (ЭО) приема второго слагаемого, сложения по модулю два, формирования, "запоминания" и распространения потенциала сквозного переноса. Для выполнения этих ЭО на вход (шину) 15 подается высокий потенциал, который разрешает работу И 7, И 25. Этот потенциал сохраняется в течение выполнения всей операции. На вход 18 подается исполнительный импульс t1, который в случае присутствия на шине 21 высокого потенциала, что соответствует коду "единица", пройдет по цепи И 2, ИЛИ 8, И 4, НЕ 13, если в триггере 1 хранится код "единица", и по цепи И 5, НЕ 14, если в триггере хранится код "нуля", таким образом, код триггера будет проинвертирован. Если на входе 21 отсутствует высокий потенциал, то значение кода триггера не меняется. В первом случае в четных разрядах исполнительный импульс с выхода И 4 через ИЛИ 11 по шине 22 поступит в старший (нечетный) разряд. Одновременно этот же сигнал с выхода И 7 поступит на третий и четвертый входы ИЛИ 10, 11 и обеспечит "хранение" потенциала, выработанного в данном разряде. Если триггер 1 хранит код "нуля", а по шинам 22 или 23 поступил сигнал переноса, то этот сигнал с выходов ИЛИ 11 и 10 поступит в старший разряд на первый и второй входы И 7. В нечетных разрядах исполнительный импульс по цепи вход 21, И 2, ИЛИ 10 поступит на третий вход И 7. Если по шинам 22, 23 поступили сигналы переноса, то с выхода И 7 этот сигнала поступит в старший разряд на ИЛИ 11 и за счет поступления на вход И 25 сохранит сигнал переноса до конца операции. Если в нечетном разряде хранится код "единицы", то исполнительный сигнал по цепи шина 18, И 2, ИЛИ 8, И 4, ИЛИ 11 поступит на вход И 25 и будет "хранить" потенциал переноса до конца выполнения операции. Одновременно этот же потенциал поступит на первый вход ИЛИ 11 старшего (четного) разряда. По t2 будет продолжаться распространение и "запоминание" сигналов переносов во всех разрядах объекта. По t3, после завершения распространения максимального сквозного переноса, равного 2tи, выполняется ЭО второго сложения по модулю два. Для выполнения этой ЭО на вход 19 подается исполнительный импульс. Если из младшего разряда по шине 24 поступил сигнал переноса, то исполнительный импульс t3 по цепи вход 19, И 3, ИЛИ 8 поступит на первые входы И 4, И 5 и произведет инвертирование триггера 1. Таким образом, в триггерах 1 объекта будет сформирован результат сложения кодов двух положительных чисел. На этом собственно операция сложения закончена, но для подготовки устройства к выполнению новых операций необходимо устранить хранящиеся в цепи переносов сигналы. Для этого по t4 с шин 15 и 16 снимаются высокие потенциалы, чем обеспечивается гашение сигналов переносов во всех разрядах одновременно. Заметим, что последняя ЭО совмещается по времени с выбором новой арифметической или логической операции и на быстродействие работы объекта не влияет. Это позволяет утверждать, что операция сложения выполняется за три временных такта (3tи), при этом обеспечивается временная задержка сигналов в цепи переноса, равная  а для распостранения сигналов переноса отводится время 2tи.

а для распостранения сигналов переноса отводится время 2tи.

2. Операция вычитания положительных чисел выполняется аналогично операции сложения. Отличие состоит в том, что на вход 21 поступает инвертированный код второго слогаемого.

3. Сдвиг кода влево. Операция выполняется за четыре временных такта. По t1 выполняется ЭО инвертирования кода, за счет подачи на вход 20 исполнительного импульса. Этот импульс по цепи ИЛИ 8, И 5, НЕ 14 поступает на "единичный" вход триггера 1, если до прихода триггер хранил код "нуля", и по цепи И 4, НЕ 13, если ранее триггер хранил код "единицы". Одновременно осуществляется формирование и запоминание потенциала переноса в тех разрядах, в которых до прихода исполнительного импульса хранился код "единицы". При этом импульс проходит по цепи И 4, ИЛИ 11, И 7, ИЛИ 11, 10. В нечетных разрядах сигнал проходит по цепи И 4, ИЛИ 11, И 25, ИЛИ 11. По t2 производится установка триггеров в "нуль" (вход установки триггеров в нуль на чертеже не приводится). По t3 выполняется ЭО сложения по модулю два (вторая). При этом исполнительный импульс поступает на вход 19 и проходит по цепи И 3, ИЛИ 8, И 5, НЕ 14, есл в И 3 младшего разряда по входу 24 поступает потенциал переноса. Если сигнала переноса нет, то И 3 "закрыт" и состояние триггера 1 не меняется. По t4 производится выполнение ЭО гашения переносов. При этом с шин 15 и 16 снимаются высокие потенциалы, что выключает элементы И 7, 25 и "гасит" потенциалы переносов во всех разрядах одновременно.

4. Операция логического сложения. Выполняется за один временной такт. По t1 с выхода 16 снимается высокий потенциал, что приводит к появлению высокого потенциала на выходе НЕ 12, разрешающего прохождение исполнительного импульса через И 5. Если в данном разряде по входу 21 поступает сигнал кода "единицы", то исполнительный импульс по цепи вход 18, И 2, ИЛИ 8, И 5, НЕ 14 поступит на "единичный" вход триггера и установит его в "единицу". На этом выполнение ЭО закончено. (Для выполнения ЭО требуется дополнительно один вход элемента И 6)

5. Операция логического умножения. По t1 на вход 17 подается управляющий потенциал, который по цепи ИЛИ 9, И 6 поступает на второй вход И 4. Одновременно на вход 21 подается инверсивный код второго сомножителя. Если в рассматриваемом разряде на входе 21 имеется высокий потенциал, то исполнительный импульс, поступивший по шине 18 через И 2, ИЛИ 8, И 4, НЕ 13, поступит на "нулевой" вход триггера и установит его в "нуль". Другие разряды сохранят свое состояние, если на входе 21 этих разрядов будет "нулевой" потенциал. На этом выполнение операции закончено. Время второго такта используется для подготовки объекта к выполнению последующих операций. (Для выполнения этой операции требуется увеличить оборудование объекта только на один вход элемента ИЛИ. В известных устройствах требуется три входа).

6. ЭО приема кода "единицы" во все разряды. Выполняется за один такт. С входа 16 снимается высокий потенциал, а на вход 20 подается исполнительный импульс, который по цепи ИЛИ 8, И 5, НЕ 14 поступает на "единичный" вход триггера и устанавливает его в "единицу". (Выполнение этой ЭО не требует дополнительного оборудования).

7. Операция сложения по модулю два и инвертирования кодов рассмотрена при описании выполнения операции сложения и не требует дополнительных пояснений и оборудования.

Таким образом, предлагаемый объект позволяет повысить быстродействие выполнения операции сложения за счет сокращения в два раза временной задержки сигнала в цепях переноса и расширить перечень выполняемых операций при минимальных затратах оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТЧИК ИМПУЛЬСОВ | 2006 |

|

RU2308801C1 |

| УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2381547C2 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2004 |

|

RU2284653C2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ | 2005 |

|

RU2308073C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2010 |

|

RU2419200C1 |

| СУММАТОР КОМБИНАЦИОННОГО ТИПА | 2004 |

|

RU2275676C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является повышение быстродействия и расширение перечня арифметических и логических операций, выполняемых устройством, при минимальных затратах оборудования. Устройство содержит RS-триггер, шесть элементов И, четыре элемента ИЛИ, три элемента НЕ, шесть шин управления, шины переноса. 1 з.п. ф-лы, 1 ил.

| Накапливающий сумматор | 1985 |

|

SU1291968A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| ЦИФРОВОЙ СУММАТОР | 1994 |

|

RU2099776C1 |

| Накапливающий сумматор | 1987 |

|

SU1418701A1 |

| US 5691931 А, 25.11.1995 | |||

| 1972 |

|

SU416869A1 | |

Авторы

Даты

2006-06-20—Публикация

2004-11-15—Подача