Изобретение относится к области цифровой вычислительной техники и автоматики. Известен счетчик импульсов (далее объект), построенный на основе триггеров со счетным входом (См. И.Н.Букреев, Б.М.Мансуров и В.И.Горячев. Микроэлектронные схемы цифровых устройств. 1973, «Сов.Радио», стр.137, рис.5.1). Недостатком этого объекта является счетный триггер, который включает в себя элементы временной задержки счетных импульсов, что снижает быстродействие его работы, усложняет технологию изготовления триггера и повышает требования к формированию параметров счетных импульсов (крутизна фронта, длительность и другие параметры).

Известен также объект, выполненный на основе только трех логических элементов (ЛЭ) И, ИЛИ, НЕ, который устраняет недостатки приведенного выше устройства (см. тамже, стр.135-150, рис.5.7). В названном объекте триггеры собраны на основе ЛЭ И-НЕ или ИЛИ-НЕ. Он содержит основной и вспомогательный регистры на основе RS-триггеров, логические элементы И, ИЛИ, НЕ и шину счетных импульсов, подключенную к первым входам первого и второго элементов И самого младшего разряда счетчика, и выполняет только одну операцию счета импульсов.

Наиболее близким, принятым за прототип является объект по а.с. 1291968, который построен на основе RS-триггера, шести элементов И, четырех элементов ИЛИ и двух элементов НЕ в каждом разряде и выполняет операции сложения, сложение по модулю два и прием кода с числовых шин. Однако этот объект не выполняет ряд логических операций, таких как сдвиг кода в сторону старших разрядов, сдвиг кода в сторону младших разрядов, логическое сложение и логическое умножение. Это сужает область применения объекта.

Целью изобретения является повышение быстродействия и расширение перечня выполняемых объектом логических операций при минимальных затратах оборудования. С этой целью предложен объект, содержащий в каждом разряде один RS-триггер, первый, второй и третий элементы И, первый, второй, третий, четвертый элементы ИЛИ, первый, второй и третий элементы НЕ, первую и вторую шины счетных импульсов и информационную шину, при этом в каждом разряде единичный выход RS-триггера соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, выход первого элемента ИЛИ подключен к первому входу третьего элемента И, выход которого соединен с первым входом первого элемента И и с входом третьего элемента НЕ, выход которого соединен с первым входом второго элемента И, отличающийся тем, что введены четвертый элемент И, четвертый элемент НЕ, при этом первый вход второго элемента ИЛИ соединен с информационной шиной и с входом четвертого элемента НЕ, выход которого подключен к третьему входу первого элемента И, второй вход которого соединен с первой шиной счетных импульсов, а выход - со вторым входом четвертого элемента И, первый вход которого соединен с выходом четвертого элемента ИЛИ, первый вход которого соединен с шиной сдвига влево, выход третьего элемента НЕ соединен со вторым входом четвертого элемента ИЛИ старшего разряда, второй вход второго элемента ИЛИ подключен ко второй шине счетных импульсов, а его третий вход соединен с выходом первого элемента И младшего разряда, являющегося выходом импульсного сигнала переноса из младшего разряда, выход второго элемента ИЛИ подключен ко второму входу второго элемента И, выходы четвертого и второго элементов И через первый и второй элементы НЕ подключены к R и S входам RS-триггера соответственно, кроме того, S вход RS-триггера соединен с третьим входом третьего элемента И, третий вход первого элемента ИЛИ соединен с шиной управления логическим умножением, первый вход третьего элемента ИЛИ соединен с шиной управления операцией инвертирования кода, хранящегося в триггерах, второй вход третьего элемента ИЛИ соединен с выходом третьего элемента И младшего разряда, являющимся шиной потенциального сквозного переноса в старший разряд, выход третьего элемента ИЛИ соединен с вторым входом третьего элемента И, при этом в первый разряд введены пятый элемент И, пятый элемент ИЛИ, третья шина счетных импульсов и шина импульсов сдвига, третья шина счетных импульсов подключена к первому входу пятого элемента ИЛИ и к четвертому входу второго элемента ИЛИ, шина импульсов сдвига соединена со вторым входом пятого элемента И и со вторым входом пятого элемента ИЛИ, выход которого соединен со вторым входом первого элемента И и является первой шиной счетных импульсов для всех разрядов, первый и третий входы пятого элемента И соединены, соответственно, с шиной сдвига вправо и выходом импульсного сигнала переноса из последнего разряда, выход пятого элемента И соединен с третьим входом второго элемента ИЛИ, при этом шина потенциального сквозного переноса в первом разряде является шиной управления операцией счета импульсов.

Предлагаемый объект позволяет выполнять дополнительно операции инвертирования, вычитания, сдвига кода в сторону старших и младших разрядов, что обеспечивает умножение двоичных кодов, хранящихся в триггерах объекта, на 2, 4, 8 и т.д., делить коды чисел на 2, 4 и т.д., принимать и выдавать последовательно коды чисел в объект и из объекта, выполнять операции логического сложения и умножения. Выполнение указанных операций расширяет функциональные возможности объекта, т.е. создает положительный эффект. Заметим, что кроме расширения перечня выполняемых операций, повышается быстродействие вычислительного процесса за счет исключения времени пересылки кода во второй триггер и исключение пересылок информации в другие узлы и блоки вычислительной системы для выполнения перечисленных выше операций. Отметим отличительные признаки, которые обеспечивают положительный эффект:

1. Включение в состав оборудования каждого разряда второго элемента ИЛИ и соответствующих связей обеспечивает выполнение элементарных операций (ЭО) приема кода в триггеры и счет импульсов, поступивших по первой шине счетных импульсов, при этом результат счета будет занесен в триггеры через время, равное времени переноса и длительности счетного импульса (2Tu). В прототипе это время равно (3Тu), т.е. повышается быстродействие работы устройства (п.1).

2. Включение в состав оборудования разряда третьего элемента ИЛИ, пятой шины управления и соответствующих соединений обеспечивает инвертирование состояния триггеров, которое выполняется перед и после выполнения вычитания, что расширяет функции объекта. (п.2).

3. Введение в состав оборудования четвертого элемента И, четвертого элемента ИЛИ и седьмой шины управления с соответствующими соединениями входов и выходов логических элементов обеспечивает выполнение ЭО сдвига кода влево (в сторону старших разрядов) (п.3).

4. Четвертый элемент НЕ и восьмая шина управления с соответствующими соединениями обеспечивают выполнение ЭО логического умножения (п.4).

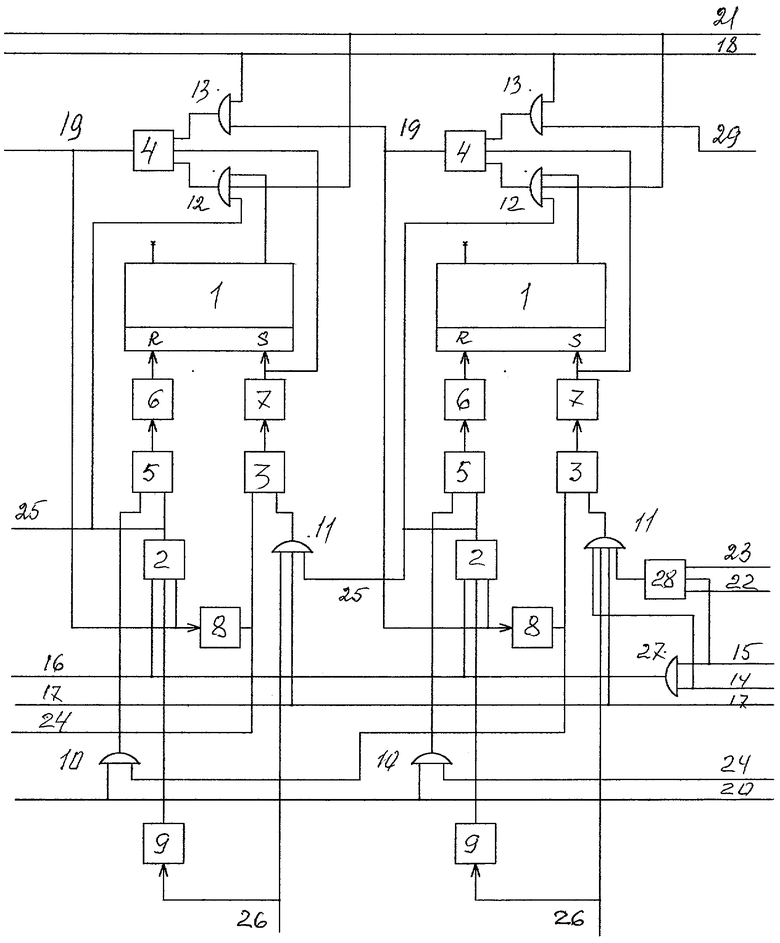

Для пояснения работы предлагаемого объекта на чертеже приведена функциональная схема первого и второго разрядов. На чертеже приняты следующие обозначения: RS-триггер 1, элементы И 2-5, 28, элементы НЕ 6-9, элементы ИЛИ 10-13, 27, третья шина счетных импульсов 14, шина импульсов сдвига 15, первая шина счетных импульсов 16, вторая шина счетных импульсов 17, шина управления операцией инвертирования 18, шина потенциального сквозного переноса 19 в старшие разряды, шина сдвига влево 20, шина логического умножения 21, шина сдвига вправо 22, выход импульсного сигнала переноса последнего разряда 23, выход инверсного кода младшего разряда 24, выход импульсного сигнала переноса из младшего разряда 25, информационная шина 26, шина управления операцией счета 29.

Предложенный объект работает следующим образом.

В каждом разряде информационная шина 26 через ИЛИ 11, И 3, НЕ 7 соединена с "единичным" входом триггера 1 и входом И 4. Выход И 4 через И 2, И 5, НЕ 6 соединен с "нулевым" входом триггера. "Единичный" выход триггера соединен с первым входом ИЛИ 12, шина 21 соединена с третьим входом ИЛИ 12. Выходы ИЛИ 12, 13 соединены с входами И 4, выход которого является переносом сигнала в старший разряд и соединен с входами И 2, НЕ 8. Второй вход И 2 подключен к шине 16, третий вход И 2 связан с выходом НЕ 9, вход которого соединен с шиной 26. Выход И 2 соединен с входами И 5 и ИЛИ 12 рассматриваемого разряда и с входом ИЛИ 11 старшего разряда, второй вход ИЛИ 11 подключен к шине 17. Шина 20 соединена с первым входом ИЛИ 10. Выход НЕ 8 подключен к входу И 3 рассматриваемого разряда и к входу ИЛИ 10 старшего разряда, выход этого элемента соединен с входом И 5. В статике все управляющие шины имеют "нулевой" (низкий) потенциал, а шина 20 - "единичный" (высокий). С выходов НЕ 6-9 на входы триггера 1, И 3, 2, 4 поступают высокие значения потенциалов. Рассмотрим работу объекта при выполнении операций счета импульсов, инвертирования кода триггеров, вычитания импульсов, сдвига влево, сдвига вправо, логического сложения, логического умножения и приема кода единиц во все разряды.

1. Операция счета импульсов. На вход 29 первого разряда подается высокий потенциал операции. Первый счетный импульс по входу 14, ИЛИ 11, И 3, НЕ 7 поступает на "единичный" вход триггера 1 и устанавливает его в "единицу". Одновременно этот же импульс "запрещает" выработку потенциала переноса во второй разряд. После истечения времени, равного длительности счетного импульса, с выхода И 4 в старший разряд будет поступать сигнал переноса, который подготовит к работе И 2 и за счет переключения НЕ 8 запретит работу И 3. Второй счетный импульс по цепи вход 14, ИЛИ 27, шина 16, И 2, И 5, НЕ 6 поступит на "нулевой" вход триггера 1 и установит его в "нуль". Одновременно по цепи выход И 4, И 2, И 3 будет поддерживаться высокий потенциал на первом входе И 2, независимо от времени переключения триггера первого разряда, и через ИЛИ 11, И 3, НЕ 7 будет установлен в "единицу" триггер 1 второго разряда. Далее порядок переключения триггеров первого и второго разрядов повторяется. Счет импульсов прекращается после прекращения поступления счетных импульсов по шине 14.

2. Операция инвертирования кода триггеров. Для выполнения этой операции на шину 18 подается "высокий" потенциал. После чего на шины 17 и 14 одновременно поступает исполнительный импульс, который пройдет по цепи И 2, И 5, НЕ 6 на "нулевой" вход триггера и установит его в "нуль", если до прихода импульса в триггере хранился код "единицы". Если раньше триггер хранил код "нуля", то импульс по цепи шина 17, ИЛИ 11, И 3, НЕ 7 поступит на "единичный" вход триггера и установит его в "единицу". Таким образом код, хранящийся в триггерах 1, будет проинвертирован.

3. Операция вычитания импульсов. Операция выполняется аналогично выполнению операции счета импульсов. Отличие состоит в том, что до и после ее выполнения производится первое и второе инвертирование кодов, хранящихся в триггерах.

4. Операция сдвига кода влево. На время выполнения этой операции с шины 20 снимается высокий потенциал, а на шину 21 подается высокий потенциал. По шине 15 поступает исполнительный импульс сдвига, который по цепи ИЛИ 27, шина 16, И 2, И 5, НЕ 6 поступает на "нулевой" вход триггера 1, если до поступления этого импульса в триггере хранился код "единицы". Если в старшем разряде до начала сдвига был код "нуля", то сигнал с выхода И 2 младшего разряда по цепи ИЛИ 11, И 3, НЕ 7 поступит на "единичный" вход триггера и установит его в "единицу" т.е. произойдет сдвиг кода на один разряд влево. Если до начала сдвига в обоих разрядах хранился код "единицы", то с выхода НЕ 8 младшего разряда по цепи вход 24, ИЛИ 10 старшего разряда запрещается прохождение импульса через И 5, НЕ 6 на "нулевой" вход триггера старшего разряда. Таким образом за один временной такт выполняется сдвиг кода на один разряд влево.

5. Операция сдвига кода вправо. Эта операция выполняется аналогично выполнению предыдущей операции. Отличие состоит в том, что при необходимости сдвинуть код на m разрядов вправо осуществляют сдвиг кода на n-m разрядов влево (здесь n - число разрядов объекта). При этом код старшего разряда счетчика заносится в первый (младший) разряд счетчика по цепи выход И 2 самого старшего разряда, И 28, ИЛИ 11, И 3, НЕ 7 самого младшего разряда.

6. Операция логического сложения. Выполняется за один временной такт. Исполнительный импульс поступает по информационной шине 26, ИЛИ 11, И 3, НЕ 7 на "единичный" вход триггера. Если на шине 26 отсутствует высокий потенциал, соответствующий коду "единице", то код триггера 1 не меняется.

7. Операция логического умножения. Выполняется за один временной такт. Для ее выполнения на шины 18 и 21 одновременно поступают управляющие потенциалы. При этом во всех разрядах потенциал с выхода И 4 поступает на первый вход И 2, на второй вход которого по шинам 15, 16 поступает исполнительный импульс, который по цепи элементов И 2, И 5, НЕ 6 поступит на "нулевой" вход триггера, если в данном разряде отсутствует высокий потенциал на информационной шине 26, и установит триггер 1 в "нуль". Если код второго сомножителя равен "единице", то триггер 1 не меняет своего состояния. На этом выполнение операции завершается.

8. Операция приема кода "единиц" во все разряды. Выполняется за один временной такт. Для ее выполнения на шину 17 подается исполнительный импульс, который по цепи элементов ИЛИ 11, И 3, НЕ 7 поступает на "единичный" вход триггера 1 и устанавливает его в "единицу".

Таким образом, предлагаемый объект повышает быстродействие работы и расширяет перечень выполняемых операций, по сравнению с прототипом, в 1,5 раза при минимальных затратах оборудования, определяемых суммарным числом входов логических элементов (цена Квайна). Это число равно 31. При этом дополнительно выполняются операции инвертирования, вычитания, логического сложения, логического умножения, сдвига кода влево, сдвига кода вправо, а на выполнение каждой операции требуется только около 4 входов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТЧИК ИМПУЛЬСОВ | 2006 |

|

RU2308801C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2010 |

|

RU2419200C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| СУММАТОР КОМБИНАЦИОННОГО ТИПА | 2004 |

|

RU2275676C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2005 |

|

RU2284654C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ | 2005 |

|

RU2308073C2 |

Изобретение относится к цифровой вычислительной технике и устройствам автоматики. Технический результат заключается в повышении быстродействия выполнения операции счета и расширении перечня выполняемых операций. Каждый разряд счетчика содержит только один RS-триггер, по четыре элемента И, ИЛИ, НЕ, восемь шин управления и информационную шину. Операция счета импульсов выполняется за два временных такта. По времени первого такта формируется потенциал максимального по времени переноса. По второму временному такту в RS-триггеры заносится результат счета. Кроме счета импульсов, устройство выполняет операции инвертирования RS-триггеров, вычитания импульсов, сдвига кода влево и вправо, логическое сложение и умножение. Особенностью счетчика является то, что правильный перенос искусственно поддерживается за счет поступления сигнала в схему переноса, если триггер устанавливается в "нуль", и за счет запрета распространения сигнала переноса в данном разряде, если триггер устанавливается в "единицу". Суммарное число входов логических элементов одного разряда счетчика равно 31 (цена Квайна), в т.ч. 7 входов для построения триггера. 1 ил.

Счетчик импульсов, выполненный на основе логических элементов И, ИЛИ, НЕ, содержащий в каждом разряде один RS-триггер, первый, второй и третий элемент И, первый, второй, третий, четвертый элементы ИЛИ, первый, второй и третий элементы НЕ, первую и вторую шины счетных импульсов и информационную шину, при этом в каждом разряде единичный выход RS-триггера соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, выход первого элемента ИЛИ подключен к первому входу третьего элемента И, выход которого соединен с первым входом первого элемента И и с входом третьего элемента НЕ, выход которого соединен с первым входом второго элемента И, отличающийся тем, что введены четвертый элемент И, четвертый элемент НЕ, при этом первый вход второго элемента ИЛИ соединен с информационной шиной и с входом четвертого элемента НЕ, выход которого подключен к третьему входу первого элемента И, второй вход которого соединен с первой шиной счетных импульсов, а выход - со вторым входом четвертого элемента И, первый вход которого соединен с выходом четвертого элемента ИЛИ, первый вход которого соединен с шиной сдвига влево, выход третьего элемента НЕ соединен со вторым входом четвертого элемента ИЛИ старшего разряда, второй вход второго элемента ИЛИ подключен ко второй шине счетных импульсов, а его третий вход соединен с выходом первого элемента И младшего разряда, являющегося выходом импульсного сигнала переноса из младшего разряда, выход второго элемента ИЛИ подключен ко второму входу второго элемента И, выходы четвертого и второго элементов И через первый и второй элементы НЕ подключены к R и S входам RS-триггера соответственно, кроме того, S вход RS-триггера соединен с третьим входом третьего элемента И, третий вход первого элемента ИЛИ соединен с шиной управления логическим умножением, первый вход третьего элемента ИЛИ соединен с шиной управления операцией инвертирования кода, хранящегося в триггерах, второй вход третьего элемента ИЛИ соединен с выходом третьего элемента И младшего разряда, являющимся шиной потенциального сквозного переноса в старший разряд, выход третьего элемента ИЛИ соединен с вторым входом третьего элемента И, при этом в первый разряд введены пятый элемент И, пятый элемент ИЛИ, третья шина счетных импульсов и шина импульсов сдвига, третья шина счетных импульсов подключена к первому входу пятого элемента ИЛИ и к четвертому входу второго элемента ИЛИ, шина импульсов сдвига соединена со вторым входом пятого элемента И и со вторым входом пятого элемента ИЛИ, выход которого соединен со вторым входом первого элемента И и является первой шиной счетных импульсов для всех разрядов, первый и третий входы пятого элемента И соединены, соответственно, с шиной сдвига вправо и выходом импульсного сигнала переноса из последнего разряда, выход пятого элемента И соединен с третьим входом второго элемента ИЛИ, при этом шина потенциального сквозного переноса в первом разряде является шиной управления операцией счета импульсов.

| Накапливающий сумматор | 1985 |

|

SU1291968A1 |

| SU 1292479 A1, 07.10.1986 | |||

| Накапливающий сумматор | 1987 |

|

SU1418705A1 |

| Счетчик импульсов | 1986 |

|

SU1422404A1 |

| US 4991186, 05.02.1991. | |||

Авторы

Даты

2006-09-27—Публикация

2004-11-25—Подача