Изобретение относится к вычислительной технике и может быть использовано при построении нейросетевых систем обработки информации.

Известно устройство для обработки информации на базе регулярной структуры памяти, ориентированное на параллельное выполнение вычислений и содержащее взаимосвязанные посредством коммутатора операционные блоки, блоки памяти и блоки ввода/вывода данных [Паттерсон Д., Андерсон Т., Кадвел Н. и др. Доводы в пользу IRAM. - Компьютерра, №15, 1998, Приложение С.3-14].

Недостатками устройства являются ориентация технического решения на концепцию последовательного управления вычислениями и ограниченное число процессорных блоков. Вследствие ограниченного числа процессорных блоков данное устройство не позволяет эффективно решать задачи нейросетевого базиса с высокой степенью распараллеливания вычислительного процесса.

Известно также устройство для обработки информации, содержащее операционные блоки, взаимосвязанные с блоками локальной памяти команд и локальной памяти данных, блоки стековой памяти результатов, соединенные с выходами соответствующих операционных блоков и входами одноименных блоков локальной памяти данных, блоки ввода и вывода данных, подключенные к параллельной шине [Компьютеры на СБИС: в 2-х кн. Кн.1: Пер. с япон. / Мотоока Т., Томита С. и др. - М.: Мир, 1988, С.102-107].

Недостаток данного устройства - программное распараллеливание вычислений: на этапе компиляции определяется возможность одновременного выполнения отдельных программных фрагментов и производится их распределение по операционным блокам, число которых в устройстве ограничено, что не позволяет в полной мере реализовать потенциальные возможности распараллеливания процесса решения задачи. В устройстве не предусмотрены аппаратные средства, направленные на решение задач, свойственных нейросетевому базису.

Наиболее близким техническим решением к предлагаемому изобретению и выбранным авторами за прототип является устройство для обработки информации, содержащее операционные блоки, входы которых взаимосвязаны с выходами блоков локальной памяти команд и блоков локальной памяти данных, а выходы - с первой шиной, блоки стековой памяти результатов, входы которых соединены со второй шиной, а выходы - с входами соответствующих блоков локальной памяти данных, блоки ввода и вывода данных, подключенные к первой шине, отличающееся тем, что оно содержит по числу блоков локальной памяти данных блоки локальной памяти функциональных параметров и блоки локальной памяти готовности данных, триггеры занятости по числу операционных блоков, третью шину в виде кольца, посредством которой взаимосвязаны входы операционных блоков, выходы триггеров занятости, выходы блоков локальной памяти данных, блоков локальной памяти команд, блоков локальной памяти функциональных параметров и блоков локальной памяти готовности данных, причем входы блоков локальной памяти функциональных параметров и блоков локальной памяти команд соединены с первой шиной, которая совместно со второй шиной образует кольцевую шину, а входы блоков локальной памяти готовности данных соединены с выходами одноименных блоков стековой памяти результатов [патент РФ 2179739, МПК G06F 15/00. Устройство для обработки информации / Г.Ф.Нестерук, Ф.Г.Нестерук. - №2000108883/09; Заявлено 10.04.2000. Опубл. 20.02.2002. Бюл. №5. Приоритет от 10.04.2000].

Недостатком прототипа является ограниченная пропускная способность кольцевой шины, соединяющей выходные шины операционных блоков и входные шины блоков стековой памяти результатов и, как следствие, снижение общей производительности устройства из-за простоев операционных блоков в ожидании поступления данных.

Задачей настоящего изобретения является повышение производительности устройства за счет локальной буферизации пакетов данных, формируемых операционными блоками, и обеспечения более оперативного обслуживания буферизированных пакетов данных с помощью механизма равновероятного циклического назначения приоритетов.

Поставленная задача достигается тем, что в устройство для обработки информации введены локальные стеки пакетов данных, входные шины которых соединены с выходными шинами одноименных операционных блоков, выходные шины - с параллельной шиной, а первые управляющие выходы - с управляющими входами соответствующих операционных блоков, регистр готовности, каждый разряд которого соединен со вторым управляющим выходом одноименного локального стека пакетов данных, приоритетную цепь с циклическим назначением приоритетов, первые и вторые входы которой взаимосвязаны с прямым и инверсным выходами разрядов регистра готовности, первые выходы - с первыми управляющими входами соответствующих локальных стеков пакетов данных, второй выход - со вторыми управляющими входами всех локальных стеков пакетов данных, а третий вход соединен по схеме "монтажное ИЛИ" с управляющими выходами блоков стековой памяти результатов, выходные шины которых соединены с входными шинами блоков локальной памяти команд и блоков локальной памяти функциональных параметров. Кроме того, приоритетная цепь с циклическим назначением приоритетов может содержать сдвигающий регистр, взаимосвязанный с генератором тактовых импульсов, пары последовательно включенных двухвходовых логических элементов И и ИЛИ, соединенные в кольцо, трехвходовые логические элементы И по числу локальных стеков пакетов данных, первые входы трехвходовых логических элементов И соединены с третьим входом приоритетной цепи с циклическим назначением приоритетов, вторые входы трехвходовых логических элементов И - с одноименными первыми входами приоритетной цепи с циклическим назначением приоритетов и соответствующими входами многовходового логического элемента ИЛИ, первые входы двухвходовых логических элементов И соединены с соответствующими вторыми входами приоритетной цепи с циклическим назначением приоритетов, вторые входы двухвходовых логических элементов И - с третьими входами соответствующих трехвходовых логических элементов И и выходами двухвходовых логических элементов ИЛИ соответствующей пары последовательно включенных двухвходовых логических элементов И и ИЛИ, первые входы двухвходовых логических элементов ИЛИ - с выходами двухвходовых логических элементов И предыдущей пары последовательно включенных двухвходовых логических элементов И и ИЛИ, вторые входы двухвходовых логических элементов ИЛИ - с соответствующими выходами сдвигающего регистра, а выход многовходового логического элемента ИЛИ взаимосвязан с вторым выходом приоритетной цепи с циклическим назначением приоритетов.

При реализации устройства для обработки информации в соответствии с заявляемым изобретением возникает технический результат - возможность работы устройства в режиме реального времени вследствие оперативного поступления пакетов данных, формируемых операционными блоками, в блоки стековой памяти результатов.

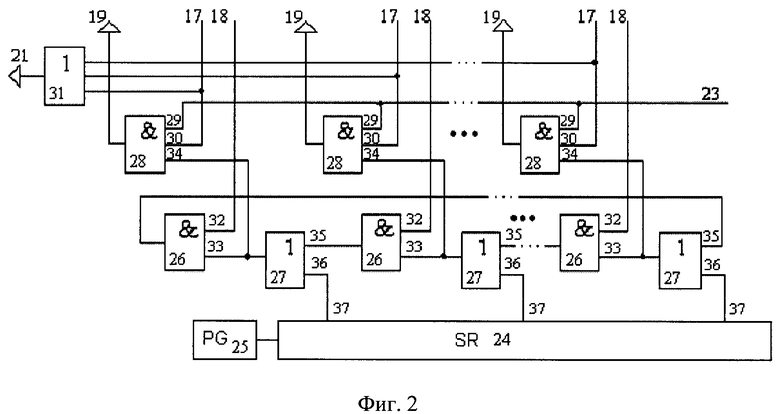

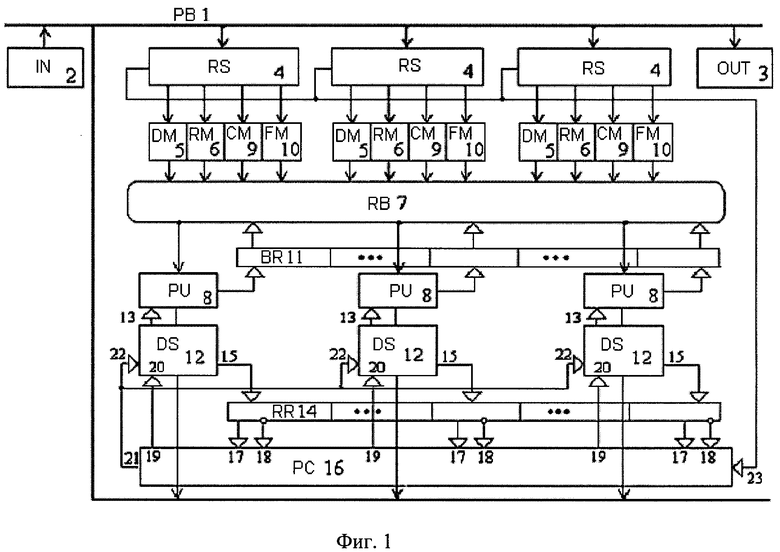

На фиг.1 представлена структурная схема предлагаемого устройства для обработки информации, а на фиг.2 - возможный вариант приоритетной цепи с циклическим назначением приоритетов.

Устройство для обработки информации содержит параллельную шину РВ 1, соединенную с блоками ввода данных IN 2 и блоками вывода данных OUT 3, блоками стековой памяти результатов RS 4, которые соединены с блоками локальной памяти данных DM 5 и блоками локальной памяти готовности данных RM 6, кольцевую шину RB 7, с которой взаимосвязаны операционные блоки PU 8, блоки локальной памяти команд СМ 9, блоки локальной памяти функциональных параметров FM 10 и регистр занятости BR 11, локальные стеки пакетов данных DS 12, первые управляющие выходы 13 которых соединены с управляющими входами соответствующих операционных блоков PU 8, регистр готовности RR 14, каждый разряд которого соединен со вторым управляющим выходом 15 одноименного локального стека пакетов данных DS 12, приоритетную цепь с циклическим назначением приоритетов PC 16, первые 17 и вторые 18 входы которой взаимосвязаны с прямым и инверсным выходами разрядов регистра готовности RR 14, первые выходы 19 - с первыми управляющими входами 20 соответствующих локальных стеков пакетов данных DS 12, второй выход 21 - со вторыми управляющими входами 22 всех локальных стеков пакетов данных DS 12, а третий вход 23 соединен по схеме "монтажное ИЛИ" с управляющими выходами блоков стековой памяти результатов RS 4.

Приоритетная цепь с циклическим назначением приоритетов PC 16 содержит сдвигающий регистр SR 24, взаимосвязанный с генератором тактовых импульсов PG 25, пары последовательно включенных двухвходовых логических элементов И 26 и ИЛИ 27, соединенные в кольцо, трехвходовые логические элементы И 28 по числу локальных стеков пакетов данных DS 12, первые входы 29 трехвходовых логических элементов И 28 соединены с третьим входом 23 приоритетной цепи с циклическим назначением приоритетов PC 16, вторые входы 30 трехвходовых логических элементов И 28 - с одноименными первыми входами 17 приоритетной цепи с циклическим назначением приоритетов PC 16 и соответствующими входами многовходового логического элемента ИЛИ 31, первые входы 32 двухвходовых логических элементов И 26 соединены с соответствующими вторыми входами 18 приоритетной цепи с циклическим назначением приоритетов PC 16, вторые входы 33 двухвходовых логических элементов И 26 - с третьими входами 34 соответствующих трехвходовых логических элементов И 28 и выходами двухвходовых логических элементов ИЛИ 27 соответствующей пары последовательно включенных двухвходовых логических элементов И и ИЛИ, первые входы 35 двухвходовых логических элементов ИЛИ 27 - с выходами двухвходовых логических элементов И 26 предыдущей пары последовательно включенных двухвходовых логических элементов И и ИЛИ, вторые входы 36 двухвходовых логических элементов ИЛИ 27 - с соответствующими выходами 37 сдвигающего регистра SR 24, а выход многовходового логического элемента ИЛИ 31 взаимосвязан со вторым выходом 21 приоритетной цепи с циклическим назначением приоритетов PC 16.

Рассмотрим процесс работы устройства для обработки информации, изображенного на фиг.1, в котором использована приоритетная цепь с циклическим назначением приоритетов в соответствии с фиг.2.

В режиме ввода исходных данных устройства для обработки информации пакеты данных, формируемые в блоке ввода данных IN 2, поступают на параллельную шину РВ 1 в формате:

Вводимые пакеты данных с параллельной шины РВ 1 поступают в блоки стековой памяти результатов RS 4, откуда поле "значение данных" заносится в соответствующую ячейку блока локальной памяти данных DM 5. Одновременно в том же адресном сечении блока локальной памяти готовности данных RM 6 устанавливается бит готовности. Установка всех битов готовности в некотором адресном сечении блока локальной памяти готовности данных RM 6 инициирует выборку командного пакета из данного адресного сечения блоков локальной памяти данных DM 5, команд СМ 9, функциональных параметров FM 10 и передачу выбранного командного пакета на кольцевую шину RB 7 устройства. При этом адресное сечение блока локальной памяти готовности данных RM 6 обнуляется.

Процесс обработки командного пакета. Командный пакет по кольцевой шине RB 7 достигает операционного блока PU 8, разряд регистра занятости BR 11 которого сброшен. Фиксация командного пакета во входных цепях операционного блока PU 8 удаляет его с шины RB 7 и устанавливает соответствующий разряд регистра занятости BR 11, что приводит к перенаправлению других командных пакетов, находящихся на шине RB 7, к оставшимся операционным блокам PU 8. В случае занятости всех операционных блоков PU 8 командные пакеты циркулируют по шине RB 7 до сброса одного из разрядов регистра занятости BR 11. Зафиксированный во входных цепях операционного блока PU 8 командный пакет содержит полный набор значений данных и функциональных параметров, подлежащих обработке, указание на реализуемую функцию и коды адресов командных пакетов - приемников результата. Операционный блок PU 8 после завершения обработки формирует столько пакетов данных, сколько адресов командных пакетов - приемников результата он содержит, и по мере формирования пакеты данных загружаются в соответствующий локальный стек пакетов данных DS 12, который после занесения первого из пакетов данных устанавливает соответствующий разряд регистра готовности RR 14. Выдача операционным блоком PU 8 всех подготовленных им пакетов данных сопровождается сбросом одноименного разряда регистра занятости BR 11.

В соответствии со значениями разрядов регистра готовности RR 14, подаваемых на первые 17 и вторые 18 входы приоритетной цепи с циклическим назначением приоритетов PC 16, первые выходы 19 приоритетной цепи с циклическим назначением приоритетов PC 16 и трехвходовых логических элементов И 28 (фиг.2) обеспечивают выбор одного из локальных стеков пакетов данных DS 12, готовых к выдаче пакетов данных на параллельную шину РВ 1. Последовательность из чередующихся двухвходовых логических элементов И 26 и логических элементов ИЛИ 27 решает задачи: создание из двухвходовых логических элементов И 26 цепи запрета выбора остальных локальных стеков пакетов данных DS 12 и изменение с помощью двухвходовых логических элементов ИЛИ 27 условий работы цепи запрета за счет операции сдвига унитарного кода вида 0…0100, осуществляемого в сдвигающем регистре SR 24 в соответствии с импульсами, поступающими от генератора тактовых импульсов PG 25. Уровень логического нуля на третьем входе 23 приоритетной цепи с циклическим назначением приоритетов PC 16 блокирует поступление пакетов данных от всех локальных стеков пакетов данных DS 12 на параллельную шину РВ 1, если хотя бы на одном управляющем выходе блоков стековой памяти результатов RS 4 сформирован уровень логического нуля, что соответствует полному заполнению данного блока стековой памяти результатов RS 4. Если же в ранее заполненном блоке стековой памяти результатов RS 4 освобождается хотя бы одна ячейка, то на третьем входе 23 приоритетной цепи с циклическим назначением приоритетов PC 16 формируется уровень логической единицы, который разрешает выдачу унитарного кода выборки на первые выходы 19 приоритетной цепи с циклическим назначением приоритетов PC 16. Готовность хотя бы одного локального стека пакетов данных DS 12 к выдаче пакетов данных (установлен в единицу соответствующий разряд регистра готовности RR 14) приводит к формированию на втором выходе 21 приоритетной цепи с циклическим назначением приоритетов PC 16 уровня логической единицы сигнала извлечения, поступающего на второй управляющий вход 22 всех локальных стеков пакетов данных DS 12. Циклическое изменение приоритета обеспечивается изменением положения единицы в унитарном коде в результате операции сдвига содержимого сдвигающего регистра SR 24. Единица унитарного кода через соответствующий двухвходовой логический элемент ИЛИ 27, формируя сигнал разрешения выборки на ближайшем слева трехвходовом логическом элементе И 28, приводит к появлению уровня логической единицы на одноименном первом выходе 19 приоритетной цепи с циклическим назначением приоритетов PC 16, если установлен в единицу соответствующий из разрядов регистра готовности RR 14 и отсутствует переполнение блоков стековой памяти результатов RS 4 (на третьем входе 23 приоритетной цепи с циклическим назначением приоритетов PC 16 - уровень логической единицы). Нули унитарного кода не влияют на работу цепи запрета.

Приоритетная цепь с циклическим назначением приоритетов PC 16 генерирует унитарный код выборки локального стека пакетов данных DS 12 в соответствии с правилами: в блоках стековой памяти результатов RS 4 есть свободные ячейки (на третьем входе 23 приоритетной цепи с циклическим назначением приоритетов PC 16 - сигнал логической единицы); наивысший приоритет предоставляется локальному стеку пакетов данных DS 12, положение которого в структуре устройства соответствует положению единицы в унитарном коде регистра сдвига SR 24; выбирается самый приоритетный или ближайший слева от него локальный стек пакетов данных DS 12 с готовыми пакетами данных. Пакеты данных выдаются на параллельную шину РВ 1 по сигналу извлечения, поступающему со второго выхода 21 приоритетной цепи с циклическим назначением приоритетов PC 16 на второй управляющий вход 22 всех локальных стеков пакетов данных DS 12. Полное освобождение локального стека пакетов данных DS 12 сопровождается сбросом соответствующего разряда регистра готовности RR 14. Локальные стеки пакетов данных DS 12 представляют собой память типа FIFO, поэтому процесс занесения пакетов данных с выходных шин операционных блоков PU 8 может быть совмещен во времени с процессом извлечения пакетов данных с выхода стека пакетов данных DS 12 на параллельную шину РВ 1 и далее во входные цепи соответствующих блоков стековой памяти результатов RS 4. Далее - аналогично процессу ввода исходных данных.

Режим вывода результатов вычислений. Результаты вычислений формируются операционными блоками PU 8 в виде пакетов данных, адресное поле каждого из которых соответствует одному из адресов блоков вывода данных OUT 3. Пакеты данных описанным выше образом поступают с выходных шин операционных блоков PU 8 в локальные стеки пакетов данных DS 12 и далее на параллельную шину РВ 1. Однако они не заносятся не в один из блоков стековой памяти результатов DS 4, а фиксируются во входных цепях блоков вывода данных OUT 3.

Режим программирования устройства для обработки информации. Программирование заявляемого устройства осуществляется перед его использованием в вышеперечисленных режимах работы. При программировании необходимо для каждого командного пакета в соответствующее адресное сечение блока локальной памяти команд СМ 9 ввести коды адресов командных пакетов - приемников результата. В этом случае значение адреса командного пакета - приемника результата (поле "значение") пакета данных, формируемого в блоке ввода IN 2, через параллельную шину РВ 1 и соответствующий блок стековой памяти результатов DS 4 заносится в адресное сечение (поле "адрес командного пакета" и поле "адрес в пакете") заданного блока локальной памяти команд СМ 9 (поле "номер блока локальной памяти").

Режим настройки функциональных параметров устройства для обработки информации. Настройка функциональных параметров производится после осуществления программирования заявляемого устройства, но перед его функционированием в качестве нейронной сети. Процесс занесения значений функциональных параметров аналогичен вышерассмотренной последовательности программирования с той лишь разницей, что поле "значение" пакета данных помещается в адресное сечение соответствующего блока локальной памяти функциональных параметров FM 10. Выполнение процедуры настройки после осуществления программирования устройства обязательно при решении задач в нейросетевом базисе, т.к. процесс программирования задает топологию нейронной сети, а функциональные параметры подбираются в процессе "обучения" уже сформированной сети и заносятся в локальную память функциональных параметров FM 10. Если же функциональные параметры заранее известны (сеть "обучена"), то порядок программирования и настройки устройства для обработки информации может быть произвольным.

Введение в структуру устройства локальных стеков пакетов данных DS 12 по числу операционных блоков PU 8, регистра готовности RR 14 и приоритетной цепи с циклическим назначением приоритетов PC 16, взаимосвязанной с регистром готовности RR 14 и с локальными стеками пакетов данных DS 12, позволяет решить поставленную задачу повышения производительности устройства для обработки информации за счет оперативного освобождения операционных блоков PU 8 от результатов обработки и их буферизации в локальных стеках пакетов данных 12, а также совмещения во времени процессов загрузки пакетов данных в локальные стеки пакетов данных DS 12 и их извлечения на параллельную шину РВ 1 и далее в соответствующие блоки стековой памяти результатов RS 4 без использования относительно медленного механизма кольцевой шины RB 8. Циклическое назначение приоритетов обеспечивает в заданном временном интервале равную вероятность обслуживания всем локальным стекам пакетов данных DS 12 вне зависимости от порядка их подключения к параллельной шине устройства для обработки информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2379751C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2006 |

|

RU2331923C2 |

| НЕЙРОСЕТЕВОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО | 2008 |

|

RU2394274C2 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ В НЕЙРОННЫХ СЕТЯХ | 2004 |

|

RU2263964C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2000 |

|

RU2179739C2 |

| НЕЙРОСЕТЕВОЕ ДИСКРЕТНОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО | 2003 |

|

RU2250501C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2000 |

|

RU2176815C1 |

| Устройство для асинхронной ассоциативной загрузки многопроцессорной вычислительной системы | 1986 |

|

SU1410053A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1536383A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении нейросетевых систем обработки информации. Техническим результатом изобретения является повышение производительности устройства за счет буферизации пакетов данных и обеспечения равновероятного обслуживания стеков пакетов данных с помощью механизма циклического назначения приоритетов. Устройство содержит параллельную шину, соединенную с блоками ввода и вывода данных, блоками стековой памяти результатов, взаимосвязанных с блоками локальной памяти данных, локальной памяти готовности данных, локальной памяти команд, локальной памяти функциональных параметров, кольцевую шину, с которой взаимосвязаны операционные блоки, блоки локальной памяти данных, локальной памяти команд, локальной памяти функциональных параметров, локальной памяти готовности данных и регистр занятости, локальные стеки пакетов данных, которые соединены с одноименными операционными блоками, параллельной шиной, регистром готовности и с приоритетной цепью с циклическим назначением приоритетов, которая соединена регистром готовности и с блоками стековой памяти результатов. 1 з.п. ф-лы, 2 ил.

1. Устройство для обработки информации, содержащее параллельную шину, соединенную с блоками ввода и блоками вывода данных, входными шинами блоков стековой памяти результатов, выходные шины которых соединены с входными шинами блоков локальной памяти данных и блоков локальной памяти готовности данных, кольцевую шину, с которой взаимосвязаны входные шины операционных блоков, выходные шины блоков локальной памяти данных, блоков локальной памяти команд, блоков локальной памяти функциональных параметров, блоков локальной памяти готовности данных и регистра занятости, каждый из разрядов которого соединен с управляющим выходом соответствующего операционного блока, отличающееся тем, что оно содержит локальные стеки пакетов данных, входные шины которых соединены с выходными шинами одноименных операционных блоков, выходные шины - с параллельной шиной, а первые управляющие выходы - с управляющими входами соответствующих операционных блоков, регистр готовности, каждый разряд которого соединен со вторым управляющим выходом одноименного локального стека пакетов данных, приоритетную цепь с циклическим назначением приоритетов, первые и вторые входы которой взаимосвязаны с прямым и инверсным выходами разрядов регистра готовности, первые выходы - с первыми управляющими входами соответствующих локальных стеков пакетов данных, второй выход - со вторыми управляющими входами всех локальных стеков пакетов данных, а третий вход соединен по схеме «монтажное ИЛИ» с управляющими выходами блоков стековой памяти результатов, выходные шины которых соединены с входными шинами блоков локальной памяти команд и блоков локальной памяти функциональных параметров.

2. Устройство для обработки информации по п.1, отличающееся тем, что приоритетная цепь с циклическим назначением приоритетов содержит сдвигающий регистр, взаимосвязанный с генератором тактовых импульсов, пары последовательно включенных двухвходовых логических элементов И и ИЛИ, соединенные в кольцо, трехвходовые логические элементы И по числу локальных стеков пакетов данных, первые входы трехвходовых логических элементов И соединены с третьим входом приоритетной цепи с циклическим назначением приоритетов, вторые входы трехвходовых логических элементов И - с одноименными первыми входами приоритетной цепи с циклическим назначением приоритетов и соответствующими входами многовходового логического элемента ИЛИ, первые входы двухвходовых логических элементов И соединены с соответствующими вторыми входами приоритетной цепи, вторые входы двухвходовых логических элементов И - с третьими входами соответствующих трехвходовых логических элементов И и выходами двухвходовых логических элементов ИЛИ соответствующей пары последовательно включенных двухвходовых логических элементов И и ИЛИ, первые входы двухвходовых логических элементов ИЛИ - с выходами двухвходовых логических элементов И предыдущей пары последовательно включенных двухвходовых логических элементов И и ИЛИ, вторые входы двухвходовых логических элементов ИЛИ - с соответствующими выходами сдвигающего регистра, а выход многовходового логического элемента ИЛИ взаимосвязан с вторым выходом приоритетной цепи с циклическим назначением приоритетов.

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2000 |

|

RU2179739C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2000 |

|

RU2176815C1 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ В НЕЙРОННЫХ СЕТЯХ | 2004 |

|

RU2263964C1 |

| JP 5197707 A, 06.08.1993 | |||

| WO 03096269 A1, 20.11.2003. | |||

Авторы

Даты

2009-11-20—Публикация

2008-03-03—Подача