Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки дискретной информации, в нейросетевом базисе.

Известно операционное устройство, предназначенное для параллельной обработки информации и содержащее операционные блоки, взаимосвязанные с локальной памятью команд, локальной памятью данных и локальными стеками результатов, блоки ввода и вывода данных, подключенные к параллельной шине [Компьютеры на СБИС: в 2-х кн. Кн. 1: Пер. с япон. / Мотоока Т., Томита С. и др. - М.: Мир, 1988, с.102-107].

Недостатком данного операционного устройства является решение задачи параллелизма вычислений посредством компилятора, который программными средствами определяет возможность одновременного выполнения программных фрагментов и производит их распределение по операционным блокам. Подобный подход не позволяет реализовать потенциальные возможности распараллеливания процесса решения задачи.

Известно также операционное устройство на базе регулярной структуры памяти, ориентированное на параллельное выполнение вычислений и содержащее взаимосвязанные посредством сети передачи пакетов данных операционные блоки, блоки памяти и блоки ввода/вывода данных [Майерс Г. Архитектура современных ЭВМ: В 2-х кн. Кн. 2 - Пер. с англ. - Мир, 1985, с.232-253].

Недостатком устройства является сложность сети передачи пакетов данных, не линейно возрастающая при увеличении числа операционных блоков, необходимых для эффективного решения задач нейросетевого базиса с высокой степенью распараллеливания вычислительного процесса.

Наиболее близким техническим решением к предлагаемому изобретению, выбранным авторами за прототип, является нейросетевое операционное устройство, предназначенное для параллельной обработки дискретной информации и содержащее локальные пулы командных пакетов, каждый из которых образован локальной памятью данных, локальной памятью готовности данных, локальной памятью команд и локальной функциональной памятью, первую кольцевую шину, с которой соединены выходные шины локальных пулов командных пакетов и входные шины взаимосвязанных с одноименными триггерами занятости операционных блоков, предназначенных для обработки командных пакетов и формирования пакетов данных, вторую кольцевую шину, с которой взаимосвязаны блоки ввода данных, блоки вывода данных с соответствующими схемами сравнения и локальные стеки данных с одноименными схемами сравнения, выходная шина локальных стеков данных соединена с входными шинами локальной памяти данных и локальной памяти готовности данных [Патент 2179739 РФ, МПК G06F 15/00. Устройство для обработки информации. / Г.Ф.Нестерук, Ф.Г.Нестерук. - № 2000108883/09; заявлено 10.04.2000; опубл. 20.02.2002. Бюл. № 5. Приоритет от 10.04.2000].

Недостатком прототипа является последовательный характер передачи командных пакетов от множества локальных пулов командных пакетов к множеству операционных блоков, что снижает общую производительность устройства.

Задачей настоящего изобретения является повышение производительности нейросетевого операционного устройства за счет аппаратной поддержки одновременной передачи командных пакетов от множества локальных пулов командных пакетов к множеству операционных блоков посредством параллельных регистров, позволяющих реализовать как параллельную передачу, так и сдвиг командных пакетов в первой кольцевой шине.

Поставленная задача достигается тем, что нейросетевое операционное устройство, предназначенное для параллельной обработки пакетов и содержащее локальные пулы командных пакетов, каждый из которых образован локальной памятью данных, локальной памятью готовности данных, локальной памятью команд и локальной функциональной памятью, первую кольцевую шину, которая последовательно объединяет параллельные регистры командных пакетов, содержащие одноименные разряды готовности, причем первая кольцевая шина соединена с входными шинами операционных блоков, взаимосвязанных с соответствующими триггерами занятости, при этом операционные блоки предназначены для обработки командных пакетов и формирования пакетов данных, вторую кольцевую шину, которая последовательно объединяет параллельные регистры пакетов данных, содержащие одноименные разряды готовности, выходная шина каждого локального стека данных соединена с входными шинами локальной памяти данных и локальной памяти готовности данных соответствующего локального пула командных пакетов, отличается тем, что оно дополнительно содержит локальные стеки результатов, параллельные регистры ввода/вывода с одноименными разрядами готовности, логический элемент И-НЕ и логические элементы Запрет по числу операционных блоков, причем вторая кольцевая шина, которая последовательно объединяет параллельные регистры пакетов данных с одноименными разрядами готовности, также объединяет параллельные регистры ввода/вывода с одноименными разрядами готовности, входная шина каждого локального стека результатов соединена с выходной шиной соответствующего операционного блока, выходные шины локальных стеков результатов соединены посредством второй кольцевой шины с входными шинами параллельных регистров пакетов данных, а управляющие входы и управляющие выходы каждого локального стека результатов соединены с разрядами готовности соответствующих параллельных регистров пакетов данных и первыми управляющими входами одноименных операционных блоков, второй управляющий вход каждого из операционных блоков соединен с выходом соответствующего логического элемента Запрет, прямой и инверсный входы каждого логического элемента Запрет соединены с разрядом готовности одноименного параллельного регистра командных пакетов и управляющим входом локальных пулов командных пакетов, а инверсный вход - с одноименным входом логического элемента И-НЕ, выходы триггеров занятости взаимосвязаны с соответствующим входом логического элемента И-НЕ, выход которого соединен с тактовыми входами параллельных регистров командных пакетов, управляющий вход каждого блоков ввода данных соединен с разрядом готовности соответствующего параллельного регистра ввода/вывода, выходная шина каждого блока ввода данных посредством второй кольцевой шины соединена с входной шиной соответствующего параллельного регистра ввода/вывода, входная шина каждого блока вывода данных соединена посредством второй кольцевой шины с выходной шиной соответствующего параллельного регистра ввода/вывода, управляющий вход каждого из блоков вывода данных соединен с выходом одноименной схемы сравнения, входные шины каждой из которых соединены с одноименным адресным регистром и с разрядом готовности соответствующего параллельного регистра ввода/вывода и с одноименной шиной адреса, входная шина каждого локального стека данных посредством второй кольцевой шины соединена с выходной шиной соответствующего параллельного регистра пакетов данных, управляющий вход каждого локального стека данных соединен с выходом другой одноименной схемы сравнения, входные шины каждой из которых соединены с одноименным адресным регистром и разрядом готовности соответствующего параллельного регистра пакетов данных и с одноименной шиной адреса, а выходные шины каждого локального стека данных соединены с входными шинами локальной памяти команд и локальной функциональной памяти соответствующего локального пула командных пакетов, а каждый локальный пул командных пакетов соединен с соответствующим параллельным регистром командных пакетов.

Кроме того, для ускорения освобождения параллельных регистров командных пакетов, входящих в состав первой кольцевой шины, за счет возможности буферизации командных пакетов на входах операционных блоков, в заявляемое нейросетевое операционное устройство введены буферные параллельные регистры, содержащие одноименные разряды готовности, входная и выходная шины каждого из буферных параллельных регистров соединены с выходной шиной соответствующего параллельного регистра командных пакетов и входной шиной одноименного операционного блока, первый и второй управляющие входы, а также управляющий выход каждого из буферных параллельных регистров соединены с выходом соответствующего логического элемента Запрет, выходом соответствующего триггера занятости, а также со вторым управляющим входом одноименных операционных блоков и инверсным входом одноименного логического элемента Запрет.

При реализации операционных устройств в соответствии с заявляемым изобретением возникает технический результат - повышение оперативности вычислений при эмуляции работы нейронной сети вследствие уменьшения непроизводительных затрат времени на передачу командных пакетов к операционным блокам. Дополнительным техническим результатом является повышение функциональной устойчивости операционного устройства вследствие того, что в его архитектуре заложена аппаратная избыточность, прежде всего в избыточном числе операционных блоков. Отказ ряда операционных блоков не сказывается на правильности функционирования заявляемого устройства, т.к. командные пакеты по первой кольцевой шине перенаправляются к свободным в данный момент времени исправным операционным блокам, у которых триггеры занятости сброшены. Функциональная устойчивость заявляемого нейросетевого операционного устройства обеспечивается безадресностью операционных блоков. Командные пакеты поступают на обработку только в исправные и свободные операционные блоки, триггеры занятости которых сброшены, в то время как в отказавших операционных блоках триггер занятости постоянно установлен.

Правильность функционирования заявляемого устройства при наличии неисправностей и отказов дополнительно обеспечивается информационной избыточностью нейронных сетей, для реализации которых предназначено заявляемое устройство. Известно, что деструкция фрагмента нейронной сети компенсируется избыточным распределенным хранением информации и не приводит к потере функциональности.

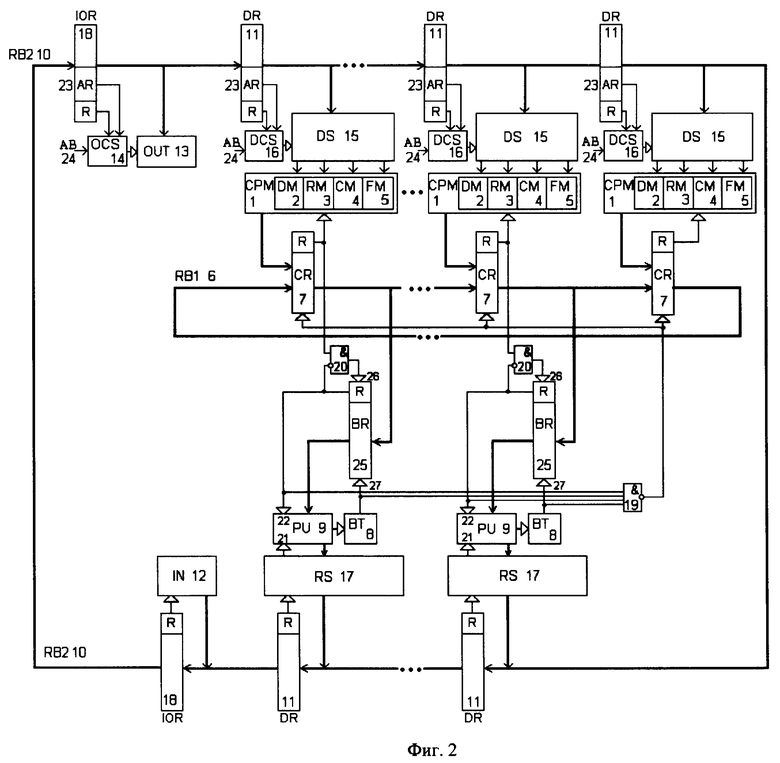

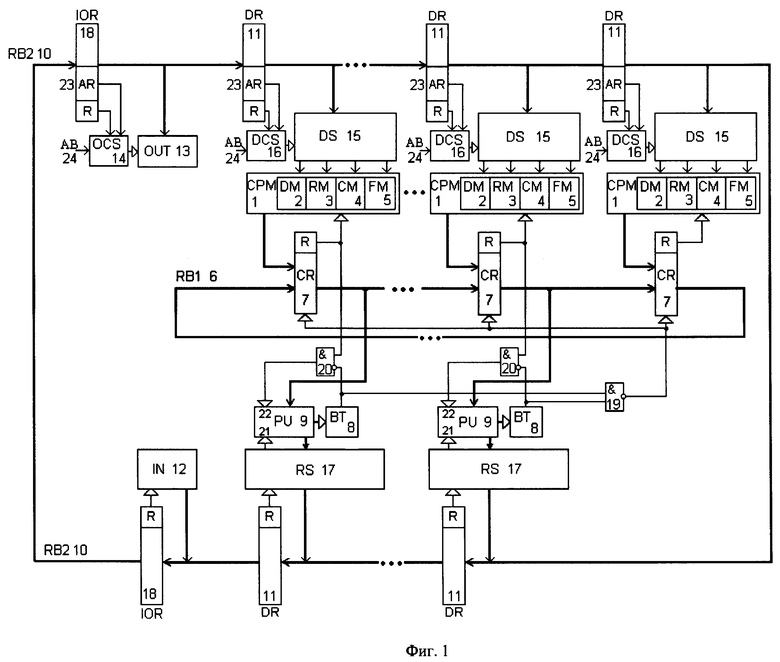

На фиг.1 представлена структурная схема заявляемого нейросетевого операционного устройства, а на фиг.2 - вариант нейросетевого операционного устройства с параллельными регистрами для буферизации командных пакетов.

Нейросетевое операционное устройство (фиг.1) содержит локальные пулы командных пакетов СРМ 1, каждый из которых образован локальной памятью данных DM 2, локальной памятью готовности данных RM 3, локальной памятью команд СМ 4 и локальной функциональной памятью FM 5, первую кольцевую шину RB1 6, в состав которой входят параллельные регистры командных пакетов CR 7, содержащие одноименные разряды готовности R, триггеры занятости ВТ 8, операционные блоки PU 9, предназначенные для обработки командных пакетов и формирования пакетов данных, вторую кольцевую шину RB2 10, в состав которой входят параллельные регистры пакетов данных DR 11 с одноименными разрядами готовности R, с которой взаимосвязаны блоки ввода данных IN 12, блоки вывода данных OUT 13 с соответствующими схемами сравнения OCS 14 и локальные стеки данных DS 15 с одноименными схемами сравнения DCS 16, локальные стеки результатов RS 17, параллельные регистры ввода/вывода IOR 18 с одноименными разрядами готовности R, логический элемент И-НЕ 19 и логические элементы Запрет 20 по числу операционных блоков PU 9, выходные шины локальных стеков результатов RS 17 взаимосвязаны с входными шинами параллельных регистров пакетов данных DR 11, а управляющие входы и управляющие выходы локальных стеков результатов RS 17 - с разрядами готовности соответствующих параллельных регистров пакетов данных DR 11 и первыми управляющими входами 21 одноименных операционных блоков PU 9, второй управляющий вход 22 каждого из операционных блоков PU 9 соединен с выходом соответствующего из логических элементов Запрет 20, входные шины схем сравнения DCS 16 соединены с одноименным из адресных регистров AR 23, с разрядом готовности R соответствующего параллельного регистра пакетов данных DR 11 и одноименной шины адреса АВ 24.

Рассмотрим функционирование нейросетевого операционного устройства, изображенного на фиг.1.

В режиме ввода исходных данных блоки ввода IN 12 формируют пакеты данных в формате:

и передают их на вторую кольцевую шину шины RB2 10 в параллельные регистры ввода/вывода IOR 18, если одноименный разряд готовности R сброшен (контейнер для передачи пакета данных свободен). Фиксация пакета данных в параллельном регистре ввода/вывода IOR 18 сопровождается установкой разряда готовности R (контейнер для передачи пакетов данных заполнен).

Во второй кольцевой шине RB2 10 в режиме сдвига производится последовательная перезапись пакета данных, выключающего разряд готовности R, в ближайший параллельный регистр пакетов данных DR 11 до тех пор, пока в одной из схем совпадения DCS 16 не будет сформирован сигнал равенства поля AR 23 параллельного регистра пакетов данных DR 11, содержащего код "Номер блока локальной памяти" пакета данных и кода адреса на соответствующей шине адреса АВ 24. Сформированный сигнал поступает на управляющий вход локального стека данных DS 15 и вызывает занесение пакета данных в соответствующий локальный стек данных DS 15. При этом происходит сброс разряда готовности R одноименного параллельного регистра пакетов данных DR 11 (контейнер для передачи пакетов данных свободен).

Поле "Значение" пакета данных из локального стека данных DS 15 заносится в ячейку локальной памяти данных DM 2 в соответствии с полями "Адрес командного пакета", "Адрес в пакете" пакета данных. Одновременно в том же адресном сечении локальной памяти готовности данных RM 3 сбрасывается в нуль бит готовности. Сброс в нуль всех битов готовности в некотором адресном сечении блока локальной памяти готовности данных RM 3 инициирует выборку командного пакета из данного адресного сечения локального пула командных пакетов СРМ 1 и его передачу на первую кольцевую шину RB1 6 (занесение в параллельный регистр командных пакетов CR 7) при условии, что сброшен разряд готовности R одноименного параллельного регистра командных пакетов CR 7. При этом в данное адресное сечение блока локальной памяти готовности данных RM 3 записывается слово из одних единиц.

В процессе обработки командные пакеты, зафиксированные в параллельных регистрах командных пакетов CR 7 (с установленным разрядом готовности R), будут переданы в те из операционных блоков PU 9, триггеры занятости ВТ 8 которых сброшены (PU исправны и свободны), т.е. в те из операционных блоков PU 9, на второй управляющий вход 22 которых поступит сигнал с выхода одноименного логического элемента Запрет 20. Фиксация командного пакета во входных цепях операционных блоков PU 9 устанавливает соответствующие триггеры занятости ВТ 8 и приводит к сбросу разрядов готовности R одноименных параллельных регистров командных пакетов CR 7 (контейнер для передачи командных пакетов свободен).

Если в результате рассмотренной передачи командных пакетов останутся свободные операционные блоки PU 9 (триггеры занятости ВТ 8 которых сброшены), то на выходе логического элемента И-НЕ 19 сформируется сигнал сдвига, управляющий тактовыми входами параллельных регистров командных пакетов CR 7, и произойдет перезапись командных пакетов, выключая разряды готовности R, в соответствующие соседние параллельные регистры командных пакетов CR 7.

При этом на вторых управляющих входах 22 ряда свободных операционных блоков PU 9 может быть сформирован высокий уровень сигнала с выходов одноименных логических элементов Запрет 20, что приведет к фиксации командных пакетов во входных цепях соответствующих операционных блоков PU 9.

В случае занятости всех исправных операционных блоков PU 9 низкий уровень сигнала сдвига с выхода логического элемента И-НЕ 19 не позволяет тактировать операцию перезаписи командных пакетов в параллельных регистрах командных пакетов CR 7 до того момента, пока не освободится хотя бы один из операционных блоков PU 9 (не будет сброшен хотя бы один из триггеров занятости ВТ 8).

Зафиксированный во входных цепях операционного блока PU 9 командный пакет представлен в формате:

и содержит полный набор значений данных, подлежащих обработке, функциональных параметров компонентов нейронной сети, указание на реализуемую операцию и коды адресов командных пакетов - приемников результата. Операционный блок PU 9 после завершения обработки формирует столько пакетов данных, сколько адресов командных пакетов - приемников результата - он содержит, и по мере формирования пакеты данных заносятся в локальные стеки результатов RS 17, если на первый управляющий вход 21 соответствующего операционного блока PU 9 поступает сигнал «стек результатов не заполнен» с управляющего выхода одноименного локального стека результатов RS 17. Только после передачи всех подготовленных операционным блоком PU 9 пакетов данных сбрасывается в нуль соответствующий триггер занятости ВТ 8.

Пакеты данных с выходной шины соответствующих локальных стеков результатов RS 17 заносятся в одноименные параллельные регистры пакетов данных DR 11, если их разряды готовности R сброшены (контейнер для передачи пакетов данных свободен). Далее - аналогично процессу ввода исходных данных.

При выводе результаты вычислений, формируемые операционными блоками PU 9 в виде пакетов данных, адресное поле каждого из которых соответствует одному из адресов блоков вывода данных OUT 13, поступают на вторую кольцевую шину RB2 10 и по мере сдвига фиксируются в параллельных регистрах ввода/вывода IOR 18. При совпадении полей "Номер блока локальной памяти" пакетов данных с адресами блоков вывода данных OUT 13, поданных на адресные шины АВ 24, и установленных разрядах готовности R одноименных параллельных регистров ввода/вывода IOR 18 (контейнер для передачи пакетов данных заполнен) осуществляется передача пакетов выводимых данных из параллельных регистров ввода/вывода IOR 18 в блоки вывода данных OUT 13 с одновременной сбросом разрядов готовности R соответствующих параллельных регистров ввода/вывода IOR 18 (контейнер для передачи пакетов данных свободен).

Режим программирования нейросетевого операционного устройства. Программирование заявляемого устройства осуществляется перед началом его использования в рабочем режиме. При программировании необходимо для каждого командного пакета в соответствующее адресное сечение блока локальной памяти команд СМ 4 ввести коды адресов командных пакетов - приемников результата. В этом случае значение адреса командного пакета - приемника результата (поле "значение") пакета данных, формируемого в блоке ввода данных IN 12, через вторую кольцевую шину RB2 10 и соответствующий локальный стек данных DS 15 заносится в адресное сечение (поле "адрес командного пакета" и поле "адрес в пакете") заданного блока локальной памяти команд СМ 4 (поле "номер блока локальной памяти").

Режим настройки функциональных параметров нейросетевого операционного устройства. Настройка функциональных параметров производится после осуществления программирования заявляемого устройства, но перед его использованием в рабочем режиме. Процесс занесения значений функциональных параметров аналогичен вышерассмотренной последовательности программирования с той лишь разницей, что поле "значение" пакета данных помещается в адресное сечение соответствующей локальной функциональной памяти FM 5. Выполнение процедуры настройки после осуществления программирования устройства характерно для "необученной" нейронной сети, т.к. процесс программирования задает топологию нейронной сети, а функциональные параметры подбираются и заносятся в локальную функциональную память FM 5 в процессе обучения уже сформированной сети. Если же функциональные параметры заранее известны (сеть обучена), то порядок программирования и настройки отказоустойчивого нейросетевого устройства роли не играет.

Фиг.2 иллюстрирует вариант нейросетевого операционного устройства с буферизацией командных пакетов, в которое дополнительно включены буферные параллельные регистры BR 25, содержащие одноименные разряды готовности R, входная и выходная шины каждого из буферных параллельных регистров BR 25 соединены с выходной шиной соответствующего параллельного регистра командных пакетов CR 7 и входной шиной одноименного операционного блока PU 9, первый 26 и второй 27 управляющие входы, а также управляющий выход каждого из буферных параллельных регистров BR 25 соединены с выходом соответствующего логического элемента Запрет 20, выходом соответствующего триггера занятости ВТ 8, а также со вторым управляющим входом 22 одноименного операционных блоков PU 9 и инверсным входом одноименного логического элемента Запрет 20.

Функционирование варианта нейросетевого операционного устройства (фиг.2) аналогично описанному выше с небольшими изменениями в режиме обработки командных пакетов, которые вызваны введением буферных параллельных регистров BR 25 в состав заявляемого устройства.

В процессе обработки командные пакеты, зафиксированные в параллельных регистрах командных пакетов CR 7 (с установленным разрядом готовности R), будут переданы в те из буферных параллельных регистров BR 25, разряды готовности R которых сброшены, т.е. в буферные параллельные регистры BR 25, выбранные высоким уровнем сигнала по первому 26 управляющему входу с выхода соответствующего логического элемента Запрет 20. Процесс записи в буферные параллельные регистры BR 25 сопровождается сбросом разрядов готовности R соответствующих параллельных регистров командных пакетов CR 7. В случае, если одноименные операционные блоки PU 9 исправны и свободны (триггеры занятости ВТ 8 сброшены и на вторых управляющих входах 27 буферных параллельных регистров BR 25 низкий уровень сигнала), то пакеты данных будут зафиксированы во входных цепях операционных блоков PU 9, на второй управляющий вход 22 которых поступает высокий уровень сигнала с выхода разряда готовности R одноименных буферных параллельных регистров BR 25. Фиксация командного пакета во входных цепях операционных блоков PU 9 устанавливает соответствующие триггеры занятости ВТ 8 и приводит к сбросу разрядов готовности R одноименных буферных параллельных регистров BR 25.

Если в результате рассмотренной передачи командных пакетов останутся свободные буферные параллельные регистры BR 25 (разряды готовности R которых сброшены), то на выходе логического элемента И-НЕ 19 сформируется сигнал сдвига, управляющий тактовыми входами параллельных регистров командных пакетов CR 7, и произойдет перезапись командных пакетов, выключая разряды готовности R, в соответствующие соседние параллельные регистры командных пакетов CR 7.

При этом могут создаваться описанные выше условия для занесения командных пакетов в буферные параллельные регистры BR 25 и для освобождения параллельных регистров командных пакетов CR 7 для фиксации командных пакетов, вновь формируемых в локальных пулах командных пакетов СРМ 1 и т.д.

В случае занятости всех буферных параллельных регистров BR 25 низкий уровень сигнала сдвига с выхода логического элемента И-НЕ 19 не позволяет тактировать операцию перезаписи командных пакетов в параллельных регистрах командных пакетов CR 7 до того момента, пока не освободится хотя бы один из буферных параллельных регистров BR 25 (не будет сброшен соответствующий разряд готовности R).

Реализуемость нейросетевого операционного устройства обусловлена использованием в составе заявляемого устройства общепринятых технических решений блоков, узлов и элементов (см., например, Каган Б. М. Электронные вычислительные машины и системы. - М.: Энергоатомиздат, 1991), известных схемотехнических решений нейронных сетей (см., например, Галушкин А.И. Нейрокомпьютеры и их применение. - М.: ИПРЖР, 2000. - Кн. 3), а также следует из вышеприведенного описания работы нейросетевого операционного устройства в различных режимах его функционирования.

На основе вышеизложенного заявляемая совокупность компонентов нейросетевого операционного устройства позволяет решить поставленную задачу повышения производительности устройства за счет аппаратной поддержки как параллельной передачи, так и сдвига командных пакетов посредством первой кольцевой шины, что говорит о достижении поставленной цели.

Эффект повышения функциональной устойчивости в заявляемом устройстве обусловлен описанной выше взаимосвязью его компонентов, которая обеспечивает аппаратную избыточность в числе операционных блоков и отказ ряда операционных блоков не сказывается на правильности функционирования заявляемого устройства, т.к. командные пакеты перенаправляются к свободным и исправным операционным блокам.

Правильность функционирования устройства при наличии неисправностей и отказов также обеспечивается информационной избыточностью нейронных сетей, для реализации которых предназначено заявляемое устройство. Известно (см., например, Галушкин А.И. Нейрокомпьютеры и их применение. - М.: ИПРЖР, 2000. - Кн. 3), что деструкция фрагмента нейронной сети компенсируется избыточным распределенным хранением информации и не приводит к потере функциональности.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2373568C1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2379751C2 |

| НЕЙРОСЕТЕВОЕ ДИСКРЕТНОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО | 2003 |

|

RU2250501C2 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ В НЕЙРОННЫХ СЕТЯХ | 2004 |

|

RU2263964C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2006 |

|

RU2331923C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2000 |

|

RU2176815C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2000 |

|

RU2179739C2 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки дискретной информации. Техническим результатом является повышение производительности устройства за счет обеспечения как одновременной передачи командных пакетов посредством параллельных регистров, так и сдвига командных пакетов посредством кольцевой шины. Нейросетевое операционное устройство содержит первую кольцевую шину для передачи командных пакетов, блоки локальной памяти данных, локальной памяти готовности данных, локальной памяти команд и локальной функциональной памяти, которые образуют блоки локальной памяти командных пакетов, операционные блоки, триггеры занятости, вторую кольцевую шину для передачи пакетов данных, блоки ввода данных и блоки вывода данных, локальные стеки результатов, параллельные регистры ввода/вывода с разрядами готовности, логический элемент И-НЕ и логические элементы Запрет по числу операционных блоков, причем параллельные регистры пакетов данных с разрядами готовности и параллельные регистры ввода/вывода с разрядами готовности образуют вторую кольцевую шину. 1 з.п. ф-лы, 2 ил.

1. Нейросетевое операционное устройство, предназначенное для параллельной обработки пакетов и содержащее локальные пулы командных пакетов, каждый из которых образован локальной памятью данных, локальной памятью готовности данных, локальной памятью команд и локальной функциональной памятью, первую кольцевую шину, которая последовательно объединяет параллельные регистры командных пакетов, содержащие одноименные разряды готовности, причем первая кольцевая шина соединена с входными шинами операционных блоков, взаимосвязанных с соответствующими триггерами занятости, при этом операционные блоки предназначены для обработки командных пакетов и формирования пакетов данных, вторую кольцевую шину, которая последовательно объединяет параллельные регистры пакетов данных, содержащие одноименные разряды готовности, выходная шина каждого локального стека данных соединена с входными шинами локальной памяти данных и локальной памяти готовности данных соответствующего локального пула командных пакетов, отличающееся тем, что оно дополнительно содержит локальные стеки результатов, параллельные регистры ввода/вывода с одноименными разрядами готовности, логический элемент И-НЕ и логические элементы Запрет по числу операционных блоков, причем вторая кольцевая шина, которая последовательно объединяет параллельные регистры пакетов данных с одноименными разрядами готовности, также объединяет параллельные регистры ввода/вывода с одноименными разрядами готовности, входная шина каждого локального стека результатов соединена с выходной шиной соответствующего операционного блока, выходные шины локальных стеков результатов соединены посредством второй кольцевой шины с входными шинами параллельных регистров пакетов данных, а управляющие входы и управляющие выходы каждого локального стека результатов соединены с разрядами готовности соответствующих параллельных регистров пакетов данных и первыми управляющими входами одноименных операционных блоков, второй управляющий вход каждого из операционных блоков соединен с выходом соответствующего логического элемента Запрет, прямой и инверсный входы каждого логического элемента Запрет соединены с разрядом готовности одноименного параллельного регистра командных пакетов и управляющим входом локальных пулов командных пакетов, а инверсный вход - с одноименным входом логического элемента И-НЕ, выходы триггеров занятости взаимосвязаны с соответствующим входом логического элемента И-НЕ, выход которого соединен с тактовыми входами параллельных регистров командных пакетов, управляющий вход каждого блоков ввода данных соединен с разрядом готовности соответствующего параллельного регистра ввода/вывода, выходная шина каждого блока ввода данных посредством второй кольцевой шины соединена с входной шиной соответствующего параллельного регистра ввода/вывода, входная шина каждого блока вывода данных соединена посредством второй кольцевой шины с выходной шиной соответствующего параллельного регистра ввода/вывода, управляющий вход каждого из блоков вывода данных соединен с выходом одноименной схемы сравнения, входные шины каждой из которых соединены с одноименным адресным регистром и с разрядом готовности соответствующего параллельного регистра ввода/вывода и с одноименной шиной адреса, входная шина каждого локального стека данных посредством второй кольцевой шины соединена с выходной шиной соответствующего параллельного регистра пакетов данных, управляющий вход каждого локального стека данных соединен с выходом другой одноименной схемы сравнения, входные шины каждой из которых соединены с одноименным адресным регистром и разрядом готовности соответствующего параллельного регистра пакетов данных и с одноименной шиной адреса, а выходные шины каждого локального стека данных соединены с входными шинами локальной памяти команд и локальной функциональной памяти соответствующего локального пула командных пакетов, а каждый локальный пул командных пакетов соединен с соответствующим параллельным регистром командных пакетов.

2. Нейросетевое операционное устройство по п.1, отличающееся тем, что оно содержит буферные параллельные регистры, содержащие одноименные разряды готовности, входная и выходная шины каждого из буферных параллельных регистров соединены с выходной шиной соответствующего параллельного регистра командных пакетов и входной шиной одноименного операционного блока, первый и второй управляющие входы, а также управляющий выход каждого из буферных параллельных регистров соединены с выходом соответствующего логического элемента Запрет, выходом соответствующего триггера занятости, а также со вторым управляющим входом одноименного операционных блоков и инверсным входом одноименного логического элемента Запрет.

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2000 |

|

RU2179739C2 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ В НЕЙРОННЫХ СЕТЯХ | 2004 |

|

RU2263964C1 |

| НЕЙРОСЕТЕВОЕ ДИСКРЕТНОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО | 2003 |

|

RU2250501C2 |

| RU 2006134402 A, 10.04.2008 | |||

| JP 5197707 A, 06.08.1993. | |||

Авторы

Даты

2010-07-10—Публикация

2008-06-02—Подача