Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки информации в нейросетевом базисе.

Известно устройство для обработки информации на базе регулярной структуры ЗУПВ, ориентированное на параллельное выполнение вычислений и содержащее взаимосвязанные посредством коммутатора операционные блоки, блоки памяти, и блоки ввода/вывода данных [Паттерсон Д., Андерсон Т., Кадвел Н., Фромм Р., Китон К., Козяракис К., Томас Р, Елик К. Доводы в пользу IRAM. - Компьютерра, №15, 1998, Приложение С.3-14].

Вследствие ограниченного числа процессорных блоков данное устройство не позволяет эффективно решать задачи нейросетевого базиса с высокой степенью распараллеливания вычислительного процесса.

Известно устройство для обработки информации, содержащее командные пулы, образованные блоками памяти команд, памяти данных и стековой памятью данных, операционные блоки, взаимосвязанные с командными пулами, а также блоки ввода и вывода данных, подключенные к параллельной шине [Компьютеры на СБИС: в 2-х кн. Кн. 1: Пер. с япон. / Мотоока Т., Томита С. и др. - М.: Мир, 1988, с.102-107].

Недостаток этого устройства - программное распараллеливание вычислений: с помощью компилятора определяется возможность одновременного выполнения ряда программных фрагментов и производится их закрепление за конкретными операционными блоками. Подобный подход не позволяет реализовать потенциальные возможности распараллеливания вычислительного процесса.

Наиболее близким техническим решением к предлагаемому изобретению, выбранным авторами за прототип, является устройство для обработки информации, содержащее пулы командных пакетов, каждый из которых образован из блоков локальной памяти команд, локальной памяти функциональных параметров, локальной памяти готовности данных и взаимосвязан с одноименным блоком стековой памяти результатов и кольцевой шиной, с которой соединены блоки ввода данных, блоки вывода данных [Патент 2179739 РФ, МПК G06F 15/00. Устройство для обработки информации. / Г.Ф.Нестерук, Ф.Г.Нестерук. - №2000108883/09; заявлено 10.04.2000; опубл. 20.02.2002. Бюл. №5. Приоритет от 10.04.2000].

Недостатком прототипа является разнесение процессов обработки и хранения информации во времени и в структуре устройства, что снижает общую производительность вычислений вследствие интенсивного обмена данными между памятью и операционными блоками.

Задачей настоящего изобретения является повышение производительности вычислений за счет организации обработки информации по месту ее хранения в пулах командных пакетов и совмещения во времени процессов занесения и преобразования данных.

Поставленная задача достигается тем, что в каждый из пулов командных пакетов устройства для обработки информации введены блок памяти управления готовностью, схема готовности, дешифратор, блок аккумуляторной памяти, умножитель, сумматор, блок функции активации и регистр пакетов данных, а каждый из блоков стековой памяти данных взаимосвязан с приоритетной цепью, схемами сравнения и входным фиксатором, образованным адресными регистрами по числу коммуникационных полей пакета данных и регистром данных, причем входные фиксаторы взаимосвязаны с кольцевой шиной и входной шиной соответствующего из блоков стековой памяти данных, а адресные регистры - с входами соответствующих схем сравнения и первыми выходами приоритетной цепи, первые входы каждой из которых соединены с выходами схем сравнения, а второй вход и второй выход - с выходом и входом одноименного блока стековой памяти данных, выходная шина адреса каждого из блоков стековой памяти данных взаимосвязана с адресными шинами блоков памяти команд, аккумуляторной памяти, памяти готовности данных, памяти управления готовностью, адресным регистром блока памяти функциональных параметров и дешифратором, а выходная шина каждого из блоков стековой памяти данных - с шинами данных блоков памяти команд, памяти функциональных параметров и входной шиной умножителя, вторая входная и выходная шины которого соединены соответственно с выходной шиной блока памяти функциональных параметров и входной шинной сумматора, вторая входная шина которого соединена с выходной шиной блока аккумуляторной памяти, а выходная шина - с входным регистром блока аккумуляторной памяти и входной шиной блока функции активации, выходные шины блока функции активации и блока памяти команд взаимосвязаны с входной шиной регистра пакетов данных, выходная шина которого соединена с кольцевой шиной, выходные шины одноименных блоков памяти готовности данных, памяти управления готовностью и дешифратора поразрядно объединены и взаимосвязаны с входным регистром блока памяти готовности данных и с входной шиной соответствующей схемы готовности, выход каждой из которых соединен с первым управляющим входом соответствующих входного регистра блока памяти готовности данных, входного регистра блока аккумуляторной памяти, адресного регистра блока памяти функциональных параметров и регистром пакетов данных, а вторые выходы всех приоритетных цепей объединены логическим элементом ИЛИ, взаимосвязанным со вторыми управляющими входами всех регистров пакетов данных.

Кроме того, в заявляемом устройстве для обработки информации приоритетная цепь содержит двухвходовые логические элементы И-НЕ и последовательно включенные двухвходовые логические элементы И, первые входы двухвходовых логических элементов И-НЕ соединены с соответствующими первыми входами приоритетной цепи, выходы двухвходовых логических элементов И-НЕ - с соответствующими первыми выходами приоритетной цепи, входами многовходового логического элемента И и первыми входами одноименных двухвходовых логических элементов И, второй вход приоритетной цепи соединен со вторым входом первого двухвходового логического элемента И-НЕ и вторым входом первого двухвходового логического элемента И, а вторые входы остальных двухвходовых логических элементов И-НЕ и двухвходовых логических элементов И - с выходами предыдущих двухвходовых логических элементов И.

При реализации устройств для обработки информации в соответствии с заявляемым изобретением возникает технический результат - повышение оперативности расчетов вследствие снижения времени эмуляции вычислительного процесса, выполняемого нейронной сетью. Дополнительным важным техническим результатом является повышение защищенности данных в устройстве для обработки информации вследствие того, что:

- операция записи данных производится не по конкретному адресу блоков памяти, а по содержанию полей пакета данных;

- отсутствует операция считывания данных из памяти и, следовательно, непосредственный доступ к хранимой информации;

- готовые к обработке данные, представленные в виде пакетов данных, извлекаются из памяти автоматически - без управления извне.

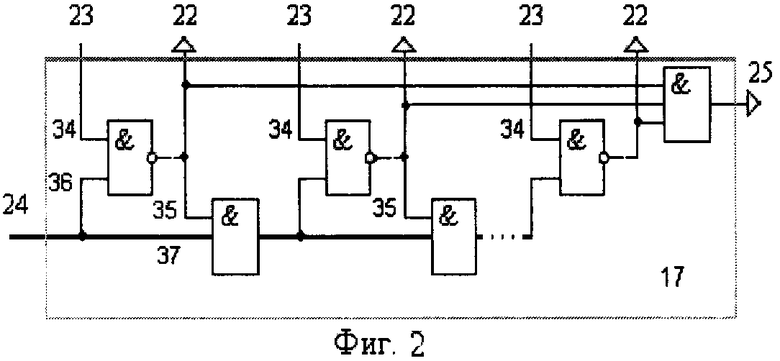

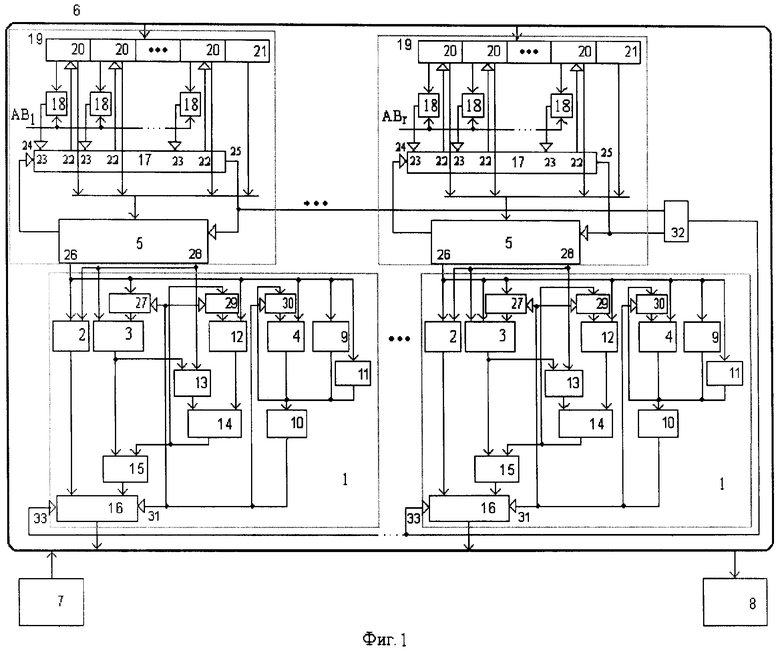

На фиг.1 представлена структурная схема предлагаемого устройства для обработки информации, а на фиг.2 - один из возможных вариантов построения приоритетной цепи.

Устройство для обработки информации содержит пулы командных пакетов 1, каждый из которых образован из блоков памяти команд 2, памяти функциональных параметров 3, памяти готовности данных 4 и взаимосвязан с одноименным блоком стековой памяти данных 5 и кольцевой шиной 6, с которой соединены блоки ввода данных 7, блоки вывода данных 8. В каждый из пулов командных пакетов введены блок памяти управления готовностью 9, схема готовности 10 и дешифратор 11, блок аккумуляторной памяти 12, умножитель 13, сумматор 14, блок функции активации 15 и регистр пакетов данных 16, а каждый из блоков стековой памяти данных 5 взаимосвязан с приоритетной цепью 17, которая соединена со схемами сравнения 18 и входным фиксатором 19, образованным адресными регистрами 20 по числу коммуникационных полей пакета данных и регистром данных 21, причем входные фиксаторы 19 взаимосвязаны с кольцевой шиной 6 и входной шиной соответствующего из блоков стековой памяти данных 5, а адресные регистры 20 - с входами соответствующих схем сравнения 18 и первыми выходами 22 приоритетной цепи 17, первые входы 23 каждой из которых соединены с выходами схем сравнения 18, а второй вход 24 и второй выход 25 - с выходом и входом одноименного блока стековой памяти данных 5, выходная шина адреса 26 каждого из блоков стековой памяти данных 5 взаимосвязана с адресными шинами блоков памяти команд 2, аккумуляторной памяти 12, памяти готовности данных 4, памяти управления готовностью 9, адресным регистром 27 блока памяти функциональных параметров 3 и дешифратором 11, а выходная шина 28 каждого из блоков стековой памяти данных 5 - с шинами данных блоков памяти команд 2, памяти функциональных параметров 3 и входной шиной умножителя 13, вторая входная и выходная шины которого соединены соответственно с выходной шиной блока памяти функциональных параметров 3 и входной шинной сумматора 14, вторая входная шина которого соединена с выходной шиной блока аккумуляторной памяти 12, а выходная шина - с входным регистром 29 блока аккумуляторной памяти 12 и входной шиной блока функции активации 15, выходные шины блока функции активации 15 и блока памяти команд 2 взаимосвязаны с входной шиной регистра пакетов данных 16, выходная шина которого соединена с кольцевой шиной 6, выходные шины одноименных блоков памяти готовности данных 4, памяти управления готовностью 9 и дешифратора 11 поразрядно объедены и взаимосвязаны с входным регистром 30 блока памяти готовности данных 4 и с входной шиной соответствующей схемы готовности 10, выход каждой из которых соединен с управляющим входом соответствующих входного регистра 30 блока памяти готовности данных 4, входного регистра 29 блока аккумуляторной памяти 12, адресного регистра 27 блока памяти функциональных параметров 3 и первым управляющим входом 31 регистра пакетов данных 16, а вторые выходы 25 всех приоритетных цепей 17 объединены логическим элементом ИЛИ 32, взаимосвязанным со вторыми управляющими входами 33 всех регистров пакетов данных 16.

Приоритетная цепь 17 может содержать двухвходовые логические элементы И-НЕ и последовательно включенные двухвходовые логические элементы И, первые входы 34 логических элементов И-НЕ соединены с соответствующими первыми входами 23 приоритетной цепи 17, выходы логических элементов И-НЕ - с соответствующими первыми выходами 22 приоритетной цепи 17, входами многовходового логического элемента И и первыми входами 35 одноименных логических элементов И, второй вход 24 приоритетной цепи соединен со вторым входом 36 первого логического элемента И-НЕ и вторым входом 37 первого логического элемента И, а вторые входы остальных логических элементов И-НЕ и логических элементов И - с выходами предыдущих логических элементов И.

Рассмотрим функционирование устройства для обработки информации, изображенного на фиг.1, в котором использована приоритетная цепь, выполненная в соответствии с фиг.2.

В соответствии со значениями сигналов с выходов схем совпадения 18, поступающих на первые входы 23 приоритетной цепи 17, первые выходы 22 приоритетной цепи 17 обеспечивают выбор одного из адресных регистров 20 входного фиксатора 19 и запрет выбора остальных регистров 20. В случае полного заполнения блока стековой памяти данных 5 уровень логического нуля на втором входе 24 приоритетной цепи 17 блокирует передачу адресного поля из регистра 20 и значения данных из регистра 21 входного фиксатора 19. Если же в блоке стековой памяти данных 5 освобождается хотя бы один уровень, то на втором входе 24 приоритетной цепи 17 появляется уровень логической единицы, который разрешает выдачу унитарного кода выборки на первые выходы 22 приоритетной цепи 17. Если ни одна из схем сравнения 18 не сформировала сигнала совпадения на первых входах 23 приоритетной цепи 17 или на второй вход 24 приоритетной цепи 17 поступил уровень логического нуля (в случае полного заполнения блока стековой памяти данных 5), то на втором выходе 25 приоритетной цепи 17 формируется сигнал запрещения загрузки блока стековой памяти данных 5.

При вводе исходные данные в блоках ввода 7 представляют в виде пакетов данных в формате:

Вводимые пакеты данных с кольцевой шины 6 поступают во входные фиксаторы 19, причем поле "Значение" заносится в регистр 21, а коммуникационные поля в составе "Номер командного пула", "Адрес командной ячейки", "Адрес в ячейке" - в соответствующие адресные регистры 20. Схемы сравнения 18 осуществляют сравнение адреса АВi (1≤I≤r), r - количество пулов командных пакетов в устройстве, i-го блока стековой памяти данных 5, с полями "Номер командного пула" всех адресных регистров 20. Совпадение хотя бы в одной схеме сравнения 18 адреса АВi с содержимым регистра 20 устанавливает уровень логической единицы на соответствующем первом входе 23 приоритетной цепи 17, что приводит к формированию на соответствующем втором выходе 22 приоритетной цепи 17 уровня логического нуля сигнала выборки адресного регистра 20 и на втором выходе 25 приоритетной цепи 17 сигнала разрешения загрузки блока стековой памяти данных 5. В блок стековой памяти данных 5 загружаются коммуникационное поле из выбранного адресного регистра 20 и значение данных из регистра данных 21, коды которых затем появляются, соответственно, на выходной шине адреса 26 и выходной шине данных 28. Поле "Значение" хi по шине данных 28 поступает в пул командных пакетов 1. Причем в командном пуле 1 фиксируется не вводимый по шине 28 код значения хi, а выбранное (в соответствии с адресной информацией на шине 26) из блока памяти функциональных параметров 3 значение весового коэффициента wi, которое при передаче через умножитель 13 преобразуется в значение произведения xiwi, и складывается на сумматоре 14 с ранее накопленным значением, выбранным из того же адресного сечения блока аккумуляторной памяти 12. На выходе сумматора формируется новое значение, которое через входной регистр 29 фиксируется по тому же адресу в блоке аккумуляторной памяти 12. Другими словами, в ячейке командного пула 1 хранятся не значения хi, а производится накопление произведений xiwi, ассоциированных со всеми поступившими к настоящему времени входными значениями хi. Одновременно в том же адресном сечении блока памяти готовности данных 4 устанавливается в нуль соответствующий бит готовности за счет выполнения поразрядной операции "монтажное ИЛИ" между выбранным из памяти 4 текущим значением слова готовности, считанным из блока памяти управления готовностью 9 словом и унитарным кодом, формируемым дешифратором 11 в соответствии с кодом из поля "Адрес в ячейке" пакета данных. Результат поразрядной операции через входной регистр 30 фиксируется в том же адресном сечении блока памяти готовности данных 4 в качестве текущего слова готовности данных. Установка в нуль всех битов готовности в некотором адресном сечении блока памяти готовности данных 4 отслеживается схемой готовности 10, которая инициирует выдачу в регистр пакетов данных 16 и далее на кольцевую шину 6 пакетов данных, в коммуникационные поля которых заносится адресная информация о командных ячейках - приемниках результата (поля "Номер командного пула", "Адрес командной ячейки", "Адрес в ячейке") из блока памяти команд 2, а в поле "Значение" - цифровой код с выхода блока функции активации 15, который выполняет сравнение накопленной в блоке аккумуляторной памяти 12 суммы всех поступивших к данному моменту произведений хiwi с порогом срабатывания формального нейрона w0, выбранного из блока памяти функциональных параметров 3, и автоматическое масштабирование результата. Выдача w0 обеспечивается обнулением адресного регистра 27, через который на адресную шину блока памяти функциональных параметров 3 поступает поле "Адрес в ячейке" пакета данных. После фиксации пакета данных в регистре 16 командная ячейка переводится в исходное состояние путем обнуления входного регистра 29 и соответствующего адресного сечения блока аккумуляторной памяти 12 и записи слова из всех единиц через входной регистр 30 в то же адресное сечение блока памяти готовности данных 4 заявляемого устройства для обработки информации.

Процесс обработки, как следует из изложенного выше, в устройстве для обработки информации производится непосредственно в пулах командных пакетов 1 и совмещен во времени с фиксацией вновь поступающих пакетов данных в блоке стековой памяти данных 5. Причем сам процесс обработки заключается в циклическом выполнении операций чтения, модификации и записи содержимого блока памяти готовности данных 4, блока аккумуляторной памяти 12 и блока памяти функциональных параметров 3, завершение которого контролируется схемами готовности 10, переводящими активные командные ячейки в исходное состояние и разрешающие формирование пакетов данных в 16. Сформированные пакеты данных поступают в кольцевую шину 6 и заносятся через входные фиксаторы 19 в соответствующие полям "Номер командного пула" блоки стековой памяти данных 5. Далее - аналогично процессу ввода исходных данных.

При выводе результаты вычислений в виде пакетов данных, коммуникационные поля каждого из которых соответствует одному из адресов блоков вывода данных 8, поступают на кольцевую шину 6 и заносятся во входные фиксаторы блоков вывода данных 8.

Режим программирования устройства для обработки информации необходим для задания топологии реализуемой нейронной сети. При программировании необходимо для каждого командного пакета в соответствующее адресное сечение блока памяти команд 2 ввести коды адресов командных пакетов - приемников результата. В этом случае значение адреса командного пакета - приемника результата (поле "Значение") пакета данных, формируемого в блоке ввода 7, через кольцевую шину 6, входной фиксатор 19 заносится в блок стековой памяти данных 5 (поле "Номер командного пула"), а затем через шину 28 - в адресное сечение (поле "Адрес командной ячейки" и поле "Адрес в ячейке") блока памяти команд 2.

Режим настройки функциональных параметров устройства для обработки информации необходим для задания весовых коэффициентов и порогов срабатывания формальных нейронов сети. Настройка функциональных параметров производится, как правило, после осуществления программирования заявляемого устройства. Процесс занесения значений функциональных параметров аналогичен вышерассмотренной последовательности программирования с той лишь разницей, что поле "Значение" пакета данных помещается в адресное сечение соответствующего блока памяти функциональных параметров 3. Выполнение процедуры настройки после программирования устройства существенно при решении задач в нейросетевом базисе, т.к. процесс программирования задает связи между элементами нейронной сети, а функциональные параметры подбираются в процессе обучения уже сформированной сети и заносятся в блоки памяти функциональных параметров 3. Если же нейронная сеть обучена и значения функциональных параметров заранее известны, то порядок программирования и настройки защищенного устройства для обработки информации может быть произвольным.

Реализуемость устройства для обработки информации обусловлена использованием в составе заявляемого устройства общепринятых технических решений блоков, узлов и элементов (см., например. Каган Б.М. Электронные вычислительные машины и системы. - М.: Энергоатомиздат, 1991), а также следует из вышеприведенного описания работы устройства для обработки информации в различных режимах его функционирования.

На основе вышеизложенного заявляемая совокупность компонентов устройства для обработки информации позволяет решить поставленную задачу повышения производительности защищенного устройства для обработки информации за счет совмещения во времени процесса загрузки значений операндов и процесса преобразования данных, а также организации обработки информации по месту ее хранения в локальных пулах командных пакетов, что говорит о достижении поставленной цели.

Эффект защиты информации в заявляемом устройстве обусловлен описанной в предлагаемом изобретении взаимосвязью его компонентов, которая обеспечивает, во-первых, безадресное занесение пакетов данных в специализированные блоки памяти пулов командных пакетов, что затрудняет несанкционированную модификацию данных, во-вторых, выборка пакетов данных из пулов командных пакетов производится автоматически по мере формирования результата и не связана с инициацией процедуры считывания информации по заданному адресу извне, что исключает несанкционированный доступ к хранимым данным.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2373568C1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2379751C2 |

| НЕЙРОСЕТЕВОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО | 2008 |

|

RU2394274C2 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ В НЕЙРОННЫХ СЕТЯХ | 2004 |

|

RU2263964C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2000 |

|

RU2179739C2 |

| НЕЙРОСЕТЕВОЕ ДИСКРЕТНОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО | 2003 |

|

RU2250501C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2000 |

|

RU2176815C1 |

| Логическое запоминающее устройство | 1980 |

|

SU947910A2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| Запоминающее устройство с последовательным доступом | 1982 |

|

SU1070606A2 |

Изобретение относится к вычислительной технике и может быть использовано при построении нейросетевых средств обработки информации. Техническим результатом является повышение производительности устройства за счет организации обработки информации по месту ее хранения в многофункциональной памяти пулов командных пакетов и совмещения во времени процессов занесения и преобразования данных. Устройство содержит блок ввода данных, блок вывода данных, кольцевую шину, локальные пулы командных пакетов, каждый из которых состоит из блока памяти команд, блока памяти функциональных параметров, блока памяти готовности данных, блока памяти управления готовностью, схемы готовности, дешифратора, блока аккумуляторной памяти, умножителя, сумматора, блока функции активации и регистра пакетов данных, блоки стековой памяти данных, приоритетные цепи, схемы сравнения, входные фиксаторы, каждый из которых образован адресными регистрами по числу коммутационных полей пакета данных и регистром данных. 1 з.п. ф-лы, 2 ил.

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2000 |

|

RU2179739C2 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ В НЕЙРОННЫХ СЕТЯХ | 2004 |

|

RU2263964C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2000 |

|

RU2176815C1 |

| Система сбора и обработки информации | 1987 |

|

SU1424024A1 |

| JP 5197707, 06.08.1993 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

2008-08-20—Публикация

2006-09-27—Подача