Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки информации в нейросетевом логическом базисе.

Известно операционное устройство для параллельной обработки числовой информации, содержащее память командных ячеек для реализации управления потоками данных, матрицу ожидания готовых командных ячеек с командными ключами, скалярные процессоры, процессор памяти для управления обменом данными между основной памятью и памятью командных ячеек, векторный процессор для обработки векторных команд, блочный процессор для управления загрузкой команд из основной памяти в память командных ячеек, а также блоки ввода и вывода данных [1].

Недостатком устройства является архитектурная ориентация на представление команд, свойственное машинам фон Неймана: коды исходных операндов и результатов вычисления хранятся в памяти, что не исключает возможность несанкционированного доступа; поле операндов в формате командной ячейки содержит коды указателей на командные ячейки - источники входных данных, а поле данных командной ячейки - код результата выполнения операции и флаг готовности результата, что усложняет процедуру определения готовности командной ячейки к обработке и, как следствие, увеличивает время решения задачи.

Известно многопроцессорное устройство, содержащее координатный коммутатор, соединенный через кэш память скалярных команд и кэш память данных с конвейерными скалярными процессорами, через векторные регистры - с конвейерными векторными модулями, через порты памяти - с блоками оперативной памяти, а через шины ввода/вывода - с блоками ввода/вывода данных [2].

В качестве недостатка устройства следует отметить последовательный характер программного управления вычислениями, что наряду с ограниченным числом операционных блоков не позволяет в полной мере реализовать потенциальные возможности распараллеливания вычислительного процесса и, следовательно, уменьшить время решения задачи. В структуре данного устройства отсутствуют аппаратные средства, необходимые для решения неформализуемых задач, свойственных нейросетевому логическому базису.

Наиболее близким техническим решением к предлагаемому изобретению является устройство для обработки дискретной информации, содержащее локальные пулы командных пакетов, состоящие из блоков оперативной памяти и блоков памяти готовности данных с логическими схемами готовности данных, объединенных соответствующими параллельными шинами памяти, которые взаимосвязаны с первым координатным коммутатором, соединенным посредством векторных регистров и блока буферной памяти векторных команд с векторным операционным блоком, а также скалярные операционные блоки, блоки ввода и блоки вывода данных [3].

Недостатком последнего технического решения можно считать использование сложного в структурном отношении координатного коммутатора, выполняющего переключение встречных информационных потоков между двунаправленными параллельными шинами памяти и однонаправленными шинами операционных блоков, что исключает одновременное выполнение операций записи и считывания из одного и того же локального пула командных пакетов и, следовательно, снижает общую производительность устройства.

Задача настоящего изобретения - ускорение вычислительного процесса за счет разнесения в пространстве операций по коммутации встречных информационных потоков между локальными пулами командных пакетов и операционными блоками, а также буферизации представленной в виде пакетов информации во входных и выходных цепях локальных пулов командных пакетов.

Поставленная задача достигается тем, что нейросетевое дискретное операционное устройство содержит второй координатный коммутатор, входные и выходные стеки по числу локальных пулов командных пакетов, причем входные шины второго координатного коммутатора соединены с выходными шинами блоков ввода данных, скалярных и векторного операционных блоков, а выходные шины второго координатного коммутатора - с входными шинами блоков вывода данных и входных стеков, выходные шины которых через параллельные шины взаимосвязаны с входными шинами соответствующих выходных стеков, выходные шины которых, в свою очередь, соединены с входными шинами первого координатного коммутатора, взаимосвязанного с входными шинами скалярных операционных блоков.

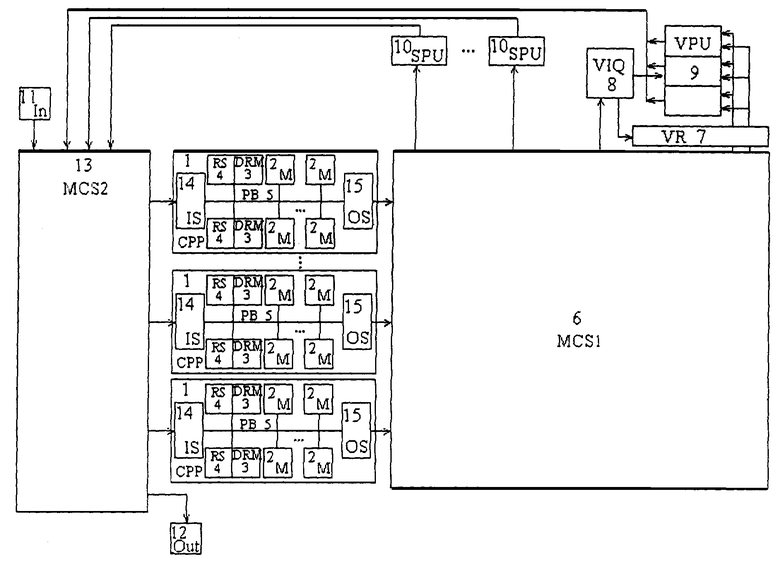

На чертеже представлена структурная схема предлагаемого нейросетевого дискретного операционного устройства.

Нейросетевое дискретное операционное устройство содержит локальные пулы командных пакетов (СРР) 1, состоящие из блоков оперативной памяти (М) 2 и блоков памяти готовности данных (DRM) 3 с логическими схемами готовности данных (RS) 4, объединенных соответствующими параллельными шинами памяти (РВ) 5, которые взаимосвязаны с первым координатным коммутатором (MCS1) 6, соединенным посредством векторных регистров (VR) 7 и блока буферной памяти векторных команд (VIQ) 8 с векторным операционным блоком (VPU) 9, скалярные операционные блоки (SPU) 10, блоки ввода (In) 11 и блоки вывода (Out) 12 данных, а также второй координатный коммутатор (MCS2) 13, входные (IS) 14 и выходные (OS) 15 стеки по числу локальных пулов командных пакетов.

Предлагаемое нейросетевое дискретное операционное устройство функционирует следующим образом.

При вводе пакеты данных, формируемые блоками ввода (In-Input) 11,

поступают во второй координатный коммутатор (MCS2 - Memory Crossbar Switch) 13, через который в соответствии с кодом поля "Address of local СРМ" каждого пакета данных на соответствующую выходную шину второго координатного коммутатора будут передаваться поля "СР address", "Operand address" и "Value" пакета данных и далее во входной стек (IS - Input Stack) 14 одноименного локального пула командных пакетов СРР. Поле "Value" с выходной шины входного стека IS заносится в ячейку блока оперативной памяти данных (М - Memory) 2, адресуемую полями "СР address" и "Operand address". В том же адресном сечении блока памяти готовности данных (DRM - Data Readiness Memory) 3 устанавливается в нуль бит готовности. Установка в нуль всех битов готовности в некотором адресном сечении блока памяти готовности данных DRM контролируется схемой готовности данных (RS - Readiness Scheme) 4, которая в этом случае инициирует запись единиц во все разряды названного адресного сечения блока памяти готовности данных DRM, формирование и выборку командного пакета из данного адресного сечения блоков оперативной памяти М на соответствующую параллельную шину памяти (РВ - Parallel Bus) 5 устройства и далее - в выходной стек (OS - Output Stack) 15 в следующем формате:

Процесс обработки скалярного командного пакета начинается с момента его передачи с параллельной шины памяти РВ в выходной стек OS соответствующего локального пула командных пакетов СРР. Наличие командного пакета в стеке OS инициирует его передачу через первый координатный коммутатор MCS1 к свободному скалярному операционному блоку (SPU - Scalar Processor Unit) 10. Причем в полях "Values of Data" и "Values of Functional Parameters" скалярного командного пакета содержатся соответственно значения вектора входных данных и значения вектора весовых коэффициентов. Аналогично организована обработка векторного командного пакета, с той лишь разницей, что передаваемый через первый координатный коммутатор MCS1 6 командный пакет заносится в векторные регистры (VR - Vector Registers) 7 (поля "Values of Data" и "Values of Functional Parameters") и блок буферной памяти векторных команд (VIQ - Vector Instructions Queue) 8 (поля "Operation and Addresses of CP"). Причем в полях "Values of Data" и "Values of Functional Parameters" векторного командного пакета содержатся соответственно значения вектора входных данных и значения матрицы весовых коэффициентов. В процессе обработки через параллельные шины памяти РВ, выходные стеки OS, первый координатный коммутатор MCS1, векторные регистры VR и блок буферной памяти векторных команд VIQ может быть организован конвейер для совмещения процедуры обработки командного пакета в векторном операционном блоке (VPU - Vector Processor Unit) 9 (умножение вектор входных данных на матрицу весовых коэффициентов) и процедуры обмена векторными командными пакетами и пакетами данных с блоками оперативной памяти М. По мере готовности происходит накопление векторных командных пакетов в векторных регистрах VR и блоке буферной памяти векторных команд VIQ.

При выводе результаты вычислений оформляются в виде пакетов данных, адресное поле каждого из которых соответствует одному из адресов блоков вывода данных (Out - Output) 12. Пакеты данных с выходов скалярных операционных блоков SPU и векторного операционного блока VPU поступают рассмотренным выше образом через второй координатный коммутатор MCS2 на его выходную шину, соединенную с соответствующими из блоков вывода Out, и фиксируются во входных цепях блоков вывода данных 12.

В режиме программирования нейросетевого дискретного операционного устройства формируется топология нейронной сети путем указания связей между отдельными ее компонентами. Для этого необходимо в каждую командную ячейку в соответствующее адресное сечение блока оперативной памяти М ввести коды адресов командных ячеек - приемников результата. Необходимая информация (поле "Value") пакета данных, формируемого в блоке ввода данных In, через соответствующую входную шину второго координатного коммутатора MCS2 заносится в адресное сечение (поля "СР address", "Operand address") заданного блока оперативной памяти М (поле "Address of local CPM"). Программирование устройства осуществляется перед его использованием в вышеперечисленных режимах функционирования.

Режим настройки функциональных параметров нейросетевого дискретного операционного устройства аналогичен рассмотренной последовательности программирования с той лишь разницей, что поле "Значение" пакета данных помещается в блок оперативной памяти М, соответствующий месту хранения функциональных параметров в данном адресном сечении. Настройка функциональных параметров производится после осуществления программирования заявляемого устройства, но перед его работой. Выполнение процедуры настройки после осуществления программирования устройства существенно при решении задач в нейросетевом логическом базисе, т.к. процесс программирования задает связи между элементами нейронной сети, а функциональные параметры подбираются в процессе обучения уже сформированной сети. Если же функциональные параметры заранее известны (сеть обучена), то порядок программирования и настройки дискретного операционного устройства может быть произвольным.

Введение в структуру нейросетевого дискретного операционного устройства второго координатного коммутатора MCS2, входных IS и выходных OS стеков по числу локальных пулов командных пакетов позволяет ускорить процесс распараллеливания вычислений за счет оперативной передачи готовых к обработке скалярных и векторных командных пакетов из локальных пулов командных пакетов СРР к скалярным SPU и векторному VPU операционным блокам посредством первого координатного коммутатора MCS1 и одновременно - пакетов данных с результатами обработки в обратном направлении от операционных блоков SPU и VPU через второй координатный коммутатор MCS2 в локальные пулы командных пакетов СРР. Наличие входных и выходных стеков в локальных пулах командных пакетов дает возможность согласовать асинхронный порядок поступления/извлечения пакетов из соответствующих пулов командных пактов с циклами операций записи/считывания из блоков оперативной памяти М и дополнительно ускорить процесс передачи информационных потоков.

Таким образом, наличие второго координатного коммутатора, входных и выходных стеков позволяет разнести в пределах устройства и осуществлять одновременную передачу встречных потоков информации, что существенно увеличивает производительность нейросетевого дискретного операционного устройства.

Источники информации

1. Компьютеры на СБИС: В 2-х кн. Кн.2: Пер. с япон. / Мотоока Т., Хорикоси X., Сакаути М. и др. - М.: Мир, 1988. - 336 с., с.78-81.

2. Паттерсон Д., Андерсон Т., Кадвел Н., Фромм Р., Китон К., Козяракис К., Томас Р, Елик К. Доводы в пользу IRAM. - Компьютеры, №15, 1998, Приложение, с.3-14.

3. Патент 2176815 РФ, МПК G 06 F 15/00. Устройство для обработки дискретной информации. / Г.Ф.Нестерук, Ф.Г.Нестерук. - №2000111364/09; Заявлено 06.05.2000; Опубл. 10.12.2001. Бюл. №34, Приоритет от 06.05.2000 - прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2000 |

|

RU2176815C1 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ В НЕЙРОННЫХ СЕТЯХ | 2004 |

|

RU2263964C1 |

| НЕЙРОСЕТЕВОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО | 2008 |

|

RU2394274C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2373568C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2006 |

|

RU2331923C2 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2379751C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2000 |

|

RU2179739C2 |

| Специализированная вычислительная система, предназначенная для вывода в глубоких нейронных сетях, основанная на потоковых процессорах | 2022 |

|

RU2793084C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ В НЕЙРОННЫХ СЕТЯХ | 2006 |

|

RU2406105C2 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки дискретной информации. Техническим результатом является ускорение вычислительного процесса за счет разнесения операций по коммутации встречных информационных потоков между пулами командных пакетов и операционными блоками, а также буферизации представленной в виде пакетов информации во входных и выходных цепях пулов командных пакетов. Этот результат достигается за счет того, что устройство содержит локальные пулы командных пакетов, состоящие из блоков оперативной памяти и памяти готовности данных с логическими схемами готовности данных, параллельные шины памяти, первый координатный коммутатор, векторные регистры, блок буферной памяти векторных команд, векторный операционный блок, скалярные операционные блоки, блоки ввода, блоки вывода данных, второй координатный коммутатор, входные и выходные стеки по числу локальных пулов командных пакетов. 1 ил.

Нейросетевое дискретное операционное устройство, содержащее локальные пулы командных пакетов, состоящие из блоков оперативной памяти и блоков памяти готовности данных с логическими схемами готовности данных, объединенных соответствующими параллельными шинами памяти, которые взаимосвязаны с первым координатным коммутатором, соединенным посредством векторных регистров и блока буферной памяти векторных команд с векторным операционным блоком, а также скалярные операционные блоки, блоки ввода и блоки вывода данных, отличающееся тем, что оно содержит второй координатный коммутатор, входные и выходные стеки по числу локальных пулов командных пакетов, причем входные шины второго координатного коммутатора соединены с выходными шинами блоков ввода данных, скалярных и векторного операционных блоков, а выходные шины второго координатного коммутатора - с входными шинами блоков вывода данных и входных стеков, выходные шины которых через параллельные шины взаимосвязаны с входными шинами соответствующих выходных стеков, выходные шины которых, в свою очередь, соединены с входными шинами первого координатного коммутатора, взаимосвязанного с входными шинами скалярных операционных блоков.

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2000 |

|

RU2176815C1 |

| СИСТЕМА ДЛЯ МОДЕЛИРОВАНИЯ ТВОРЧЕСКОЙ ИНТЕЛЛЕКТУАЛЬНОЙ ДЕЯТЕЛЬНОСТИ ЧЕЛОВЕКА | 2000 |

|

RU2190880C2 |

| US 5150450 А, 22.09.1992 | |||

| US 4951239 А, 21.08.1990. | |||

Авторы

Даты

2005-04-20—Публикация

2003-06-16—Подача