Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки дискретной информации.

Известно устройство для обработки информации, содержащее взаимосвязанные операционный блок и блок памяти, а также блоки ввода и вывода информации, ориентированное на первичную обработку по месту хранения данных [1].

В качестве достоинства устройства можно назвать распределенный характер обработки информации в многофункциональном накопителе, а недостатка - ограниченные функциональные возможности устройства.

Известно также устройство для обработки информации, содержащее в пределах кристалла взаимосвязанные операционные блоки и блоки памяти, а также блоки ввода и вывода данных, ориентированное на параллельное выполнение операций [2].

Недостатком устройства является архитектурная ориентация на последовательную концепцию фон Неймана, что затрудняет распараллеливание вычислительного процесса.

Наиболее близким техническим решением к предлагаемому изобретению является устройство для обработки информации, содержащее операционные блоки, входы которых взаимосвязаны с выходами блоков локальной памяти команд и блоков локальной памяти данных, а выходы - с первой шиной, блоки стековой памяти результатов, входы которых соединены со второй шиной, а выходы - со входами соответствующих блоков локальной памяти данных, блоки ввода и вывода данных, подключенные к первой шине [3].

В качестве недостатка последнего решения следует отметить программный подход к распараллеливанию вычислений: на этапе компиляции определяется возможность одновременного выполнения отдельных программных фрагментов и производится их жесткое закрепление за конкретными операционными блоками, что не позволяет в полной мере реализовать потенциальные возможности распараллеливания процесса решения задачи. Кроме того, в архитектуре последнего технического решения отсутствуют аппаратные средства, направленные на решение задач, свойственных нейросетевому логическому базису.

Задача настоящего изобретения - упрощение процесса распараллеливания вычислений за счет внутренней архитектурной реализации параллелизма решаемой задачи и расширение функциональных возможностей устройства для обработки информации путем решения всего спектра нейросетевых задач.

Поставленная задача достигается тем, что устройство для обработки информации содержит по числу блоков локальной памяти данных блоки локальной памяти функциональных параметров и блоки локальной памяти готовности данных, триггеры занятости по числу операционных блоков, третью шину в виде кольца, посредством которой взаимосвязаны входы операционных блоков, выходы триггеров занятости, выходы блоков локальной памяти данных, блоков локальной памяти команд, блоков локальной памяти функциональных параметров и блоков локальной памяти готовности данных, причем входы блоков локальной памяти функциональных параметров и блоков локальной памяти команд соединены с первой шиной, которая совместно со второй шиной образует кольцевую шину, а входы блоков локальной памяти готовности данных соединены с выходами одноименных блоков стековой памяти результатов.

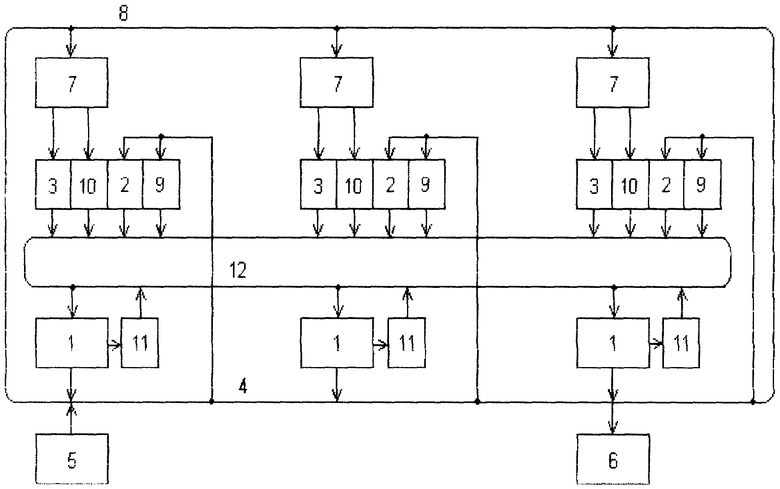

На чертеже представлена структурная схема предлагаемого устройства для обработки информации.

Устройство для обработки информации содержит операционные блоки 1, входы которых взаимосвязаны с выходами блоков локальной памяти команд 2 и локальной памяти данных 3, а выходы - с первой шиной 4, к которой присоединены блоки ввода 5 и блоки вывода 6 данных, блоки стековой памяти результатов 7, входы которых взаимосвязаны со второй шиной 8, блоки локальной памяти функциональных параметров 9, блоки локальной памяти готовности данных 10, триггеры занятости 11 и третью шину 12.

Предлагаемое устройство для обработки информации функционирует следующим образом.

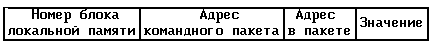

Рассмотрим процесс работы устройства в режиме ввода исходных данных. Блоки ввода 5 формируют пакеты данных в формате

Вводимые пакеты данных с первой шины 4 поступают в блоки стековой памяти результатов 7, откуда поле "значение данных" заносится в соответствующую ячейку блока локальной памяти данных 3. Одновременно в том же адресном сечении блока локальной памяти готовности данных 10 устанавливается бит готовности. Установка всех битов готовности в некотором адресном сечении блока локальной памяти готовности данных инициирует выборку командного пакета из данного адресного сечения блоков команд 2, данных 3, функциональных параметров 9 и передачу выбранного командного пакета на третью шину 12 устройства. При этом адресное сечение блока локальной памяти готовности данных обнуляется.

Процесс обработки командного пакета. Командный пакет по кольцевой шине 12 достигает операционного блока 1, триггер занятости 11 которого сброшен. Фиксация командного пакета во входных цепях операционного блока удаляет его с шины 12 и устанавливает соответствующий триггер занятости 11, что приводит к перенаправлению других командных пакетов, находящихся на шине 12, к оставшимся операционным блокам 1, триггеры занятости которых сброшены. В случае занятости всех операционных блоков командные пакеты циркулируют по шине 12 до сброса одного из триггеров занятости. Зафиксированный во входных цепях операционного блока командный пакет содержит полный набор значений данных, подлежащих обработке, указание на реализуемую функцию и коды адресов командных пакетов - приемников результата. Операционный блок 1 после завершения обработки формирует столько пакетов данных, сколько адресов командных пакетов - приемников результата он содержит, и сбрасывает соответствующий триггер занятости 11. Сформированные пакеты данных поступают в кольцевую шину, образованную первой 4 и второй 8 шинами, и заносятся в соответствующие адресам блоки стековой памяти результата 7. Далее - аналогично процессу ввода исходных данных.

Режим вывода результатов вычислений. Результаты вычислений формируются операционными блоками в виде пакетов данных, адресное поле каждого из которых соответствует одному из адресов блоков вывода данных 6. Пакеты данных поступают с выходов операционных блоков 1 на первую шину 4 и фиксируются во входных цепях блоков вывода данных 6.

Режим программирования устройства для обработки информации. Программирование заявляемого устройства осуществляется перед его использованием в вышеперечисленных режимах функционирования. При программировании необходимо для каждого командного пакета в соответствующее адресное сечение блока локальной памяти команд 2 ввести коды адресов командных пакетов - приемников результата. В этом случае значение адреса командного пакета - приемника результата (поле "значение") пакета данных, формируемого в блоке ввода 5, через первую шину 4 заносится в адресное сечение (поле "адрес командного пакета" и поле "адрес в пакете") заданного блока локальной памяти команд 2 (поле "номер блока локальной памяти").

Режим настройки функциональных параметров устройства для обработки информации. Настройка функциональных параметров производится после осуществления программирования заявляемого устройства, но перед его работой в режимах ввода данных, обработки и вывода результатов. Процесс занесения значений функциональных параметров аналогичен вышерассмотренной последовательности программирования с той лишь разницей, что поле "значение" пакета данных помещается в адресное сечение соответствующего блока локальной памяти функциональных параметров 9. Выполнение процедуры настройки после осуществления программирования устройства существенно при решении задач в нейросетевом логическом базисе, т. к. процесс программирования задает связи между элементами нейронной сети, а функциональные параметры подбираются в процессе "обучения" уже сформированной сети и заносятся в локальную память функциональных параметров 9. Если же функциональные параметры заранее известны (сеть "обучена"), то порядок программирования и настройки устройства для обработки информации может быть произвольным.

Введение в структуру устройства блоков локальной памяти функциональных параметров, блоков локальной памяти готовности данных, триггеров занятости, третьей шины в виде кольца и соединение первой и второй шин в кольцевую шину позволяет значительно упростить процесс распараллеливания вычислений за счет архитектурной самореализации параллелизма решаемой задачи. Помещение командных пакетов на кольцевую шину 12 и наличие триггеров занятости дает возможность автоматически распределять командные пакеты по свободным операционным блокам без явного указания операционного блока - получателя пакета. С другой стороны, соединение первой 4 и второй 8 шин в кольцевую шину и наличие блоков стековой памяти результатов позволяют буферизировать значительное количество пакетов данных при адресной рассылке результатов обработки в конкретные блоки локальной памяти данных. Наличие блоков локальной памяти готовности данных дает возможность запустить механизм самоуправления вычислениями и, следовательно, реализовать в максимальной степени параллелизм, свойственный данной задаче. Блоки локальной памяти функциональных параметров существенно расширяют область применения заявляемого устройства за счет реализации функции настройки (обучения), что позволяет решать специфические задачи, свойственные нейросетевому логическому базису: классификации образов, аппроксимации, предсказания, оптимизации, организации ассоциативной памяти, управления динамическими системами.

Источники информации

1. Авторское свидетельство СССР 809190.

2. D. Patterson, T. Anderson, N. Cardwell, et al. Intelligent RAM (IRAM): Chips that remember and compute. Digest of Technical Papers, 1997 IEЕЕ International Solid-State Circuits Conference, San Francisco, CA, USA, Feb. 1997.

3. Kishi M. et al. DDDP - A Distributed Data Driven Processor. 10th Annual Int. Symp. on Computer Architecture, 1983, p.p. 236-242.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2000 |

|

RU2176815C1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2379751C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2008 |

|

RU2373568C1 |

| НЕЙРОСЕТЕВОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО | 2008 |

|

RU2394274C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2006 |

|

RU2331923C2 |

| НЕЙРОСЕТЕВОЕ ДИСКРЕТНОЕ ОПЕРАЦИОННОЕ УСТРОЙСТВО | 2003 |

|

RU2250501C2 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ В НЕЙРОННЫХ СЕТЯХ | 2004 |

|

RU2263964C1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| АСИНХРОННАЯ СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2198422C2 |

| Вычислительная система | 1977 |

|

SU692400A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки дискретной информации. Технический результат заключается в упрощении процесса распараллеливания вычислений за счет внутренней архитектурной реализации параллелизма решаемой задачи и в расширении функциональных возможностей устройства для обработки информации путем решения всего спектра нейросетевых задач. Устройство содержит операционные блоки, блоки локальной памяти команд, блоки локальной памяти данных, первую шину, блоки стековой памяти результатов, вторую шину, блоки ввода и блоки вывода данных, блоки локальной памяти функциональных параметров, блоки локальной памяти готовности данных, триггеры занятости, третью шину в виде кольца. 1 ил.

Устройство для обработки информации, содержащее операционные блоки, входы которых взаимосвязаны с выходами блоков локальной памяти команд и блоков локальной памяти данных, а выходы - с первой шиной, блоки стековой памяти результатов, входы которых соединены со второй шиной, а выходы - со входами соответствующих блоков локальной памяти данных, блоки ввода и блоки вывода данных, подключенные к первой шине, отличающееся тем, что оно содержит по числу блоков локальной памяти данных блоки локальной памяти функциональных параметров и блоки локальной памяти готовности данных, триггеры занятости, каждый из которых соединен по входам с соответствующим операционным блоком, третью шину в виде кольца, посредством которой взаимосвязаны входы операционных блоков, выходы триггеров занятости, выходы блоков локальной памяти данных, блоков локальной памяти команд, блоков локальной памяти функциональных параметров и блоков локальной памяти готовности данных, причем входы блоков локальной памяти функциональных параметров и блоков локальной памяти команд соединены с первой шиной, которая совместно со второй шиной образуют кольцевую шину, а входы блоков локальной памяти готовности данных соединены с выходами одноименных блоков стековой памяти результатов.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кн | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| с япон./МОТООКА Т., ТОМИТА С | |||

| и др | |||

| - М.: Мир, 1988 | |||

| Устройство для обработки данных | 1984 |

|

SU1352498A1 |

| JP 08185381 А, 16.07.1996 | |||

| JP 58149541 А, 05.09.1983 | |||

| Система обработки данных | 1979 |

|

SU849219A1 |

Авторы

Даты

2002-02-20—Публикация

2000-04-10—Подача