Изобретение относится к импульсной цифровой технике и может быть использовано в вычислительной технике, автоматике, измерительных устройствах, радиолокации, устройствах связи и т.д. для осуществления линейно-дискретной задержки выходных импульсов относительно входных в пределах его длительности в соответствии с поступающим двоичным кодом.

Известны устройства задержки выходных импульсных сигналов относительно входных, использующие различные виды RС-цепочек, компараторов, мультивибраторов, логических элементов [1, 2]. Недостатком таких устройств является низкая точность величины временной задержки, присущая элементам аналоговой схемотехники, ограниченная длительность предельных значений, задаваемой задержки импульсов.

Также известны цифровые устройства, формирующие временные интервалы заданной величины, таймеры [3, 4], содержащие хронизатор (генератор импульсов), выход которого соединен со счетным входом счетчика импульсов, выходы которого соответственно соединены с входами цифрового компаратора, где другие входы упомянутого компаратора соответственно соединены с выходами регистра, задающего временную задержку. Однократный разовый характер формирования временных задержек таймерами не позволяет использовать их для разработки устройств линий задержки с непрерывной последовательностью поступающих сигналов.

Известна линия задержки [5], принятая как прототип решения поставленной задачи и имеющая вход и выходы, выполненная на основе последовательно соединенных ячеек сдвигового регистра, где величина задержки последовательности выходных сигналов относительно входных прямо пропорциональна количеству задействованных ячеек сдвигового регистра. Недостатком предлагаемого технического решения устройств линий задержки является большое количество используемых ячеек сдвигового регистра для получения значительных величин временной задержки входных последовательностей импульсных сигналов. Кроме того, прототип имеет ограниченную возможность формирования минимальной длительности дискрета линии задержки. Действительно, минимальный дискрет задержки определяется частотой поступающих извне сдвигающих синхронизирующих импульсов, которые поступают на интегральную схему (ИС) через внешние выводы с большой удельной емкостью относительно емкости элементов внутри ИС. Поэтому формирование наносекундных, например, интервалов временной задержки в данном устройстве является проблематичным.

Применяемое в таймерах [3, 4] техническое решение с использованием двоичных счетчиков импульсов для формирования временных интервалов отличается значительной экономичностью затрат оборудования на единицу сдвигового дискрета относительно сдвиговых регистров устройства [5]. Количественно это соотношение в пользу двоичных счетчиков импульсов выразится как N/p, где N - количество ячеек сдвигового регистра, обеспечивающего дискретность задержки импульсов; р - количество разрядов двоичного счетчика импульсов на N=2Р дискретов задержки импульсов. В качестве элементов схемы технического решения предлагаемого изобретения наиболее близкой для прототипа принята схема таймера [4].

Целью предлагаемого изобретения является уменьшение затрат оборудования на реализацию устройств линий задержки с формированием значительных величин временной задержки последовательности импульсных сигналов, выполненных в интегральном их исполнении, и получение при этом минимального дискрета задержки наносекундной величины.

Технический результат достигается тем, что в предлагаемой дискретной линии задержки импульсных сигналов, имеющей вывод для подачи входных импульсных сигналов, вывод для выдачи на внешнюю нагрузку задержанных выходных импульсных сигналов, выводы для установки кодов необходимой временной задержки выходных сигналов и содержащей генератор импульсов, выход которого соединен со счетным входом n-разрядного счетчика импульсов, n выходов которого соответственно соединены с n входами цифрового компаратора, где другие n входов упомянутого компаратора соответственно соединены с n выходами n-разрядного регистра, задающего величину кода необходимой временной задержки входных импульсных сигналов и логический элемента НЕ, генератор импульсов дополнительно снабжен входом, блокирующим/разрешающим генерацию выходных импульсов, а также дополнительно введены входной двухвходовой мультиплексор сигналов, работающий на один выход с управляющим входом, и выходной одноразрядный счетчик импульсов, при этом вывод для подачи входных импульсных сигналов соединен с первым входом входного двухвходового мультиплексора сигналов, второй вход которого также соединен с выводом для подачи входных импульсных сигналов через логический элемент НЕ, управляющий вход упомянутого мультиплексора соединен с соответствующим выходом выходного одноразрядного счетчика импульсов, счетный вход которого соединен с выходом результата сравнения цифрового компаратора, а один из соответствующих выходов выходного одноразрядного счетчика импульсов соединен с выводом для выдачи на внешнюю нагрузку задержанных выходных импульсных сигналов, причем выход упомянутого мультиплексора соединен с входом, блокирующим/разрешающим генерацию выходных импульсов упомянутого генератора.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается использованием двоичного счетчика в качестве формирователя интервалов временной задержки фронта и спада импульсов входной поступающей последовательности, что позволяет в совокупности с задержками фронтов и спадов входных импульсов создать компактную схему квазинепрерывной линии задержки выходных импульсов с наносекундным шагом интервала задержки. Счетчики импульсов в преобладающем своем применении используются в таймерах, а применение одного и того же счетчика импульсов для задержки фронта и спада входного сигнала для получения общей задержки последовательности импульсов автору неизвестно.

Проведенный анализ изобретательского уровня, включающий поиск по патентным и научно-техническим источникам информации и выявление источников, содержащих сведения об аналогах заявляемого устройства, позволяет установить, что заявителем не обнаружены решения, характеризующиеся признаками, идентичными всем существенным признакам заявленного изобретения. Определение из перечня выявленных аналогов прототипа позволило выявить совокупность существенных отличительных признаков в заявляемом объекте, изложенную в формуле изобретения. Следовательно, заявляемое изобретение соответствует требованию "новизна" по действующему законодательству. Сведений об известности отличительных признаков известных технических решений с достижением такого же, как у заявляемого устройства, положительного эффекта не имеется. На основании этого сделан вывод, что предлагаемое техническое решение соответствует критерию "изобретательский уровень".

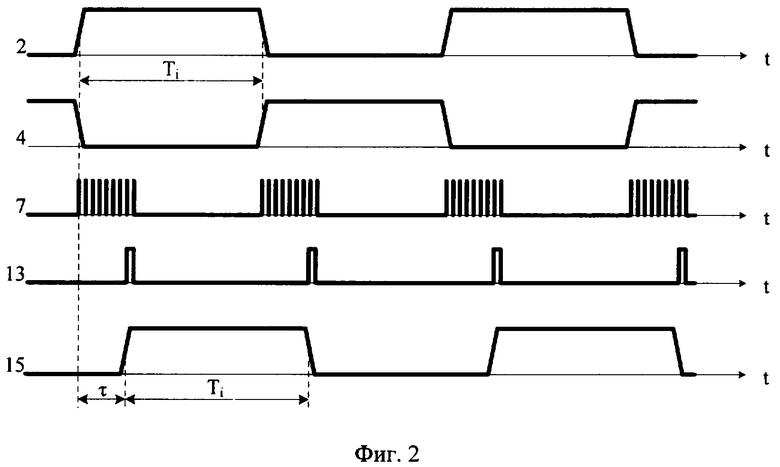

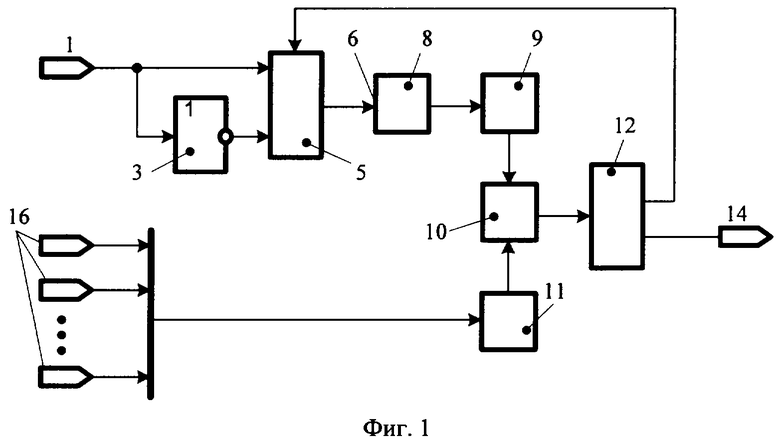

На фиг.1 представлена блок-схема предлагаемой дискретной линии задержки импульсных сигналов. На фиг.2 представлены временные диаграммы, поясняющие работу предлагаемого устройства.

Предлагаемая дискретная линия задержки импульсных сигналов содержит вывод 1 для подачи входных импульсных сигналов 2, элемент НЕ 3 для получения инвертированных входных сигналов 4, выход которого соединен с одним из входов входного двухвходового мультиплексора 5 сигналов, другой вход которого соединен с выводом 1, при этом выход мультиплексора 5 соединен с входом 6, блокирующим/разрешающим генерацию выходных импульсов 7 генератора 8 импульсов. Выход генератора 8 соединен со счетным входом n-разрядного счетчика 9 импульсов, n выходов которого соответственно соединены с n входами цифрового компаратора 10, где другие n входов компаратора 10 соответственно соединены с n выходами n-разрядного регистра 11, задающего величину кода необходимой временной задержки входных импульсных сигналов 2, при этом выход результата сравнения компаратора 10 соединен со счетным входом выходного одноразрядного счетчика 12 импульсов 13, где один из соответствующих выходов счетчика 12 соединен с управляющим входом мультиплексора 5, другой соответствующий выход счетчика 12 соединен с выводом 14 для выдачи на внешнюю нагрузку задержанных выходных импульсных сигналов 15. Входы для установки кодов необходимой временной задержки выходных сигналов 15 n-разрядного регистра 11 соединены с выводами 16 устройства. Входные импульсные сигналы 2, имеют длительности Ti где i-1, 2,…n. Выходные импульсные сигналы 15 имеют такие же длительности импульсов Ti, но с величиной задержки τ.

Предлагаемая дискретная линия задержки импульсных сигналов работает следующим образом. Вначале устройство должно находиться в исходном состоянии, когда n-разрядный счетчик 9 и выходной одноразрядный счетчик 12 были обнулены. При этом уровень выходного сигнала счетчика 12, поступающего на вход управления мультиплексором 5, разрешает прохождение сигнала непосредственно от вывода 1, при отсутствии выходного сигнала мультиплексора 5 блокируется генерация импульсов 7 по входу 6 генератора 8. По выводам 16 устройства регистр 11, задающий величину временной задержки сигналов τ, должен быть загружен соответствующим двоичным кодом. На вывод 1 устройства подаются входные импульсные сигналы 2 длительностью Ti. По наступлении фронта входного сигнала (диаграмма 2) мультиплексор 5 своим выходом разрешает генерацию импульсов 7 генератора 8, которые поступают на счетный вход счетчика 9 для подсчета импульсов. Поступающие соответствующие n-разрядные коды выходов счетчика 9 и регистра 11 сравниваются на компараторе 10, выполненном, например, на элементах «исключающее ИЛИ». При достижении равенства кодов на счетчике 9 и регистре 11 на выходе компаратора 10 формируется выходной импульс по диаграмме 13, поступающий на счетный вход выходного счетчика 12, и переключает состояние счетчика 12 (диаграмма 15). Это обстоятельство переключает вход мультиплексора 5 на инверсный выход входного сигнала 4 (на элемент НЕ 3) и тем самым прекращает через вход 6 генерацию импульсов 7 генератора 8. Таким образом, формируется задержка τ фронта входного импульса 2. Данное состояние сохраняется до наступления спада входного сигнала по диаграмме 2. Затем мультиплексор 5 разрешает генерацию импульсов 7 генератора 8, далее описанный выше процесс повторяется и формируется в соответствии с кодом регистра 11 задержка спада τ выходного сигнала по диаграмме 15. По фронтам и спадам входного импульса 2 всегда происходит сброс (обнуление) счетчика 9. Установка кода необходимой задержки τ регистра 11 осуществляется через выводы 16, при этом количество выводов 16 зависит от способа ввода информации, минимальное количество будет при последовательном вводе, например, по интерфейсу SPI.

Предложенное устройство позволяет дискретно в соответствии с длительностью импульсов генератора 8 формировать линейно задержку входных импульсных сигналов 2 любой длительности, одиночных, периодических, непериодических, с различной длительностью Ti, при этом максимальная длительность задержки импульсов τ определяется только разрядностью счетчика 9. Устройство цифровым способом формирует задержку фронта и спада импульсов, используя одну счетную 9 линейку, что повышает точность отработки величины заданной задержки τ. Величина задержки импульсных сигналов τ не превышает длительность входных сигналов Тi(τ≤Ti).

Реализация предложенного устройства в интегральном исполнении позволяет экономить площадь, занимаемую в кристалле ИС, также позволяет работать с внутренним генератором импульсов большой частоты (сотни мегагерц), что дает возможность иметь минимальный дискрет задержки наносекундной величины, таким образом получить практически квазинепрерывную линию задержки.

Источники информации

1. SU 2103808 С1, 27.01.1998.

2. RU 2257003 С1, 20.07.2005.

3. RU 2199177 С1, 20.02.2003.

4. RU 2215367 С2, 10.07.2003.

5. RU 2302075 С2, 27.08.2004.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМАЯ ЛИНИЯ ЗАДЕРЖКИ | 2011 |

|

RU2450432C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ СКОРОСТИ ПОСТУПАЮЩИХ ДАННЫХ АСИНХРОННОГО ИНФОРМАЦИОННОГО ПОТОКА | 2011 |

|

RU2446592C1 |

| Дельта-модулятор | 1987 |

|

SU1448411A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С КОРРЕКЦИЕЙ СЛУЧАЙНОЙ ПОГРЕШНОСТИ | 1991 |

|

RU2024193C1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| САМОНАСТРАИВАЮЩЕЕСЯ ЦИФРОВОЕ СГЛАЖИВАЮЩЕЕ УСТРОЙСТВО | 2017 |

|

RU2665906C1 |

| ОДНОКАНАЛЬНЫЙ КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ЧАСТОТНЫХ ИСКАЖЕНИЙ | 2009 |

|

RU2393491C2 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

Изобретение относится к импульсной цифровой технике и может быть использовано в вычислительных устройствах, автоматике, измерительных устройствах, радиолокации, устройствах связи и т.д. для осуществления линейно-дискретной задержки выходных импульсов относительно входных в пределах его длительности в соответствии с поступающим двоичным кодом. Технический результат: в уменьшении площади, занимаемой схемой в интегральном ее исполнении; в реализации минимально возможного значения дискрета линии задержки наносекундной величины. Устройство содержит логический элемент НЕ (3), мультиплексор (MX) (5), выход которого соединен с входом (6), блокирующим/разрешающим генерацию выходных импульсов генератора (8) импульсов. Выход генератора (8) импульсов соединен со счетным входом n-разрядного счетчика (9) импульсов, n выходов которого соединены с n входами цифрового компаратора (К) (10), другие n входов которого соединены с n выходами n-разрядного регистра (11), задающего величину кода необходимой временной задержки входных импульсных сигналов. При этом выход результата сравнения К (10) соединен со счетным входом выходного одноразрядного счетчика (12) импульсов, один из выходов которого соединен с управляющим входом MX (5). Отличается использованием двоичного счетчика в качестве формирователя интервалов временной задержки фронта и спада импульсов входной поступающей последовательности, что позволяет в совокупности с задержками фронтов и спадов входных импульсов получить компактную схему в интегральном исполнении квазинепрерывной линии задержки выходных импульсов. 2 ил.

Дискретная линия задержки импульсных сигналов, имеющая вывод для подачи входных импульсных сигналов, вывод для выдачи на внешнюю нагрузку задержанных выходных импульсных сигналов, выводы для установки кодов необходимой временной задержки выходных сигналов и содержащая генератор импульсов, выход которого соединен со счетным входом n-разрядного счетчика импульсов, n выходов которого соответственно соединены с n входами цифрового компаратора, где другие n входов упомянутого компаратора соответственно соединены с n выходами n-разрядного регистра, задающего величину кода необходимой временной задержки входных импульсных сигналов и логический элемент НЕ, отличающаяся тем, что генератор импульсов дополнительно снабжен входом, блокирующим/разрешающим генерацию выходных импульсов, а также дополнительно введены входной двухвходовой мультиплексор сигналов, работающий на один выход с управляющим входом, и выходной одноразрядный счетчик импульсов, при этом вывод для подачи входных импульсных сигналов соединен с первым входом входного двухвходового мультиплексора сигналов, второй вход которого также соединен с выводом для подачи входных импульсных сигналов через логический элемент НЕ, управляющий вход упомянутого мультиплексора соединен с соответствующим выходом выходного одноразрядного счетчика импульсов, счетный вход которого соединен с выходом результата сравнения цифрового компаратора, а один из соответствующих выходов выходного одноразрядного счетчика импульсов соединен с выводом для выдачи на внешнюю нагрузку задержанных выходных импульсных сигналов, причем выход упомянутого мультиплексора соединен с входом, блокирующим/разрешающим генерацию выходных импульсов, упомянутого генератора.

| ЛИНИЯ ЗАДЕРЖКИ | 2003 |

|

RU2302075C2 |

| УСТРОЙСТВО УПРАВЛЯЕМОЙ ДИСКРЕТНОЙ ЗАДЕРЖКИ | 1991 |

|

RU2024185C1 |

| Дискретно-аналоговое устройство задержки | 1979 |

|

SU879758A1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| US 4330750 A, 18.05.1982. | |||

Авторы

Даты

2009-12-27—Публикация

2008-05-12—Подача