.Id.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1988 |

|

SU1510090A2 |

| Дельта-модулятор | 1990 |

|

SU1709531A2 |

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

| Дельта-модулятор | 1990 |

|

SU1718383A1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Дельта-модулятор | 1989 |

|

SU1649666A1 |

| Дельта-модулятор | 1986 |

|

SU1345349A2 |

| Устройство для передачи и приема информации | 1987 |

|

SU1431074A1 |

| Анализатор активности непрерывных сигналов | 1987 |

|

SU1438004A2 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1589383A1 |

Изобретение относится к электросвязи и может использоваться в цифровых корреляторах. Изобретение позволяет расширить область применения дельта-модулятора за.счет обработки ДБ /хполярных входных сигналов и формирования смешанного формата выходного сигнала. Дельта-модулятор содержит компараторы 1 и 4, управляемый инвер-- тор 2, генератор 3 тактовых импуль-: сов, реверсивный счетчик 5, шифратор 6, цифроаналоговьтй преобразователь 7, формирователь 8 импульсов,триггеры 9, 14 и 15, эгхемент ЗАПРЕТ 10, элемент И 11, элемент 12 задержки, элемент ШШ 13 и элемент ИСКЛОЧАЮЩЕЕ ИЛИ 16. 3 ил. «

Ф1/г.

Изобретение отйосится к электросвязи и может, использоваться в цифровых корреляторах.

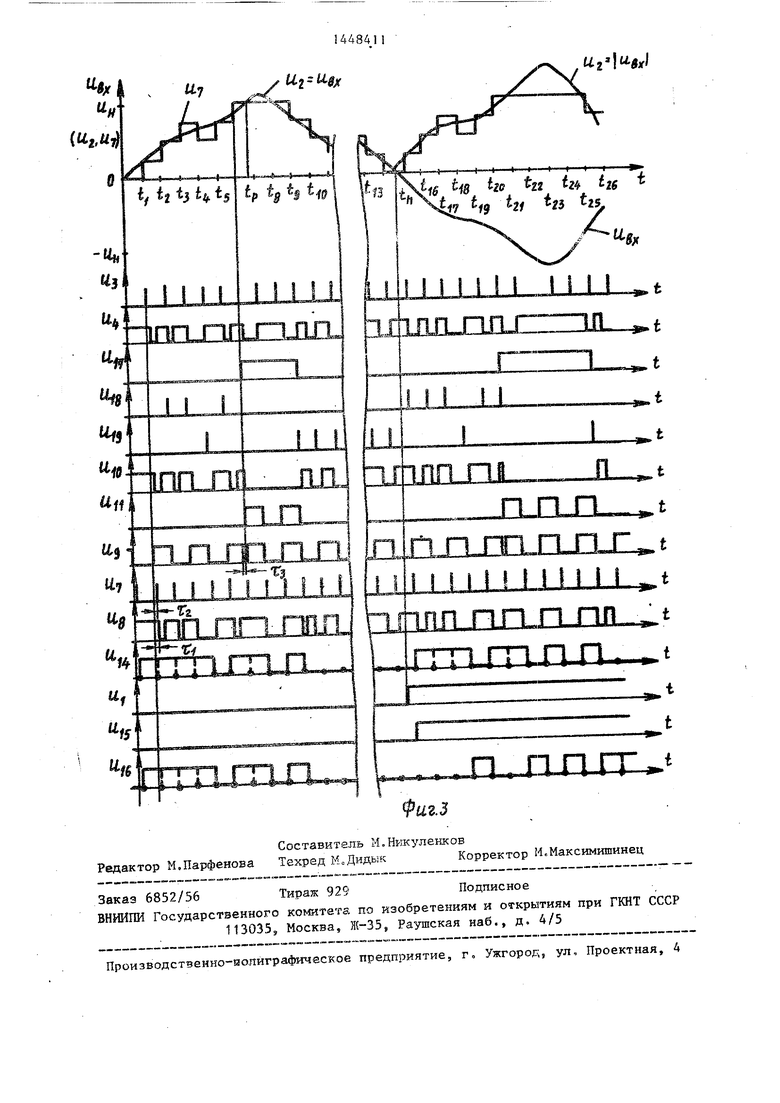

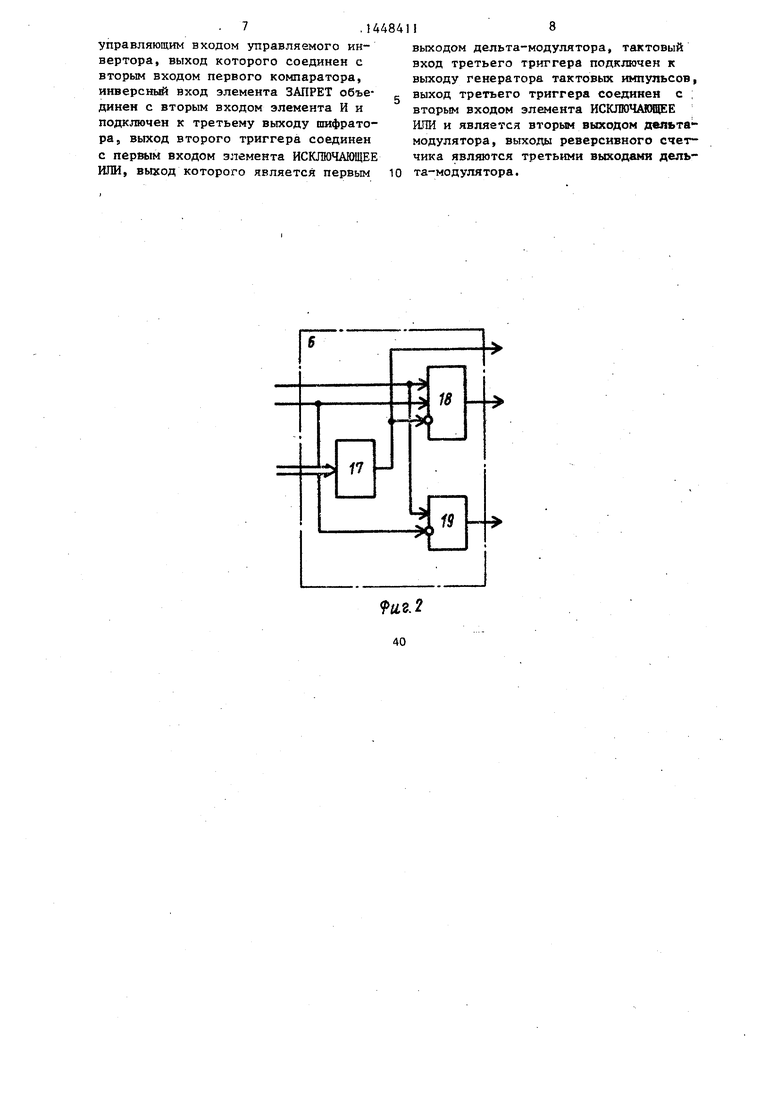

Целью изобретения является расши- рение области применения дельта-модулятора за счет обработки двухполярных входных сигналов и .формирования смешанного формата выходного сигнала. На фиг.1 представлена структурная схема предлагаемого дельта модулятора; на фиг. 2 - функциональная схема шифратора; на фиг. 3 - временные диаграммы работы дельта-модулятора.

Дельта модулятор (фиг.1)содержит второй компаратор 1 знака, управляемый инвертор 2, генератор 3 тактовых импульсов, первый компаратор 4, реверсивный счетчик 5, шифратор 6, циф- роаналоговый преобразователь- 7, фор- мирователь 8 импульсов, первый счетный триггер 9, элемент ЗАПРЕТ 10, элемент И 11, элемент 12 задержки, элемент ИЛИ 13, второй, третий D- триггеры 14, 15 и элемент 16 Исклзрча- ющее ИЛИ.

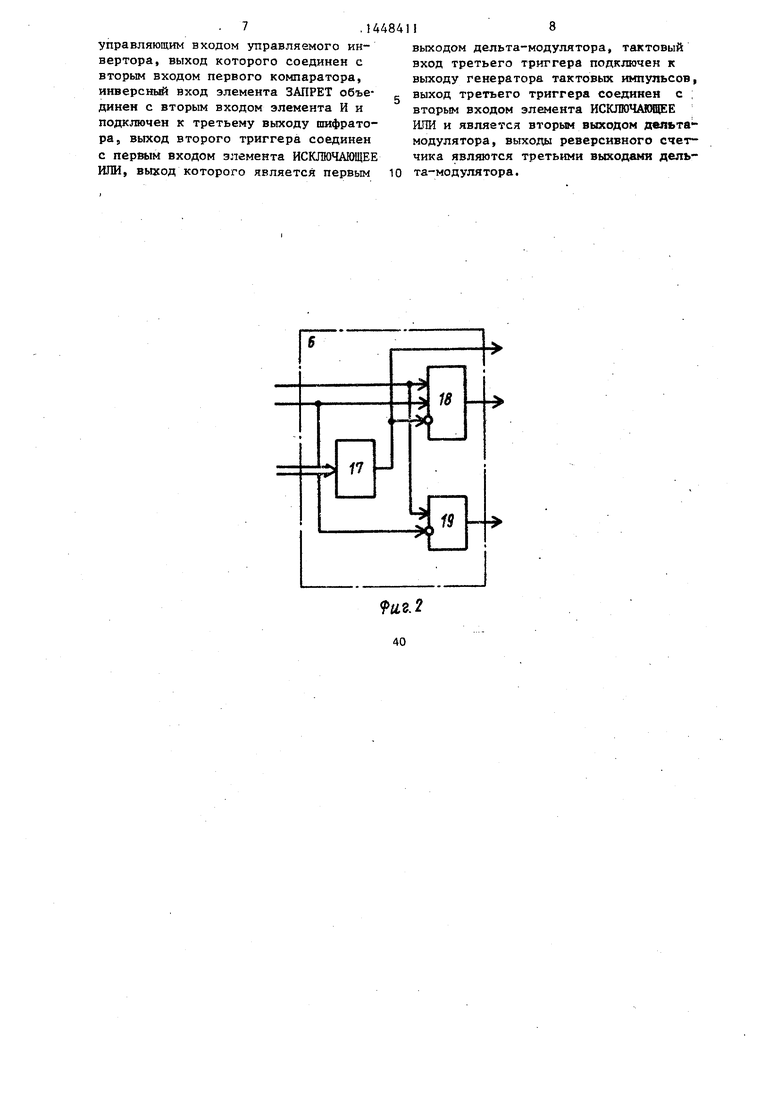

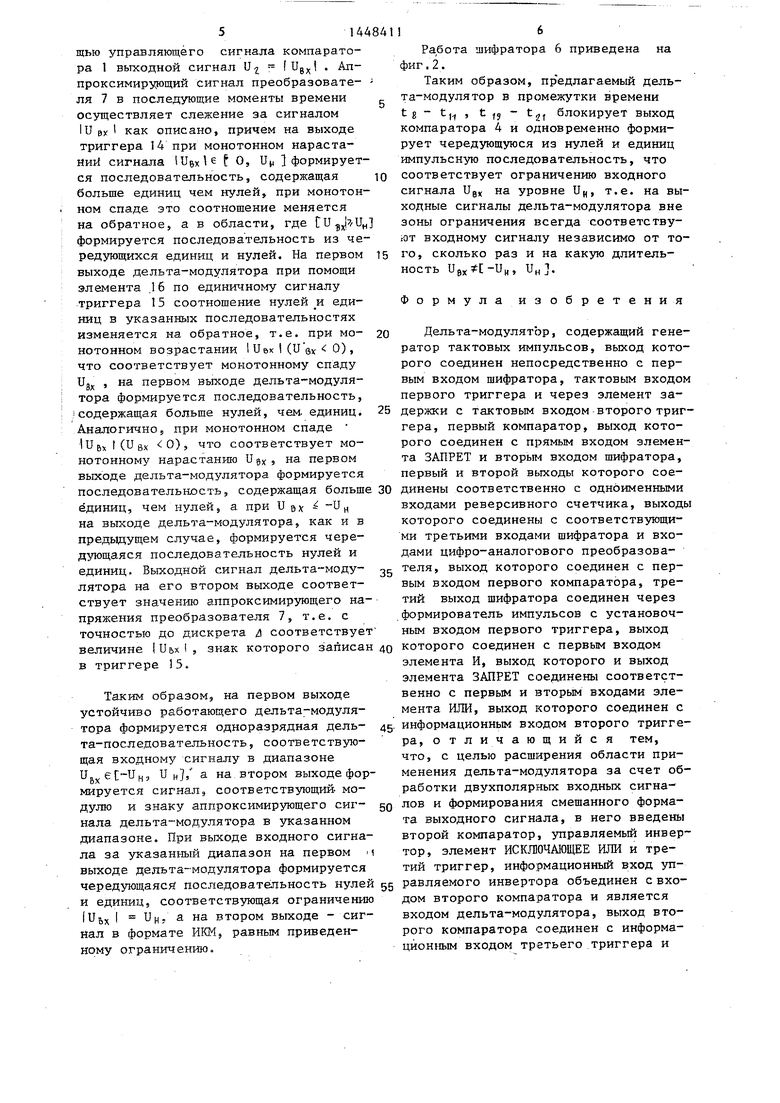

Шифратор содержит (фиг.2) элемент И 17 и элементы ЗАПРЕТ 18 и 19,

Дельта-модулятор работает следующим образом.

Входной сигнал Ugy(t) поступает на вход управляемого инвертора 2 и вход компаратора 1 знака. Выходной сигнал компаратора является заправляющим сигналом для инвертора 2, выходной сиг- нал которого всегда является неотрицательным.

Примем, что в интервале времени Со, t а происходит слежение аппроксимирующего напряжения преобразователя 7 за входным сигналом, величина которого не выходит за интервал (О, U), где и ц - номинальная величина для данного дельта-модулятора. Компаратор 1 формирует сигнал U О, и инвертор 2 пропускает входной сигнал без изменений. Реверсивный счетчик 5 заполнен до некоторого состояния, поэтому на первом выходе шифратора 6, фиксирующего максимальное состояние счетчика 5, сигнал отсутствует, т.е. сигнал на выходе элемента ЗАПРЕТ 10 соответствует выходному сигналу компаратора 4, На выходе элемента И 11 сигнал также отсутствует, на информационный вход триггера 14 подается выходной сигнал компаратона 4. Предположим, что в первом также (момент времени t,, фиг.З) после прихода первого тактового импульса от генератора 3 сигнал обратной связи преобразователя 7 меньше входного, т.е. сигнал на выходе компаратора 4 разрешает прохождение импульсов генератора 3 через шифратор 6 на вход сложения реверсивного счетчика 5,«При этом величина аппроксимирующего напряжения преобразователя 7 увеличивается на единицу дискретности 4 и принимает значение, лежащее в интервале U g, (t ,) , U в (t р + + ij, причем случай U-,(t) (t) приводит к срабатыванию компаратора 4 Выходной сигнал компаратора 1 после прихода первого тактового импульса от генератора 3 фиксируется в триггере 15, выходной сигнал которого поступает на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16. В результате сигнал на выходе элемента 16 при нулевом состоянии триггера 15 соответствует выходному сигналу триггера 14, а при единичном состоянии - инверсному выходному сигналу триггера 14. Выходной импульс компаратора 4 является на выходе элемента ИЛИ 13 после прихода соответствующего тактового импульса генератора 3 лишь спустя время задержки о,, определяемое временем срабатывания блоков 4-7, }0 и 13. Элемент 12 задержки необходим для согласования быстродействия блоков 4, 6 и 7 и задерживает тактовые импульсы на время З .; О,, вследствие чего триггер 14 в момент времени t t , запоминает сигнал элемента ИЛИ 13, значение которого равно значению сигнала компаратора 4 в момент t ,, т.е. триггер 14 выполняет функцию фиксирующей цепи нулевого порядка. Так t как в момент времени t + t выходной сигнал триггера J5 равен нулю, то выходной сигнал элемента 16 равен значению сигнала компаратора 4 в момент времени t,.

Аналогично работа дельта-модулятора происходит в интервале времени tj, t т. Сигнал элемента 16 равен сигналу триггера 14 и формируется с помощью сигнала инвертора 13, соответствующего значению прироста ап- роксимирующего напряжения преобразователя 7, причем при монотонном нарастании входного сигнала , на выходе дельта-модулятора формируется последовательность, содержащая больше единиц, чем нулей. При монотонном спаде ибх это соотношение ме 314

няется на обратное, а в области, где крутизна входного сигнала близка и нулю, число единиц и нулей в последовательности на выходе элемента 16 примерно одинаково. На выход триггера 15 поступает код, соответствующий знаку входного сигнала и код с разрядных выходов реверсивного счетчика

5,соответствующий значению аппрокси- мирующего сигнала преобразователя 7, т.е. на втором выходе дельта-модулятора формируется выходной сигнал в формате ИКМ, представленный прямым кодом со знаковым разрядом.

В случае равенства значений UB которое происходит в момент времени tp, выходные импульсы генератора 3 через шифратор 6 полностью заполняют реверсивный счетчик 5, в результате чего преобразователь 7 вырабатьгеает максимальную величину напряжения и7 UH обратной связи, а на третьем выходе блока 6 появляется импульс и, , передний фронт которого через формирователь 8 устанавливает триггер 9 в единичное состояние, спустя время, опр -деляемое задержкой срабатывания блоков 5 и 6. Этот же импульс одновременно запрещает прохождение импульсов компаратора 4 через элемент ЗАПРЕТ 10 и разрешает прохождение импульсов триггера 9 через элементы И 11 и ИЛИ 13 на вход триггера 14, в результате чего на выходе последнего спустя время задержки Из, определяемое задержкой срабатывания блоков 5,

6,11 и 13, появляется соответствующий импульс (1 выходного унитарно

го кода). До появления импульса на выходе элемента И 17 триггер 9 работает в счетном режиме, изменяя после прихода каждого тактового импульса свое состояние на противоположное. Таким образом, за счет установки триггера 9 в единичное состояние не допускается случай сбой в выходном коде из-за неправильного фазирования выходных импульсов триггера 9. Величина задержек выбирается из условия при выполнении которого в момент времени t t + 3 реализуется запись в триггер 14 состояния триггера 9.

Когда значение превышает U (момент времени t 5) импульс генератора 3, воздействуя на вход триггера 9 изменяет состояние последнего на нулевое. Импульс генератора 3 не изме

5

0 5 О

0

5

g

0

няет состояние реверсивного счетчика 5, так как шифратор 6 блокирует прохождение этих импульсов на вход сложения счетчика 5 при полном его заполнении, в результате чего на выходе триггера 15 формируется код в формате ИКМ, соответствующий номинальному значению входного напряжения. В момент времени t tg + f триггер 14 запоминает значение сигнала триггера 9, т.е. при превьппении входным сигналом номинального значения для преобразователя 7 выходной сигнал элемента 16, сформированный с помощью компаратора 1, повторяет через время задержки t сигнал триггера 9. На выходе элемента 16 при выполнении условия и 8V UH формируется код - чередующаяся последовательность единиц и нулей, соответствующая значению UH.

Работа дельта-модулятора при последующем уменьшении входного сигнала в момент времени t.,, характеризуется тем, что после прихода очередного тактового импульса генератора 3 импульс элемента ЗАПРЕТ 19 со второго выхода шифратора 6 поступает на вход вычитания реверсивного счетчика 5. При этом аппроксимирукмцее напряжение уменьшается на единице дискретности и становится меньше входнрго сигнала, что приводит в момент времени t t , + ь к появлению на выходе компаратора 4 положительного потенциала. До момента времени t t j величина сигнала элемента И 17 принимает нулевое значение, разрешая прохождение импульсов компаратора А через элемент ЗАПРЕТ 10 и запрещая прохождение импульсов триггера 9 через элемент ИИ. Поэтому в момент времени t t + Ci на вход блока 12 поступает сигнал элемента ИЛИ 13, соответствующий сигнашу компаратора 4 в момент t t,, . Благодаря этому на первом и втором выходах дельта- модулятора появляется код, соответствующий знаку приращения и величине входного сигнала.

При изменении полярности входного сигнала U «iO работа дельта-модулятора происходит следующим образом.

В момент времени t ,5(допустим, что изменение полярности U ьх происходит в момент времени t(, e(t, ) в -- триггере 15 осуществляется запись единичного выходного сигнала компара- -тора 1. Инвертор 2 формирует с помо514

щью управляющего сигнала компаратора 1 выходной сигнал U . Ап- проксимиру;ющий сигнал преобразовате-

ля 7 в последующие моменты времени

осуществляет слежение за сигналом

Iи вх как описано, причем на выходе триггера 14 при монотонном нарастаний сигнала iUgxH f О, , формируется последовательность, содержащая больше единиц чем нулей, при монотонном спаде это соотношение меняется на обратное, а в области, где ,и„ формируется последовательность из чередующихся единиц и нулей. На первом выходе дельта-модулятора при помощи элемента .16 по единичному сигналу триггера 15 соотношение нулей к единиц в указанных последовательностях изменяется на обратное, т.е. при мо- нотонном возрастании I Uex (U ex О), что соответствует монотонному спаду Ug , на первом выходе дельта-модулятора формируется последовательность, : содержащая больше нулей, чем. единиц. Аналогично, при монотонном спаде lUB lCUgx 0), что соответствует монотонному нарастанию Ugj, на первом выходе дельта-модулятора формируется последовательность, содержащая больше единиц, чем нулей, а при U вх - U на выходе дельта-модулятора, как и в предьщущем случае, формируется чередующаяся последовательность нулей и единиц. Выходной сигнал дельта-моду- лятора на его втором выходе соответствует значению аппроксимирующего напряжения преобразователя 7, т.е. с точностью до дискрета соответствует величине IUaxI, знак которого записан в триггере 15.

Таким образом, на первом выходе устойчиво работающего дельта-модулятора формируется одноразрядная дель- та-последовательность, соответствующая входному сигналу в диапазоне Uj eC-UnD и а. на, в тором выходе формируется сигнал, соответствующий модулю и знаку аппроксимирующего сиг- нала дельта-модулятора в указанном диапазоне. При выходе входного сигнала за указанный диапазон на первом выходе дельта-модулятора формируется чередующаясй последовательность нулей и единиц, соответствующая ограничению lUbx I - UH, а на втором выходе - сиг- йал в формате ИКМ, равным приведенному ограничению.

Работа шифратора 6 приведена на фиг.2.

Таким образом, пр едлагаемый дельта-модулятор в промежутки времени t g - t, , t f5 12т блокирует выход компаратора 4 и одновременно формирует чередующуюся из нулей и единиц импульсную последовательность, что соответствует ограничению входного сигнала Ug на уровне U|,, т.е. на выходные сигналы дельта-модулятора вне зоны ограничения всегда соответствуют входному сигналу независимо от того, сколько раз и на какую длительность , UHJ.

Формулаиз обретения

Дельта-модулятор, содержащий генератор тактовых импульсов, выход которого соединен непосредственно с первым входом щифратора, тактовьм входо первого триггера и через элемент задержки с тактовым входом второго триггера, первый компаратор, выход которого соединен с прямым входом элемента ЗАПРЕТ и вторым входом шифратора, первый и второй ВЕ ГХОДЫ которого соединены соответственно с одноименными входами реверсивного счетчика, выход которого соединены с соответствующими третьими входами шифратора и входами цифро-аналогового преобразователя, выход которого соединен с первым входом первого компаратора, третий выход шифратора соединен через формирователь импульсов с установочным входом первого триггера, выход которого соединен с первым входом элемента И, выход которого и выход элемента ЗАПРЕТ соединены соответственно с первьм и вторым входами элемента ИЛИ, выход которого соединен с информационным входом второго триггера, о тличающийся тем, что, с целью расщирения области применения дельта-модулятора за счет обработки двухполярных входных сигналов и формирования смещанного формата выходного сигнала, в него введены второй компаратор, управляемый инвертор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и третий триггер, информационный вход управляемого инвертора объединен с входом второго компаратора и является входом дельта-модулятора, выход второго компаратора соединен с информационным входом третьего триггера и

ч.14484

управляющим входом управляемого инвертора, выход которого соединен с вторым входом первого компаратора, инверсн вход элемента ЗАПРЕТ объединен с вторым входом элемента И и подключен к третьему выходу шифратора, выход второго триггера соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является первьм 10

8

выходом дельта-модулятора, тактовый вход третьего триггера подключен к выходу генератора тактовых импульсов, выход третьего триггера соединен с ; вторым входом элемента ИСКЛЮЧАЙТЕ ИЛИ и является вторым выходом дельта - модулятора, выходы реверсивного счетчика являются третьими выходами дель та-модулятора.

ffi2.2

| Погрибной В.А | |||

| Линейная дельта- модуляция в системах обработки сигналов с импульсно-кодовой модуляцией | |||

| - Радиотехника, 1984, № 9, с.56-58 | |||

| Дельта-модулятор | 1985 |

|

SU1257849A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-30—Публикация

1987-05-04—Подача