Текст описания приведен в факсимильном виде.

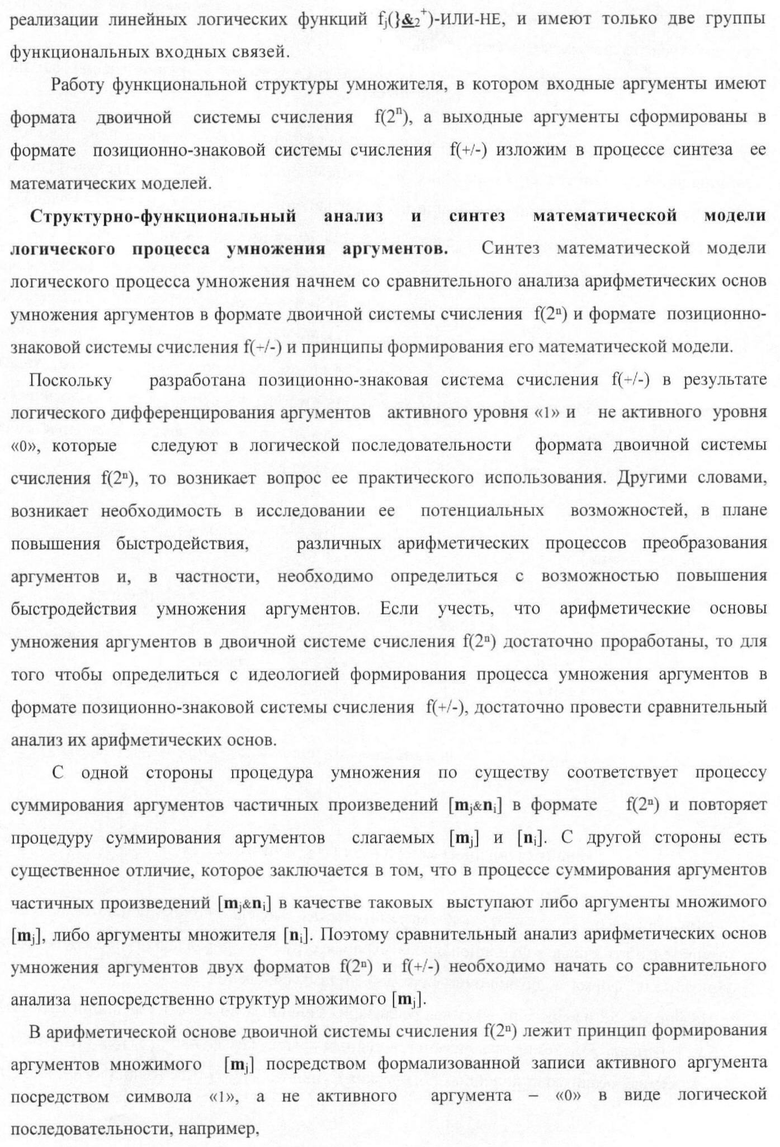

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств для выполнения арифметических операций в позиционно-знаковых кодах. Техническим результатом является повышение быстродействия устройства. Каждый разряд устройства выполнен в виде двух эквивалентных по структуре каналов - положительного и условно отрицательного, при этом, в одном из вариантов выполнения, i-ый разряд каждого канала содержит два элемента И, два элемента ИЛИ-НЕ. 4 ил.

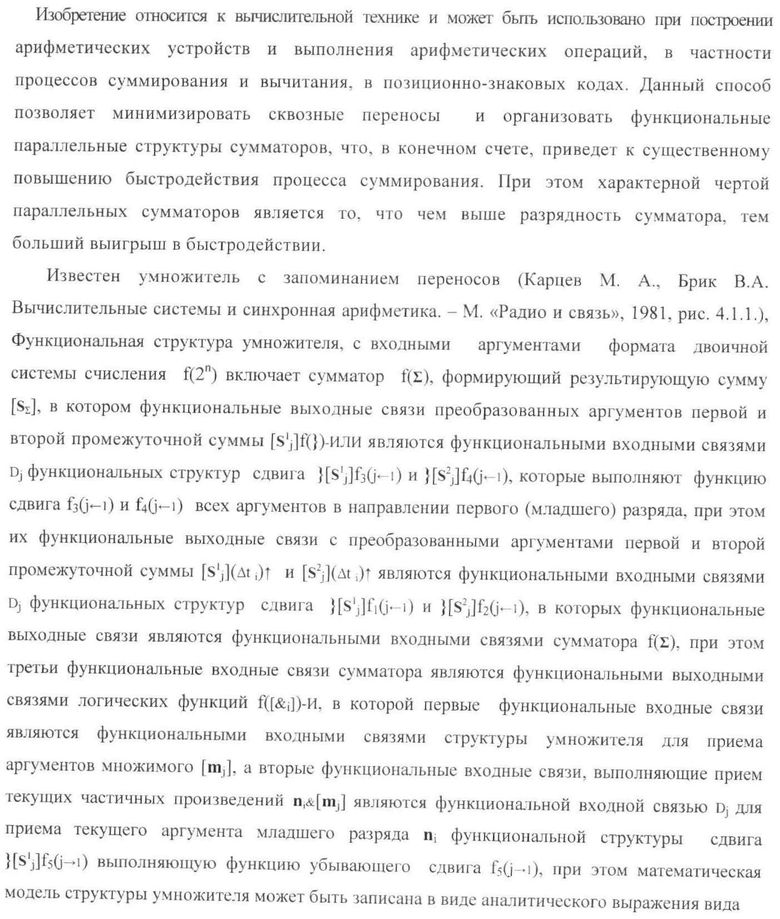

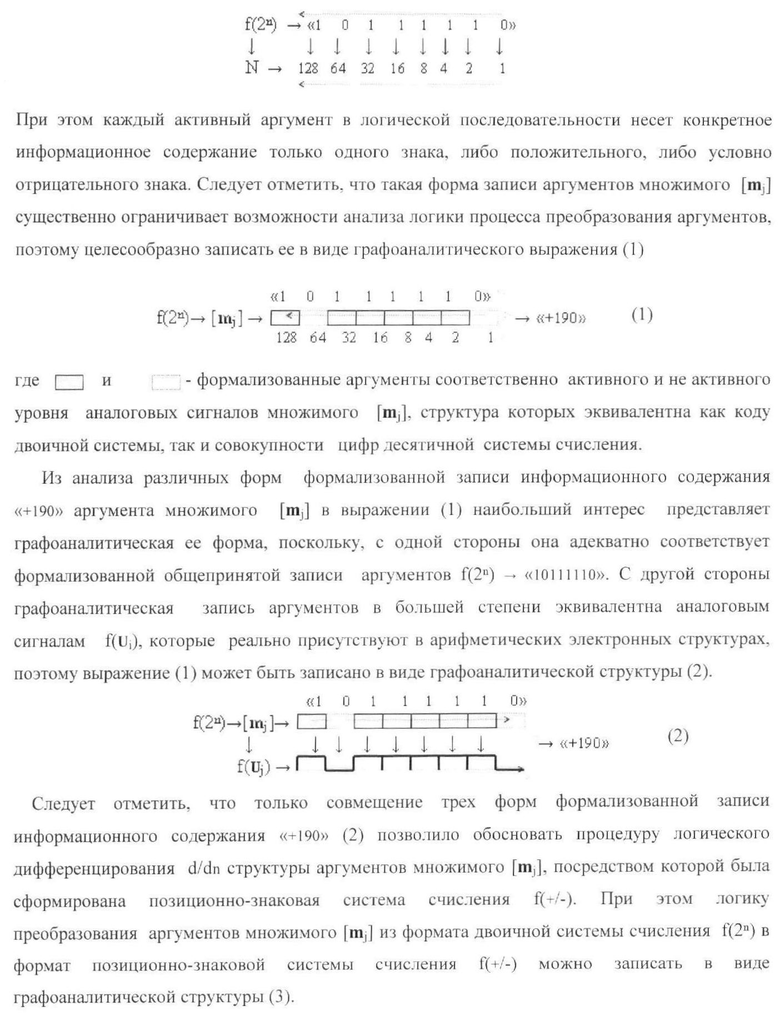

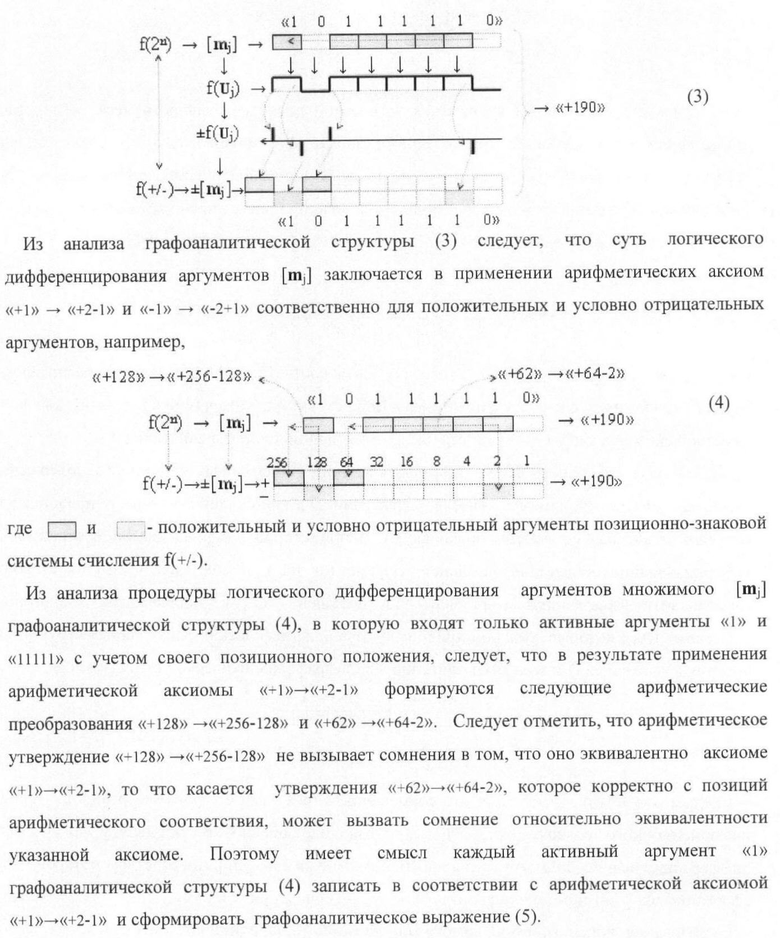

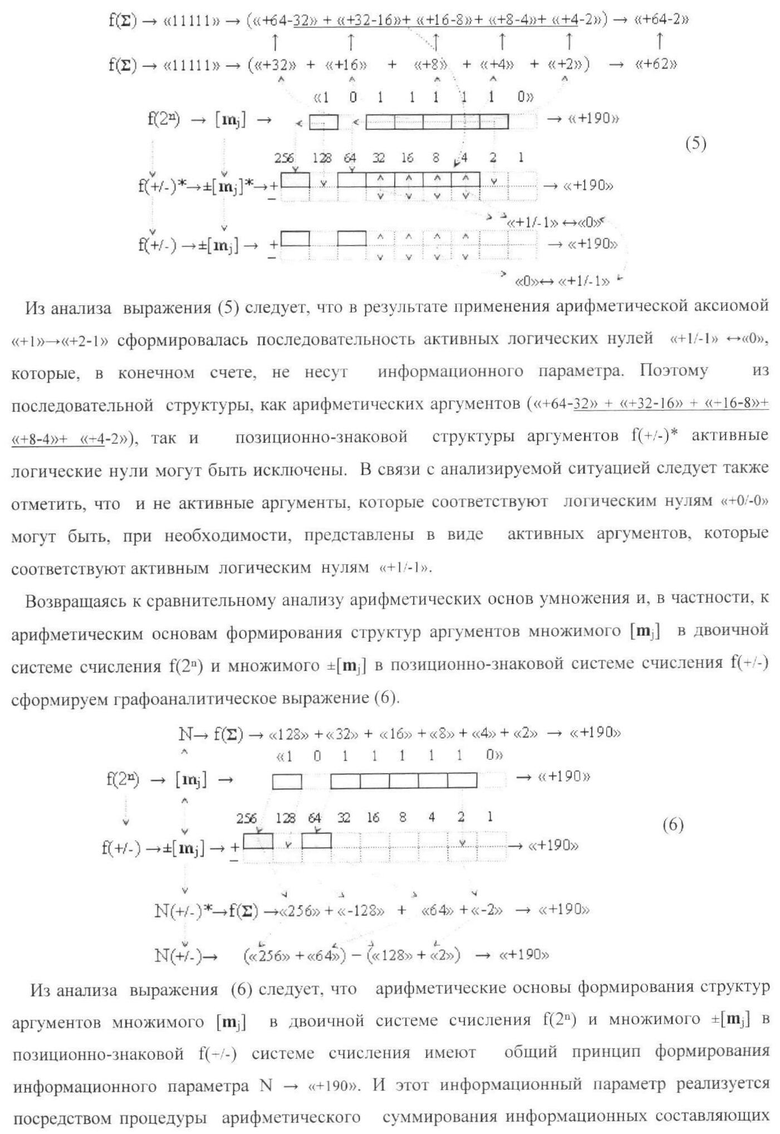

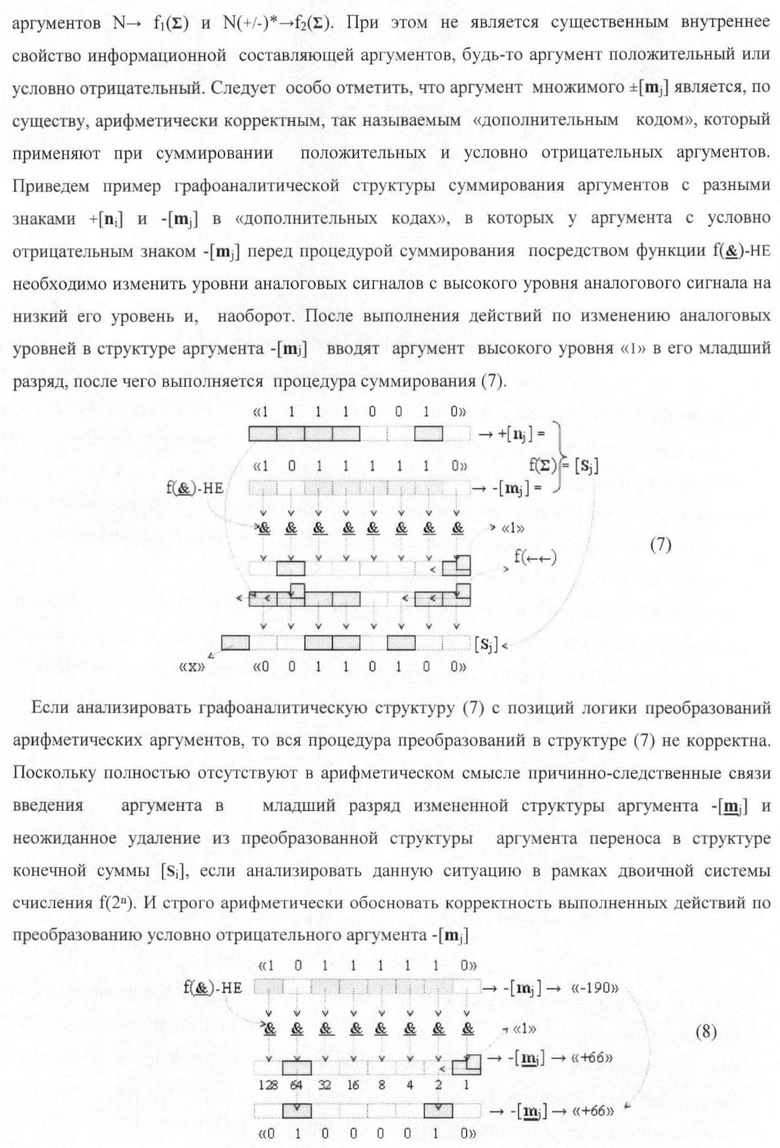

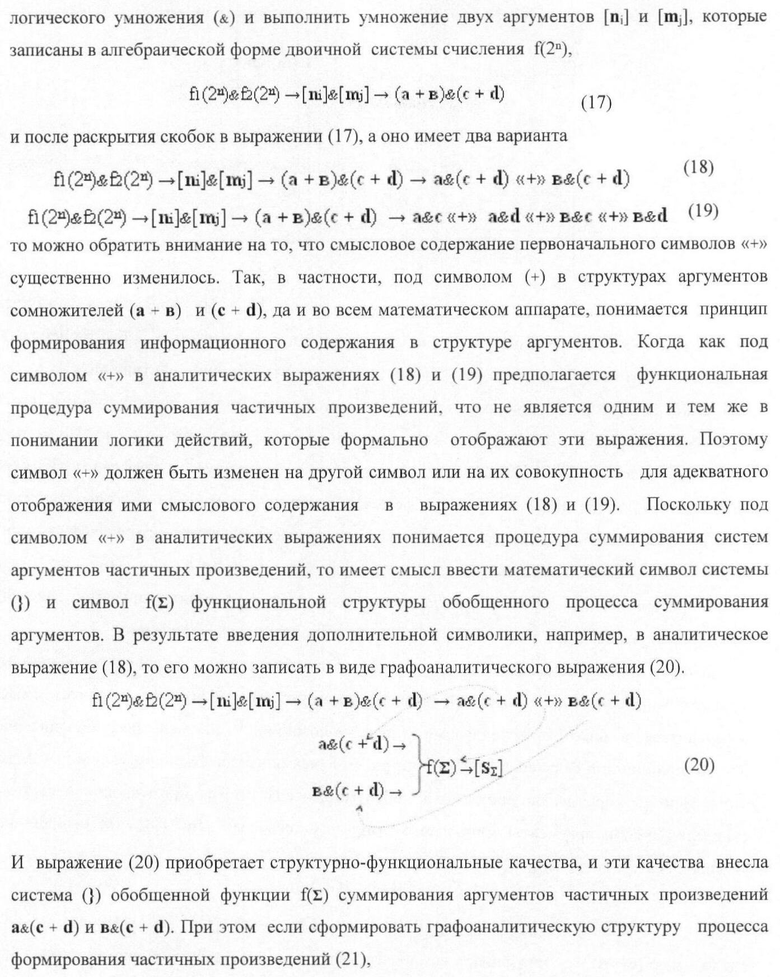

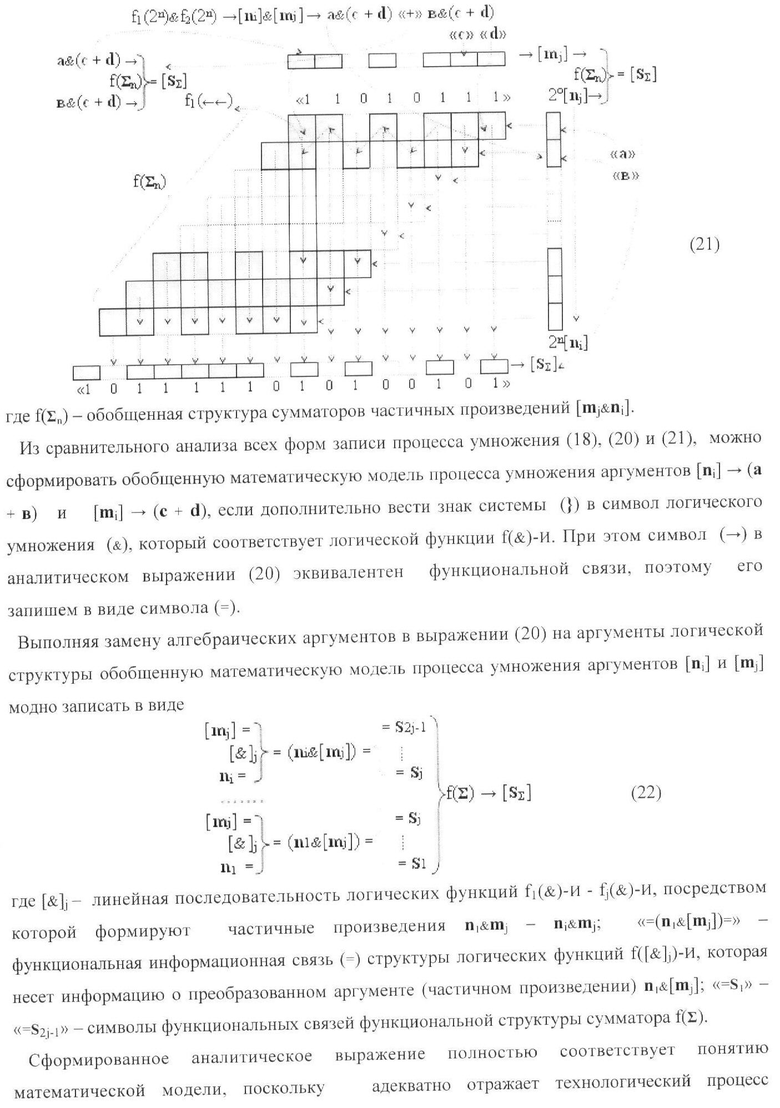

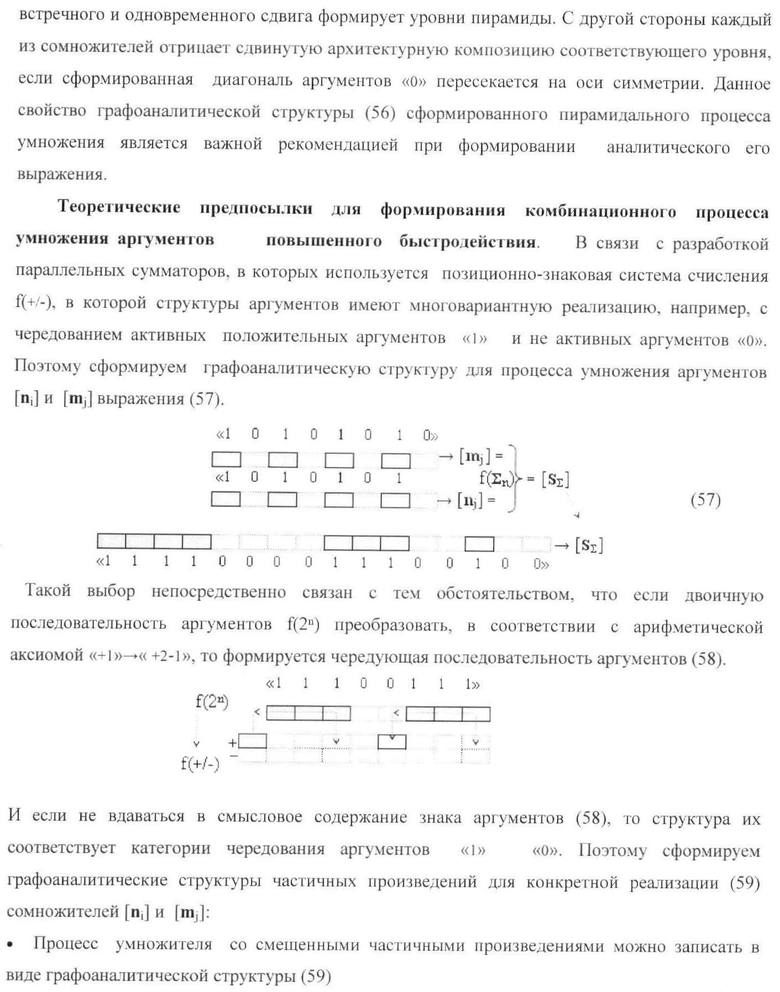

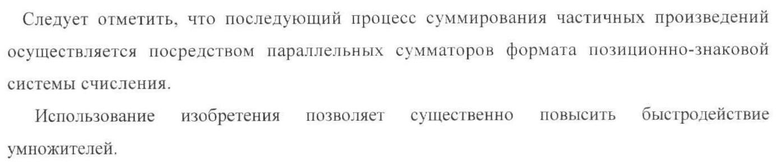

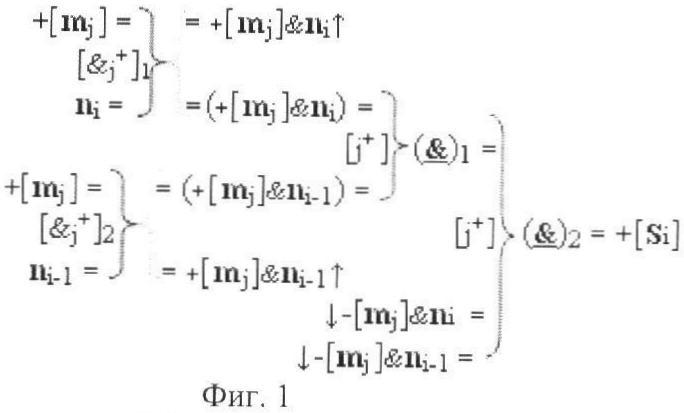

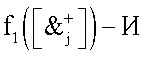

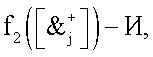

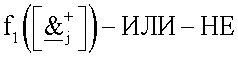

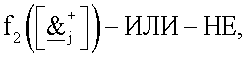

Функциональная входная структура параллельно-последовательного умножителя формата позиционно-знаковой системы счисления f(+/-), включающая линейную логическую функцию  для формирования частичного произведения

для формирования частичного произведения

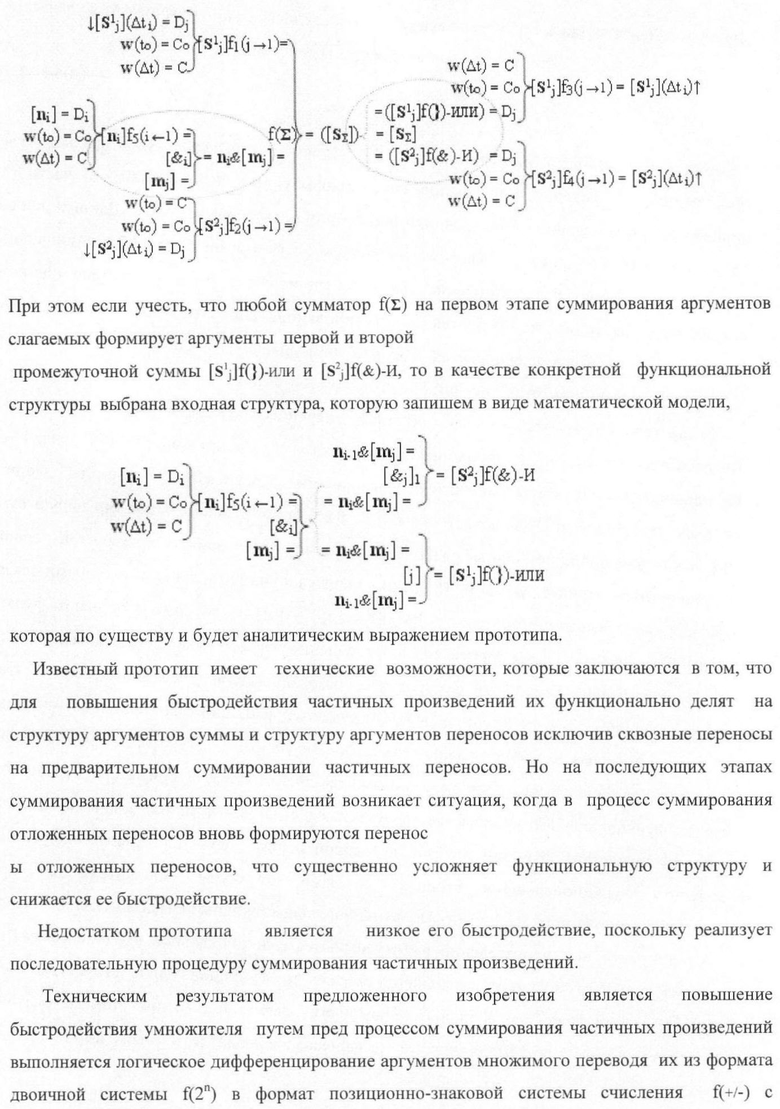

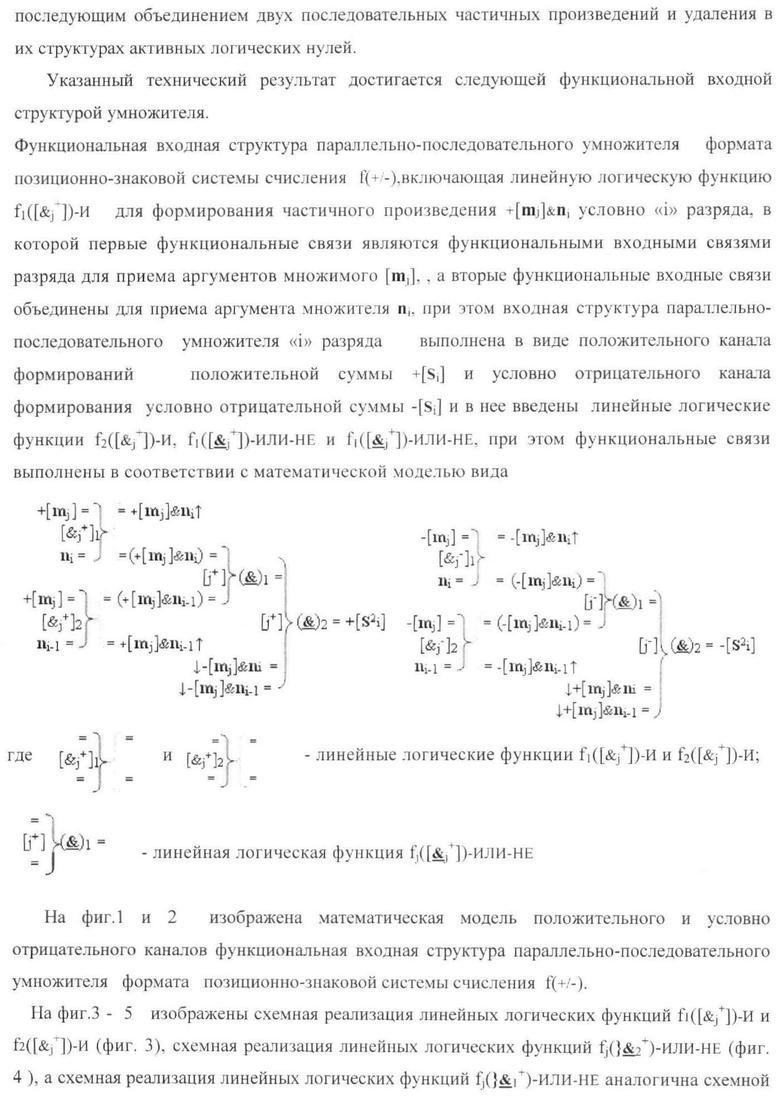

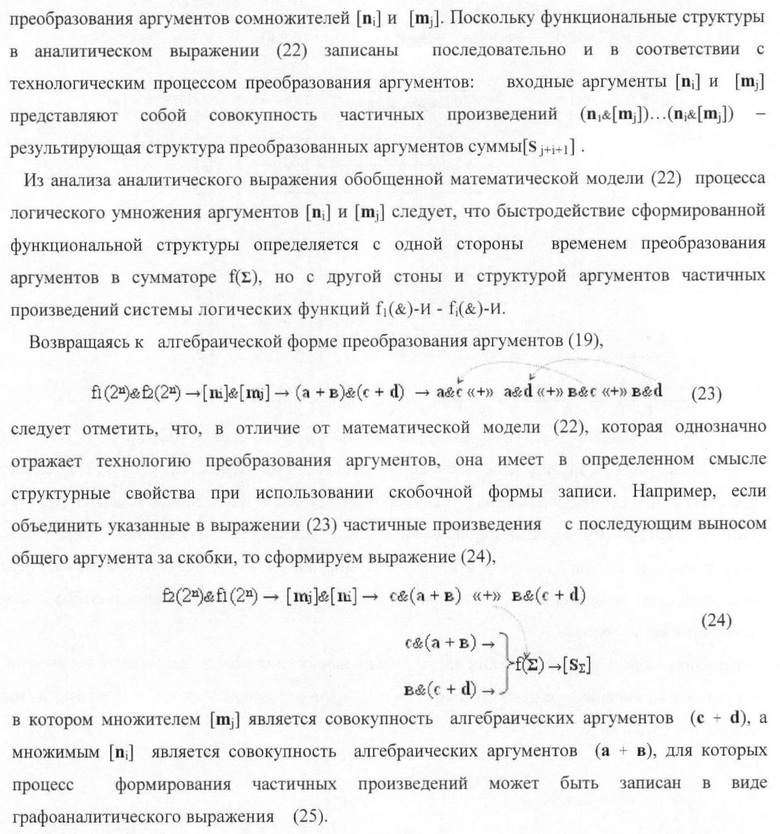

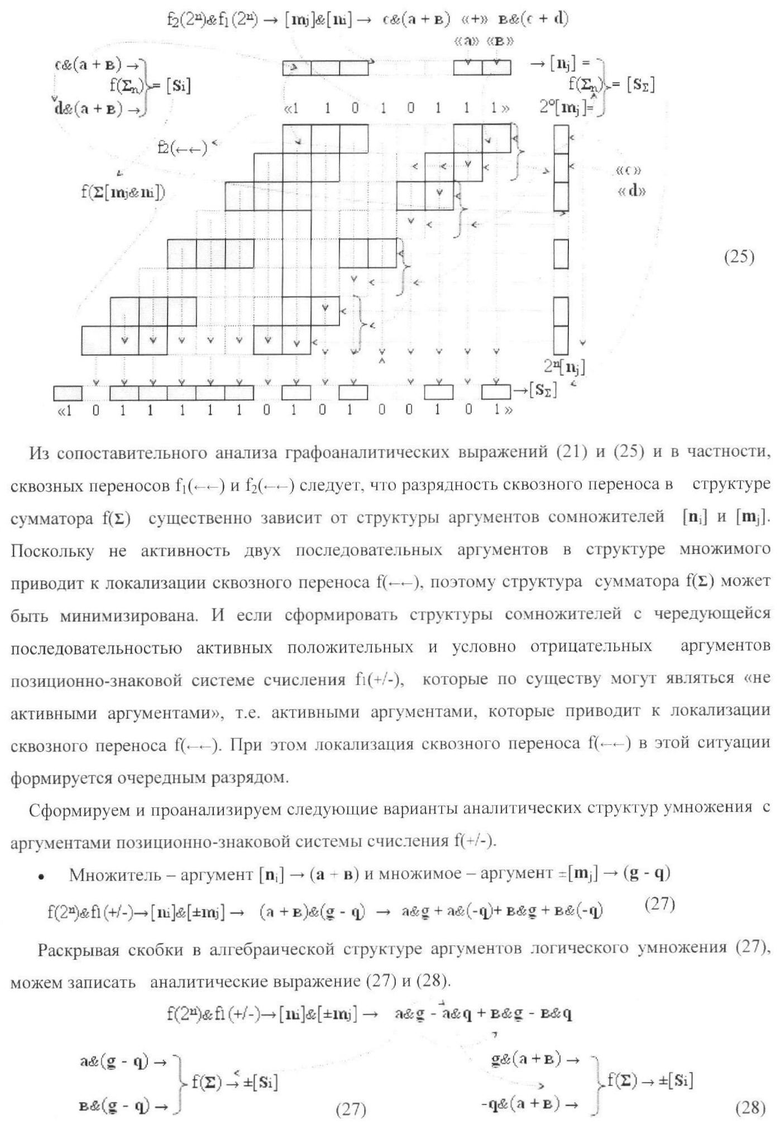

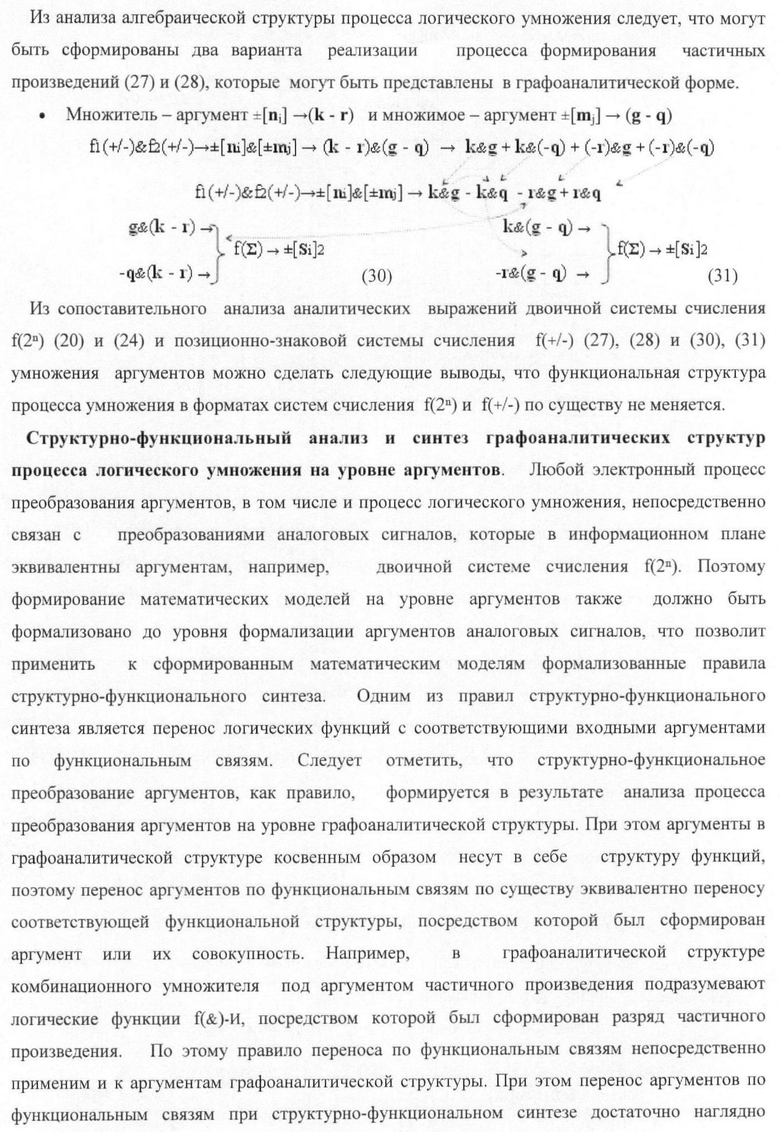

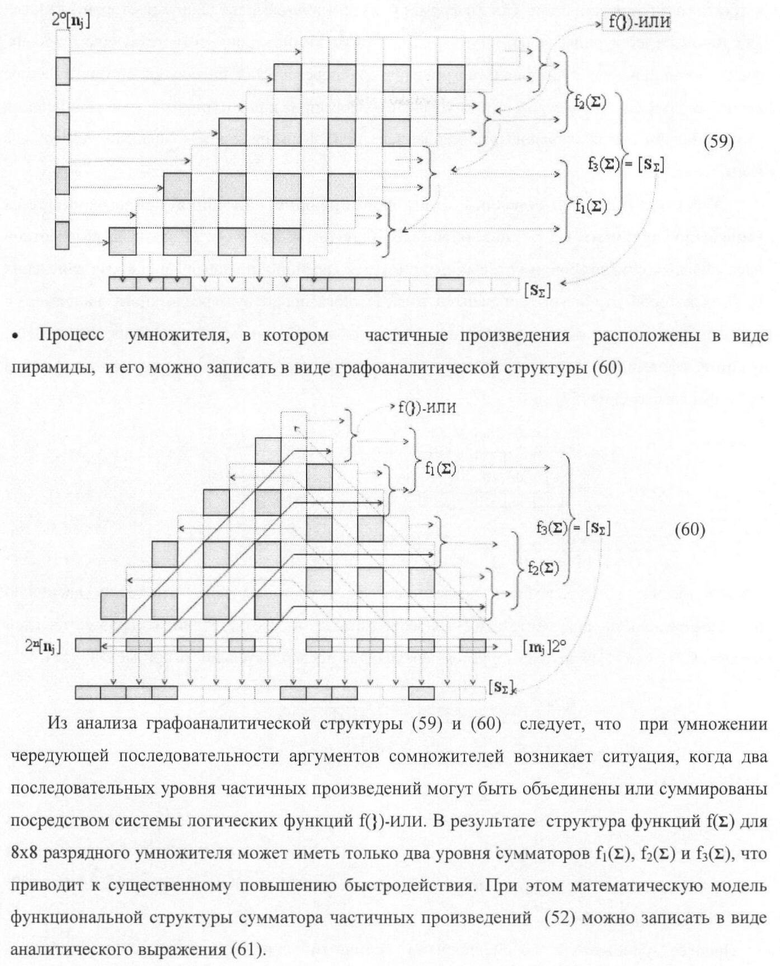

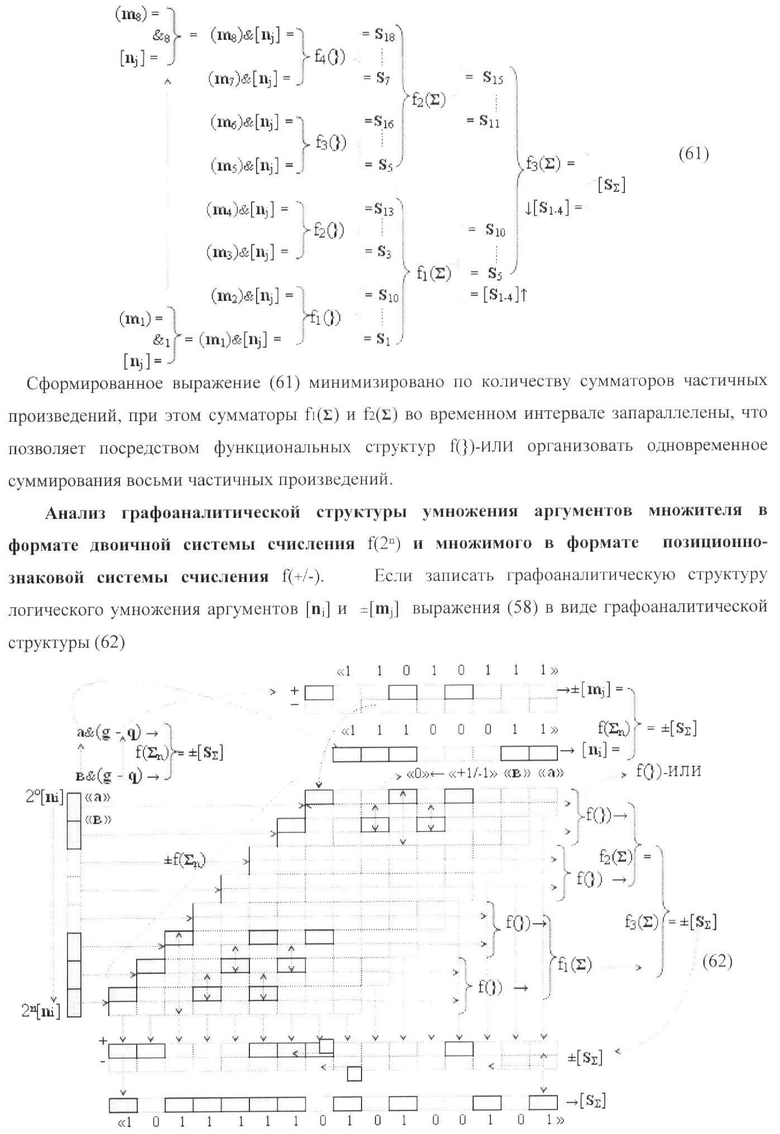

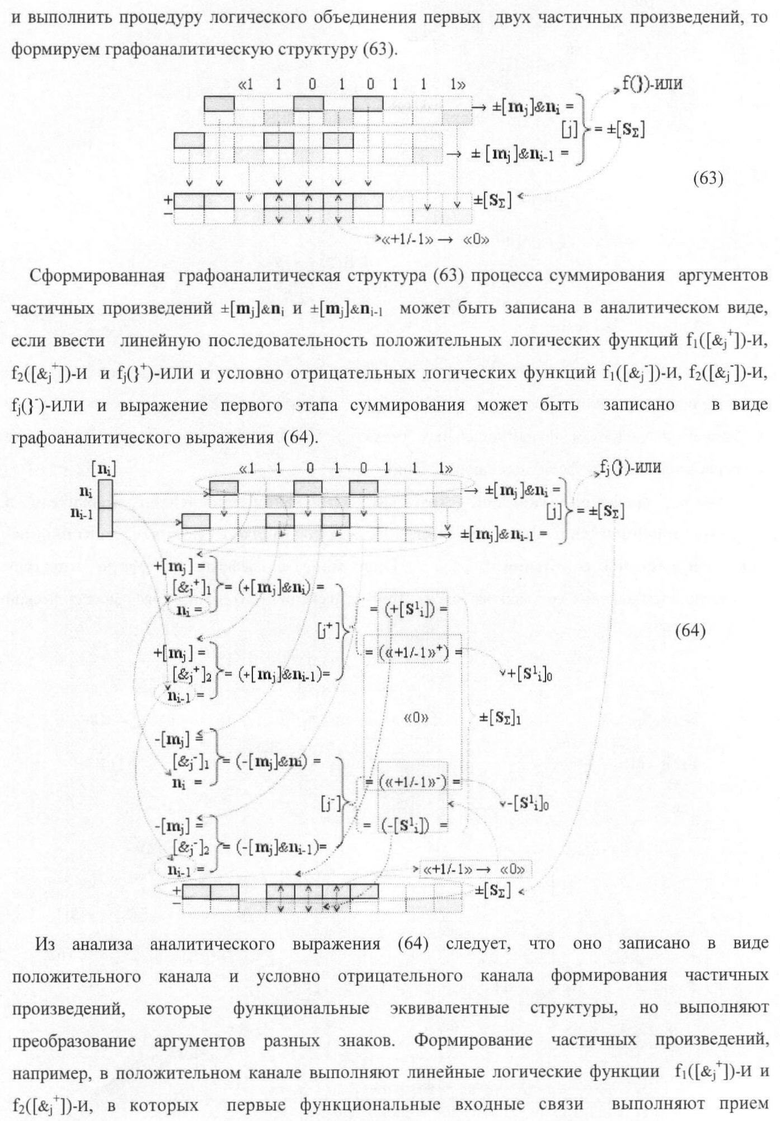

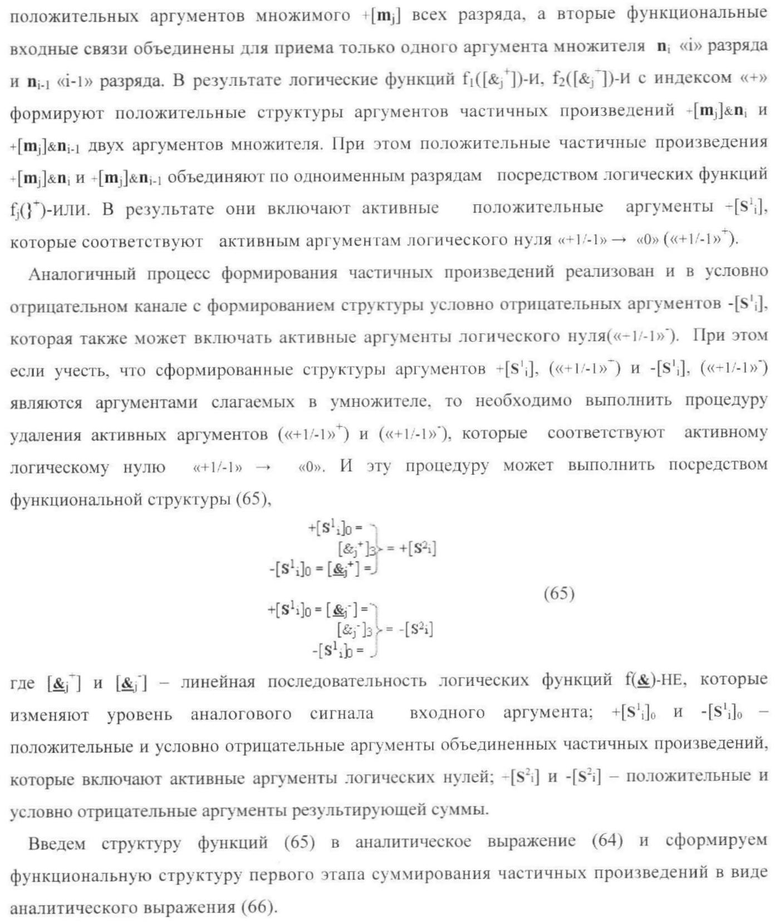

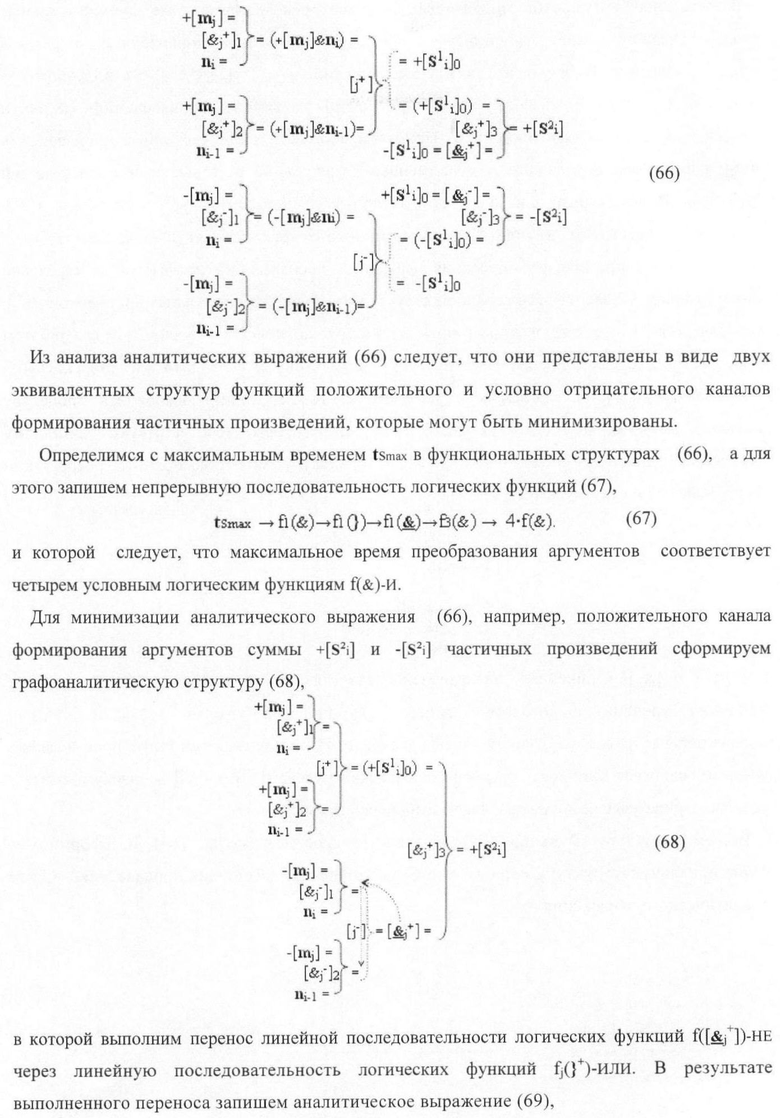

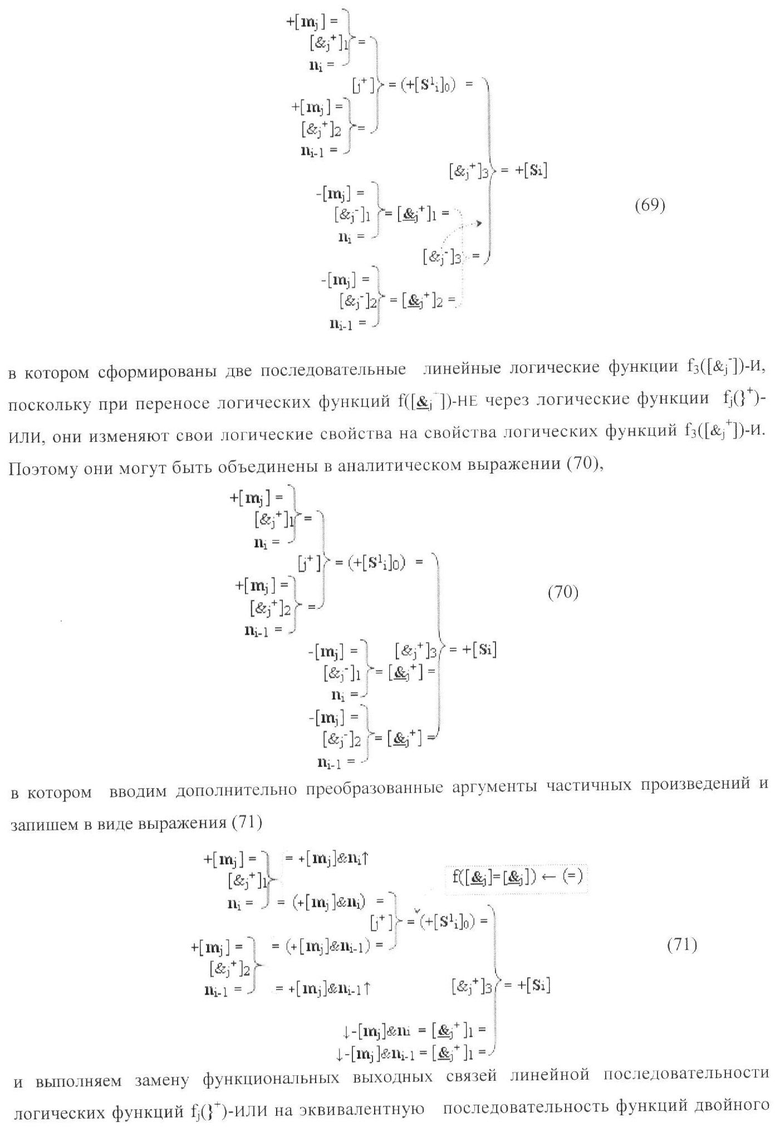

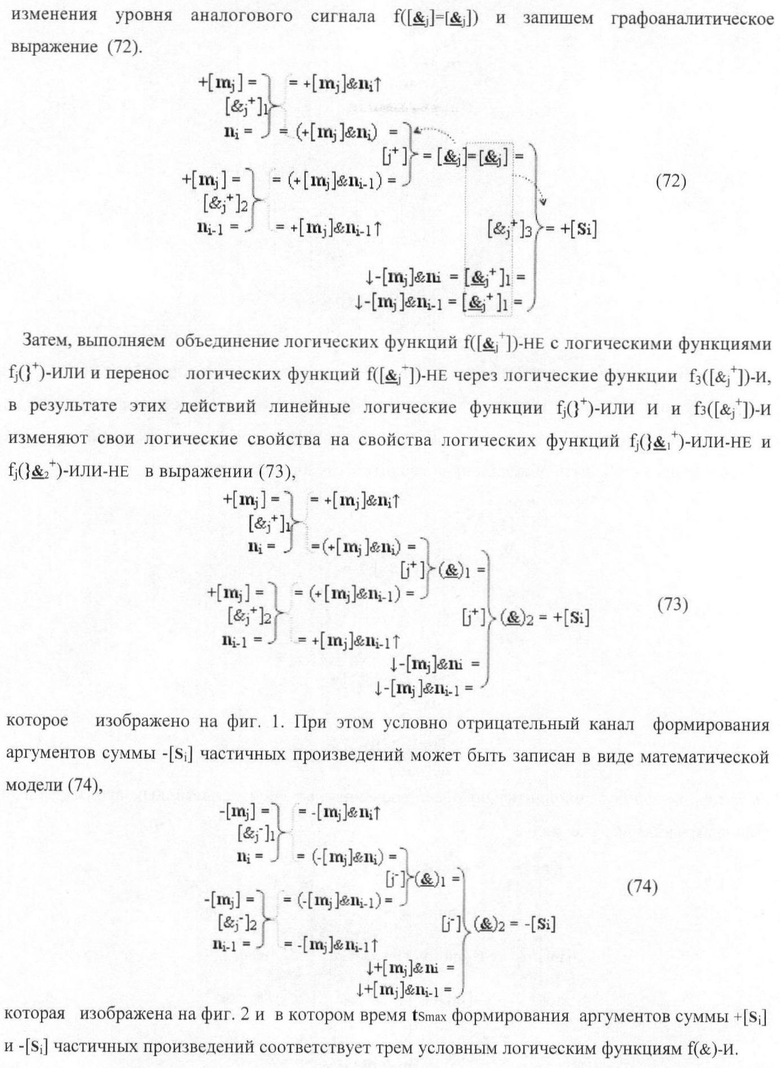

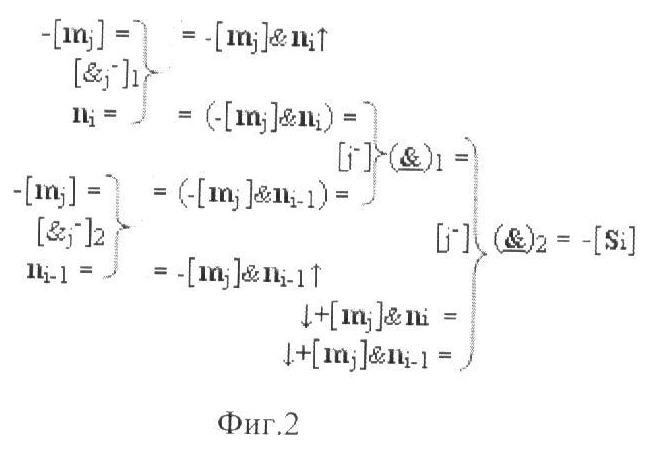

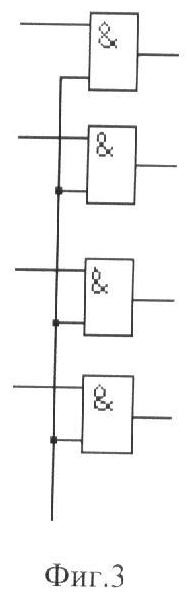

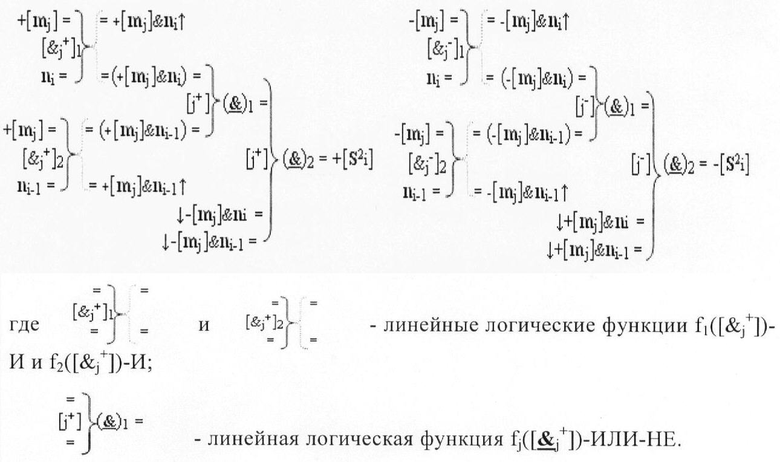

+[mj]&ni условно «i» разряда, в которой первые функциональные связи являются функциональными входными связями разряда для приема аргументов множимого [mj], а вторые функциональные входные связи объединены для приема аргумента множителя ni, отличающаяся тем, что входная структура параллельно-последовательного умножителя «i» разряда выполнена в виде положительного канала формирований положительной суммы +[Si] и условно отрицательного канала формирования условно отрицательной суммы -[Si], и в нее введены линейные логические функции

и

и  при этом функциональные связи выполнены в соответствии с математической моделью вида

при этом функциональные связи выполнены в соответствии с математической моделью вида

| КАРЦЕВ М.А., БРИК В.А | |||

| Вычислительные системы и синхронная арифметика | |||

| - М.: Радио и связь, 1981, с.164, рис.4.1.1 | |||

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| СПОСОБ УМНОЖЕНИЯ ДВУХ ЦИФРОВЫХ СИГНАЛОВ | 1993 |

|

RU2065201C1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| US 5986587 A, 16.11.1999 | |||

| US 6816877 B2, 09.11.2004. | |||

Авторы

Даты

2010-01-10—Публикация

2008-04-29—Подача