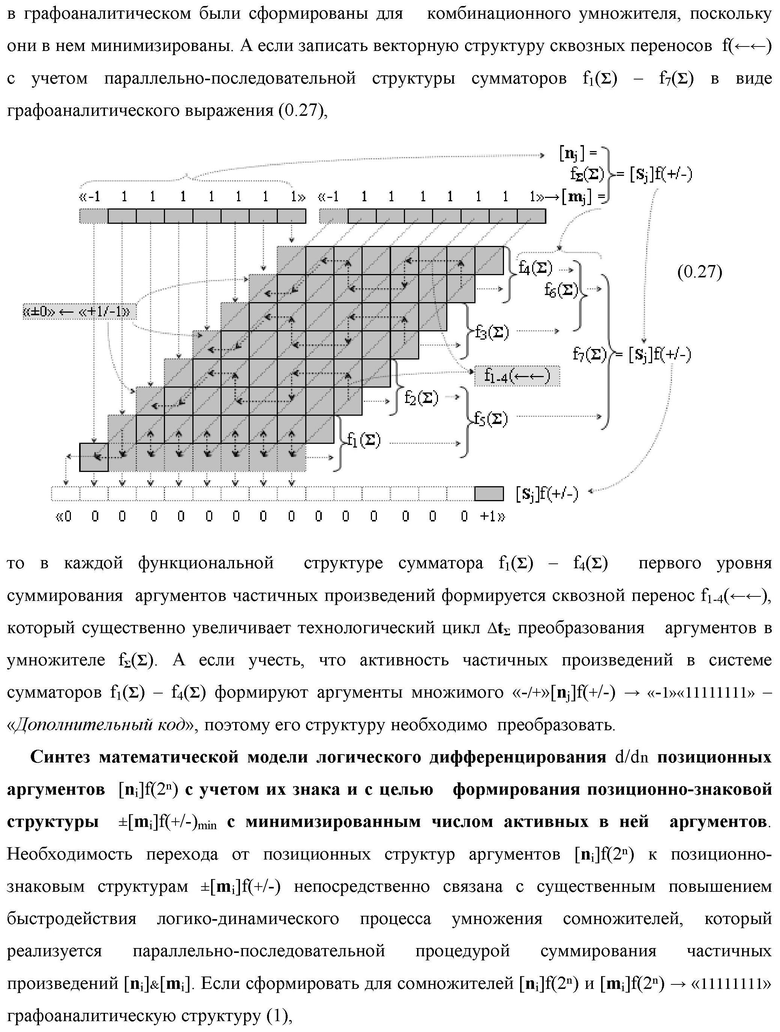

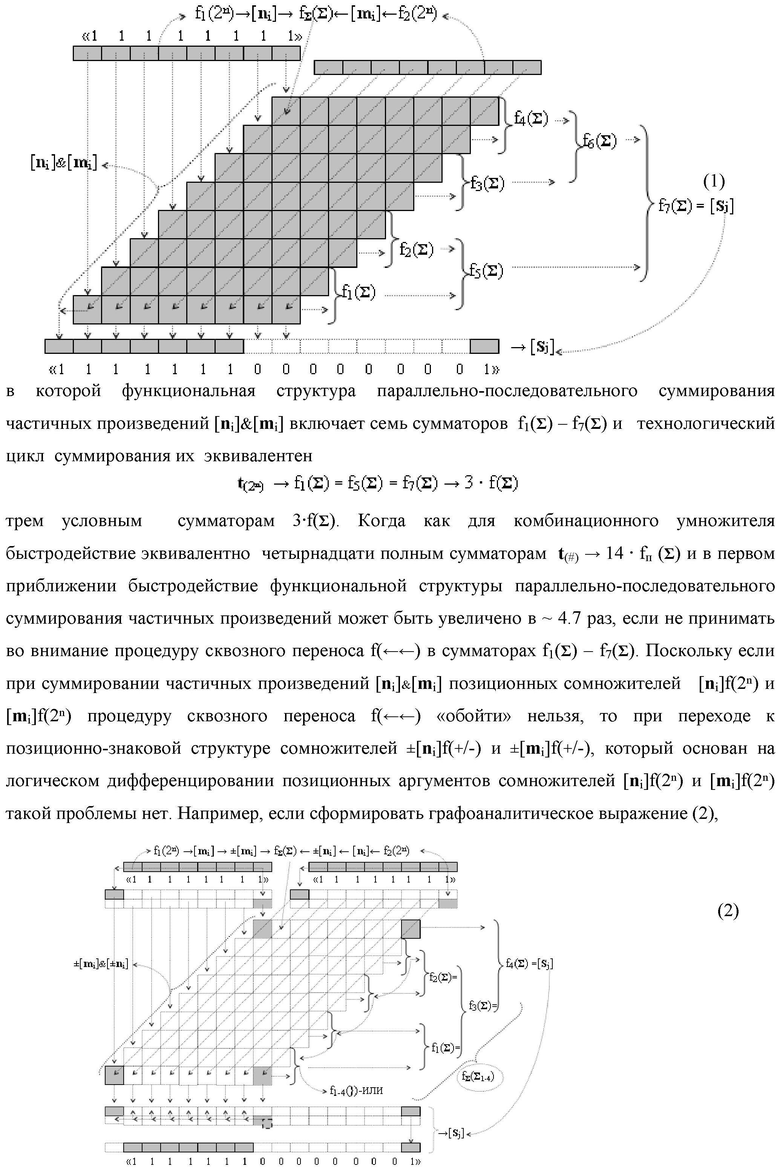

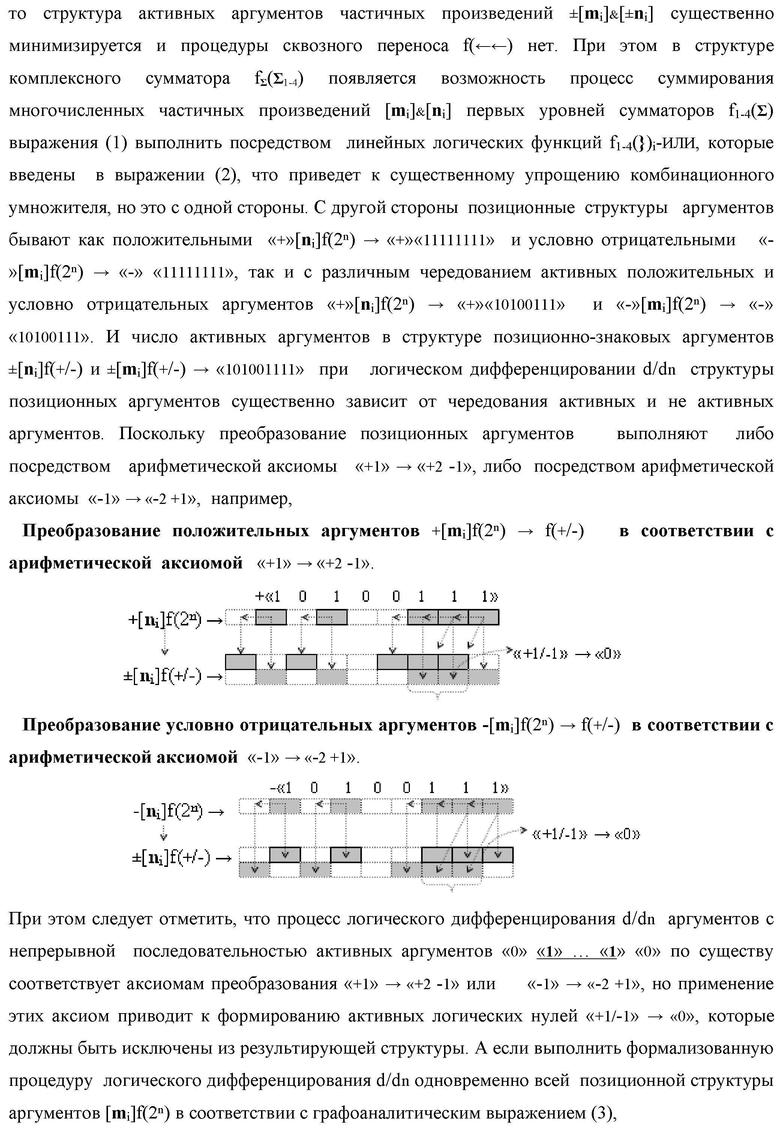

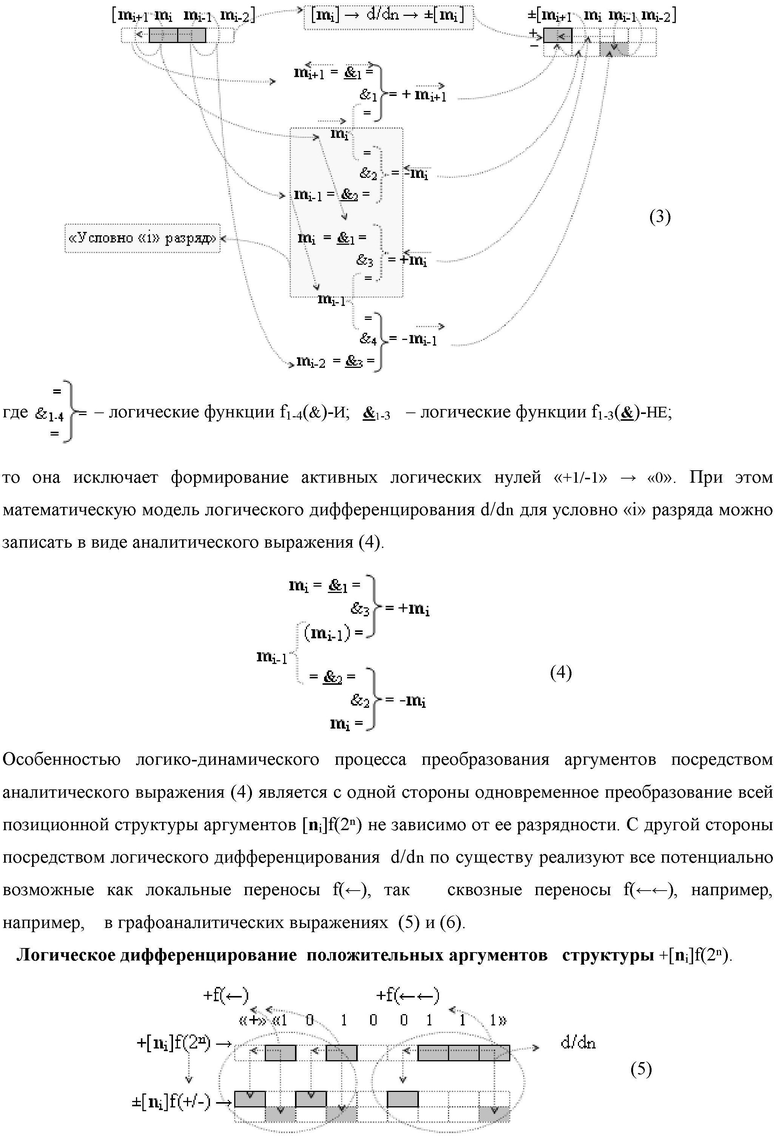

Текст описания приведен в факсимильном виде.

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств в позиционно-знаковых кодах. Техническим результатом является упрощение функциональных структур умножителей и повышение их быстродействия. В одном из вариантов изобретения функциональная структура выполнена в виде положительного и условно отрицательного каналов «j» и «j+1» разрядов преобразования входных аргументов. При этом каждый канал содержит элементы, реализующие логические функции И, ИЛИ и НЕ. 4 н.п. ф-лы.

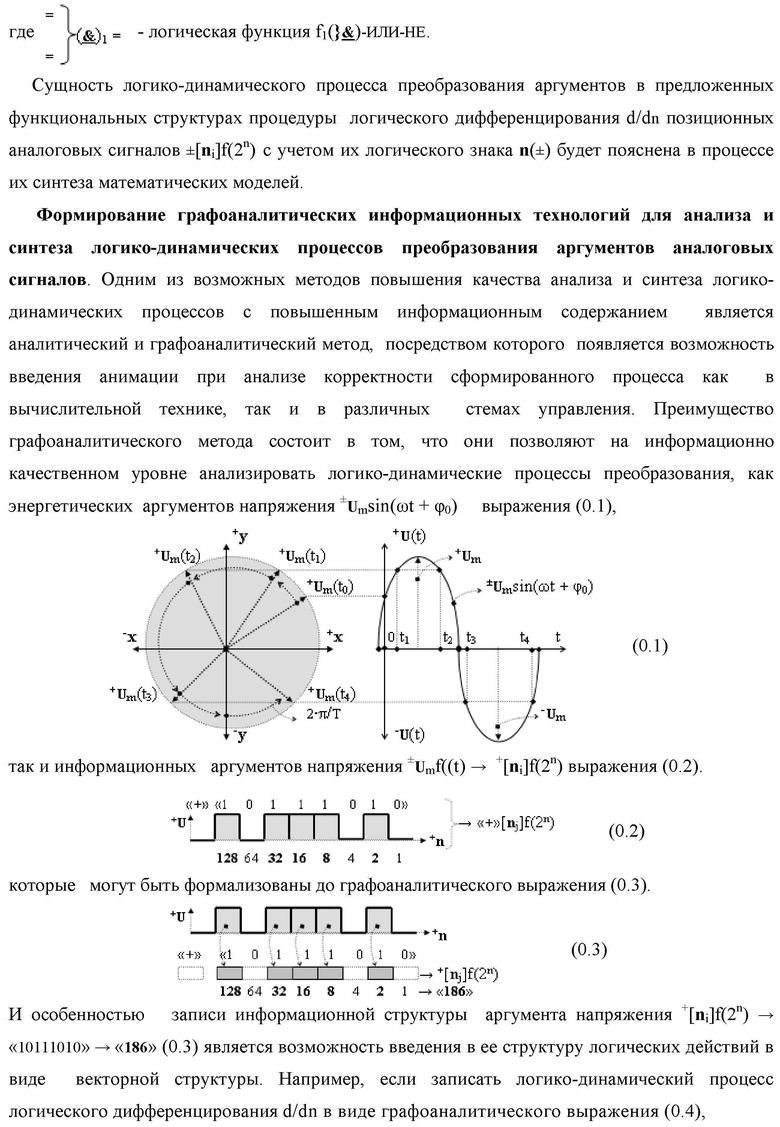

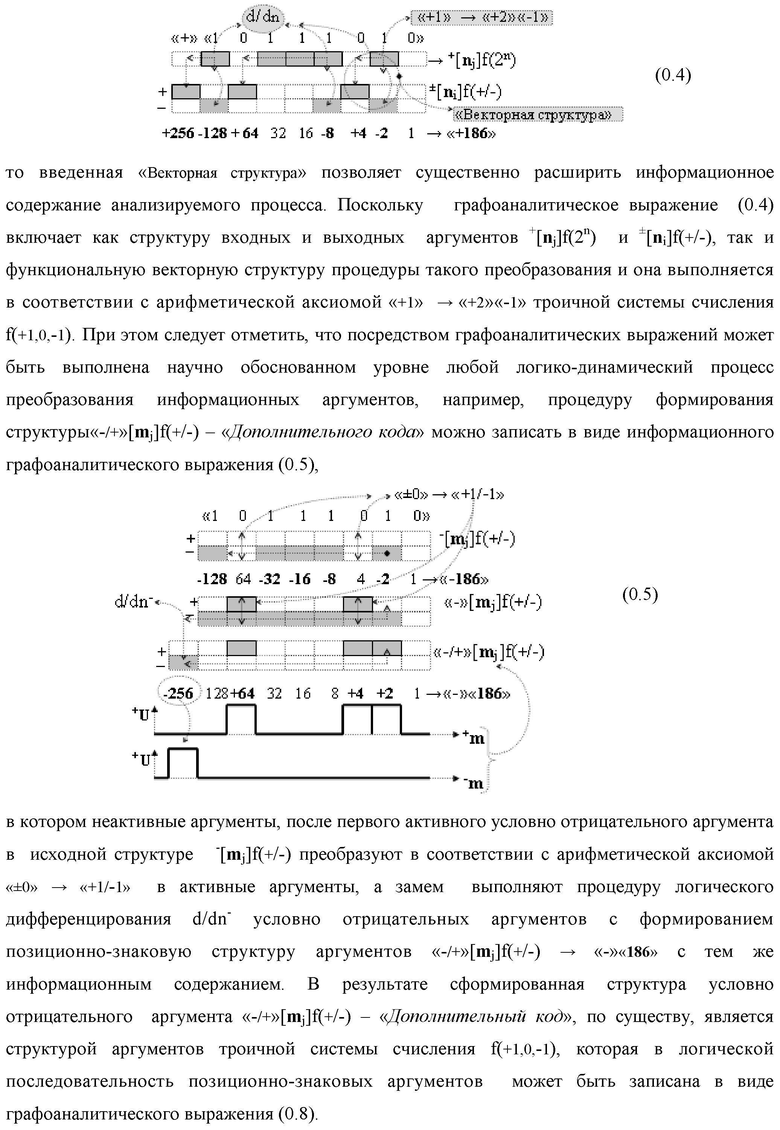

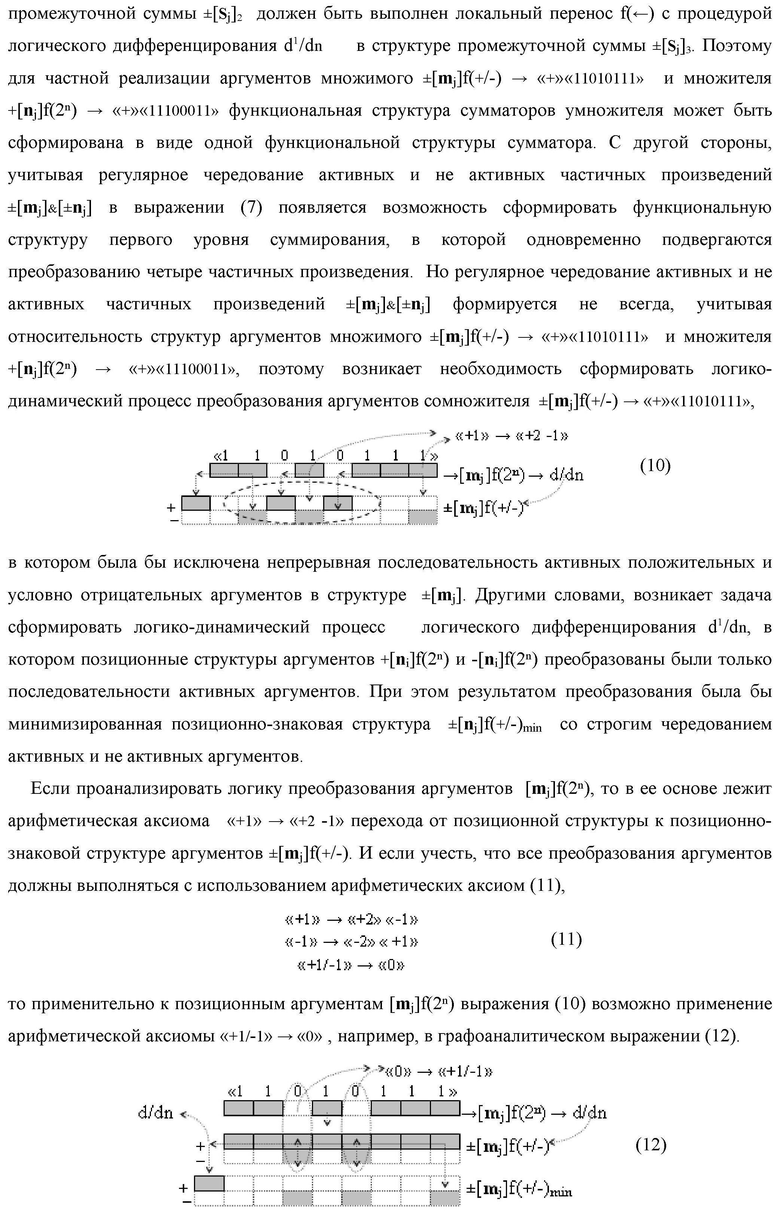

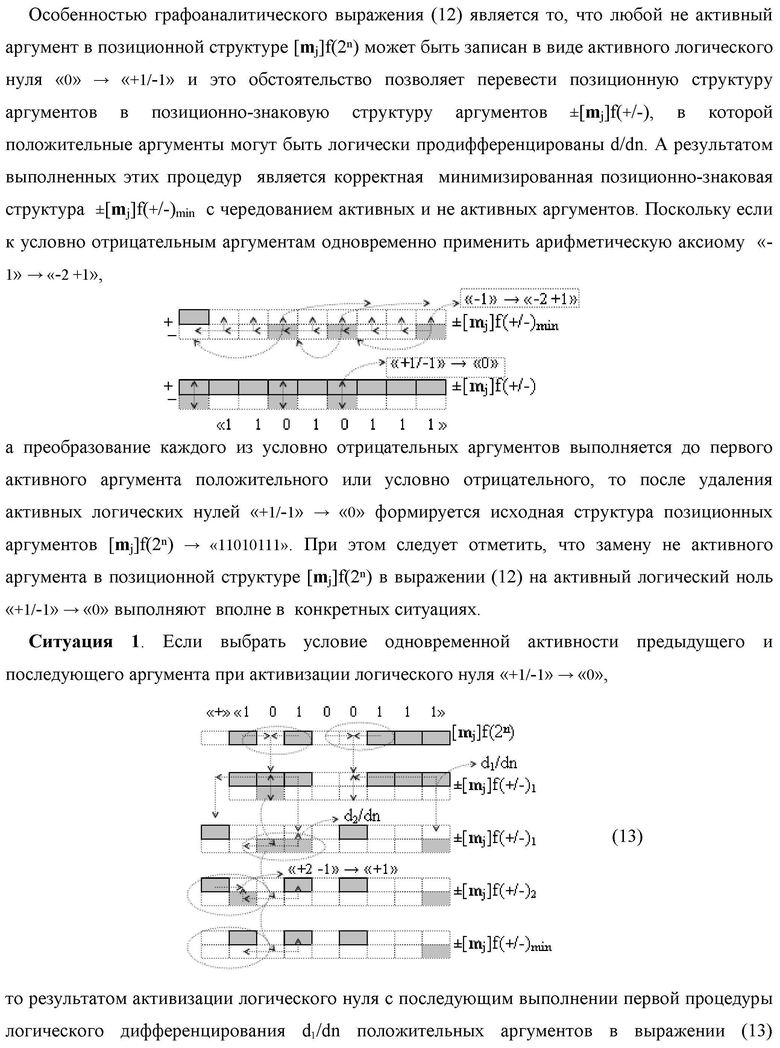

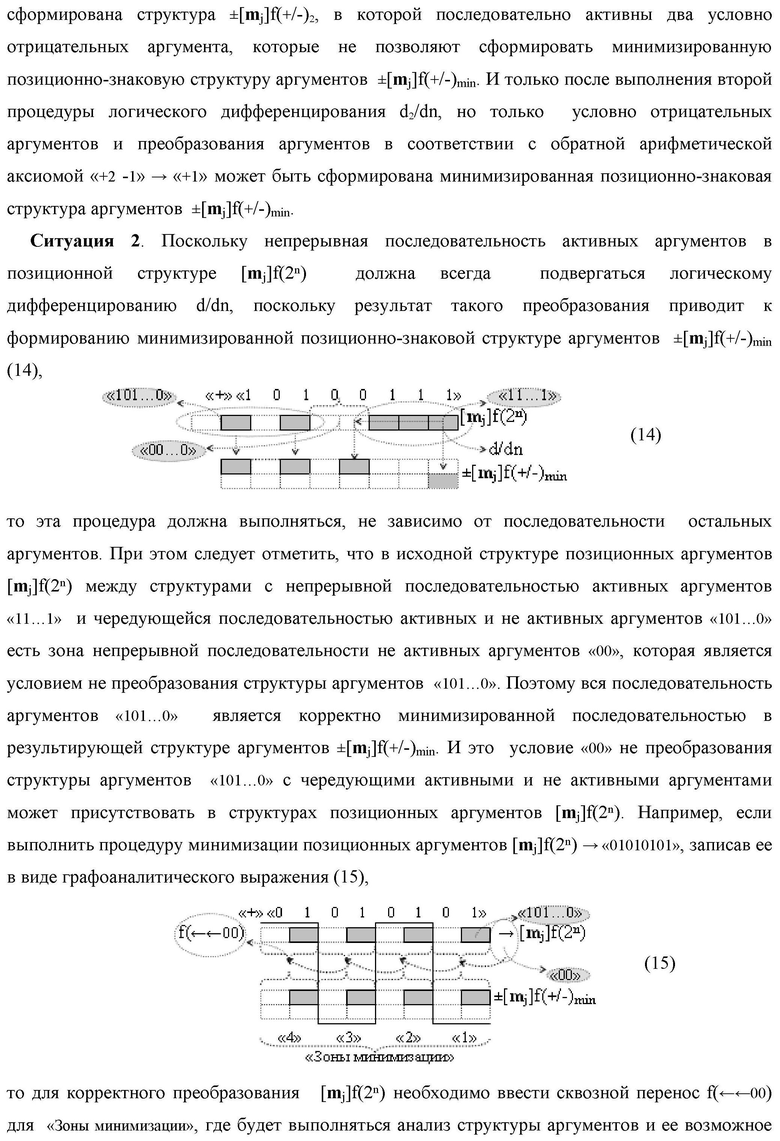

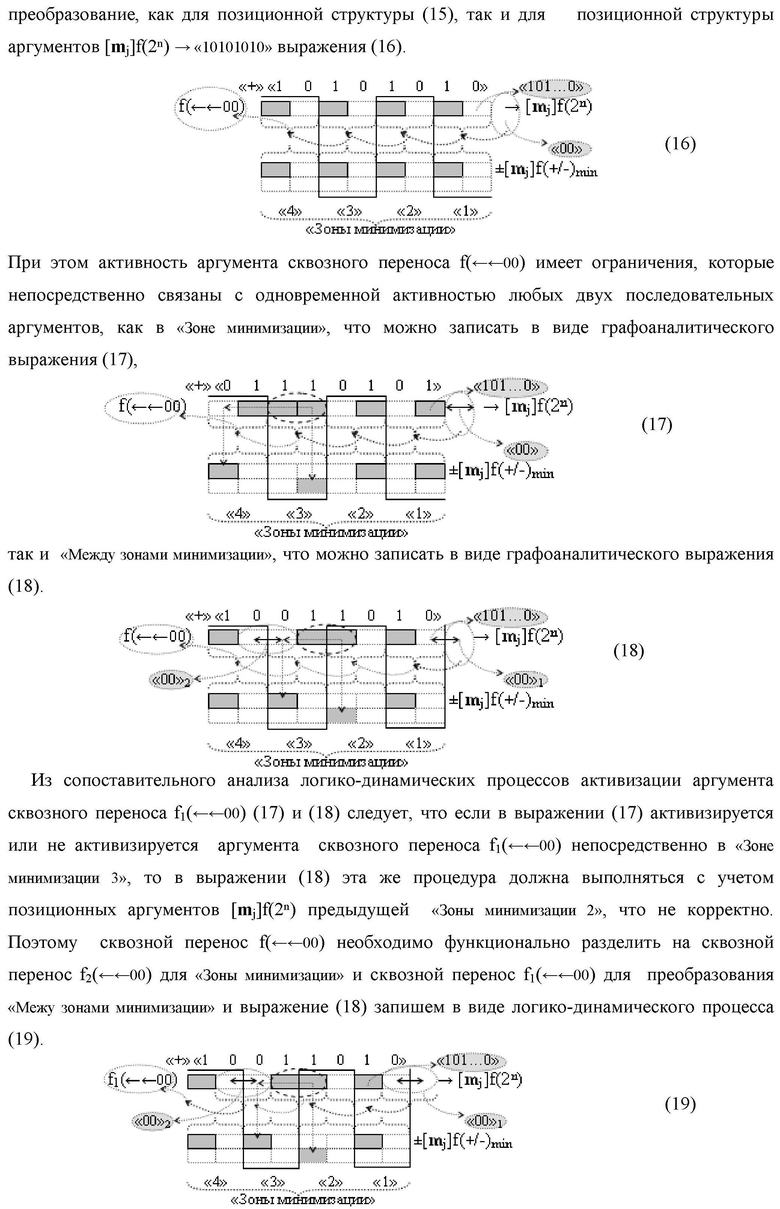

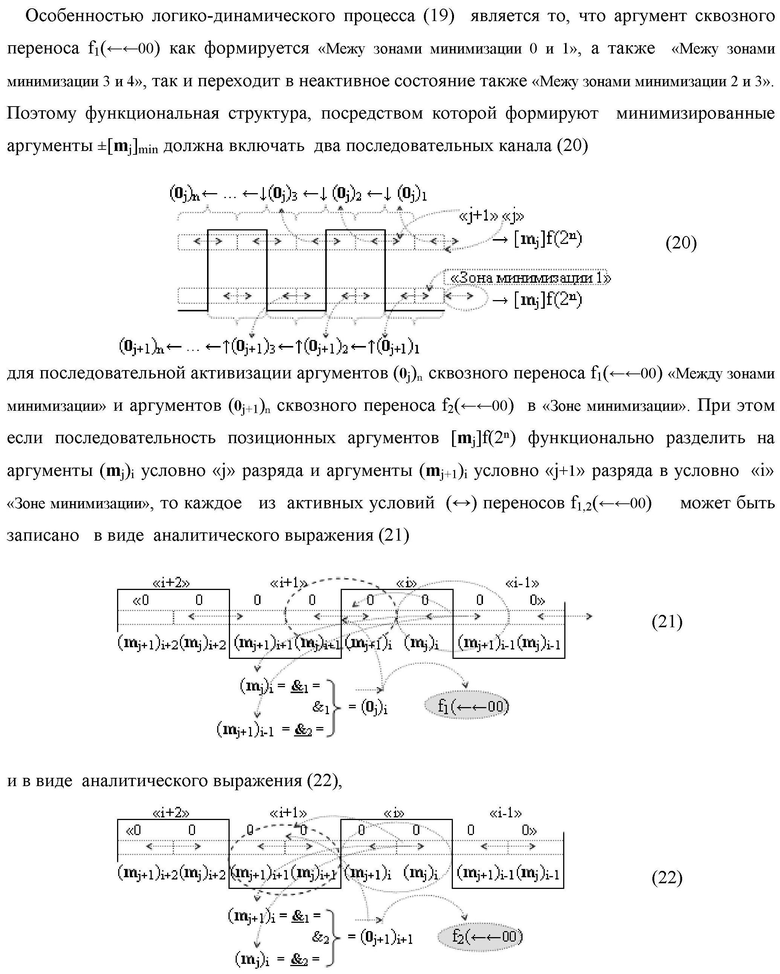

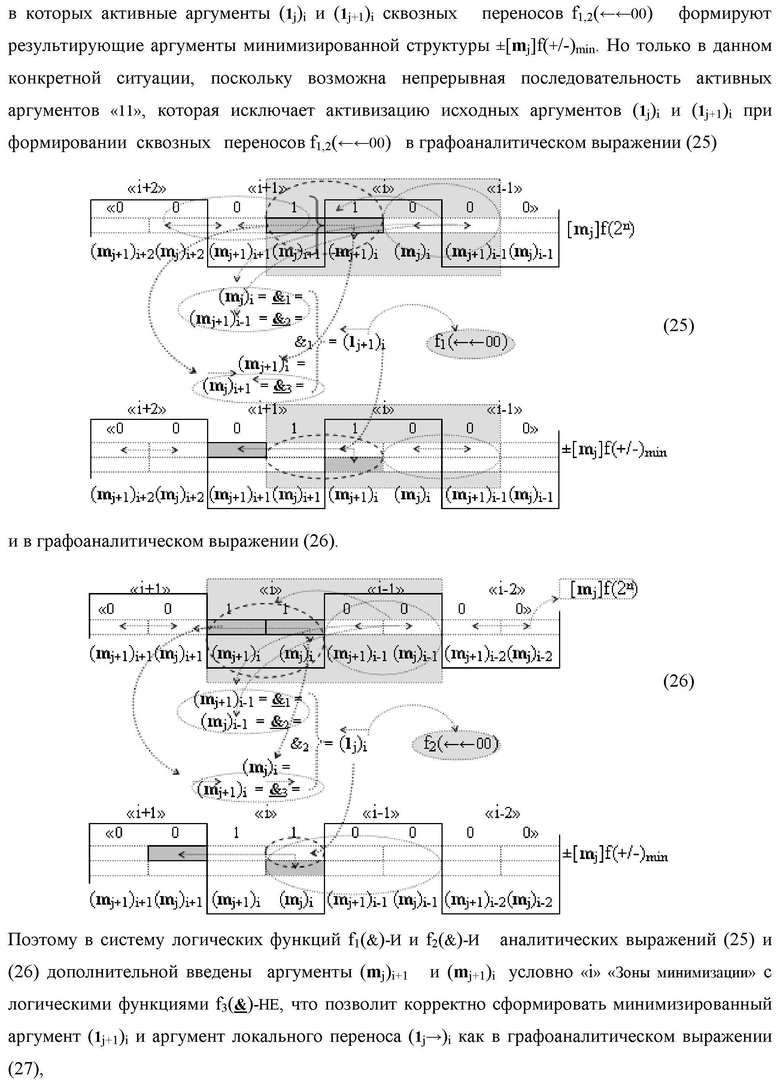

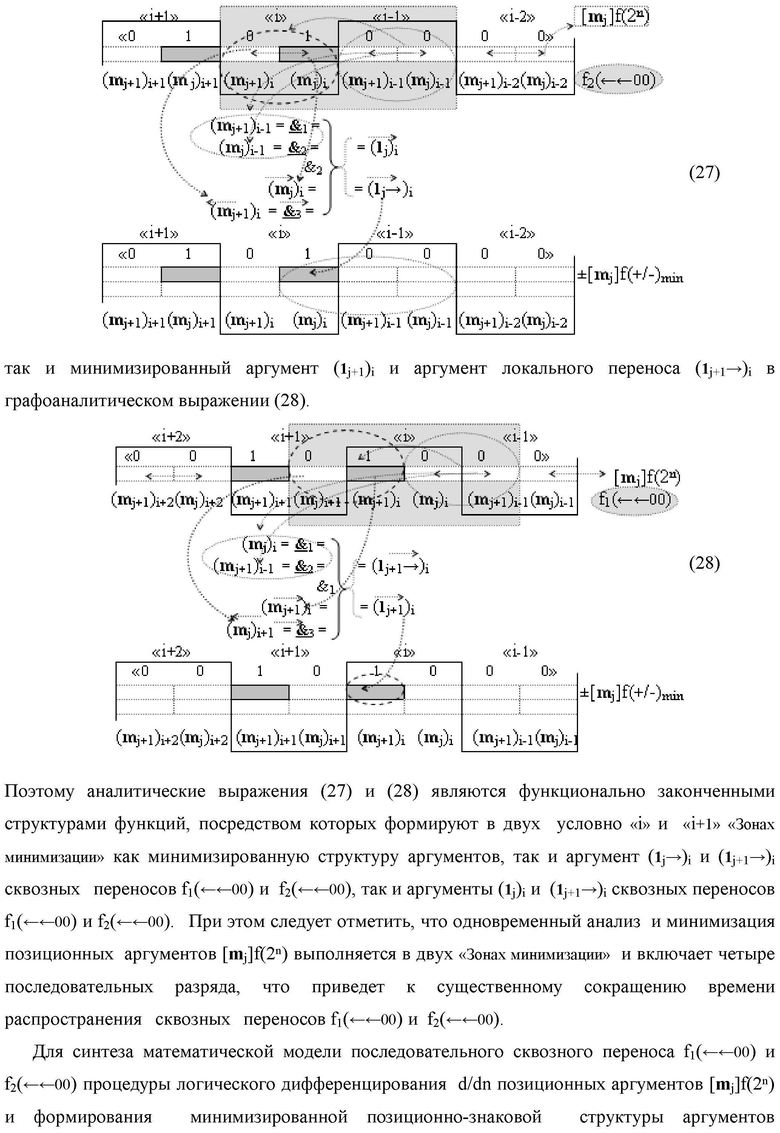

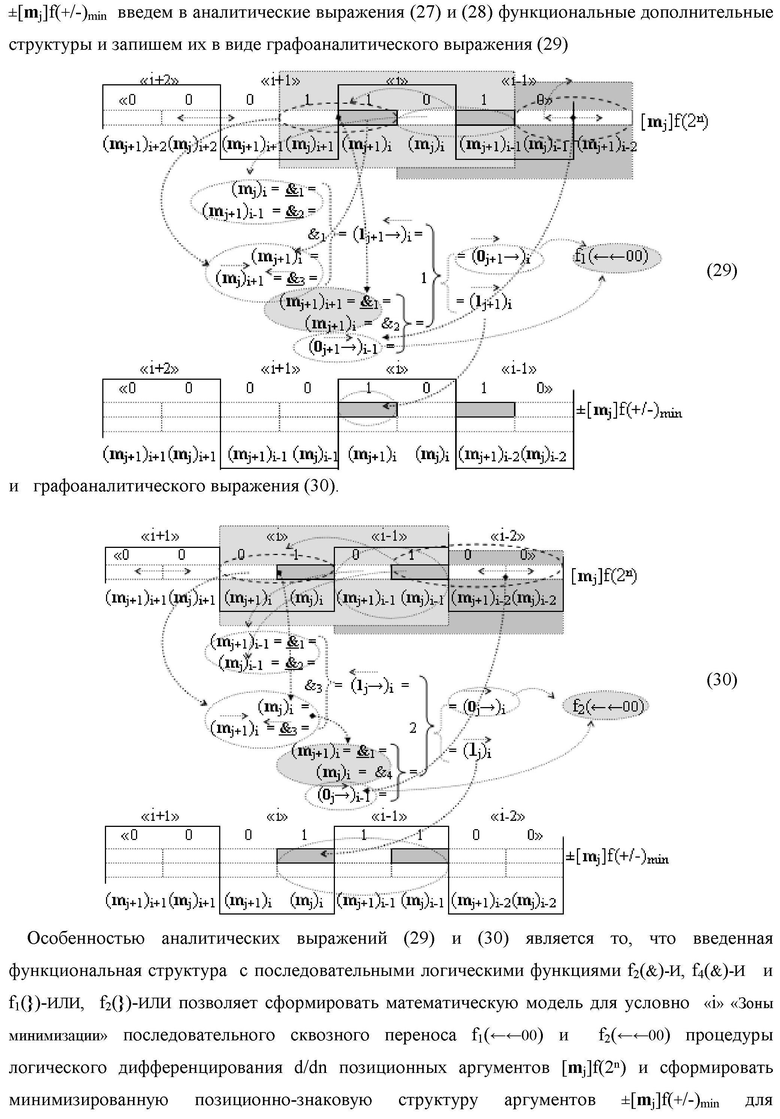

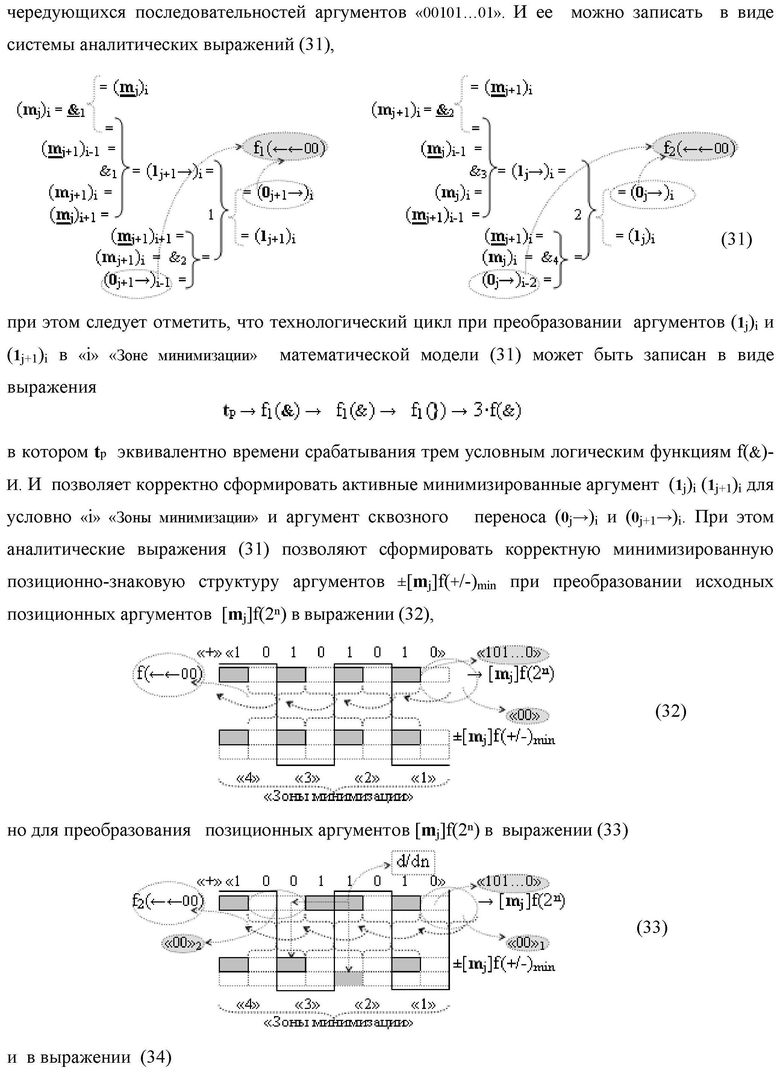

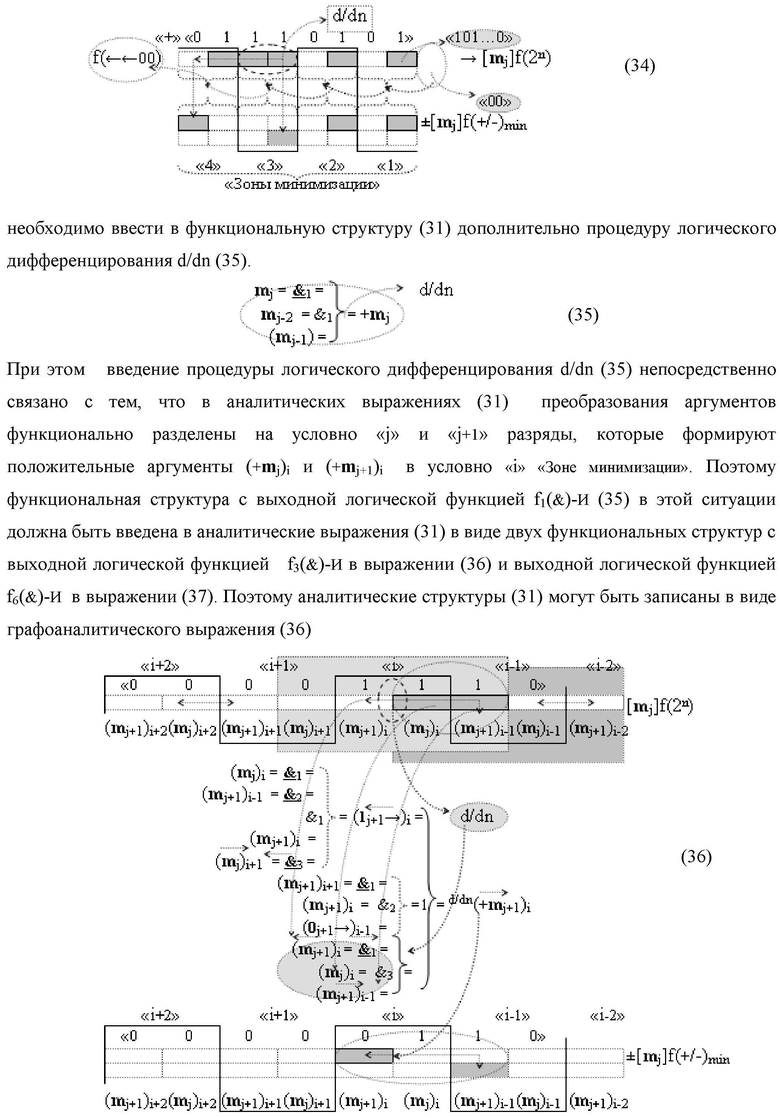

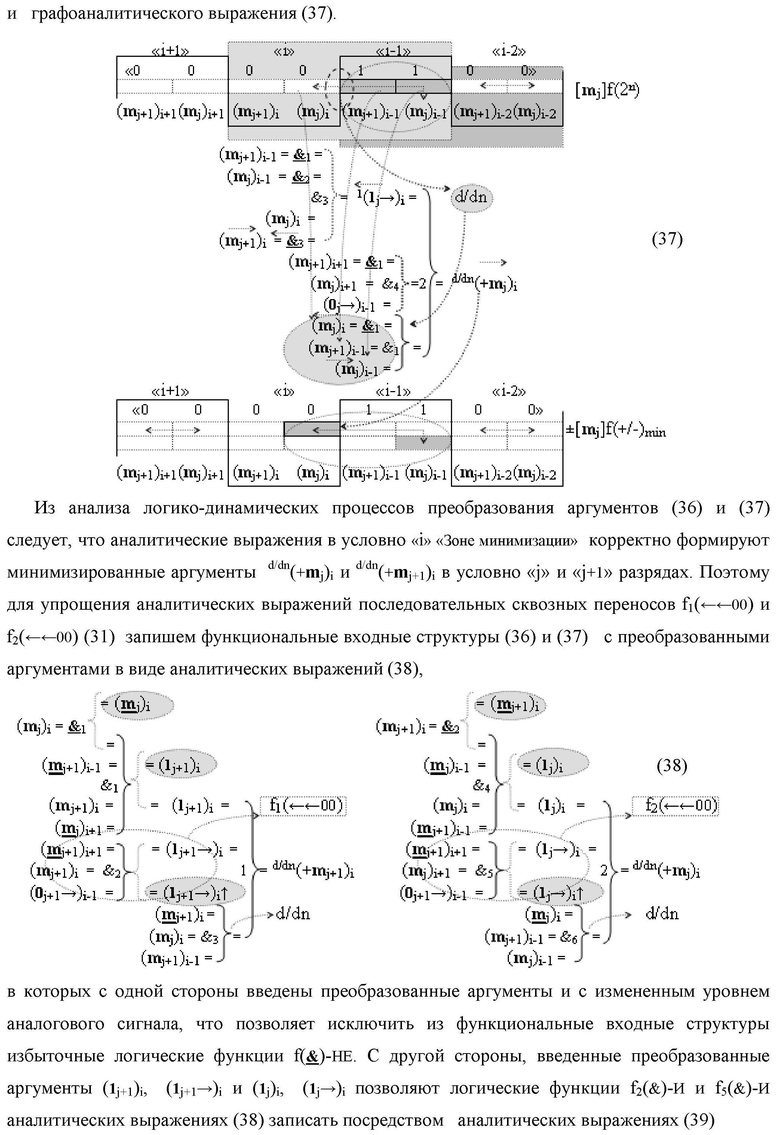

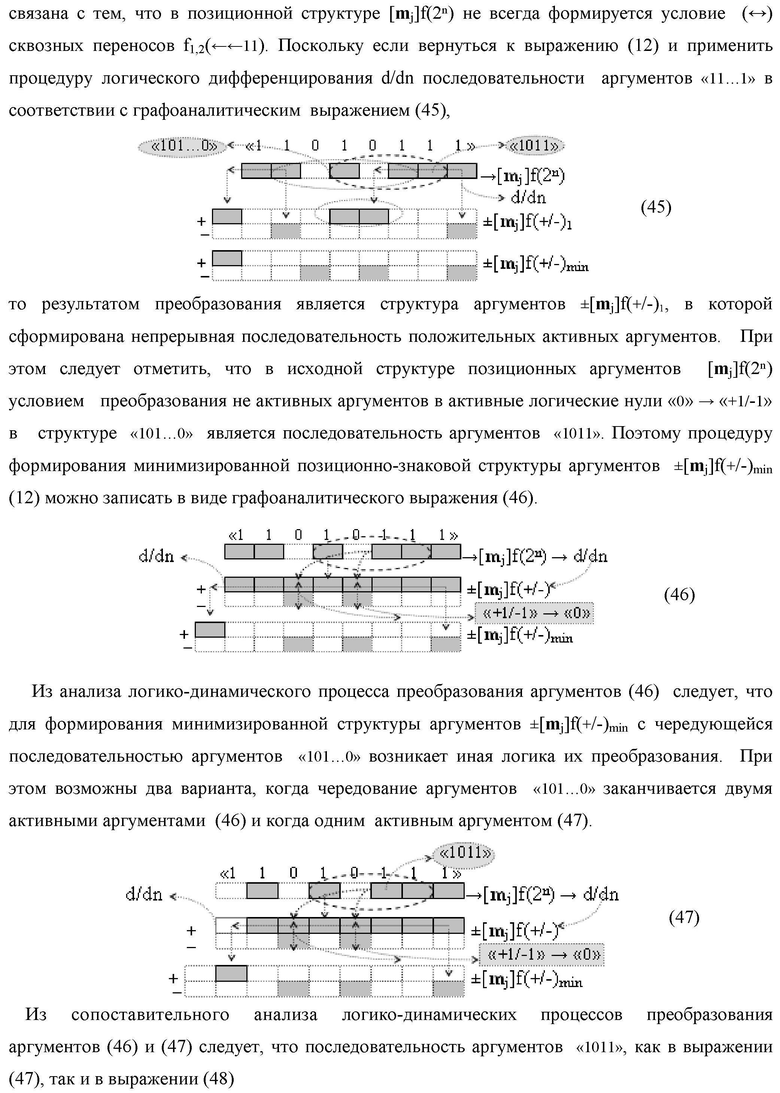

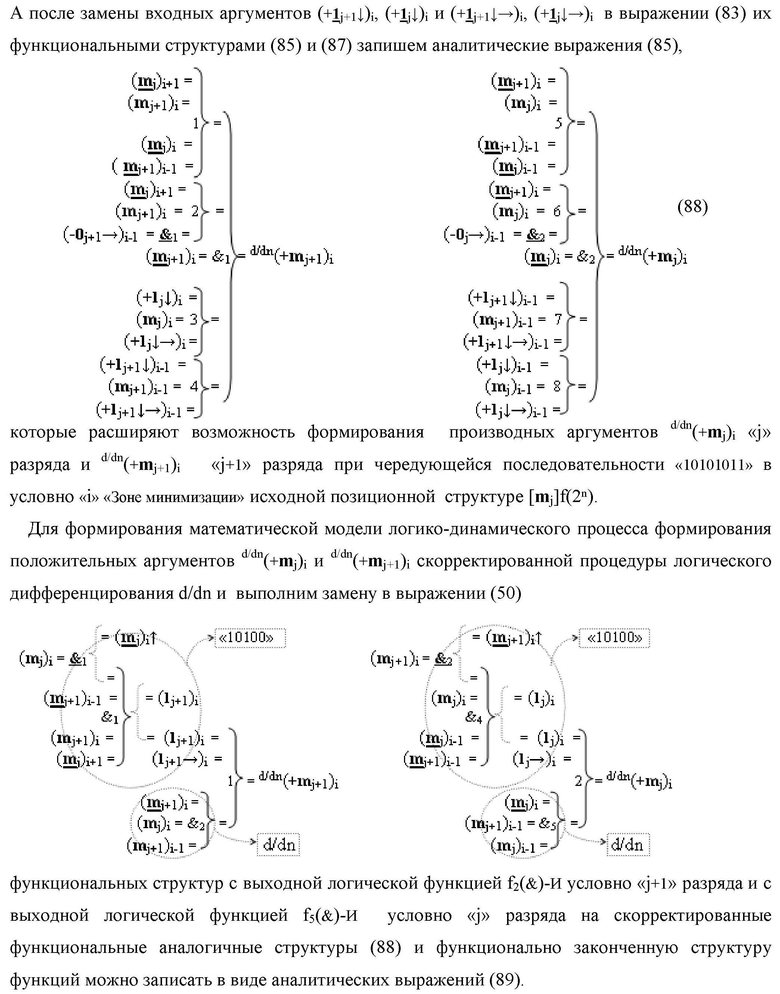

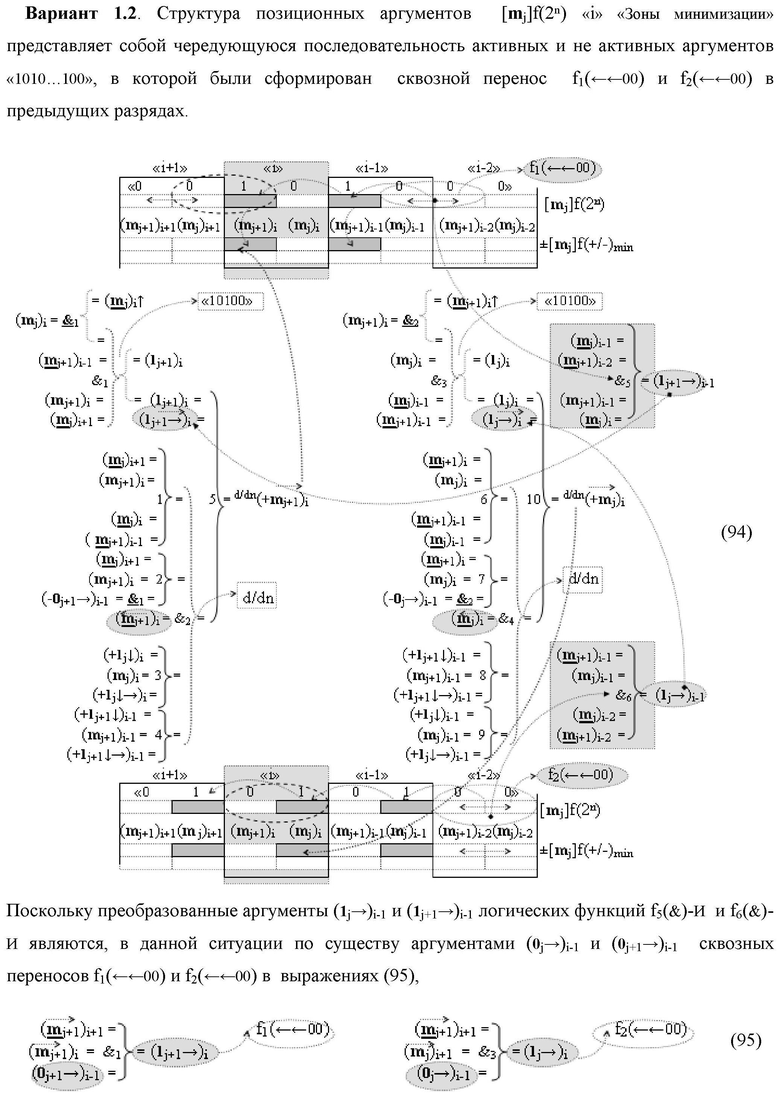

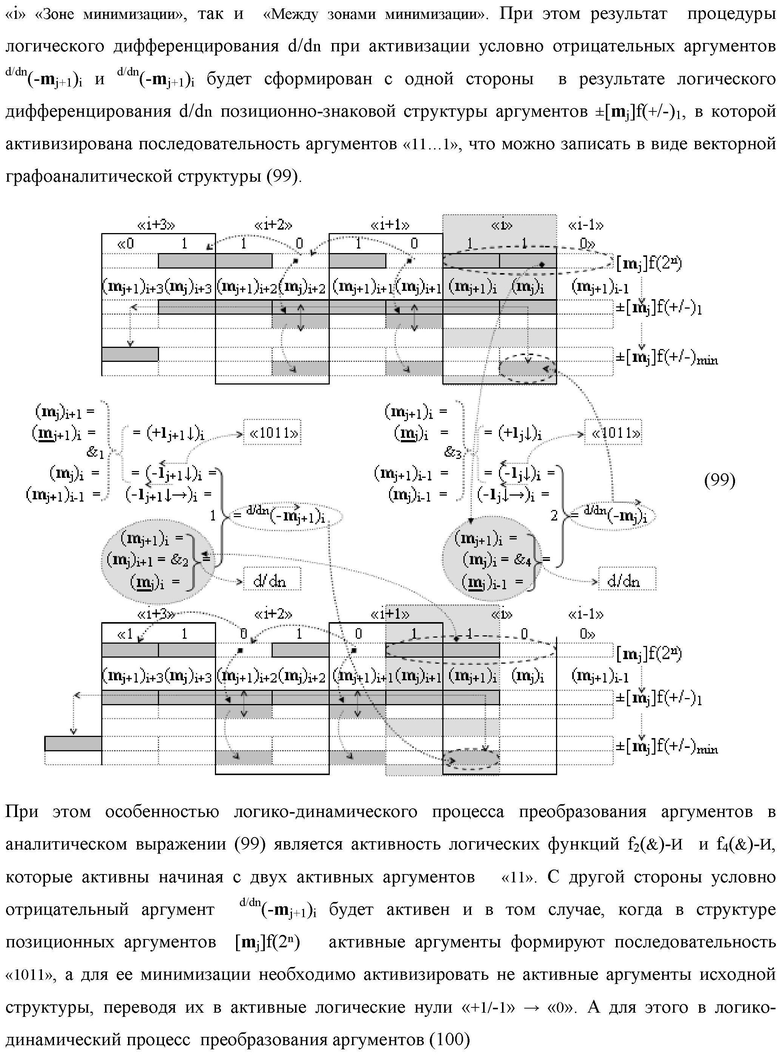

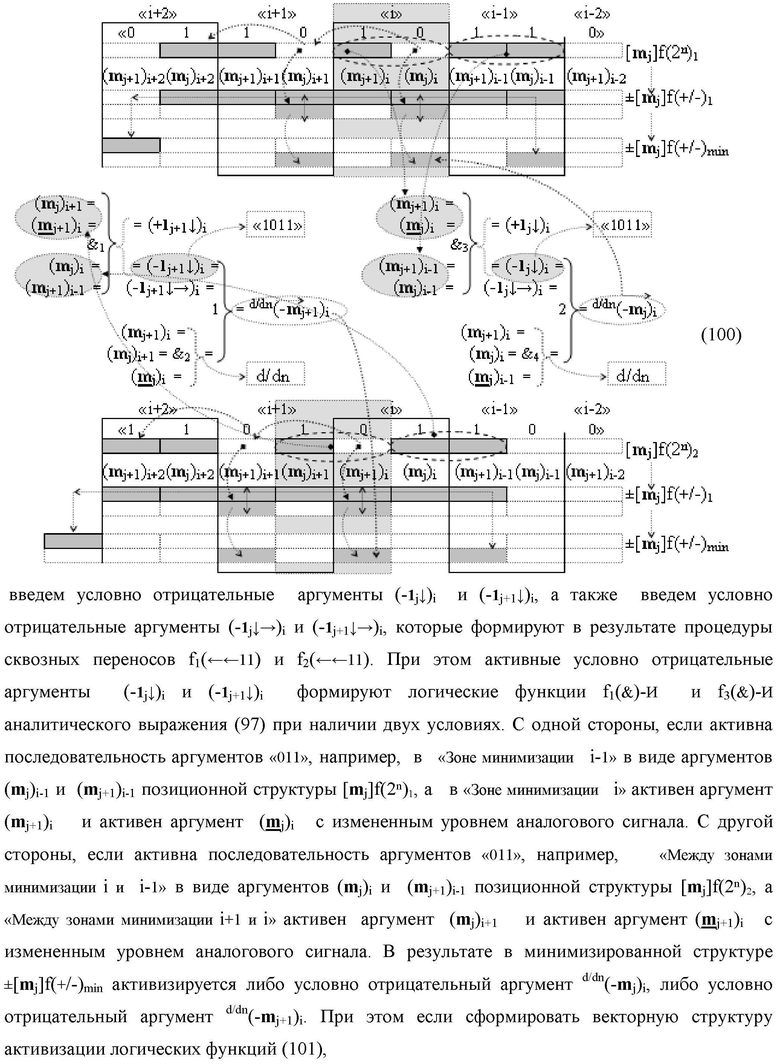

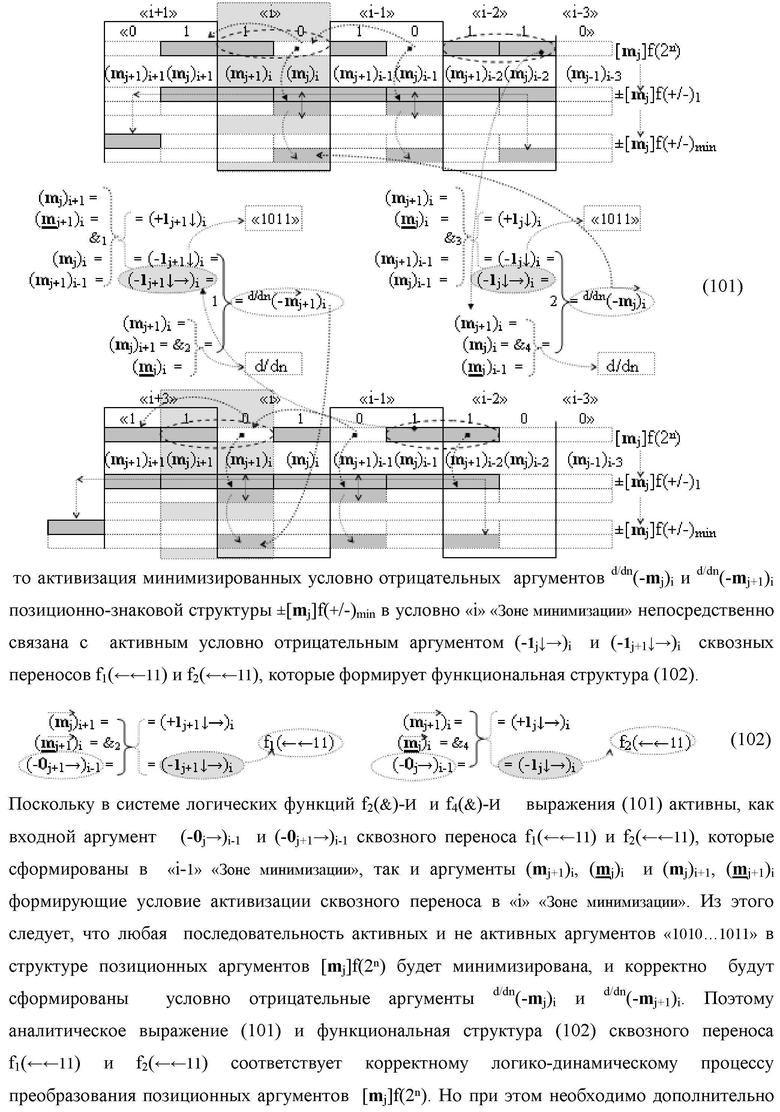

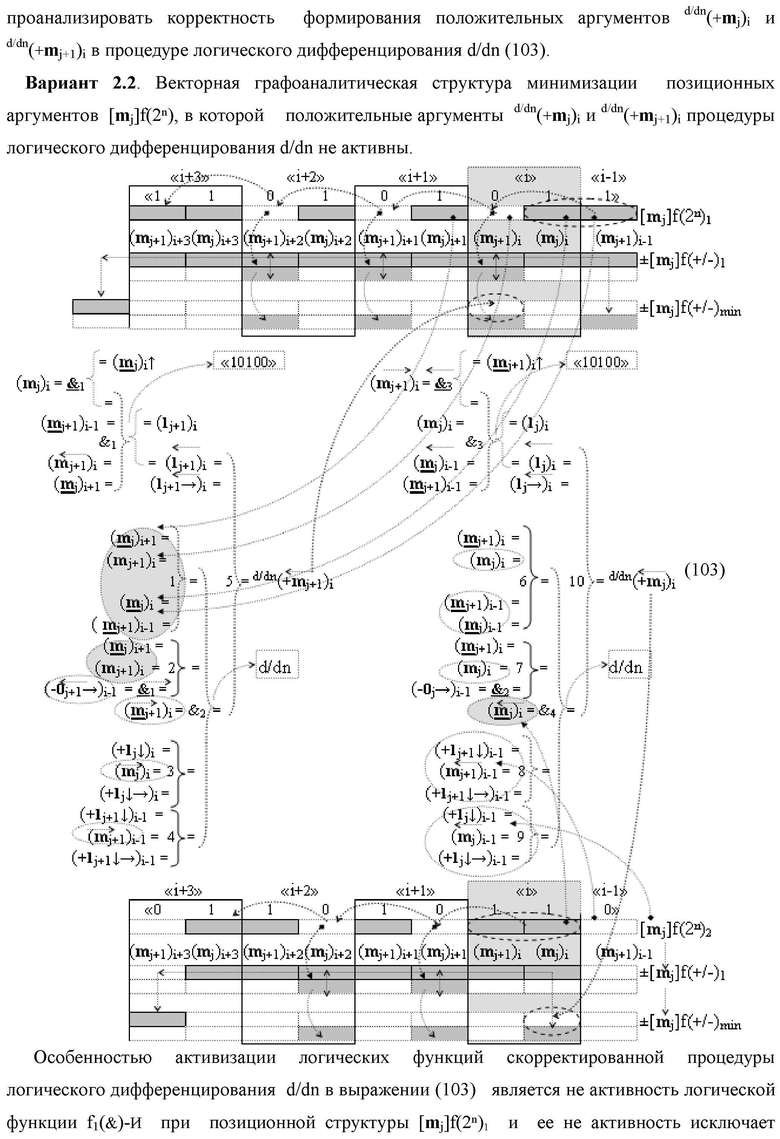

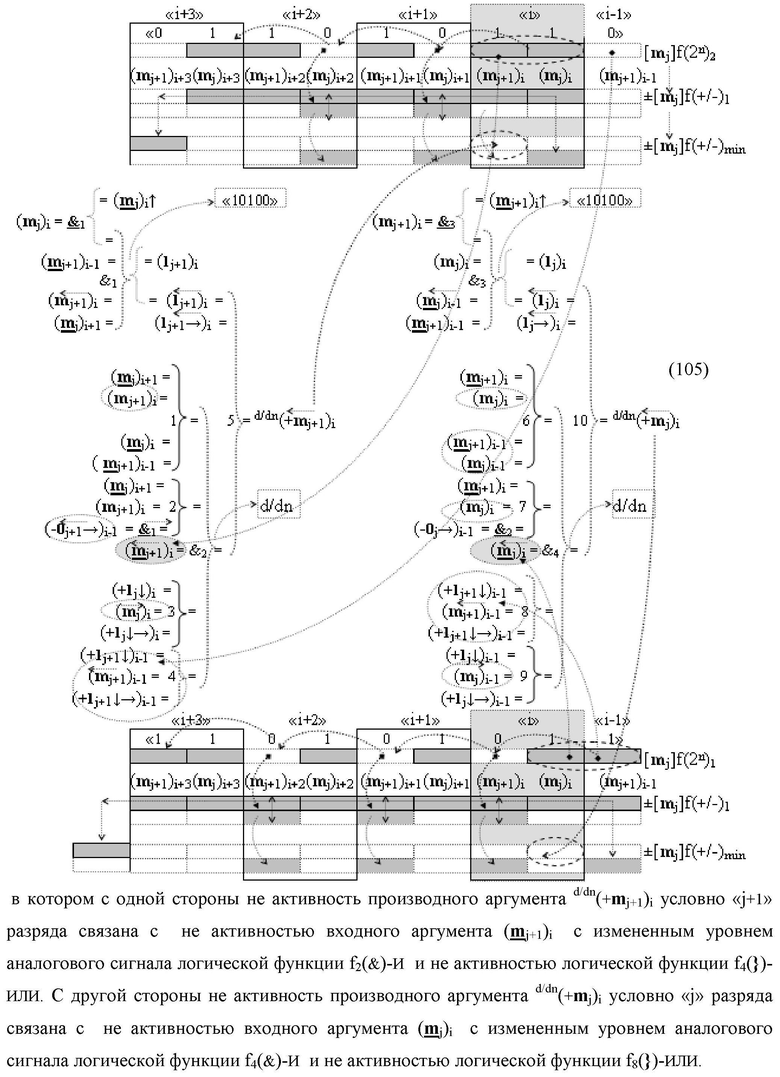

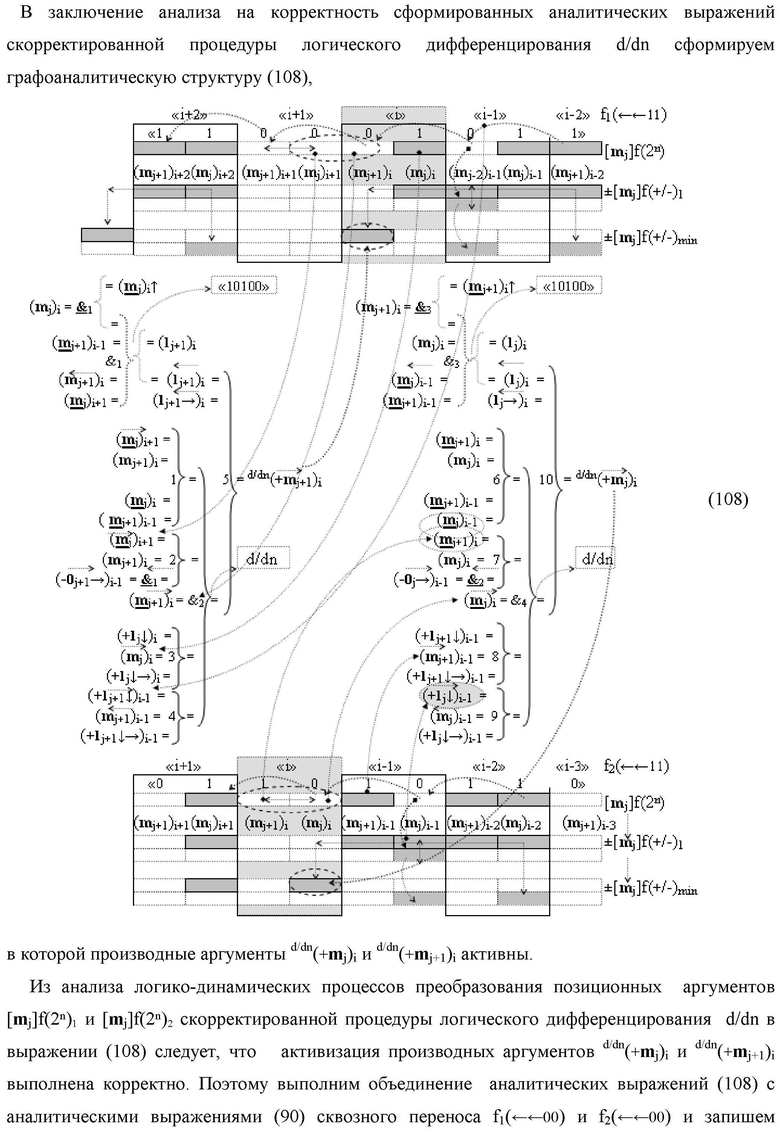

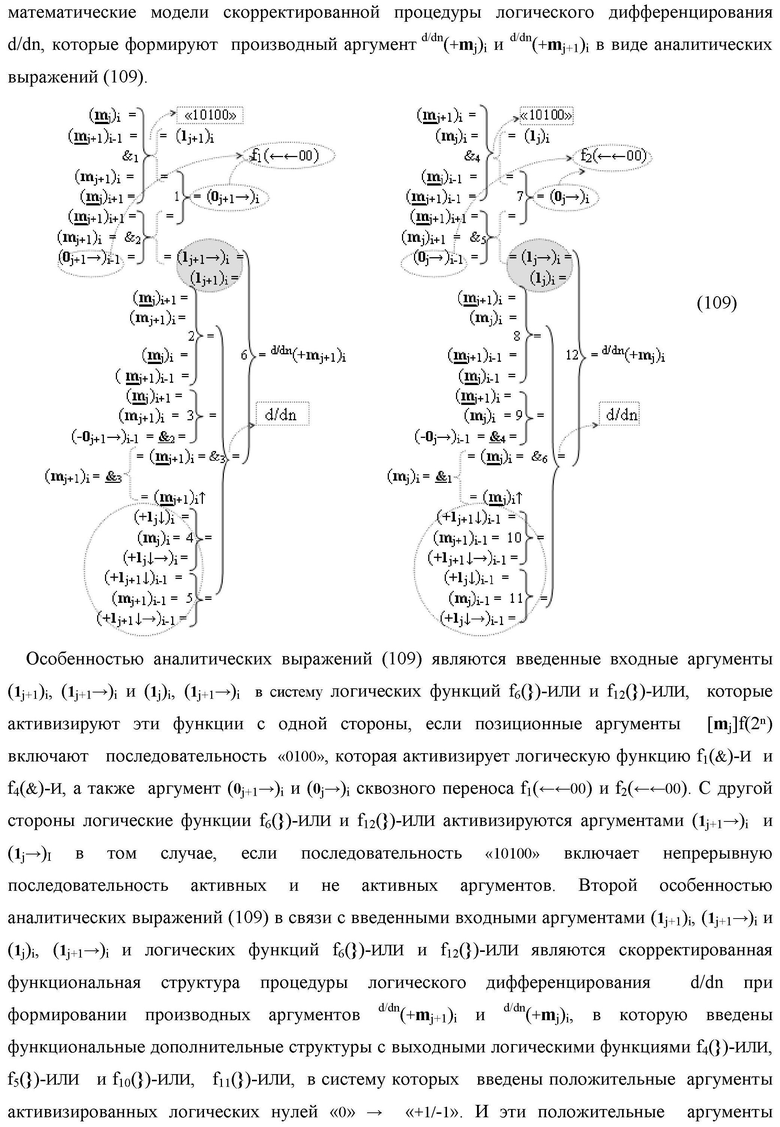

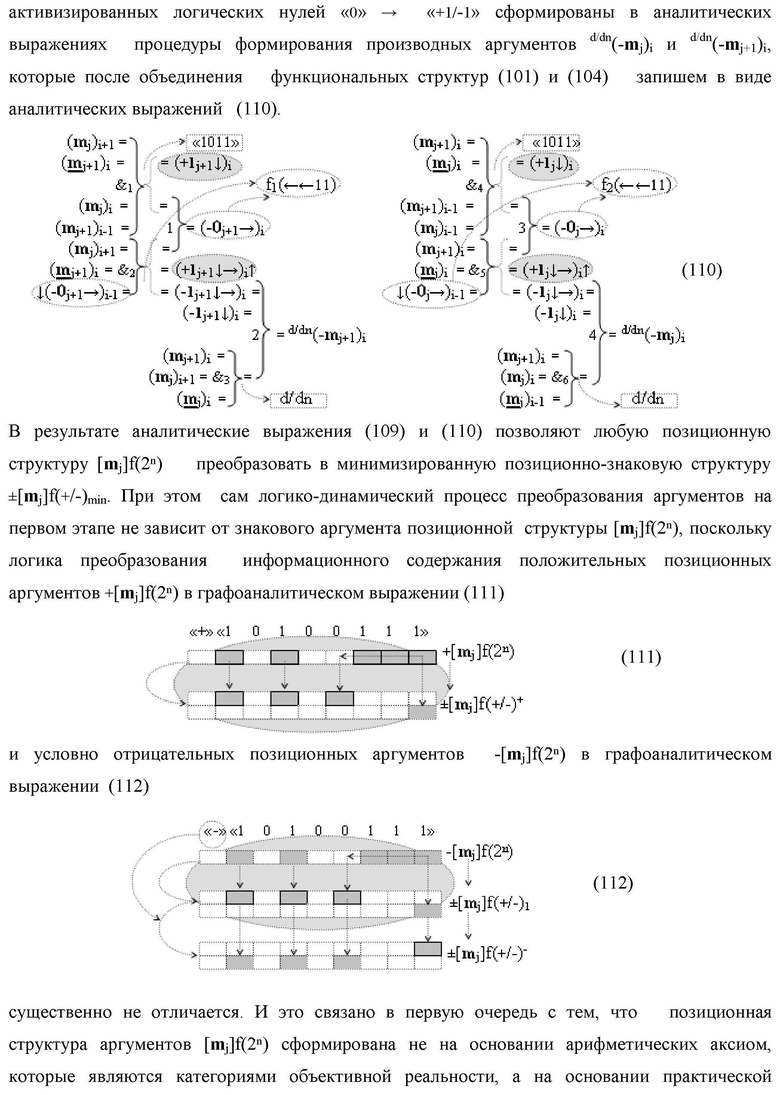

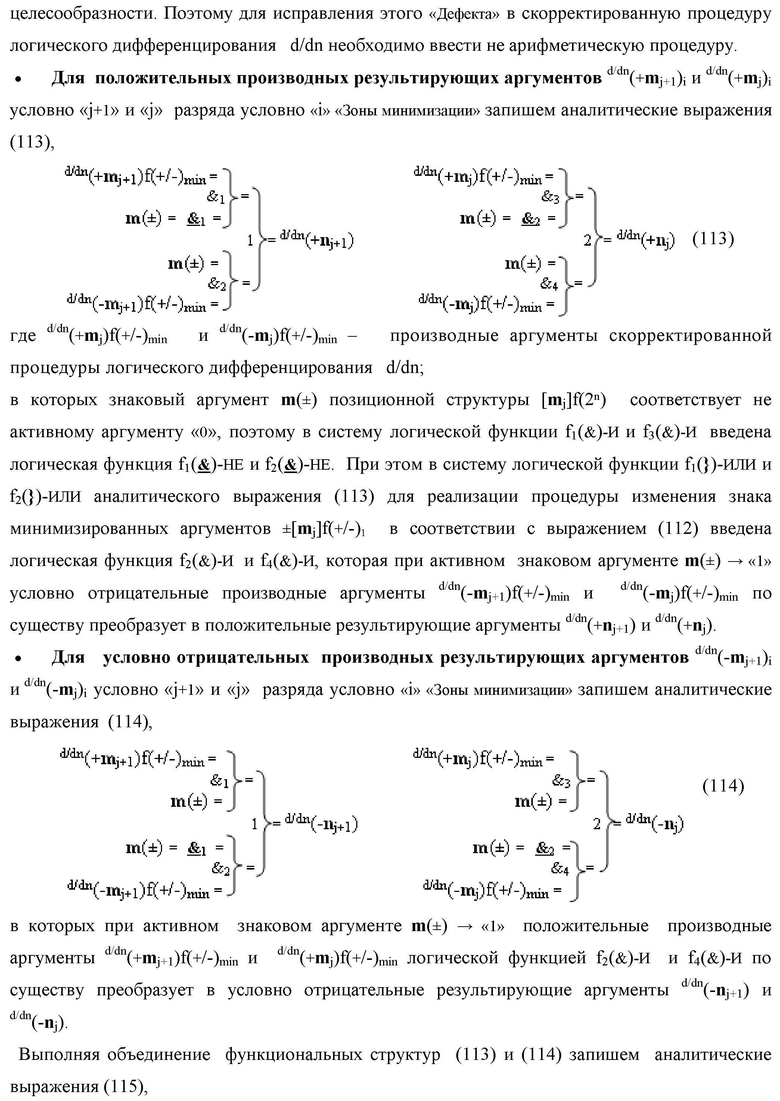

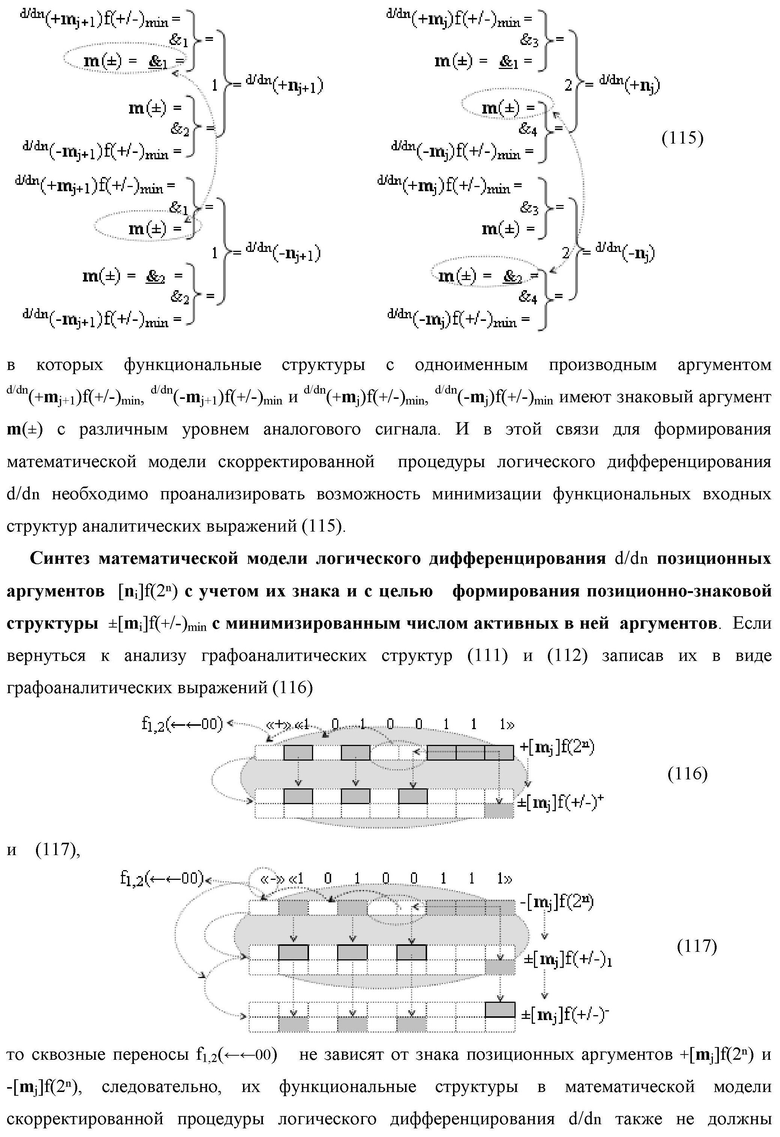

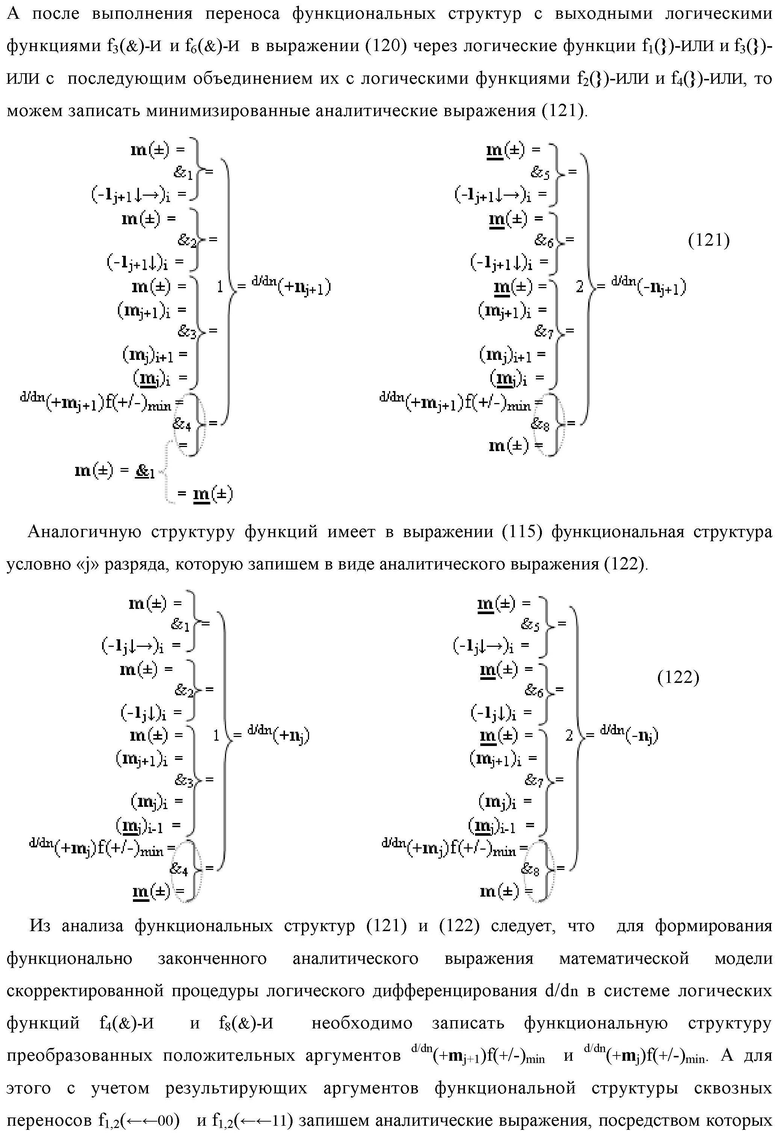

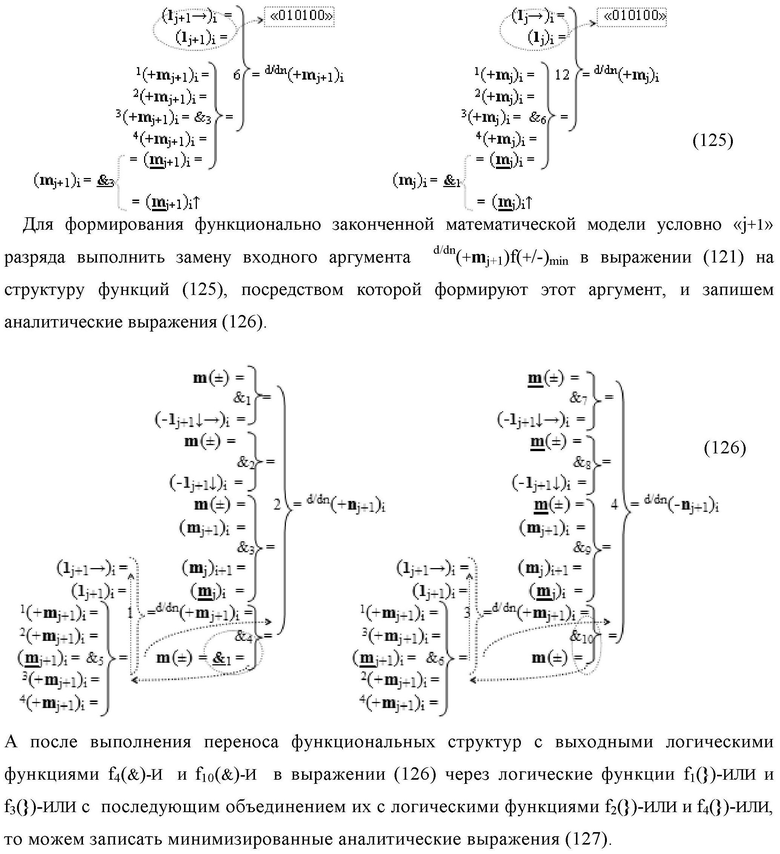

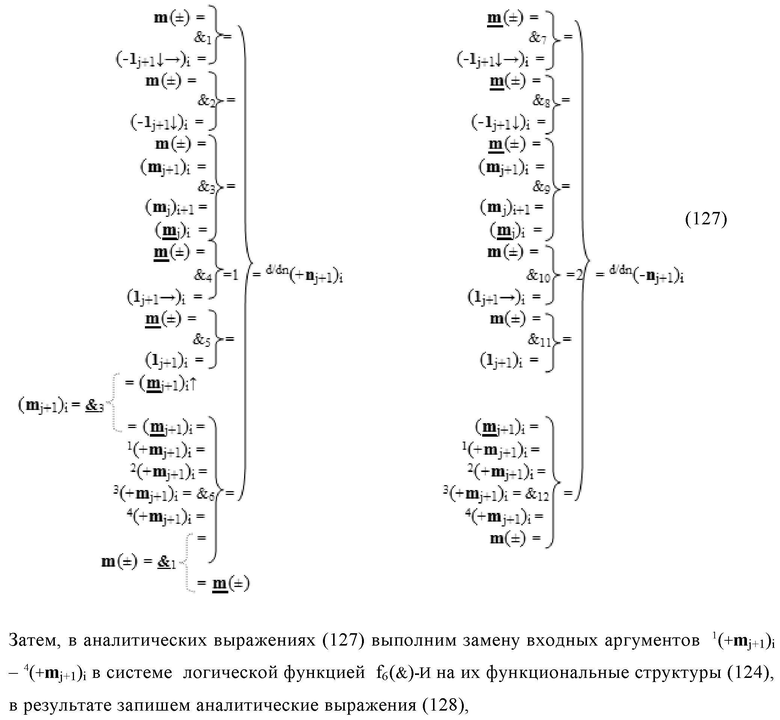

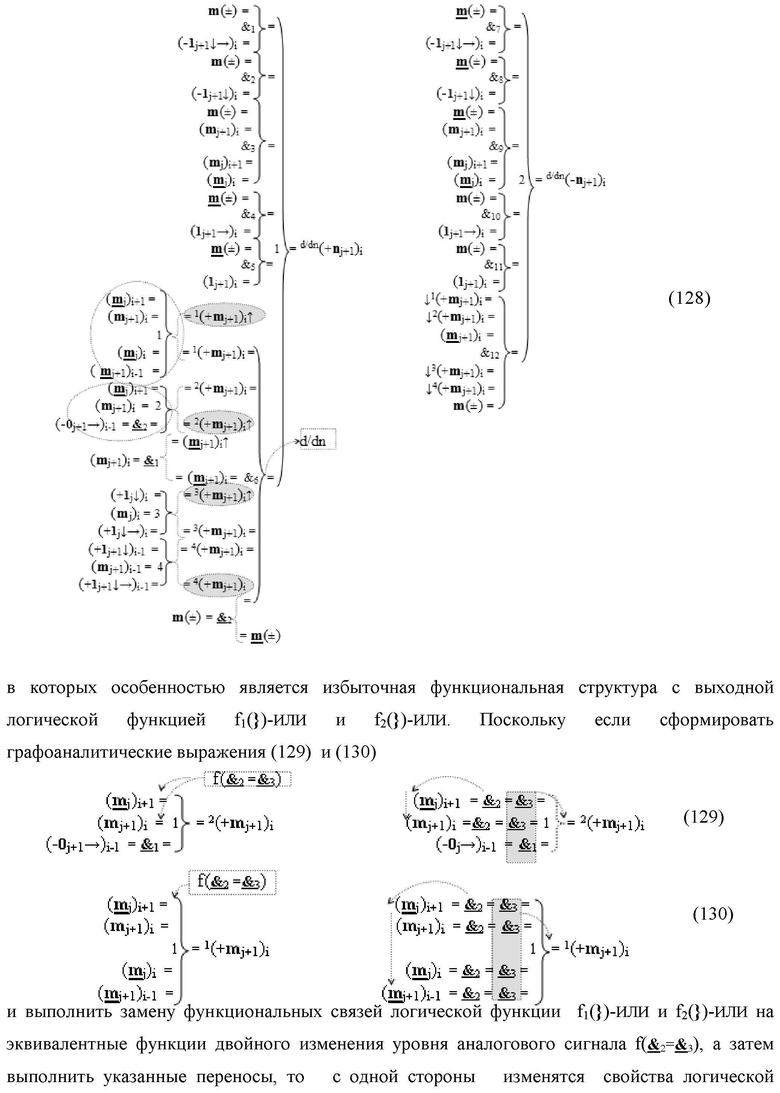

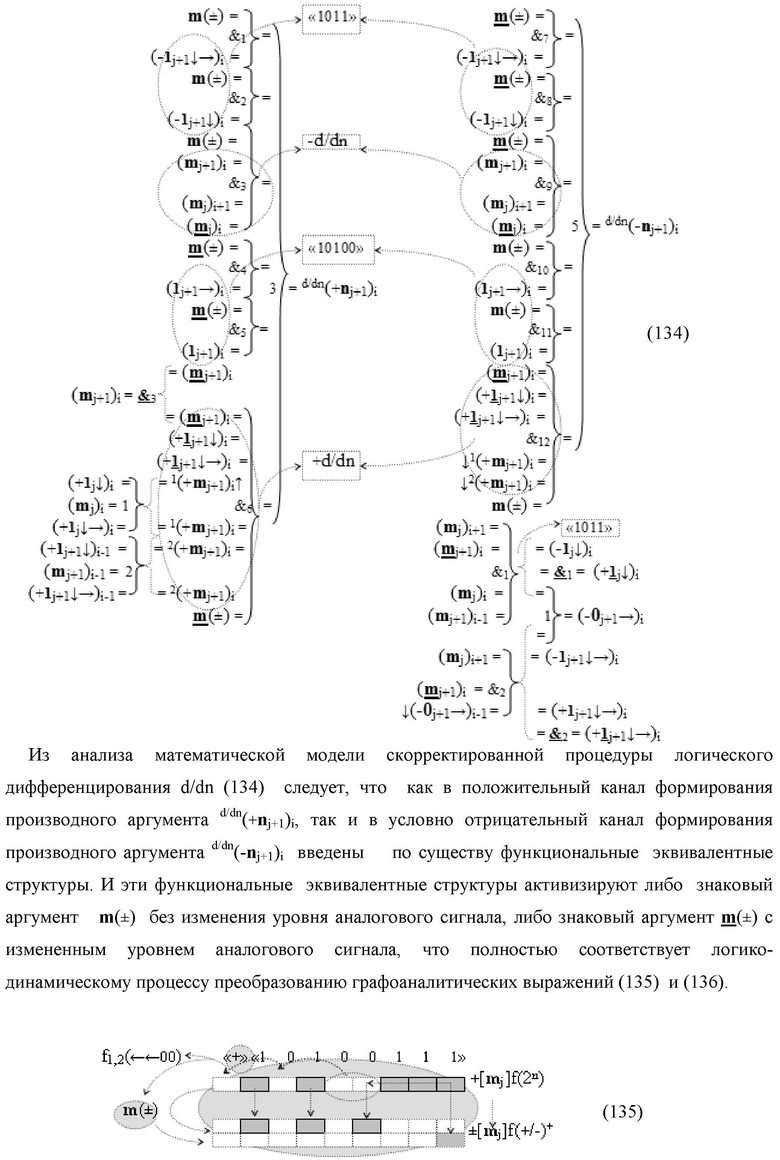

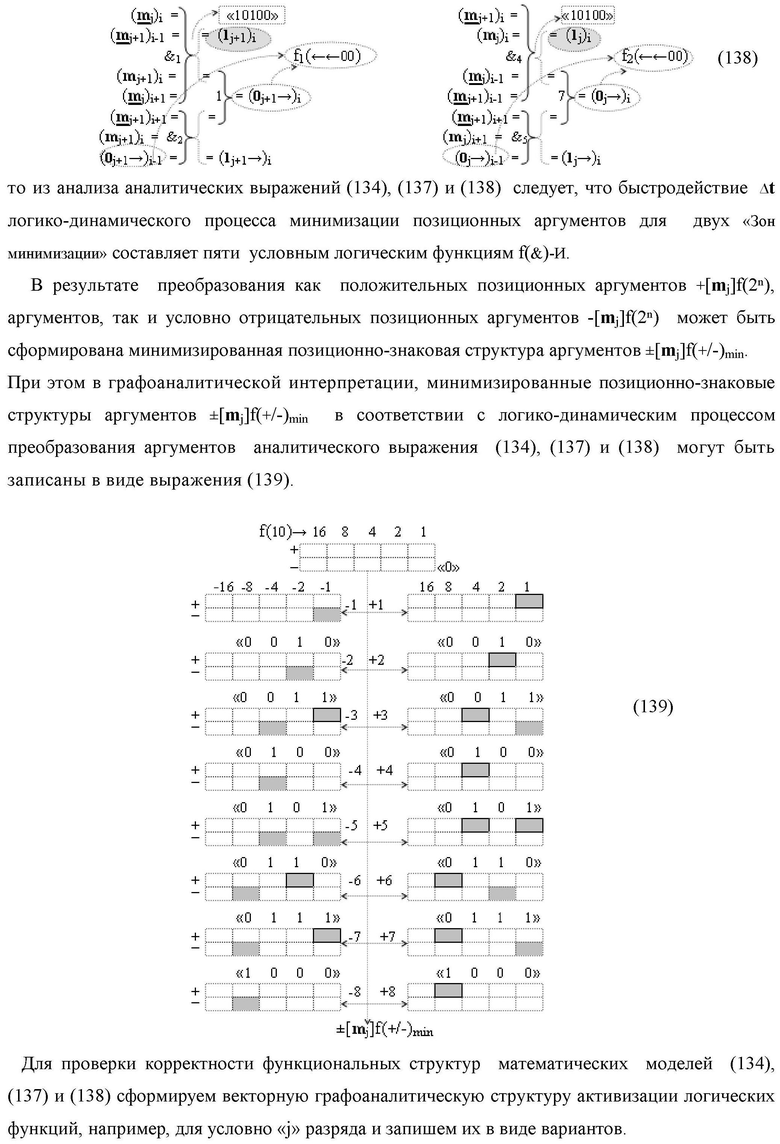

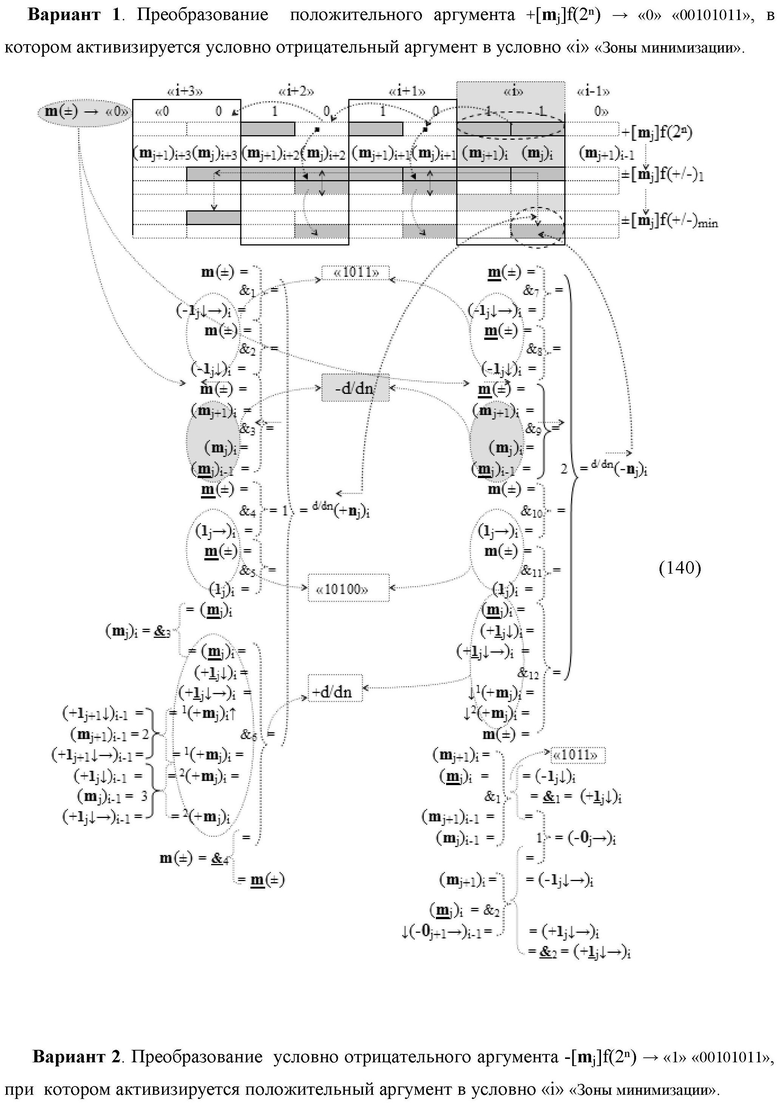

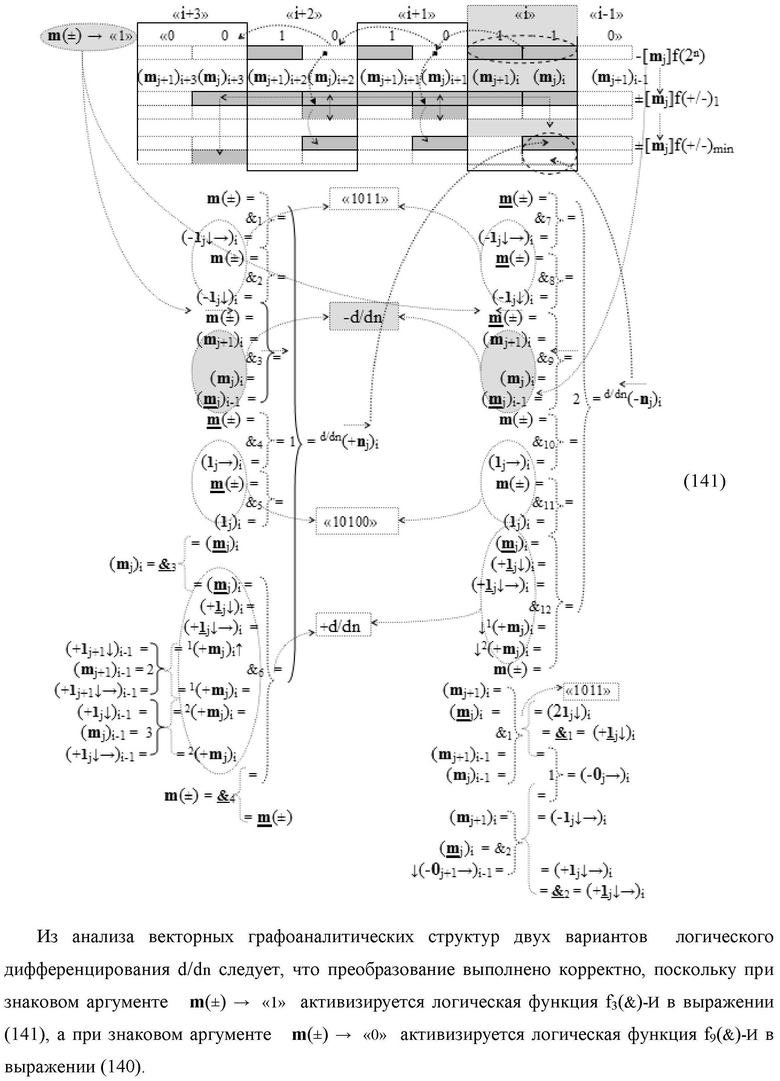

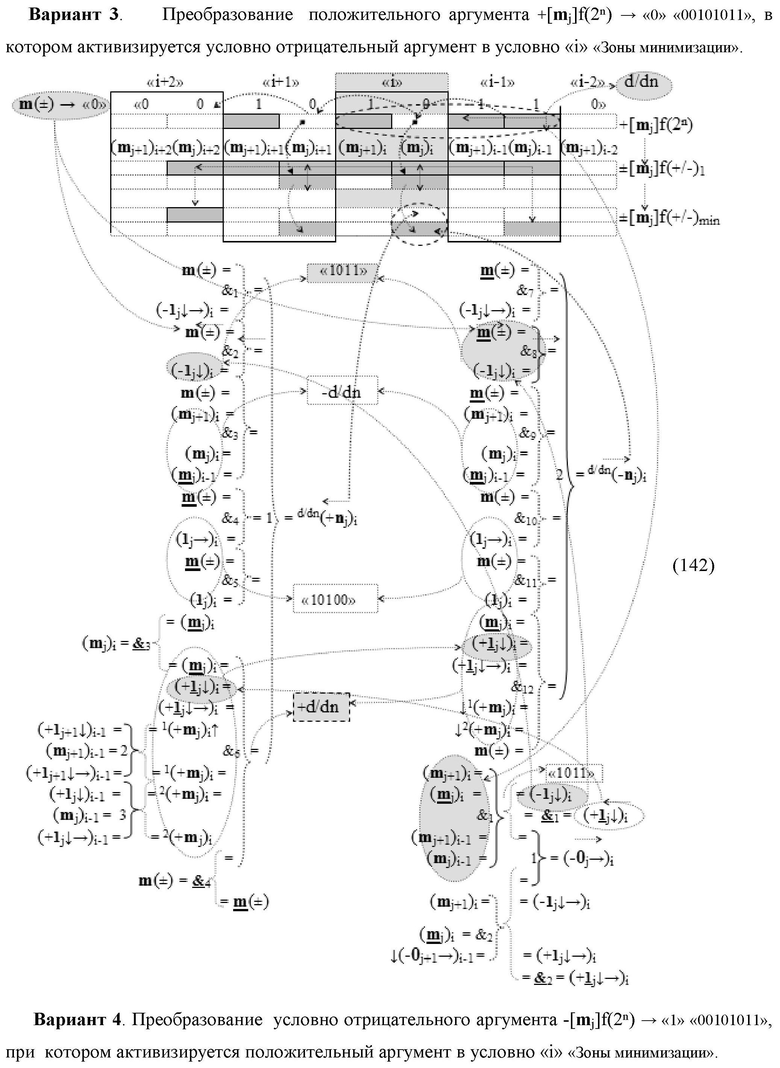

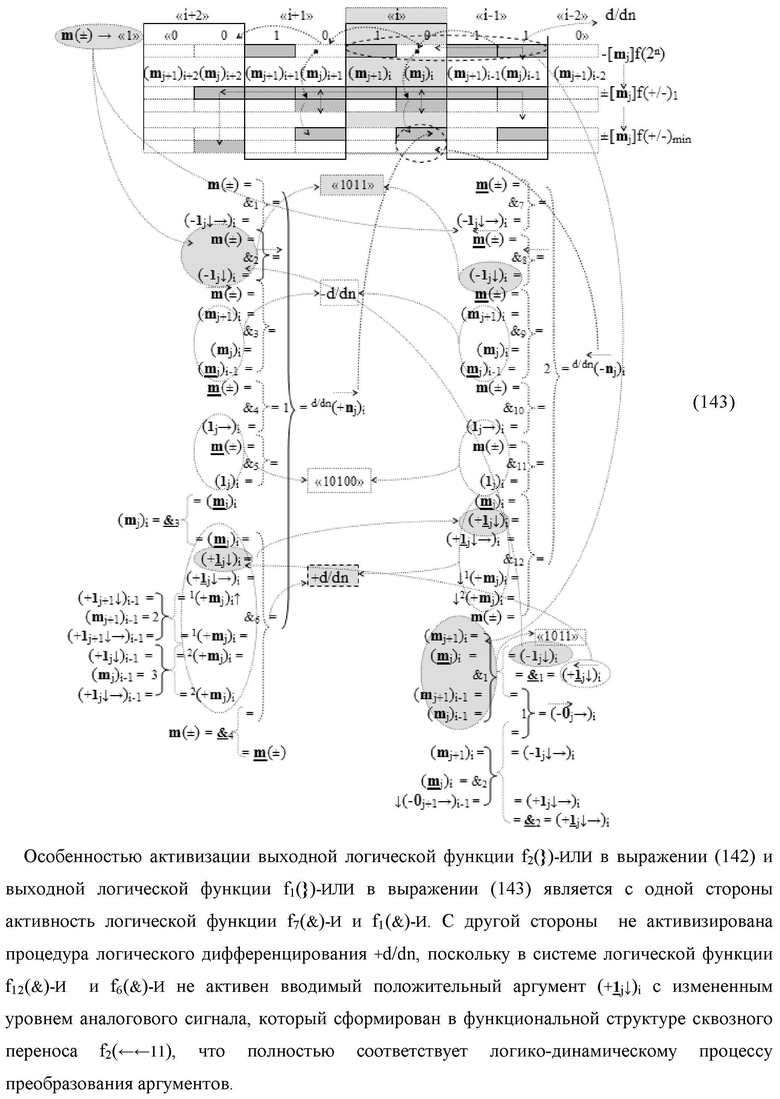

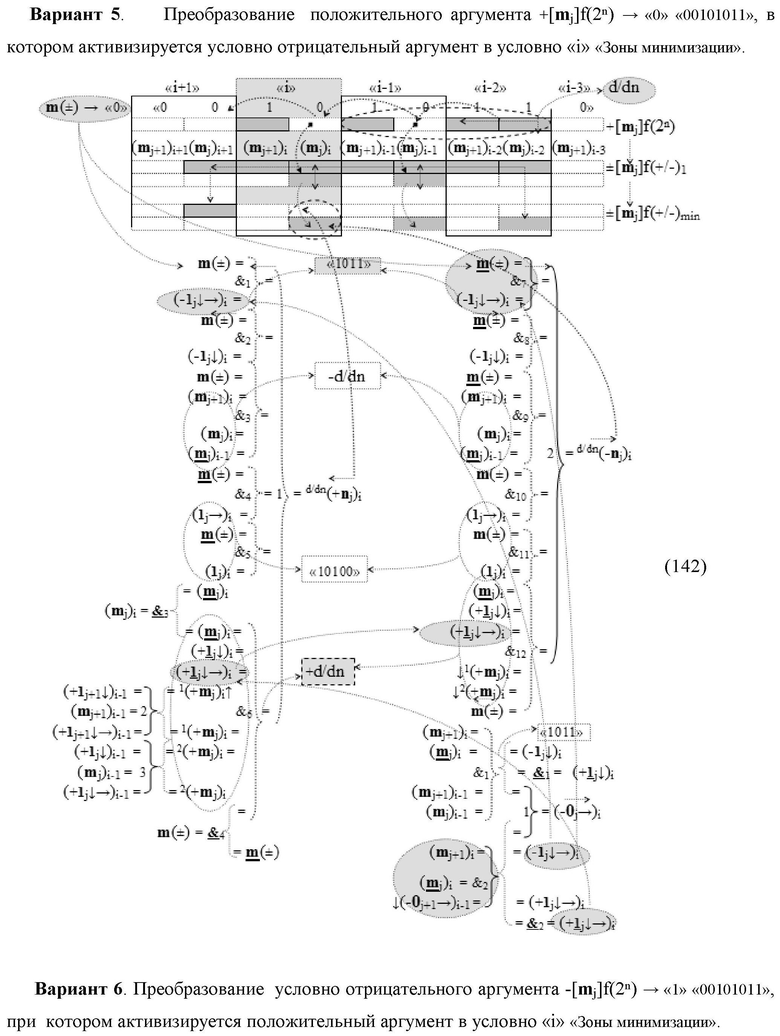

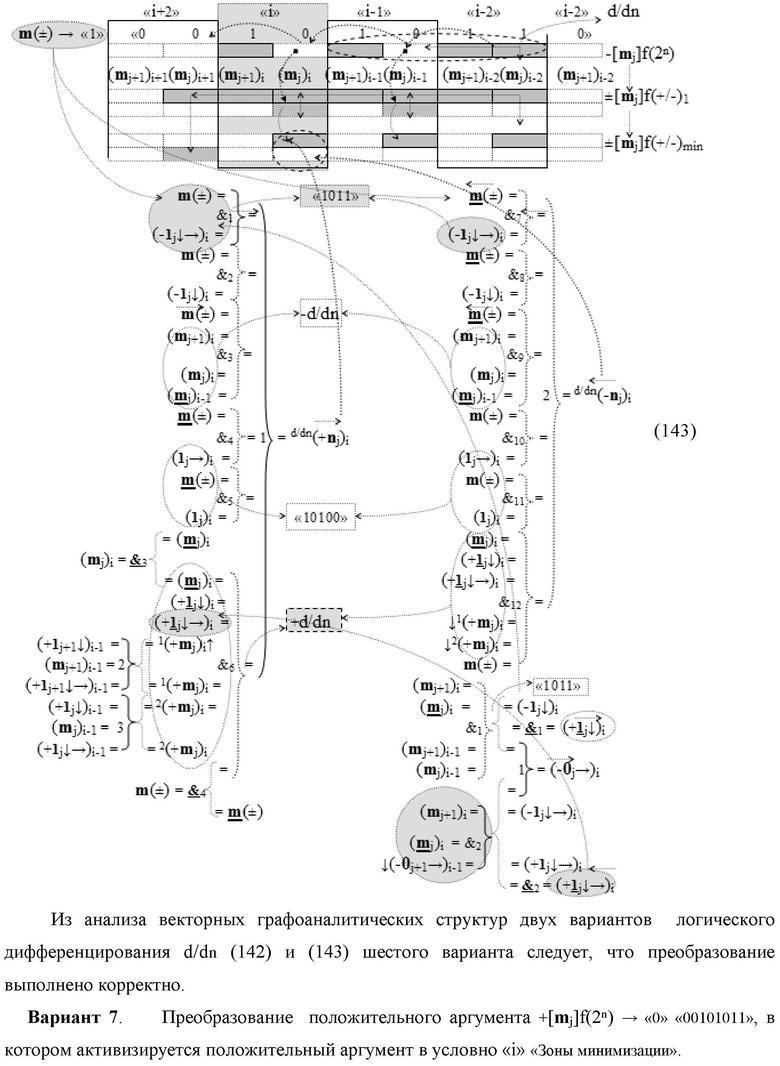

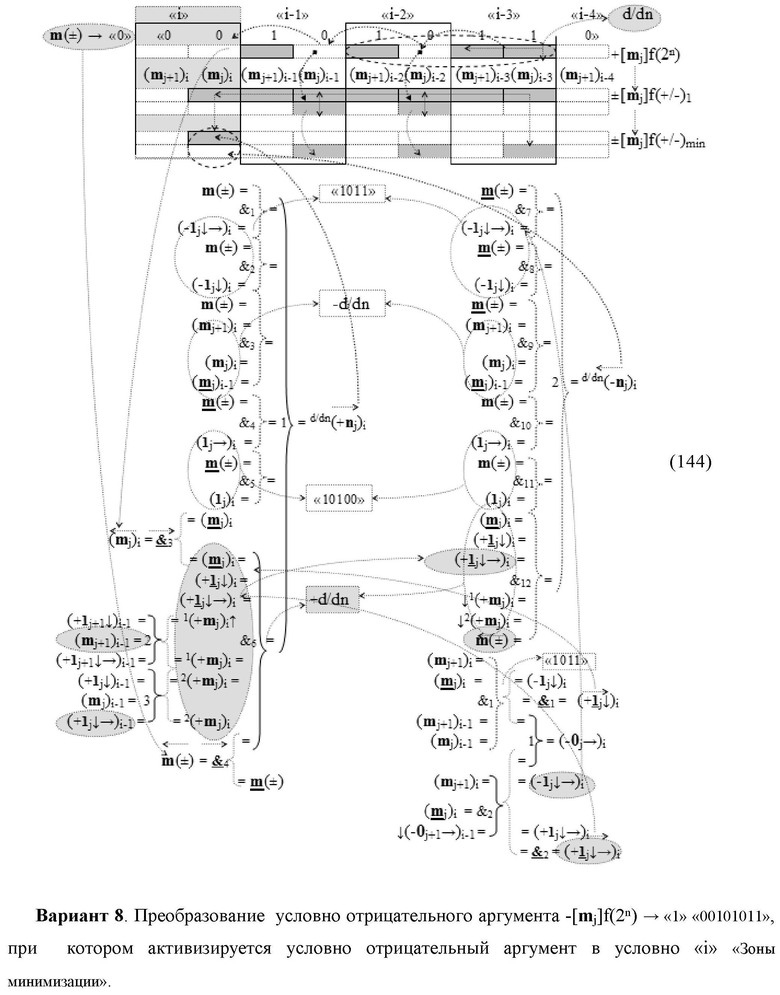

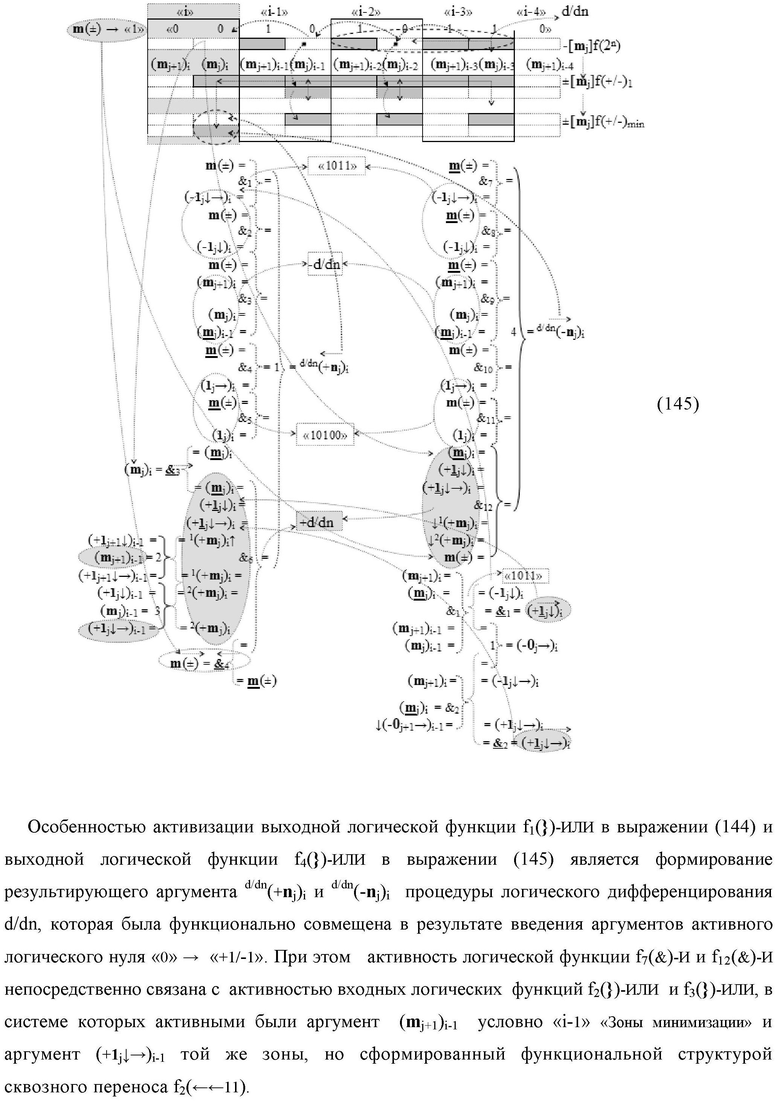

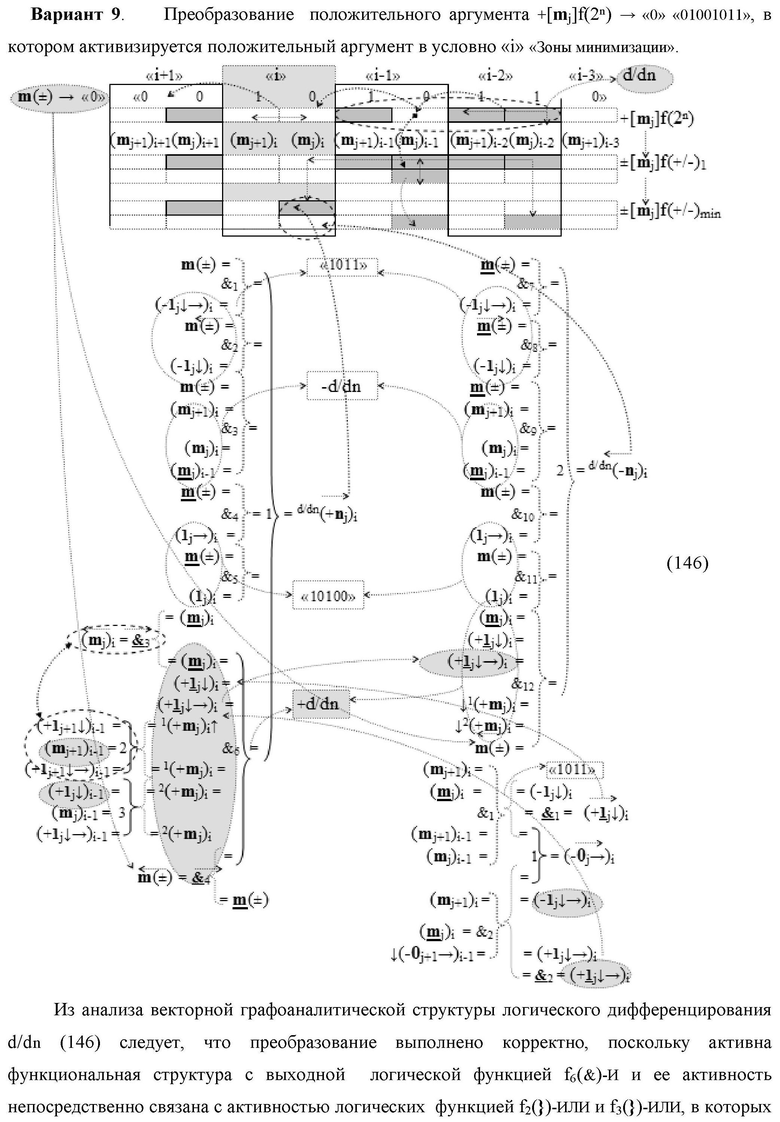

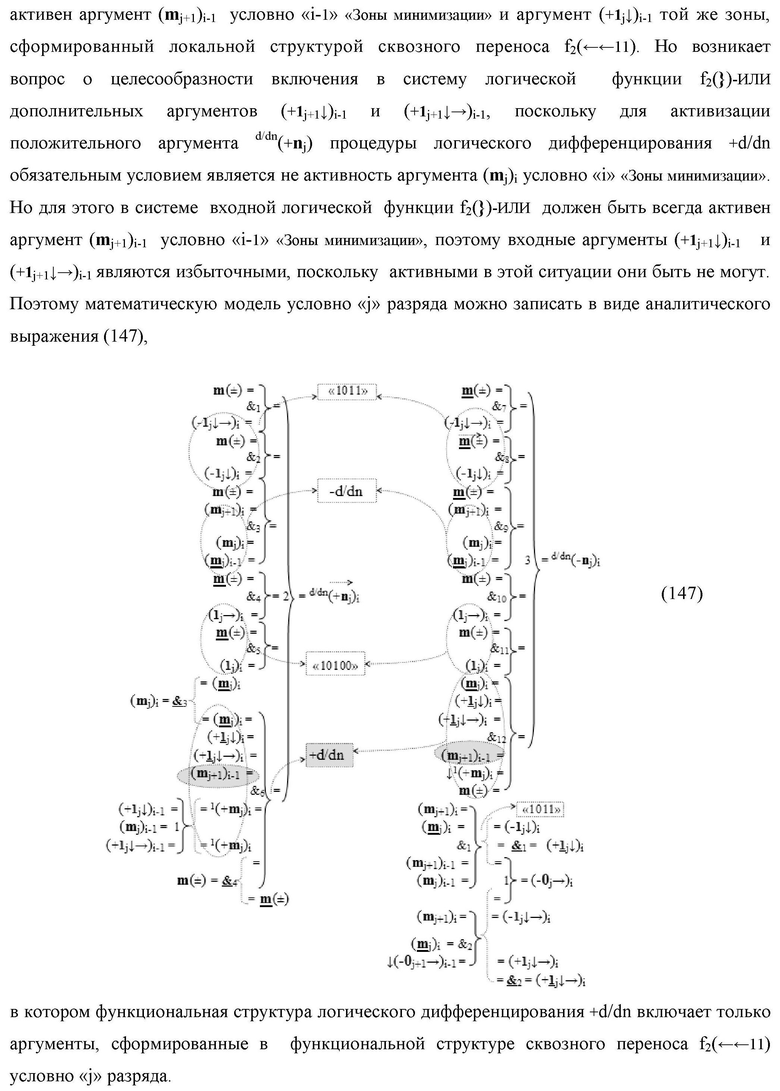

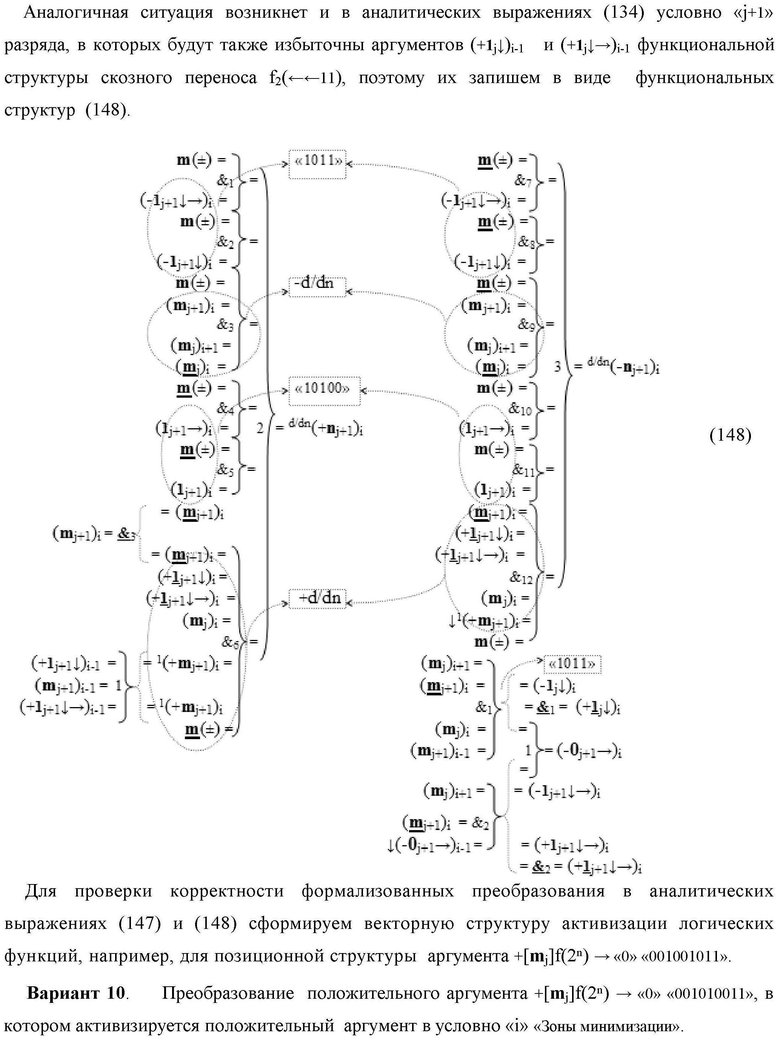

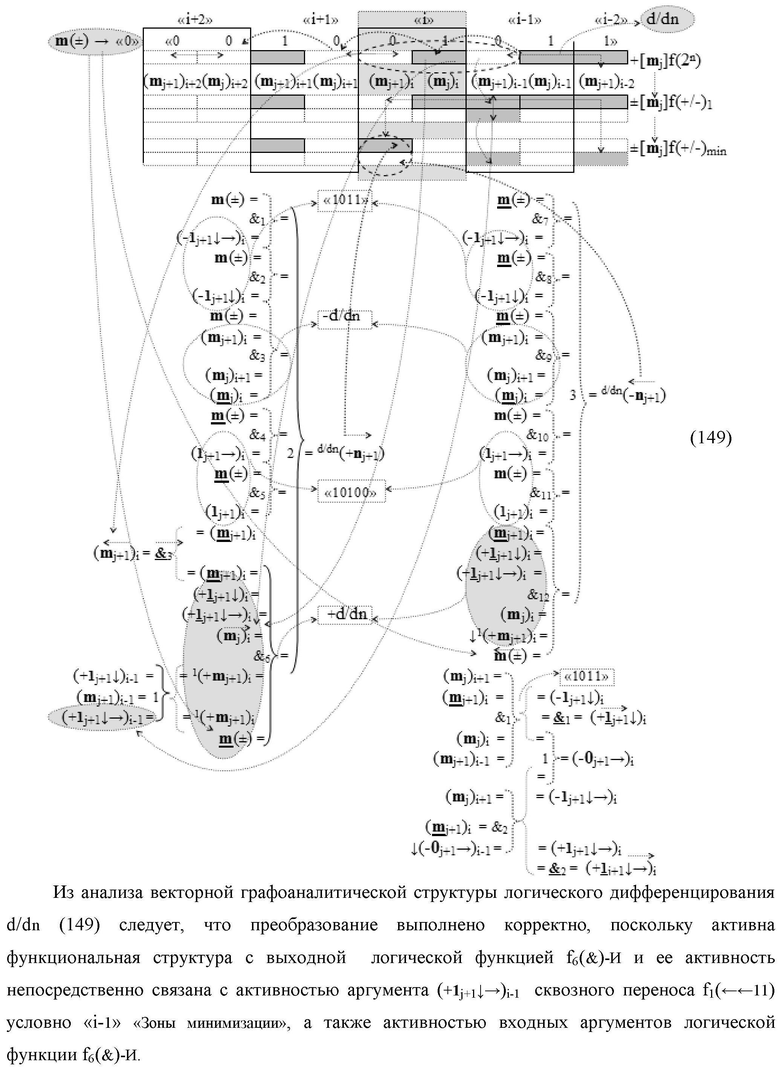

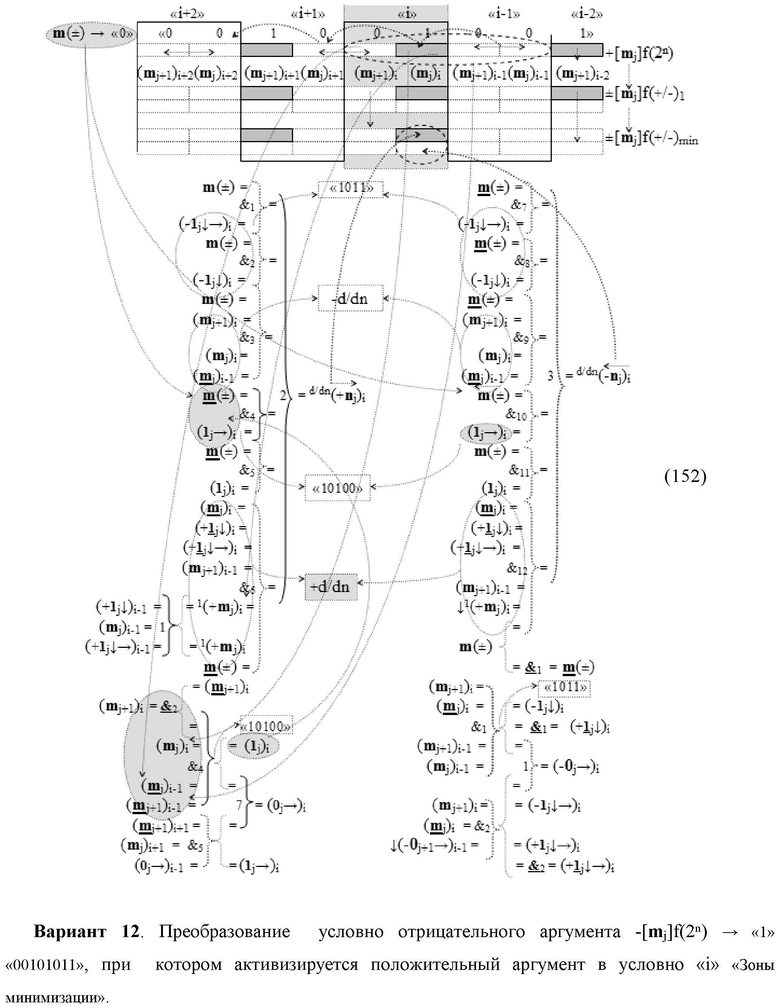

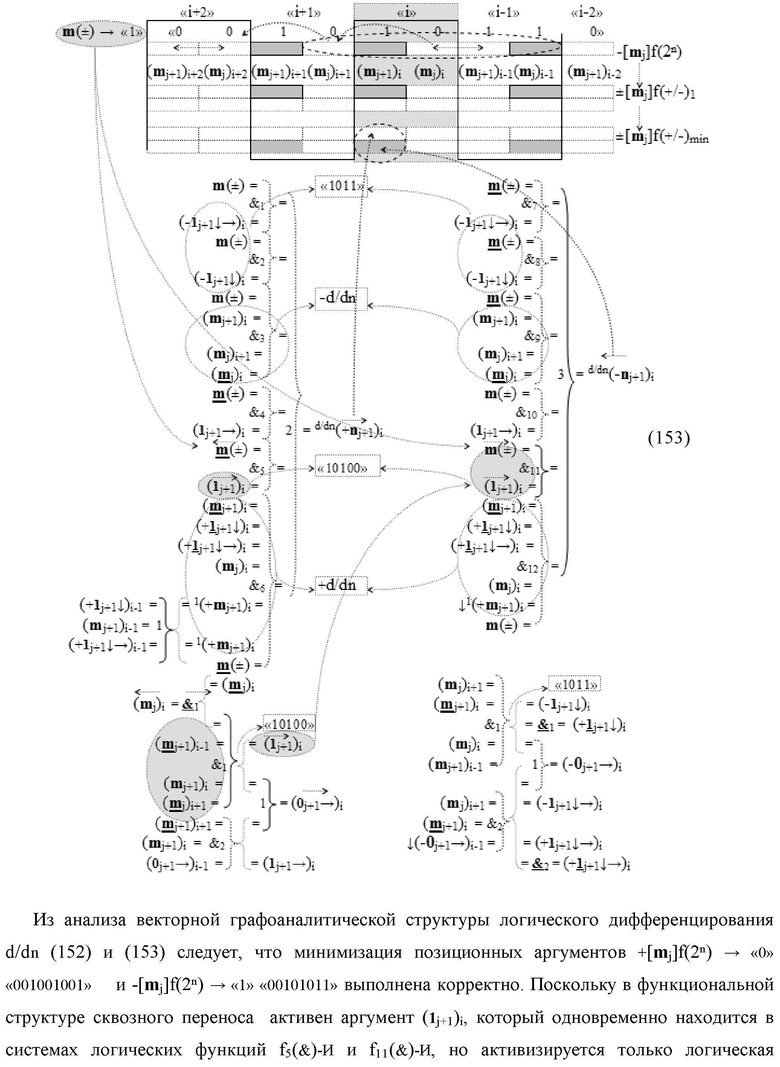

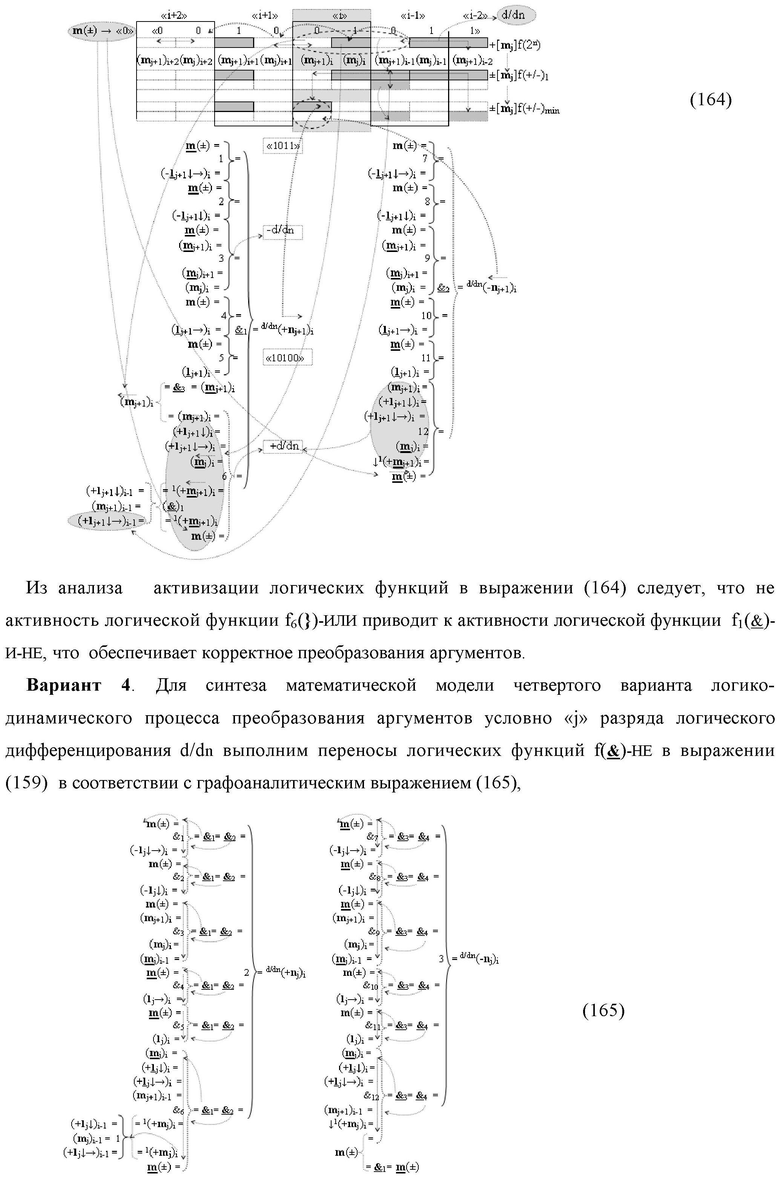

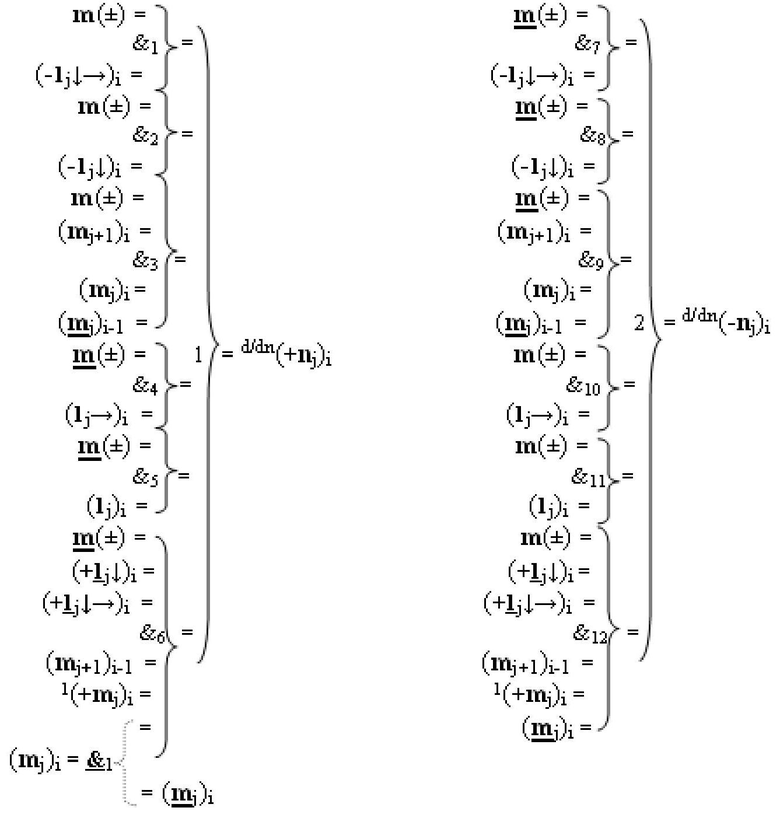

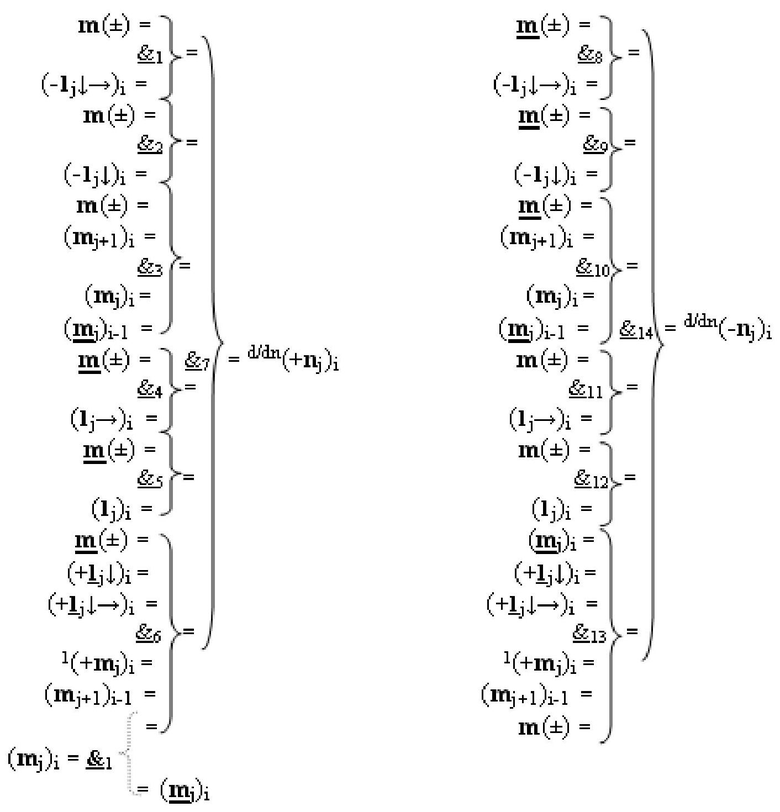

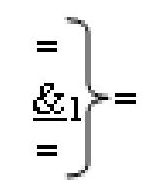

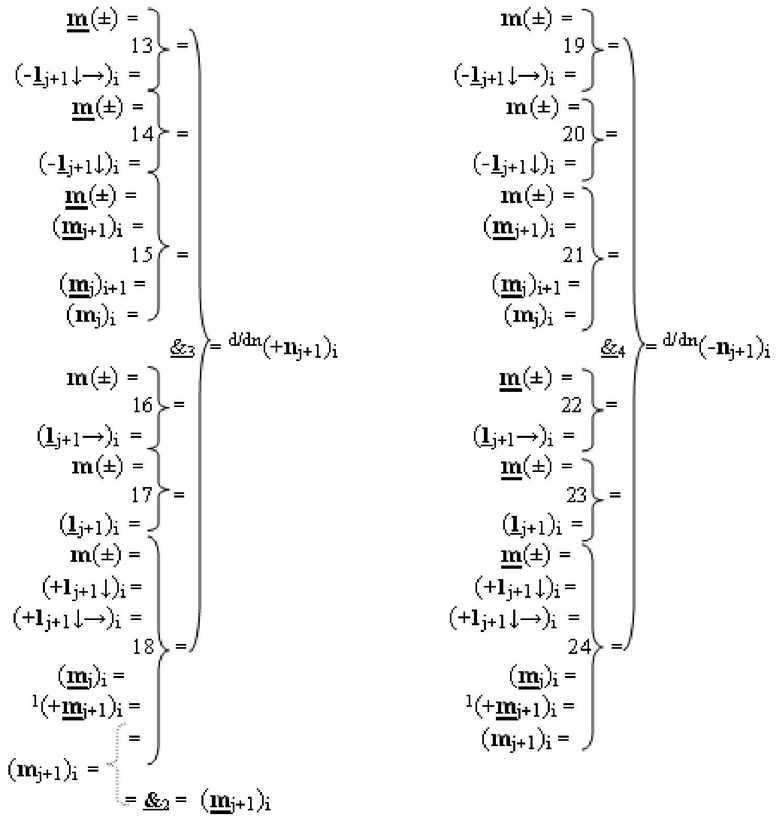

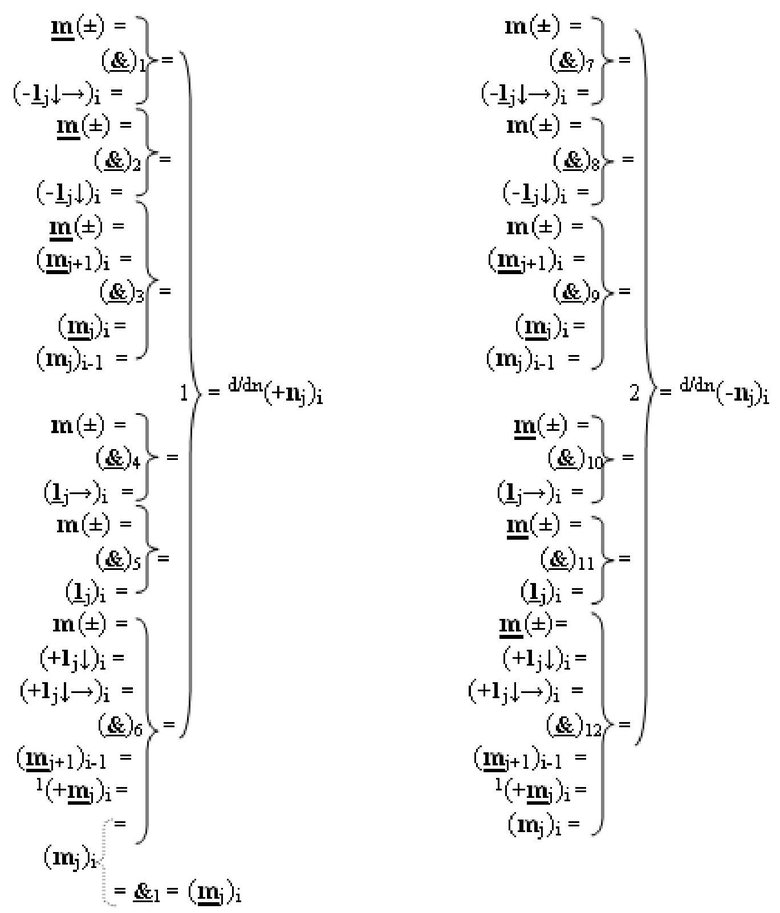

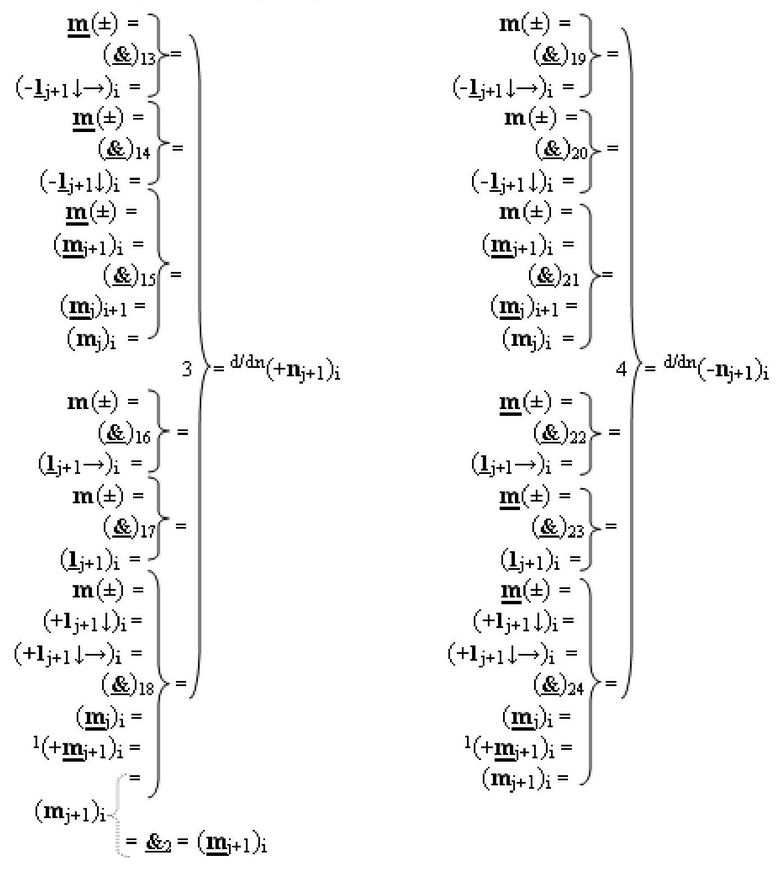

1. Функциональная структура процедуры логического дифференцирования d/dn позиционных аргументов [mj]f(2n) с учетом их знака m(±) для формирования позиционно-знаковой структуры ±[mj]f(+/-)min с минимизированным числом активных в ней аргументов, которая включает логическую функцию f(&)-HE для формирования аргумента знакового разряда m(±) с измененным уровнем аналогового сигнала и выполнена в виде положительного и условно отрицательного каналов условно «j» разряда и «j+1» разряда для преобразования входных аргументов [mj]f(2n) в условно «i» «Зоне минимизации», при этом положительный и условно отрицательный каналы двух разрядов содержат выходные логические функции f1(})-ИЛИ, f2(})-ИЛИ и f3(})-ИЛИ, f4(})-ИЛИ, в которых функциональные выходные связи являются функциональными выходными связями каналов для формирования положительного и условно отрицательного результирующих аргументов d/dn(+nj)i и d/dn(-nj)i «j» разряда и для формирования результирующих аргументов d/dn(+nj+1)i и d/dn(-nj+1)i «j+1» разряда, а функциональные входные связи логических функций f2(})-ИЛИ и f44(})-ИЛИ являются функциональными выходными связями логических функций f9(&)-И, f12(&)-И и f21(&)-И, f24(&)-И в условно отрицательных каналах и функциональные входные связи логических функций f1(})-ИЛИ и f3(})-ИЛИ являются функциональными выходными связями логических функций f3(&)-И, f6(&)-И и f15(&)-И и f18(&)-И в положительных каналах соответственно, при этом в положительных каналах «j» и «j+1» разряда функциональные входные связи логических функций f6(&)-И и f18(&)-И являются функциональными выходными связями логических функций f1(&)-HE и f2(&)-HE соответственно, которые формируют аргументы (m

j)i и (m

j+i)i с измененным уровнем аналогового сигнала и в которых функциональные входные связи выполняют прием аргументов (mj)i и (mj+1)i, а функциональные входные связи логических функций f3(&)-И и f15(&)-И являются функциональными входными связями каналов для приема аргументов m(±), (mj)i и m(±), (mj+1)i, (m

j)i соответственно, при этом в условно отрицательных каналах «j» и «j+1» разрядов функциональные входные связи логических функций f9(&)-И и f21(&)-И являются функциональными входными связями каналов для приема аргументов m(±), (mj)i и m(±), (mj+1)i, (m

j)i соответственно, а функциональные входные связи логических функций f12(&)-И и f24(&)-И являются функциональными входными связями каналов для приема аргументов m(±), (m

j)i и m(±), (mj)i (m

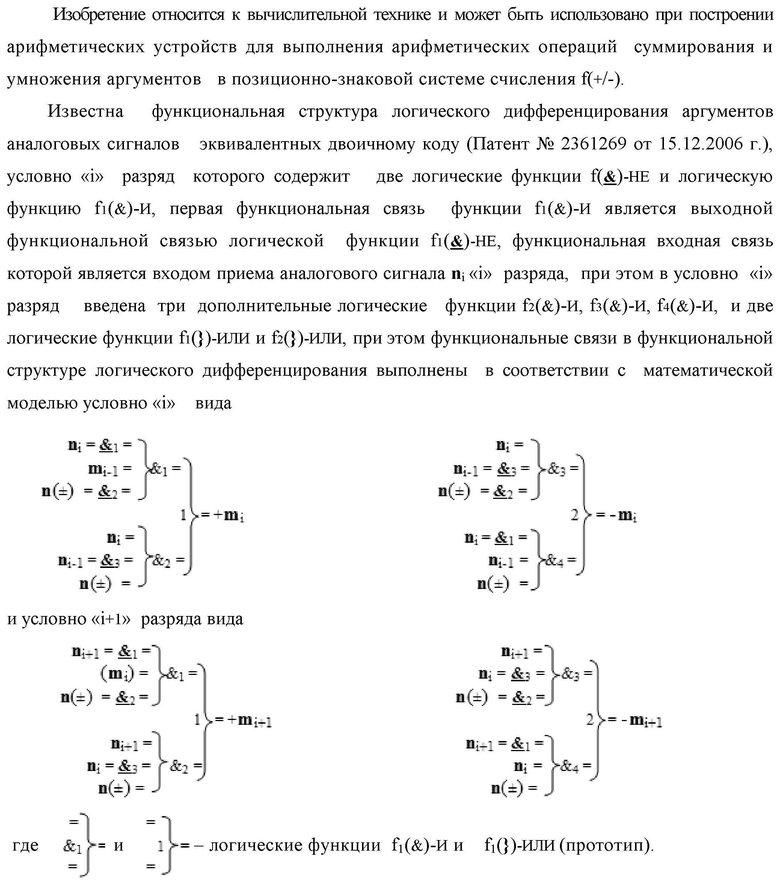

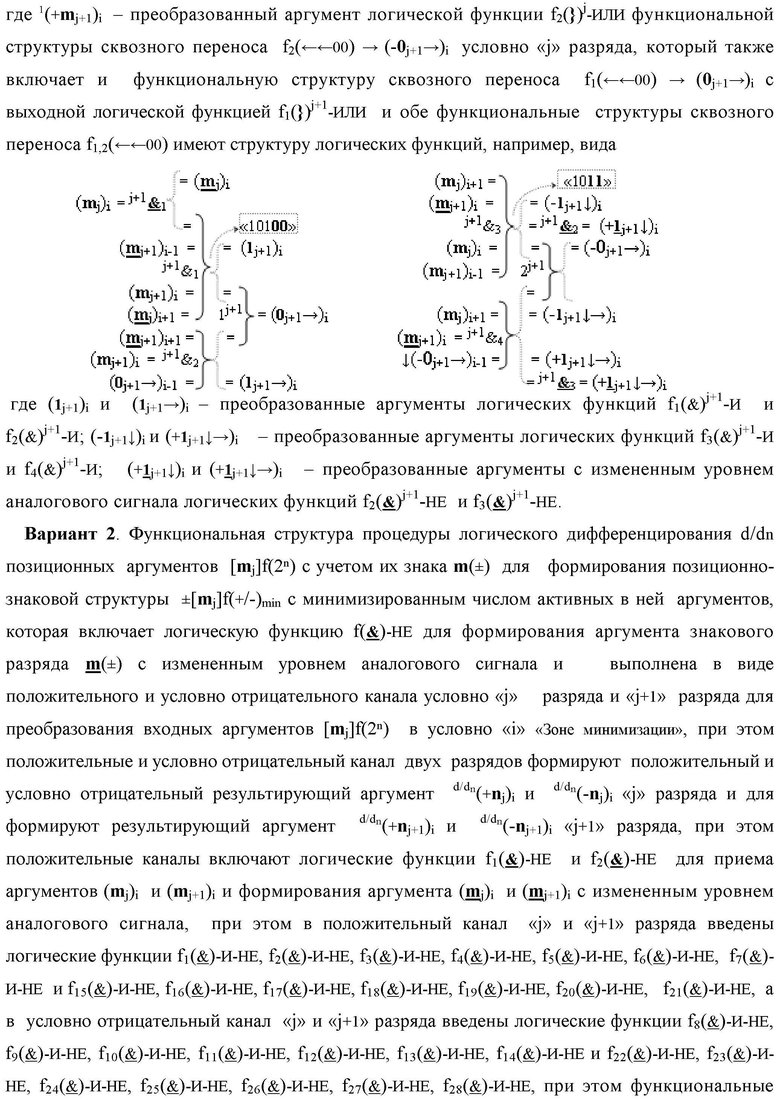

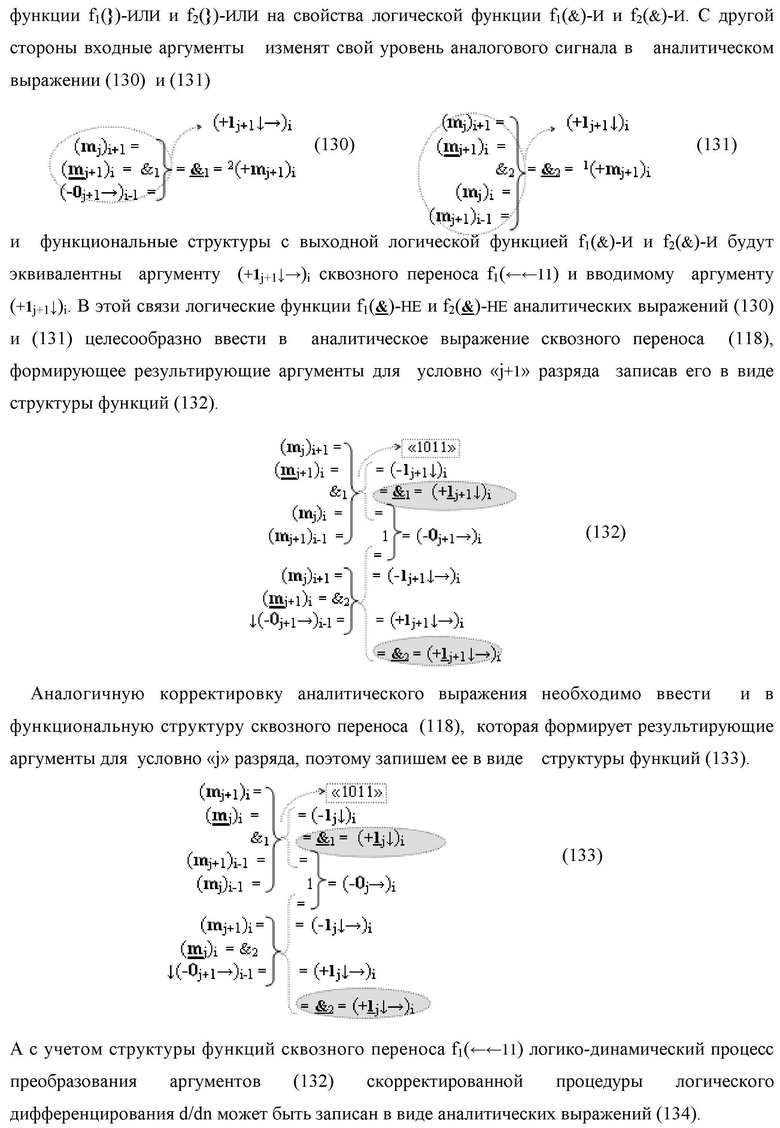

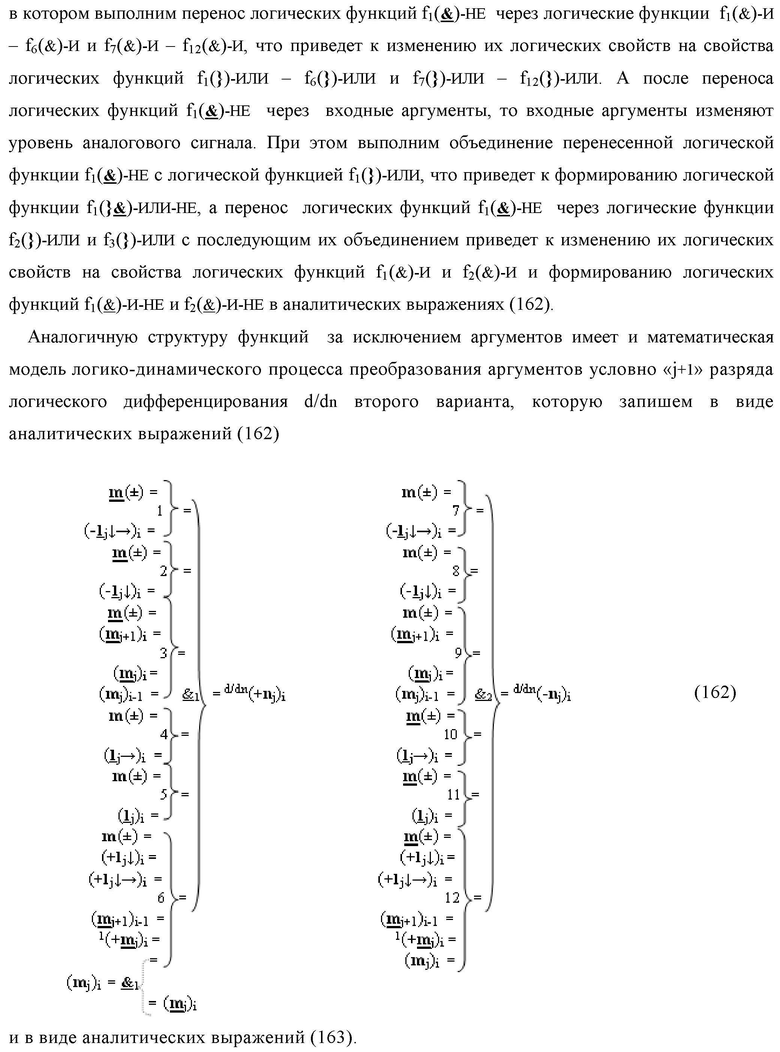

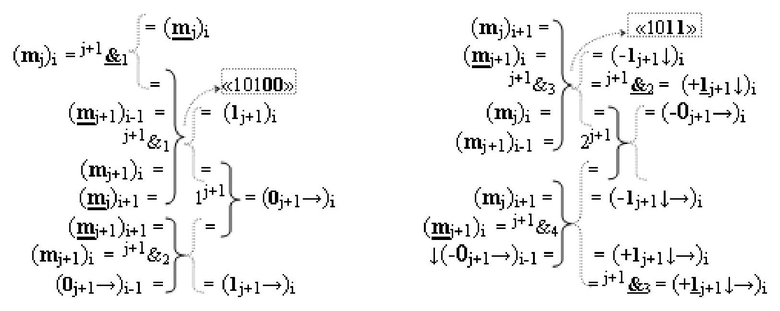

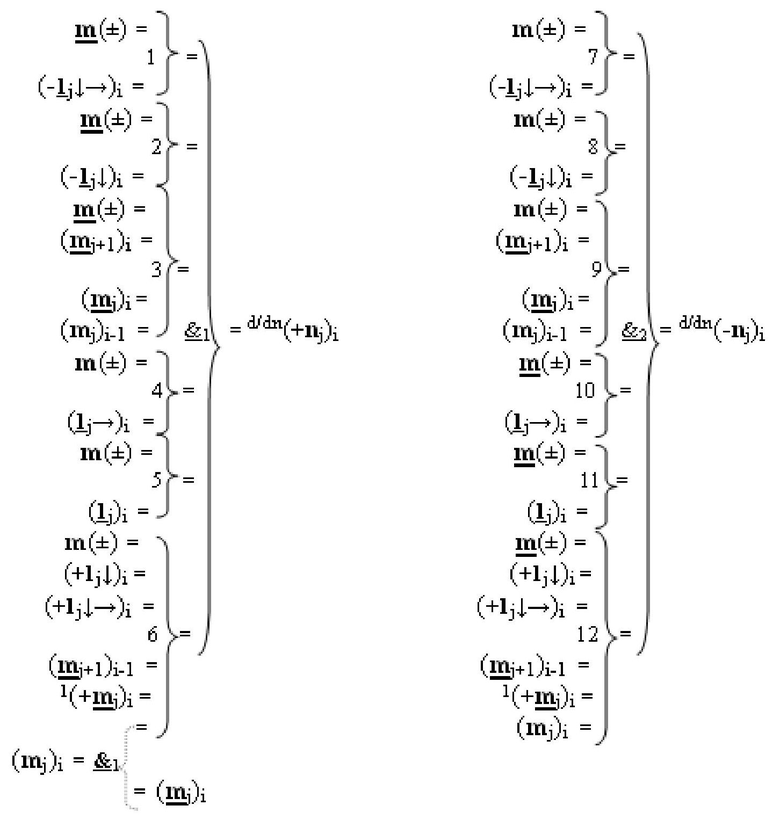

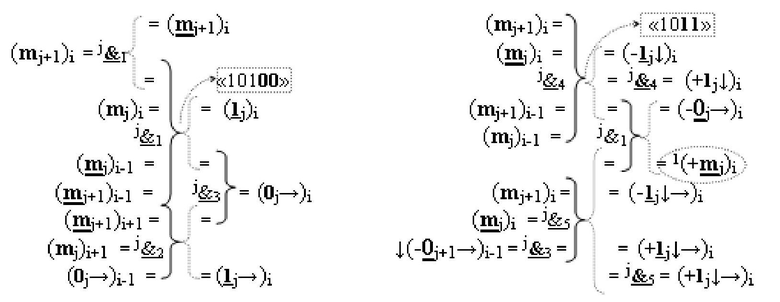

j+1)i соответственно, отличающаяся тем, что в положительный канал «j» и «j+1» разрядов введены логические функции f1(&)-И, f2(&)-И, f4(&)-И, f5(&)-И и f13(&)-И, f14(&)-И, f16(&)-И, f17(&)-И, а в условно отрицательный канал «j» и «j+1» разрядов введены логические функции f7(&)-И, f8(&)-И, f10(&)-И, f11(&)-И и f19(&)-И, f20(&)-И, f22(&)-И, f23(&)-И, при этом функциональные связи логических функций в каналах выполнены в соответствии с математической моделью условно «j» разряда вида

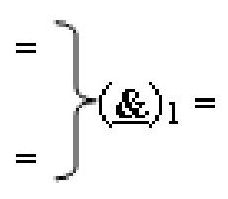

где «=&

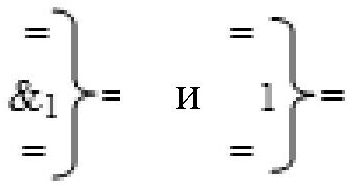

1=» - логическая функция изменения активности входных аналоговых сигналов f1(&)-HE;

- логические функции f1(&)-И и f1(})-ИЛИ;

- логические функции f1(&)-И и f1(})-ИЛИ;

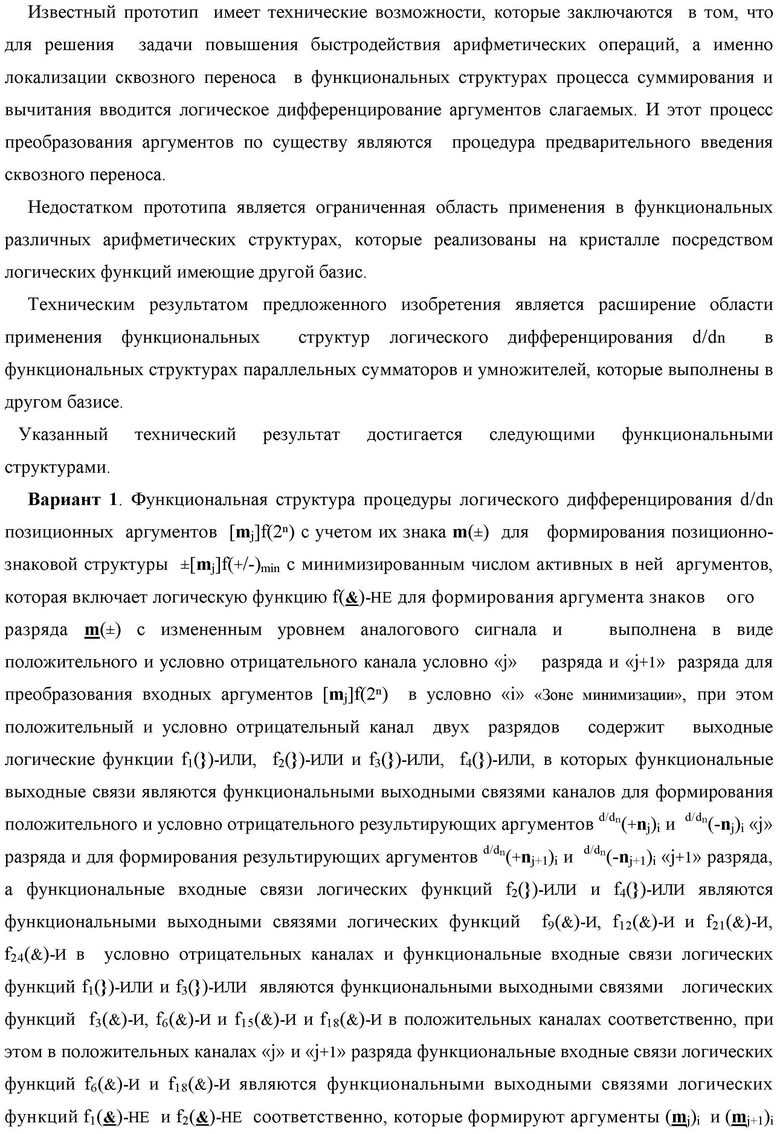

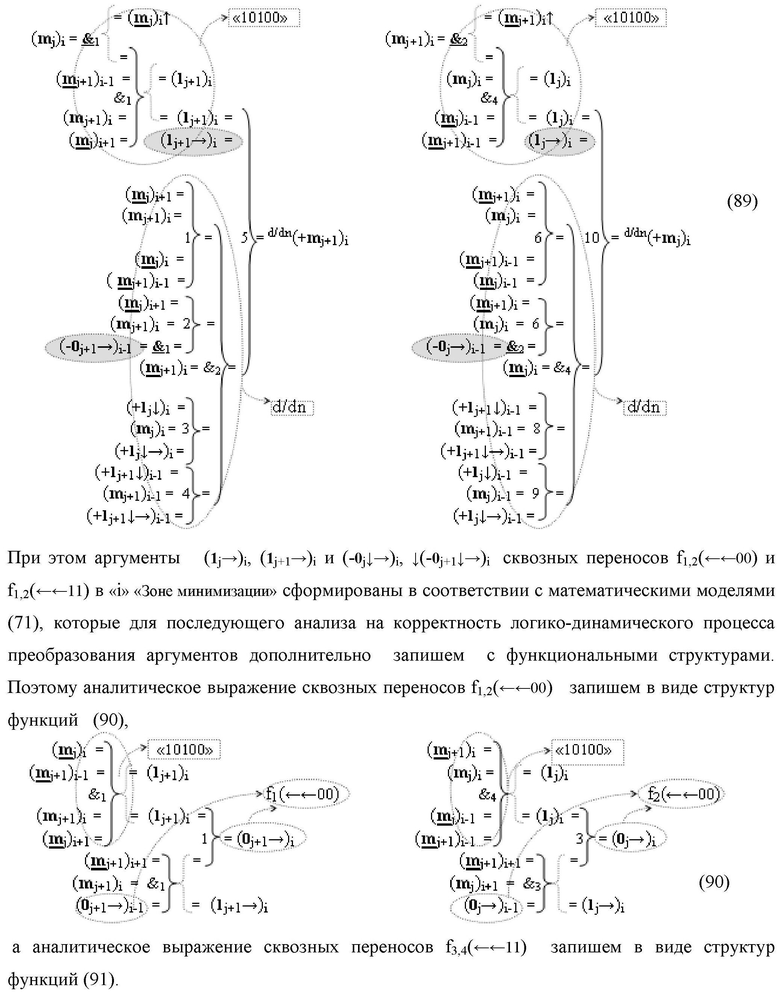

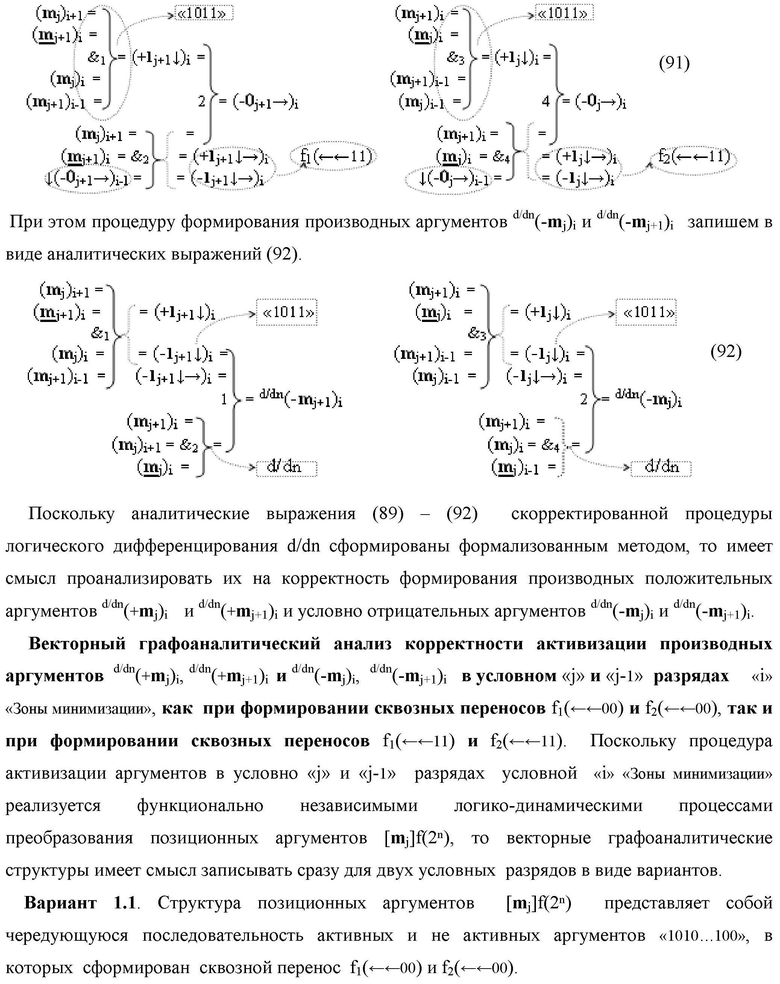

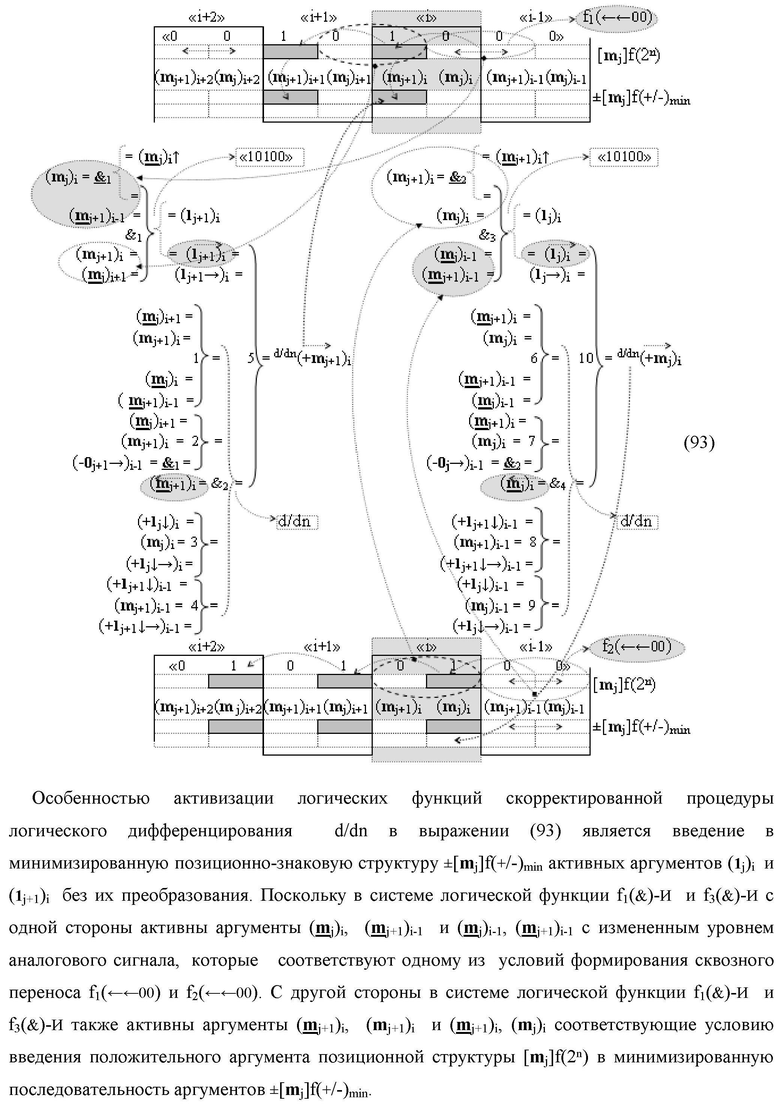

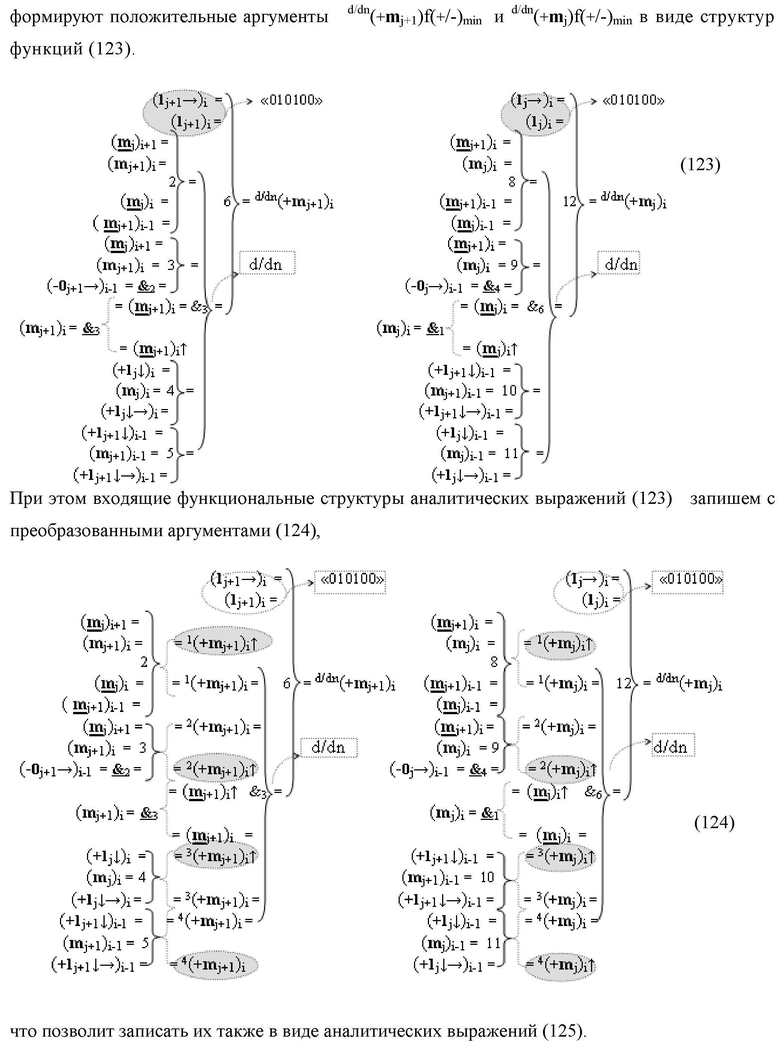

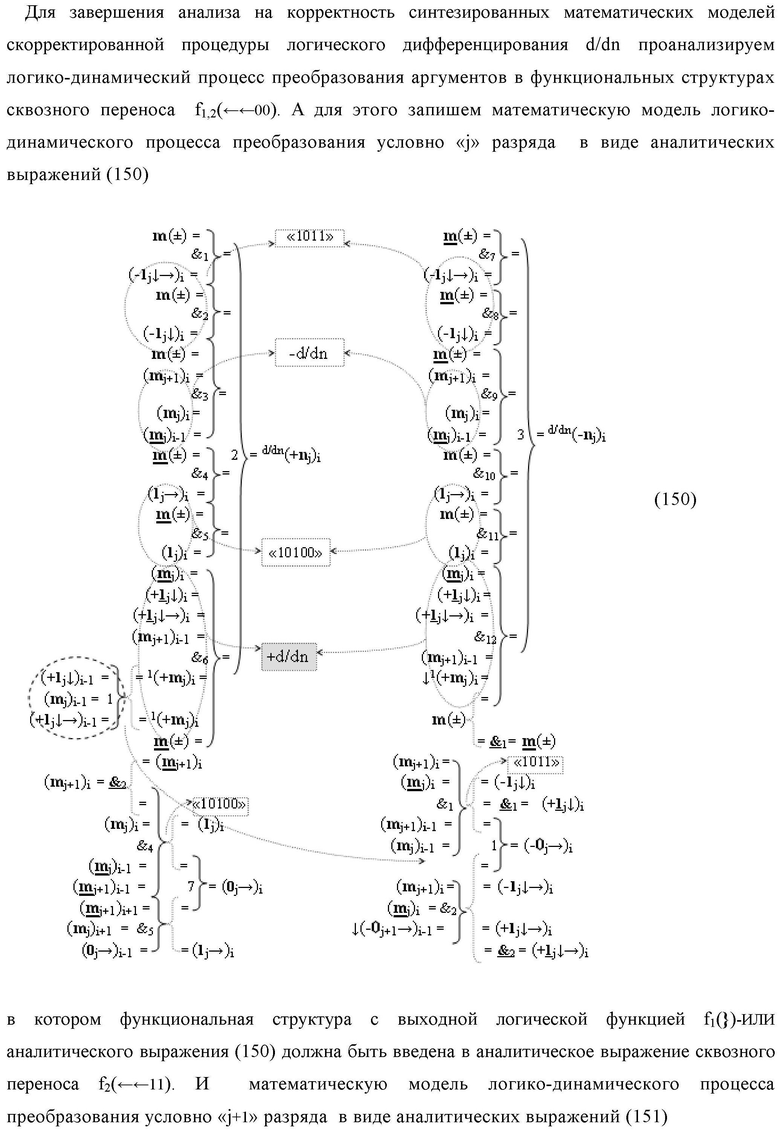

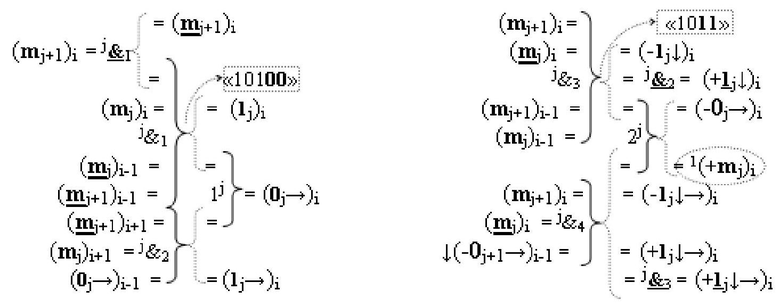

l(+mj)i - преобразованный аргумент логической функции f2(})j-ИЛИ функциональной структуры сквозного переноса f2(←←00)→(-0j→)i условно «j» разряда, который также включает и функциональную структуру сквозного переноса f1(←←00)→(0j→)i с выходной логической функцией f1(})j-ИЛИ, и обе функциональные структуры сквозного переноса f1,2(←←00) имеют структуру логических функций, например, вида

где (1j)i и (1j→)i - преобразованные аргументы логических функций f1(&)j-И и f2(&)j-И;

(-1j↓)i и (+1j↓→)i - преобразованные аргументы логических функций f3(&)j-И и f4(&)j-И;

(+1

j↓)i и (+1

j↓→)i - преобразованные аргументы с измененным уровнем аналогового сигнала логических функций f2(&)j-HE и f3(&)j-НЕ;

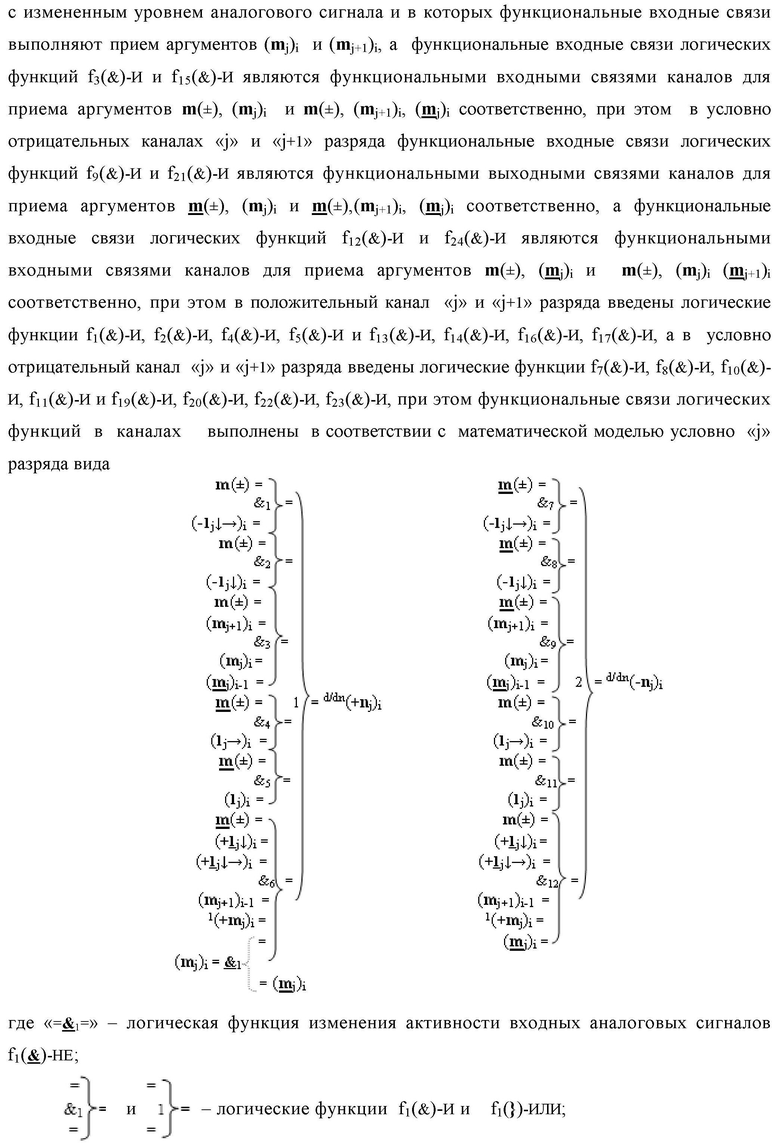

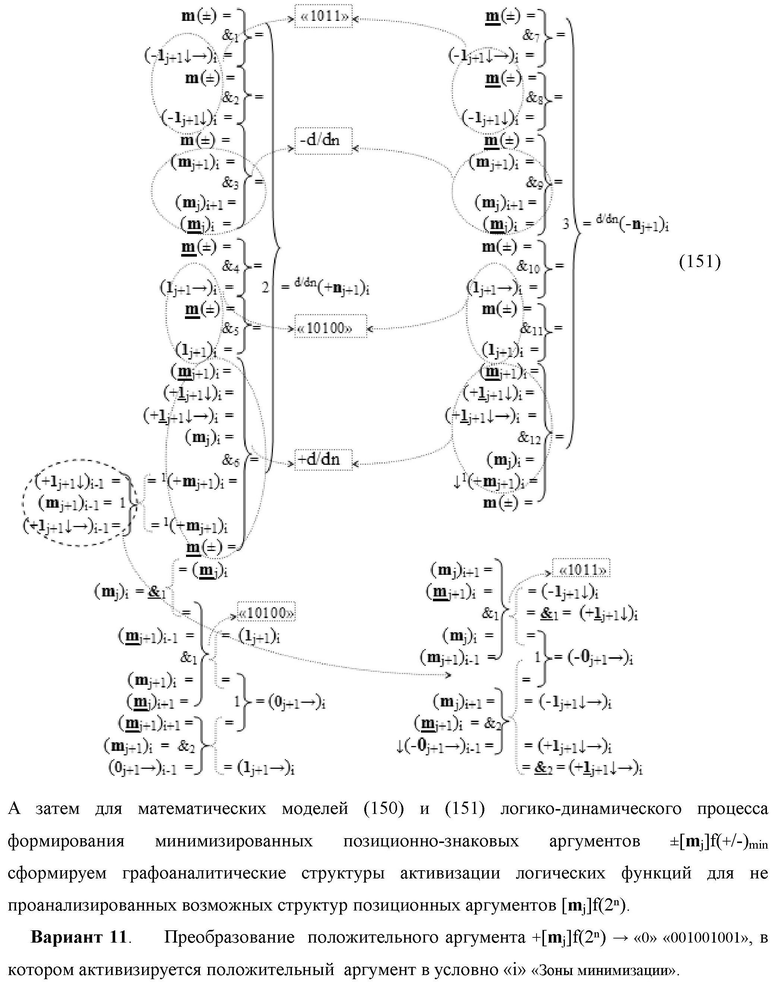

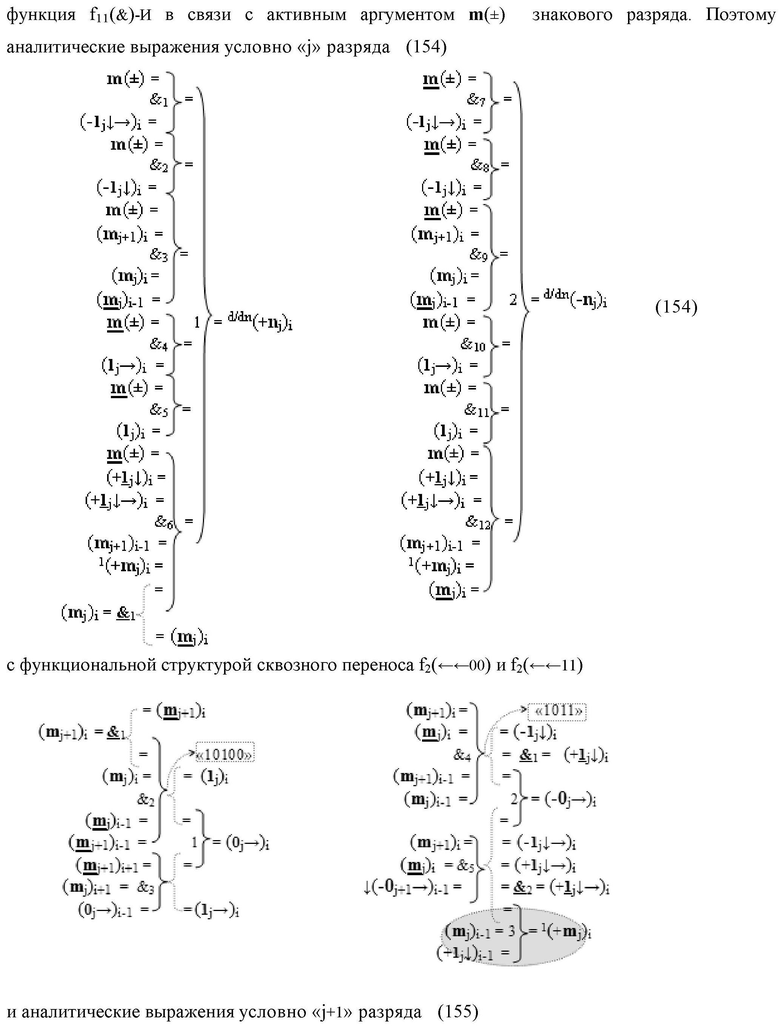

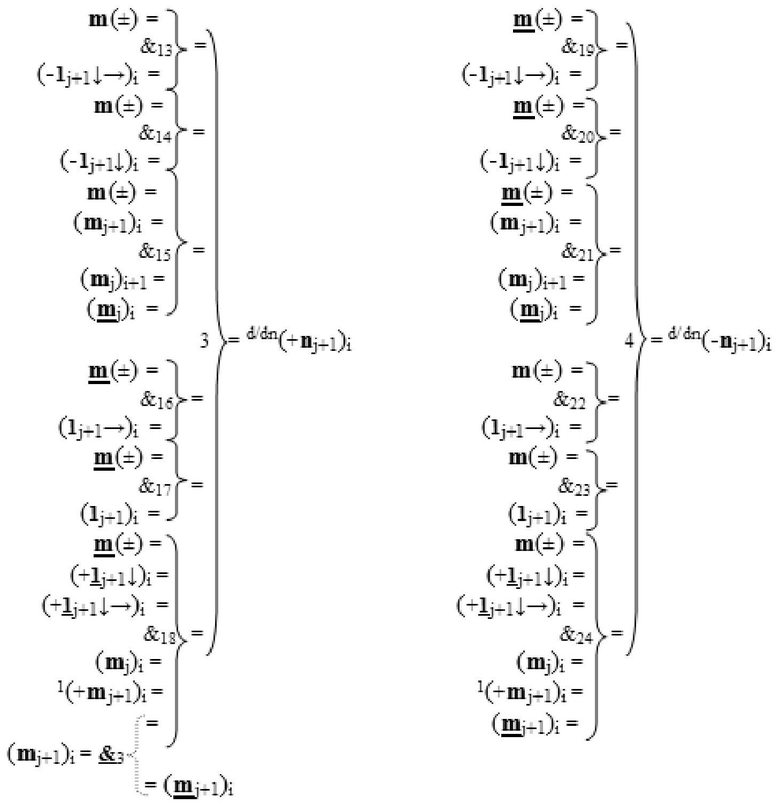

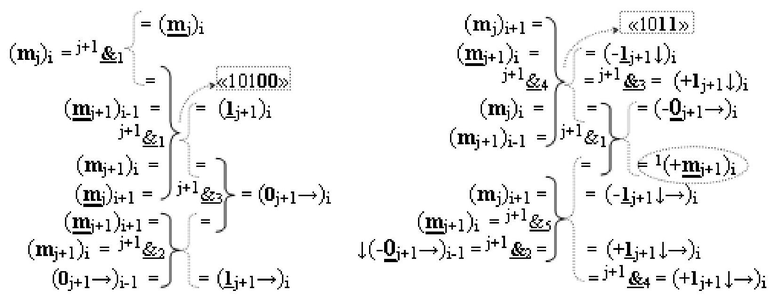

и математической моделью условно «j+1» разряда вида

где 1(+mj+1)i - преобразованный аргумент логической функции f2(})j-ИЛИ функциональной структуры сквозного переноса f2(←←00)→(-0j+1→)i условно «j» разряда, который также включает и функциональную структуру сквозного переноса f1(←←00)→(0j+1→)i с выходной логической функцией f1(})j+1-ИЛИ, и обе функциональные структуры сквозного переноса f1,2(←←00) имеют структуру логических функций, например, вида

где (1j+1)i и (1j+1→)i - преобразованные аргументы логических функций f1(&)j+1-И и f2(&)j+1-И; (-1j+1↓)i и (+1j+1↓→)i - преобразованные аргументы логических функций f3(&)j+1-И и f4(&)j+1-И; (+1

j+1↓)i и (+1

j+1↓→)i - преобразованные аргументы с измененным уровнем аналогового сигнала логических функций f2(&)j+l-HE и

f3(&)j+1-HE.

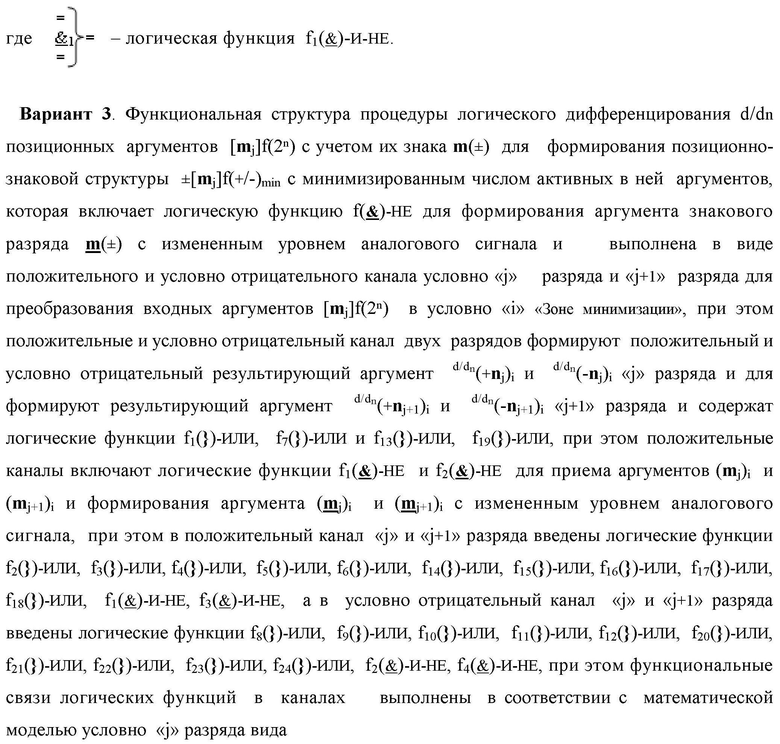

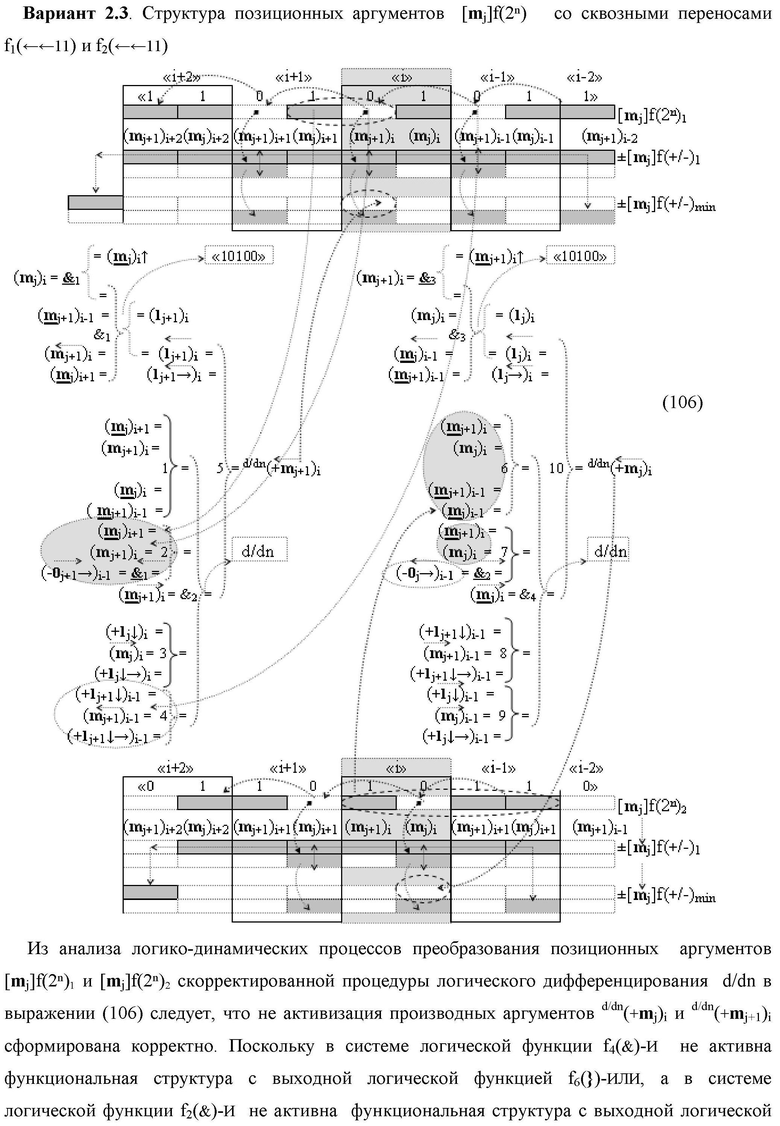

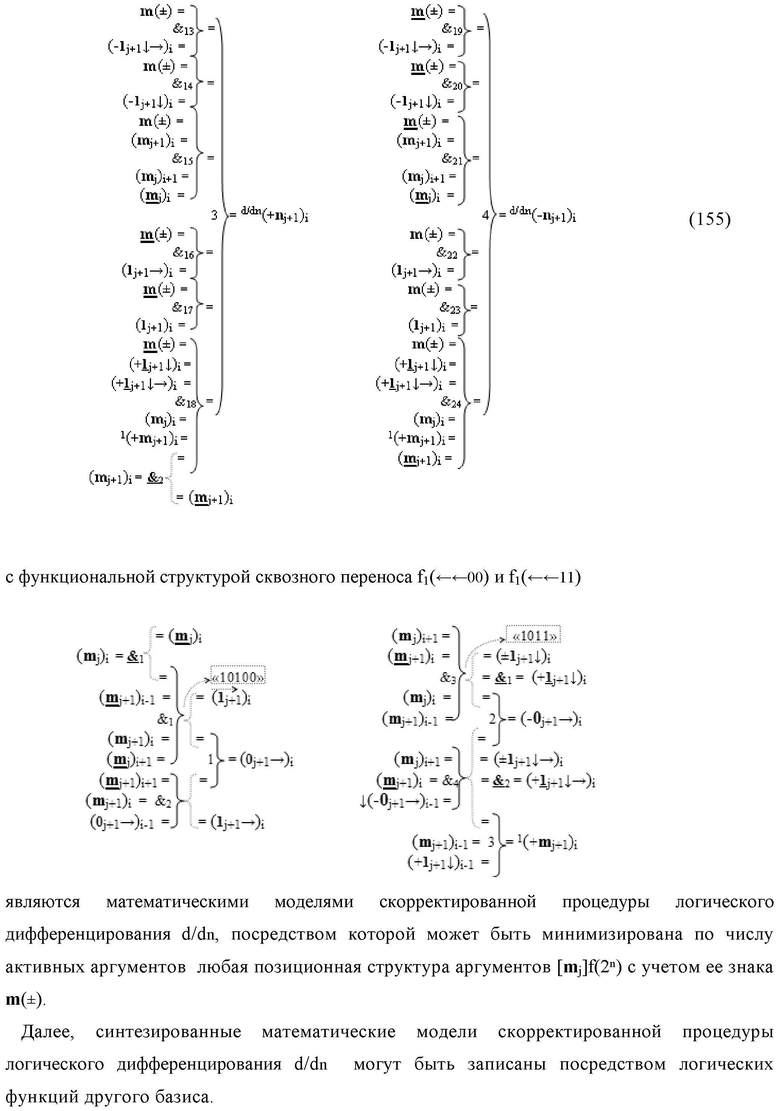

2. Функциональная структура процедуры логического дифференцирования d/dn позиционных аргументов [mj]f(2n) с учетом их знака m(±) для формирования позиционно-знаковой структуры ±[mj]f(+/-)min с минимизированным числом активных в ней аргументов, которая включает логическую функцию f(&)-HE для формирования аргумента знакового разряда m(±) с измененным уровнем аналогового сигнала и выполнена в виде положительного и условно отрицательного каналов условно «j» разряда и «j+1» разряда для преобразования входных аргументов [mj]f(2n) в условно «i» «Зоне минимизации», при этом положительные и условно отрицательный каналы двух разрядов формируют положительный и условно отрицательный результирующие аргументы d/dn(+nj)i и d/dn(-nj)i «j» разряда и формируют результирующий аргумент d/dn(+nj+1)i и d/dn(-nj+1)i «j+1» разряда, при этом положительные каналы включают логические функции f1(&)-HE и f2(&)-НЕ для приема аргументов (mj)i и (mj+1)i и формирования аргумента (m

j)i и (m

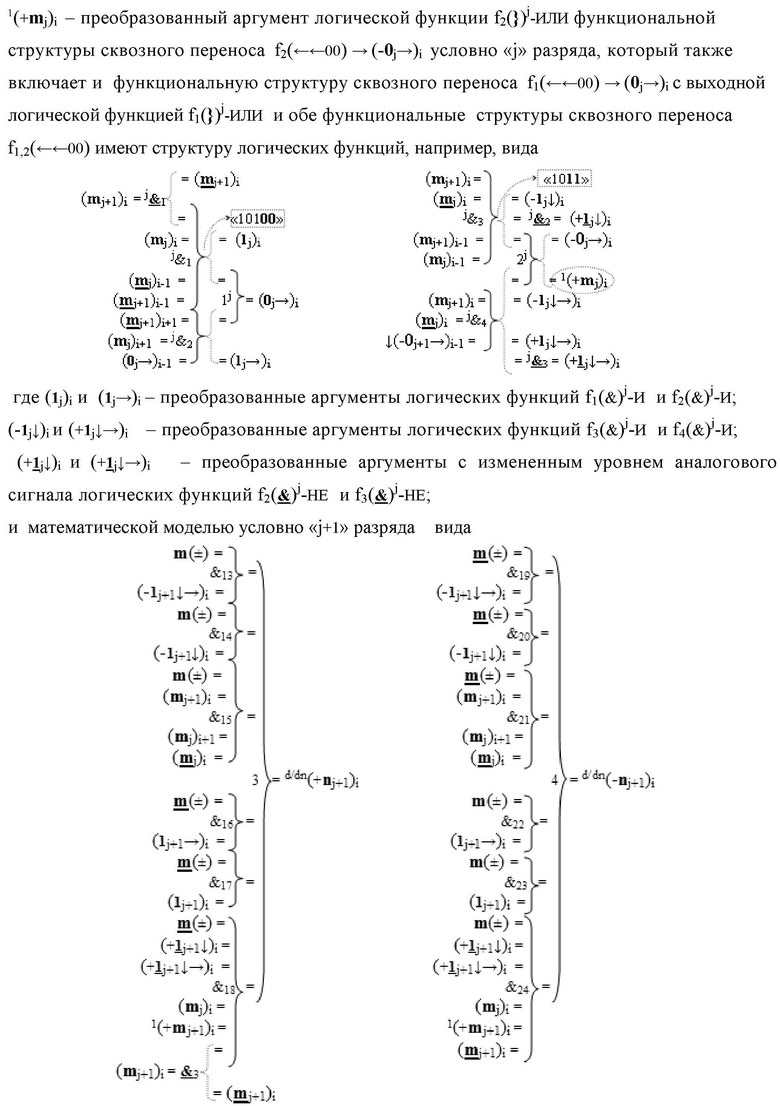

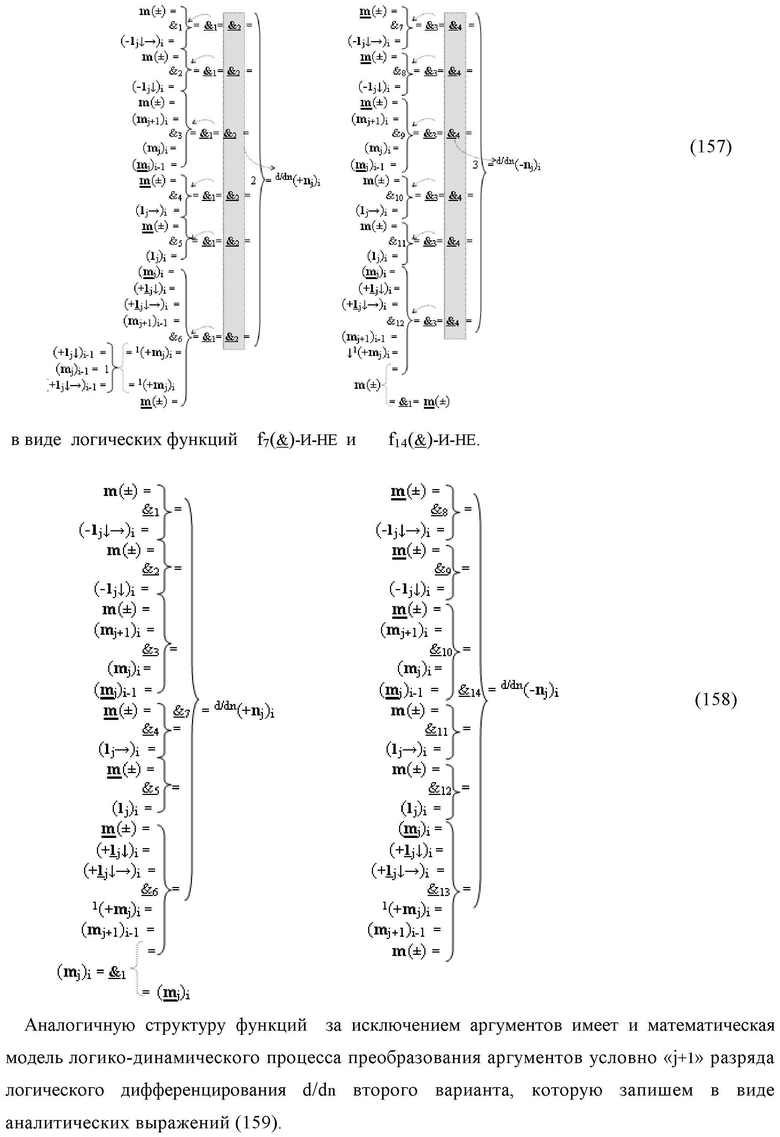

j+1)i с измененным уровнем аналогового сигнала, отличающаяся тем, что в положительный канал «j» и «j+1» разрядов введены логические функции f1(&)-И-HE, f2(&)-И-HE, f3(&)-И-НЕ, f4(&)-И-НЕ, f5(&)-И-HE, f6(&)-И-НЕ, f7(&)-И-HE и f15(&)-И-HE, f16(&)-И-НЕ, f17(&)-И-НЕ, f18(&)-И-HE, f19(&)-И-НЕ, f20(&)-И-HE, f21(&)-И-HE, а в условно отрицательный канал «j» и «j+1» разрядов введены логические функции f8(&)-И-HE, f9(&)-И-HE, f10(&)-И-НЕ, f11(&)-И-HE, f12(&)-И-HE, f13(&)-И-НЕ, f14(&)-И-HE и f22(&)-И-HE, f23(&)-И-НЕ, f24(&)-И-НЕ, f25(&)-И-НЕ, f26(&)-И-HE, f27(&)-И-HE, f28(&)-И-НЕ, при этом функциональные связи логических функций в каналах выполнены в соответствии с математической моделью условно «j» разряда вида

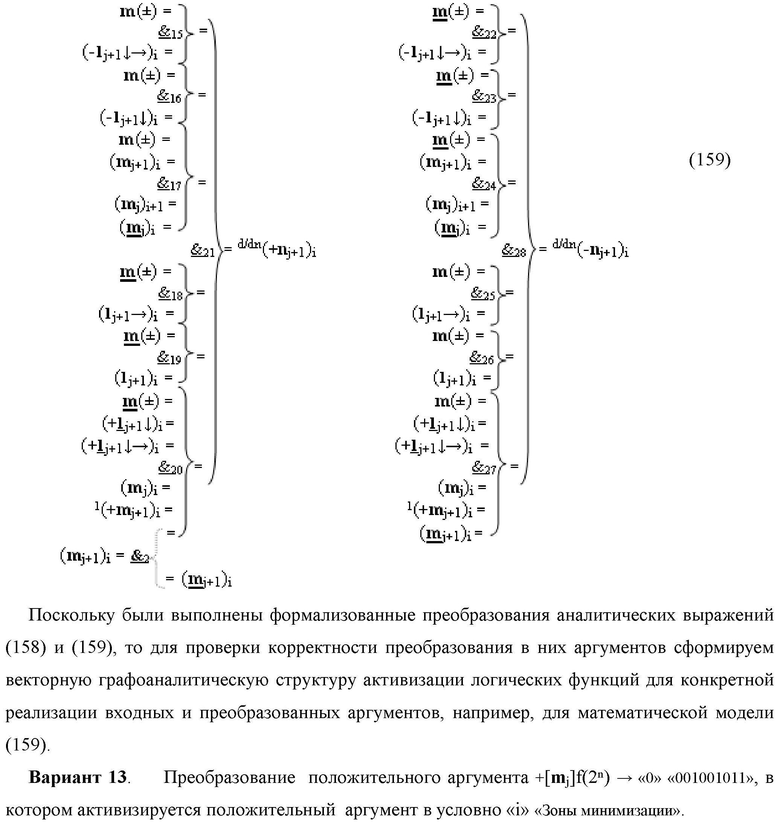

и математической моделью условно «j+1» разряда вида

где  - логическая функция f1(&)-И-НЕ.

- логическая функция f1(&)-И-НЕ.

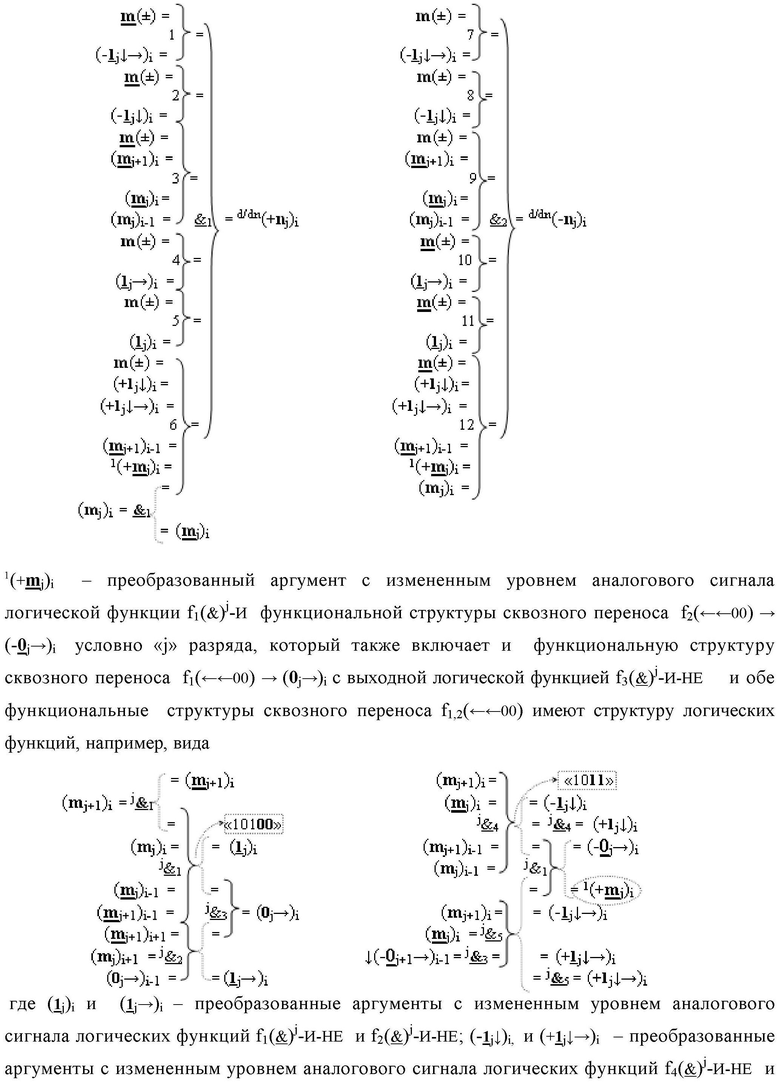

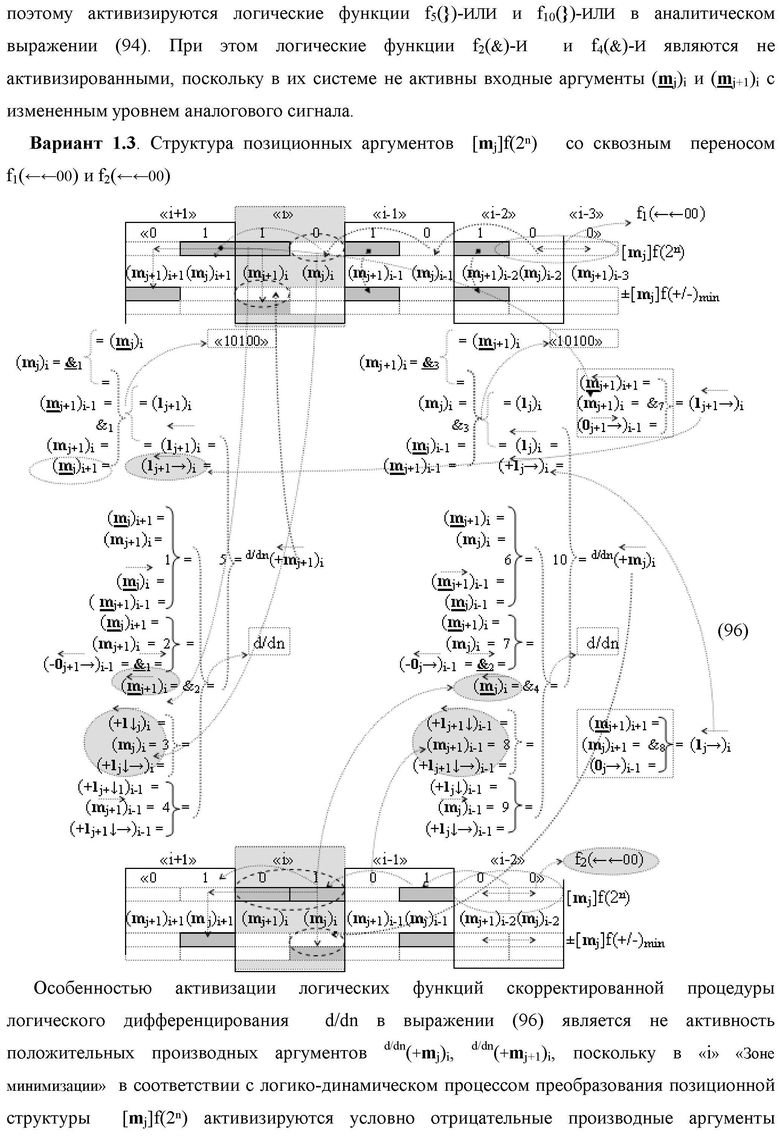

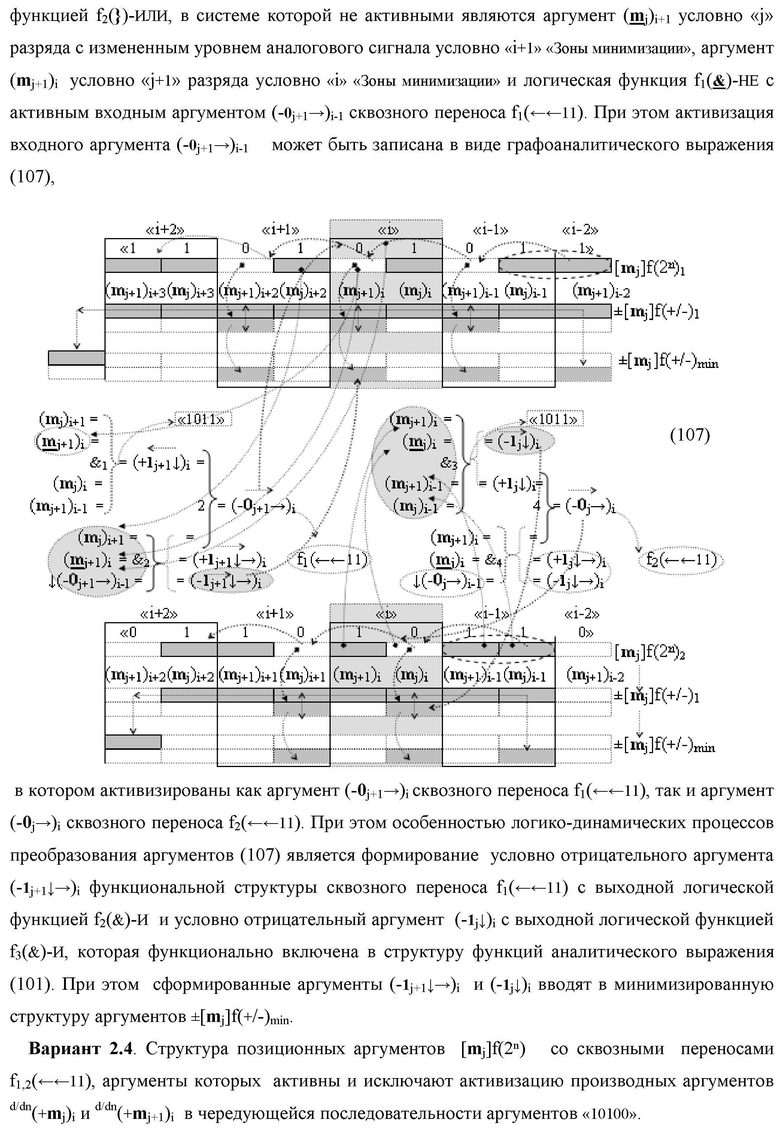

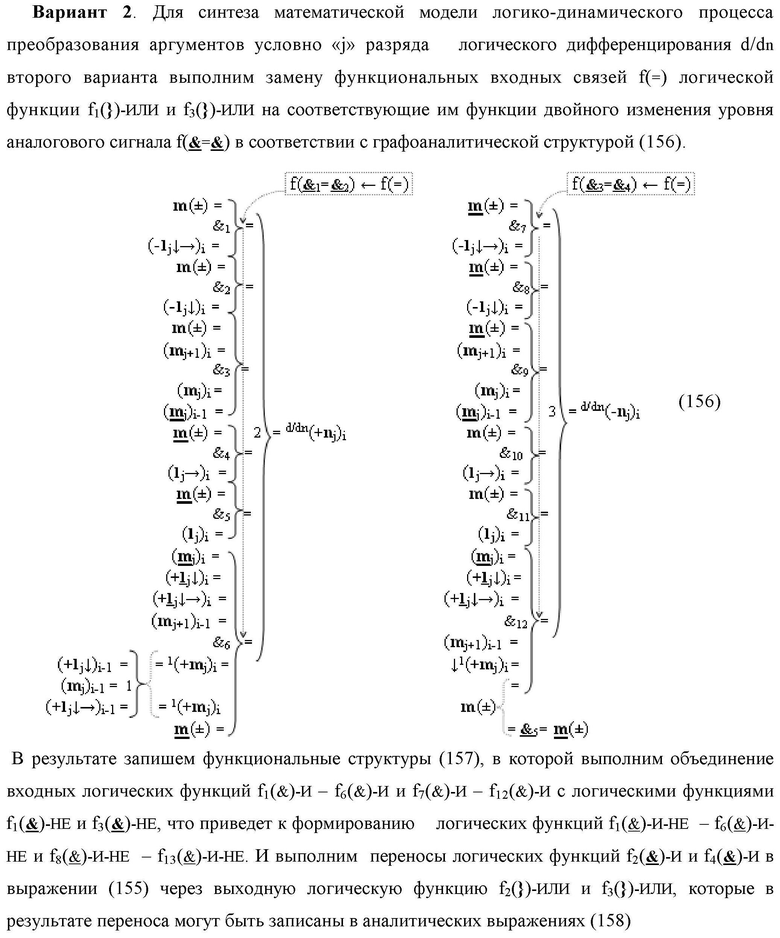

3. Функциональная структура процедуры логического дифференцирования d/dn позиционных аргументов [mj]f(2n) с учетом их знака m(±) для формирования позиционно-знаковой структуры ±[mj]f(+/-)min с минимизированным числом активных в ней аргументов, которая включает логическую функцию f(&)-HE для формирования аргумента знакового разряда m(±) с измененным уровнем аналогового сигнала и выполнена в виде положительного и условно отрицательного каналов условно «j» разряда и «j+1» разрядов для преобразования входных аргументов [mj]f(2n) в условно «i» «Зоне минимизации», при этом положительные и условно отрицательный каналы двух разрядов формируют положительный и условно отрицательный результирующие аргументы d/dn(+nj)i и d/dn(-nj)i «j» разряда и формируют результирующие аргументы d/dn(+nj+1)i и d/dn(-nj+1)i «j+1» разряда и содержат логические функции f1(})-ИЛИ, f7(})-ИЛИ и f13(})-ИЛИ, f19(})-ИЛИ, при этом положительные каналы включают логические функции f1(&)-HE и f2(&)-HE для приема аргументов (mj)i и (mj+1) и формирования аргумента (m

j)i и (m

j+1) с измененным уровнем аналогового сигнала, отличающаяся тем, что в положительный канал «j» и «j+1» разрядов введены логические функции f2(})-ИЛИ, f3(})-ИЛИ, f4(})-ИЛИ, f5(})-ИЛИ, f6(})-ИЛИ, f14(})-ИЛИ, f15(})-ИЛИ, f16(})-ИЛИ, f17(})-ИЛИ, f18(})-ИЛИ, f1(&)-И-НЕ, f3(&)-И-НЕ, а в условно отрицательный канал «j» и «j+1» разрядов введены логические функции f8(})-ИЛИ, f9(})-ИЛИ, f10(})-ИЛИ, f11(})-ИЛИ, f12(})-ИЛИ, f20(})-ИЛИ, f21(})-ИЛИ, f22(})-ИЛИ, f23(})-ИЛИ, f24(})-ИЛИ, f2(&)-И-НЕ, f4(&)-И-НЕ, при этом функциональные связи логических функций в каналах выполнены в соответствии с математической моделью условно «j» разряда вида

где 1(+m

j)i - преобразованный аргумент с измененным уровнем аналогового сигнала логической функции f1(&)j-И функциональной структуры сквозного переноса f2(←←00)→(-0

j→)i условно «j» разряда, который также включает и функциональную структуру сквозного переноса f1(←←00)→(0j→)i с выходной логической функцией f3(&)-И-НЕ, и обе функциональные структуры сквозного переноса f1,2(←←00) имеют структуру логических функций, например, вида

где (1

j)i и (1

j→)i - преобразованные аргументы с измененным уровнем аналогового сигнала логических функций f1(&)j-И-НЕ и f2(&)j-И-HE; (-1

j↓)i, и (+1

j↓→)i - преобразованные аргументы с измененным уровнем аналогового сигнала логических функций f4(&)j-И-НЕ и f5(&)j-И-НЕ; (+1j↓)i и (+1j↓→)i - преобразованные аргументы логических функций f4(&)j-HE и f5(&)j-HE;

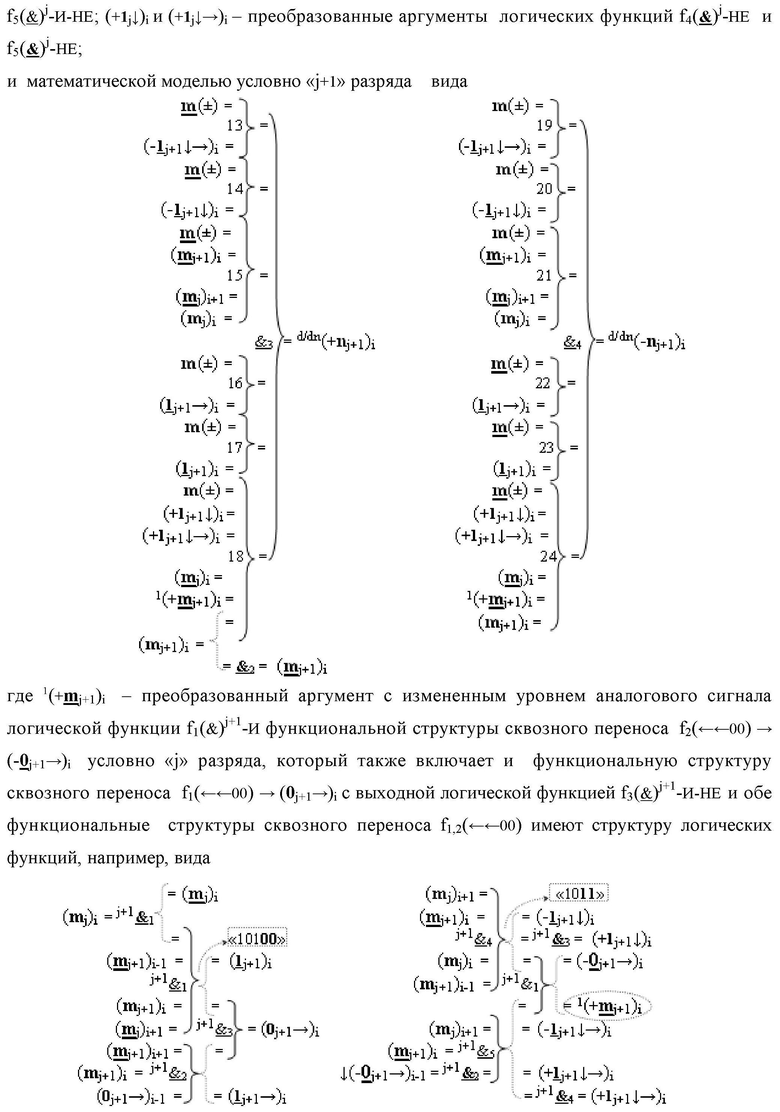

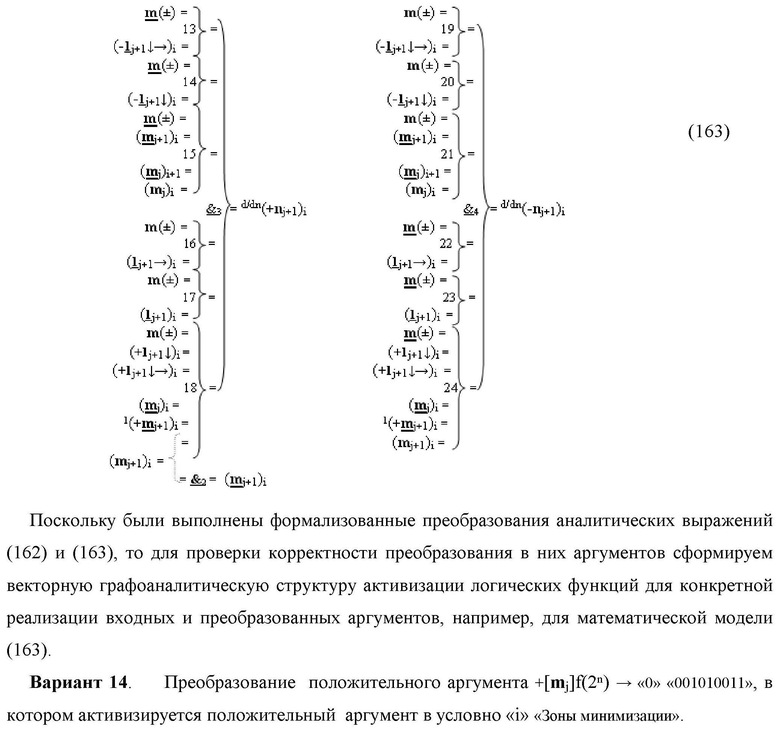

и математической моделью условно «j+1» разряда вида

где l(+m

j+1)i - преобразованный аргумент с измененным уровнем аналогового сигнала логической функции f1(&)j+1-И функциональной структуры сквозного переноса f2(←←00)→(-0

j+1→)i условно «j» разряда, который также включает и функциональную структуру сквозного переноса f1(←←00)→(0j+1→)i с выходной логической функцией f3(&)j+1-И-HE, и обе функциональные структуры сквозного переноса f1,2(←←00) имеют структуру логических функций, например, вида

где (1

j+1)i и (1

j+1→)i - преобразованные аргументы с измененным уровнем аналогового сигнала логических функций f1(&)j+1-И-HE и f2(&)j+1-И-HE; (-1

j+1↓)i,

(+1

j+1↓→)i и (-1

j+1↓→)i - преобразованные аргументы с измененным уровнем аналогового сигнала логических функций f4(&)j+1-И-HE и f5(&)j+1-И-HE; (+1j+1↓)i и (+1j+1↓→)i - преобразованные аргументы логических функций f3(&)j+1-HE и f4(&)j+l-HE.

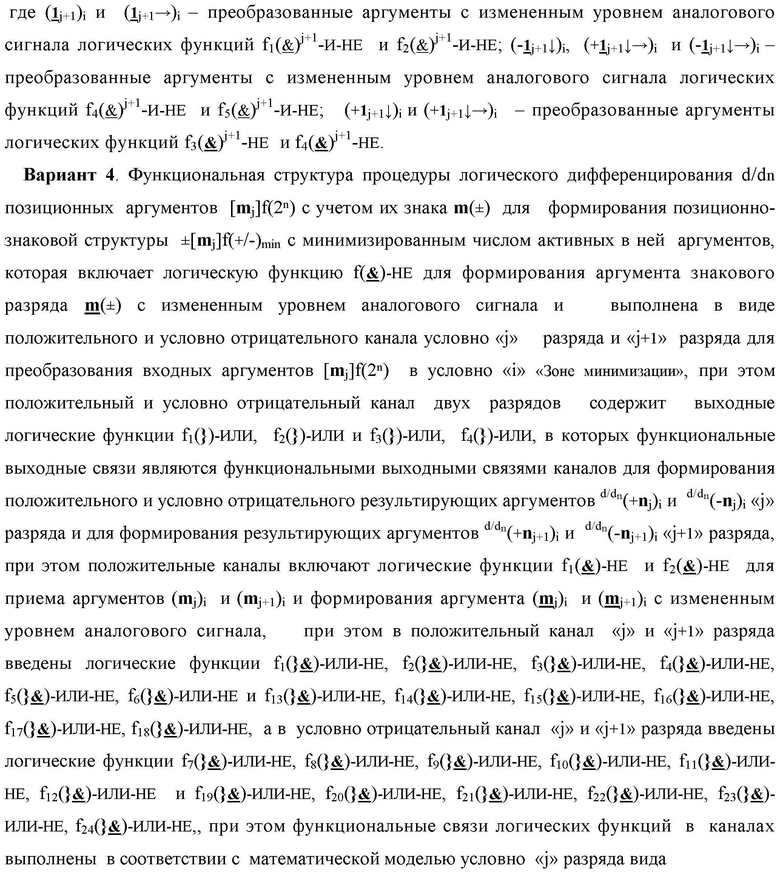

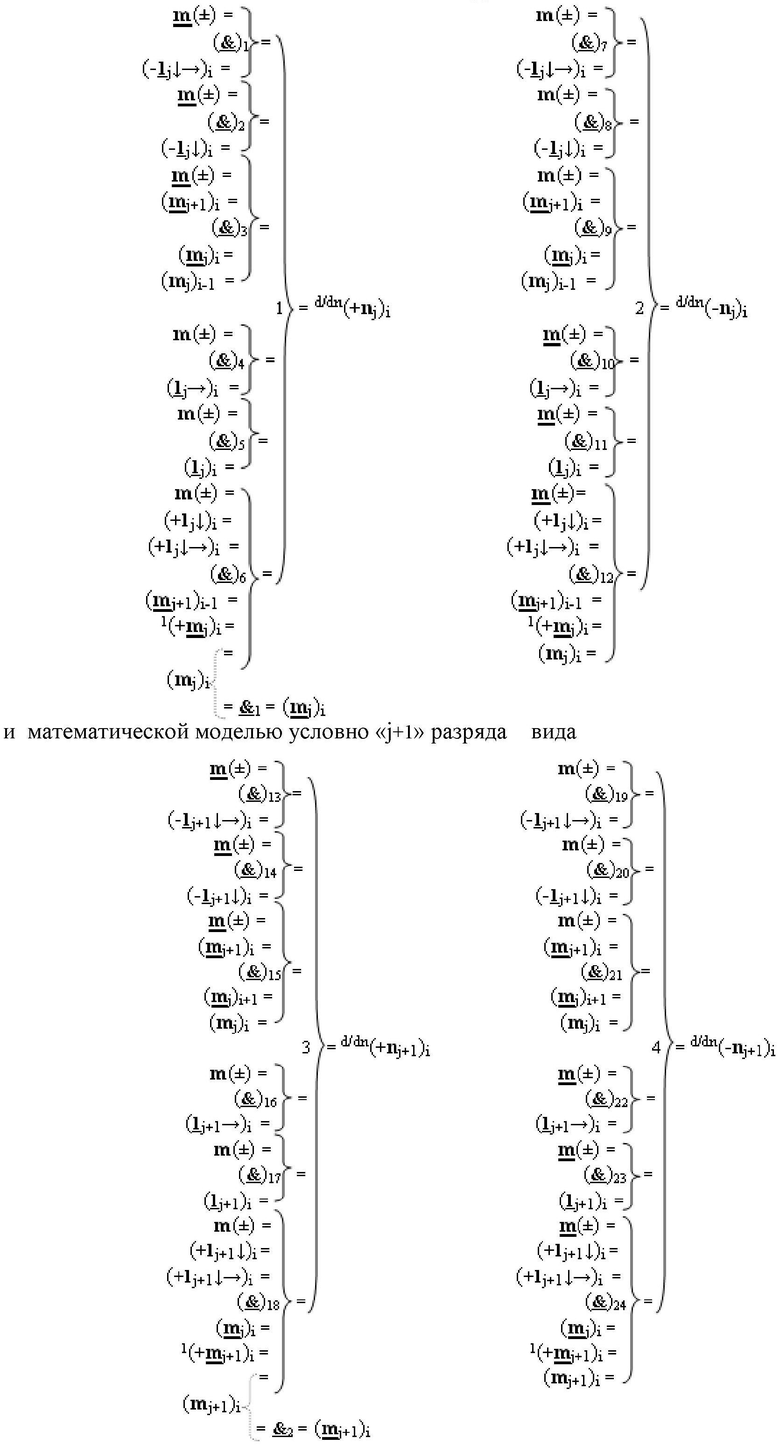

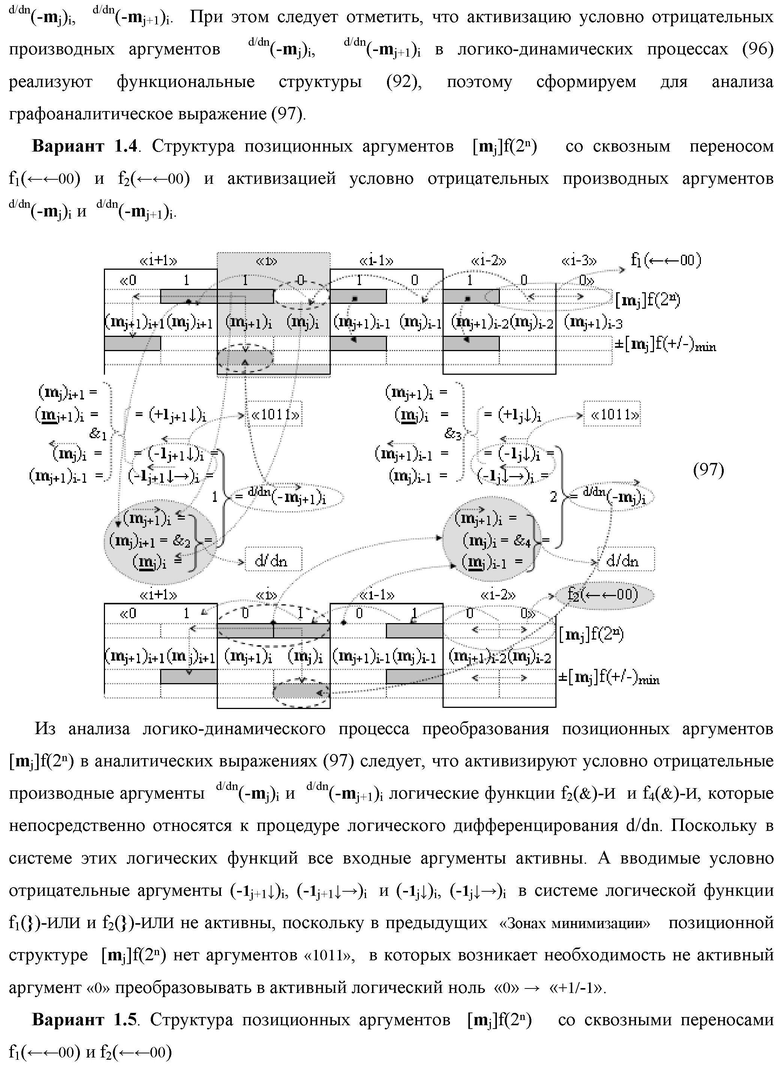

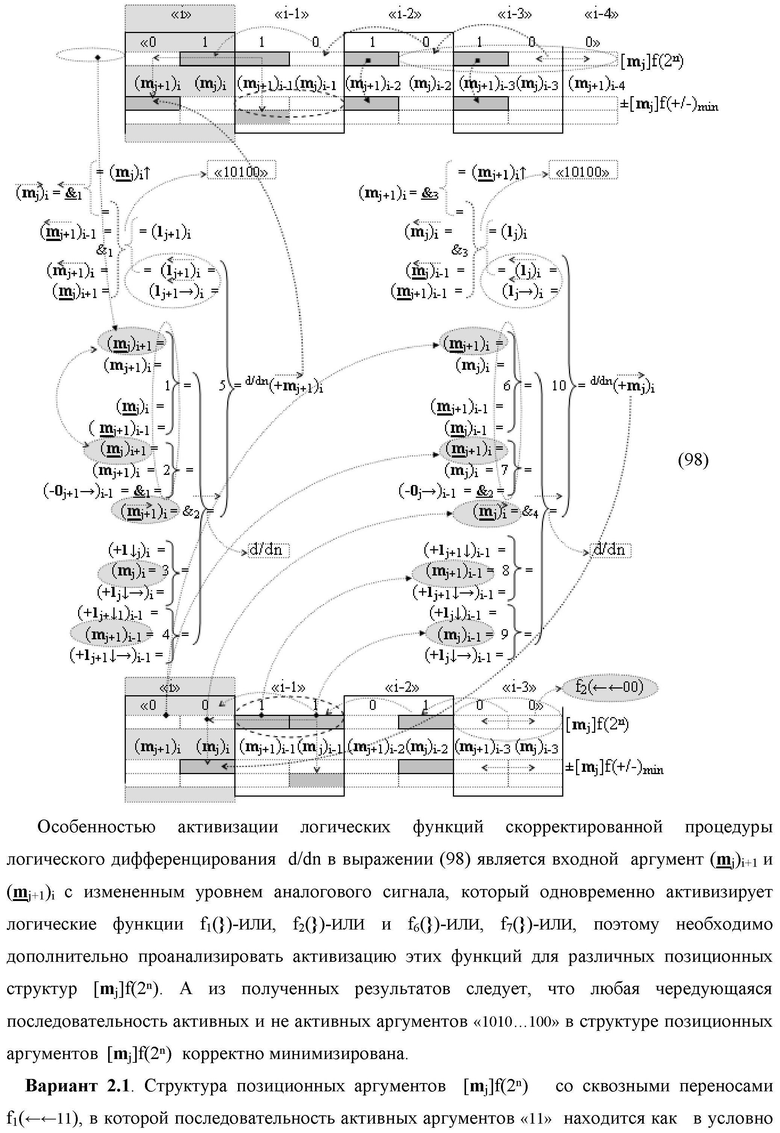

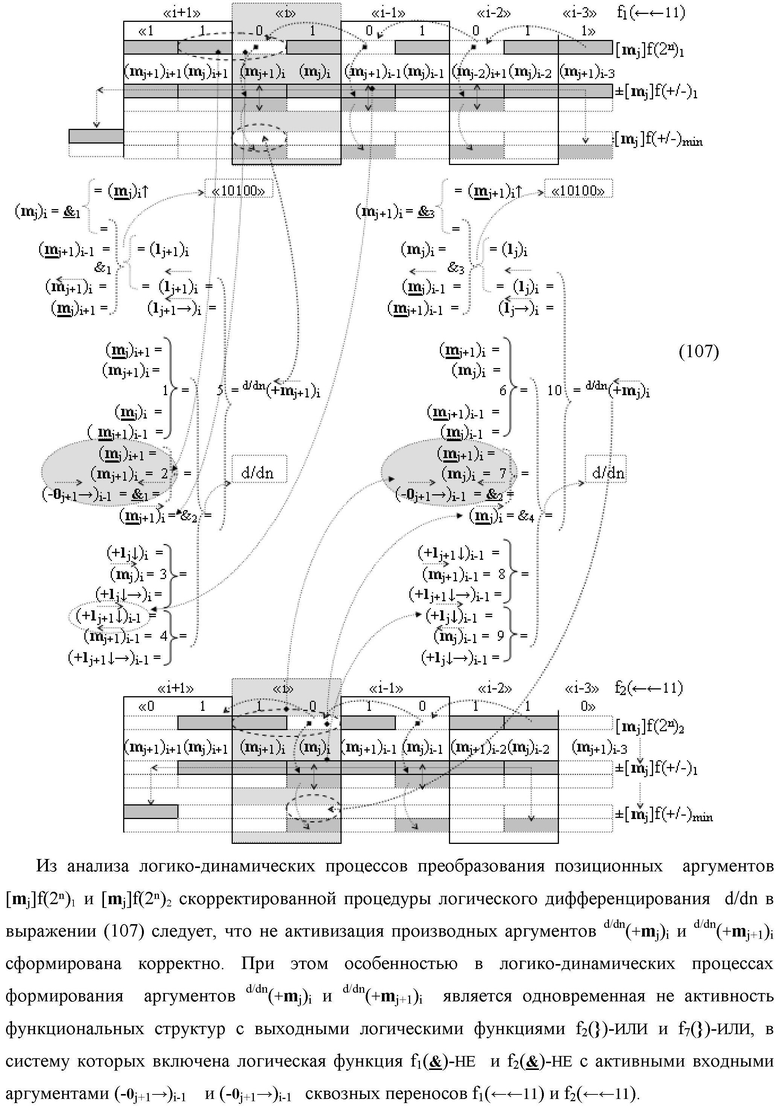

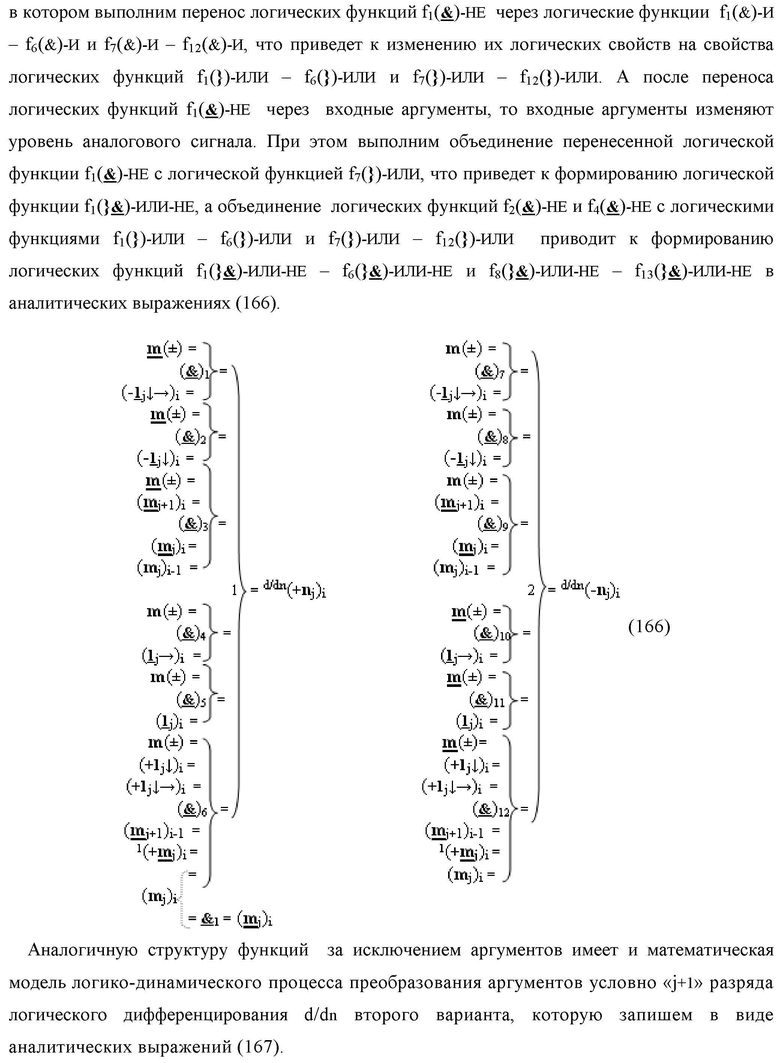

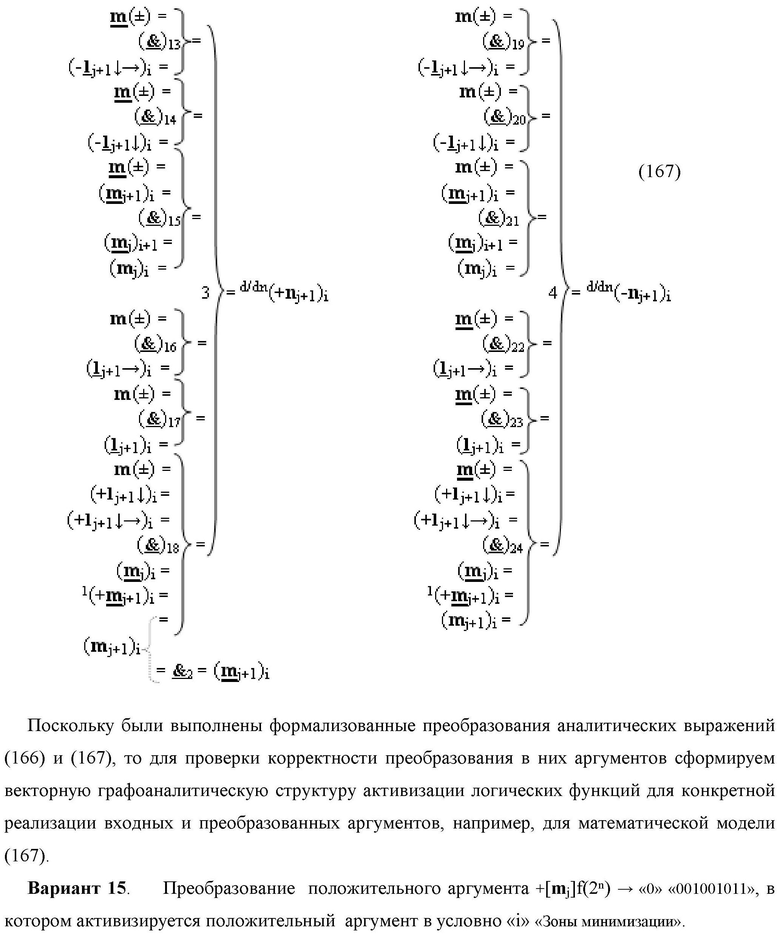

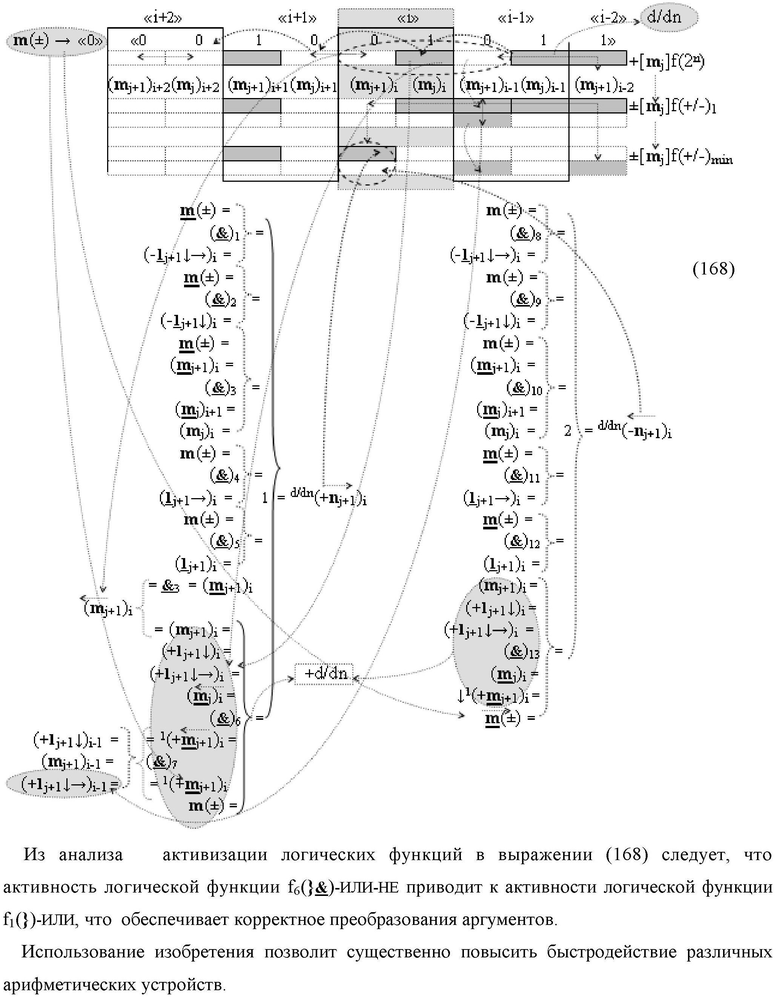

4. Функциональная структура процедуры логического дифференцирования d/dn позиционных аргументов [mj]f(2n) с учетом их знака m(±) для формирования позиционно-знаковой структуры ±[mj]f(+/-)min с минимизированным числом активных в ней аргументов, которая включает логическую функцию f(&)-HE для формирования аргумента знакового разряда m(±) с измененным уровнем аналогового сигнала и выполнена в виде положительного и условно отрицательного каналов условно «j» разряда и «j+1» разряда для преобразования входных аргументов [mj]f(2n) в условно «i» «Зоне минимизации», при этом положительный и условно отрицательный каналы двух разрядов содержит выходные логические функции f1(})-ИЛИ, f2(})-ИЛИ и f3(})-ИЛИ, f4(})-ИЛИ, в которых функциональные выходные связи являются функциональными выходными связями каналов для формирования положительного и условно отрицательного результирующих аргументов d/dn(+nj)i и d/dn(-nj)i «j» разряда и для формирования результирующих аргументов d/dn(+nj+1)i и d/dn(-nj+1)i «j+1» разряда, при этом положительные каналы включают логические функции f1(&)-HE и f2(&)-HE для приема аргументов (mj)i и (mj+1)i и формирования аргумента (m

j)i и (m

j+1)i с измененным уровнем аналогового сигнала, отличающаяся тем, что в положительный канал «j» и «j+1» разрядов введены логические функции f1(}&)-ИЛИ-НЕ, f2(}&)-ИЛИ-НЕ, f3(}&)-ИЛИ-НЕ, f4(}&)-ИЛИ-HE, f5(}&)-ИЛИ-НЕ, f6(}&)-ИЛИ-НЕ и f13(}&)-ИЛИ-НЕ, f14(}&)-ИЛИ-НЕ, f15(}&)-ИЛИ-НЕ, f16(}&)-ИЛИ-НЕ, f17(}&)-ИЛИ-НЕ, f18(}&)-ИЛИ-HE, а в условно отрицательный канал «j» и «j+1» разрядов введены логические функции f7(}&)-ИЛИ-НЕ, f8(}&)-ИЛИ-HE, f9(}&)-ИЛИ-НЕ, f10(}&)-ИЛИ-НЕ, f11(}&)-ИЛИ-НЕ, f12(}&)-ИЛИ-НЕ и f19(}&)-ИЛИ-НЕ, f20(}&)-ИЛИ-НЕ, f21(}&)-ИЛИ-НЕ, f22(}&)-ИЛИ-НЕ, f23(}&)-ИЛИ-НЕ, f24(}&)-ИЛИ-НЕ, при этом функциональные связи логических функций в каналах выполнены в соответствии с математической моделью условно «j» разряда вида

и математической моделью условно «j+1» разряда вида

где  - логическая функция f1(}&)-ИЛИ-НЕ.

- логическая функция f1(}&)-ИЛИ-НЕ.

| RU 2006144611 A, 20.06.2008 | |||

| RU 2006144612 A, 20.06.2008 | |||

| Преобразователь двоичного кода в позиционно-знаковый код | 1987 |

|

SU1438005A1 |

| Преобразователь двоичного кода в троичный код | 1983 |

|

SU1169172A1 |

| JP 57157350 A, 28.09.1982 | |||

| КАРЕТОЧНЫЙ УЗЕЛ ПЕДАЛЬНОГО ПРИВОДА ВЕЛОСИПЕДА | 0 |

|

SU180100A1 |

Авторы

Даты

2011-09-10—Публикация

2009-10-05—Подача