Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для определения интервала разбиения аргумента при проектировании частотно-импульсных функциональных преобразователей, и может быть использовано в измерительной технике в качестве устройства выбора диапазона при измерении частоты.

Наиболее близким по совокупности признаков и по технической сущности к заявляемому устройству является блок определения интервала (авторское свидетельство СССР №425174, МПК G06F 1/02, 1973), который обеспечивает формирование выходногог кода, пропорционального номеру интервала разбиения входной частоты; содержащий генератор образцовых частот, схему "ИЛИ", счетчик импульсов, импульсно-потенциальные схемы "И", регистр и элемент задержки; вход преобразуемой частоты Fx устройства подключен к генератору образцовых частот, выходы которого через схему "ИЛИ" связаны со входами счетчика импульсов, выходы разрядов которого подключены к потенциальным входам импульсно-потенциальных схем "И", соединенных своими выходами со входами триггеров регистра. Импульсные входы схем "И" через элемент задержки подключены ко входу Fx устройства, к которому подключена шина "Установка 0" счетчика импульсов. Выходы разрядов регистра, в котором образуется код интервала Nz, является выходом устройства.

Недостатками прототипа являются его ограниченные функциональные возможности, а именно схемно-конструктивно не предусмотрены возможность использования блока для реализации различных функциональных зависимостей выходного кода от номера интервала разбиения входной частоты и возможность обучения устройства на реализацию требуемой зависимости выходного кода от номера интервала входной частоты, так как он предназначен только для линейного определения интервала принадлежности входной частоты некоторому интервалу ее изменения.

Технический результат предлагаемого изобретения направлен на расширение функциональных возможностей, а именно на реализацию различных функциональных зависимостей выходного кода от номера интервала разбиения входной частоты, достигаемый за счет использования искусственной нейронной сети и блока ее обучения, обеспечивающих реализацию требуемой нелинейной зависимости выходного кода от номера интервала разбиения входной частоты. Использование блока памяти весовых коэффициентов для нейронной сети позволяет использовать одно и то же устройство для реализации различных различных функциональных зависимостей выходного кода от номера интервала разбиения входной частоты.

Технический результат достигается тем, что в блок определения интервала, содержащий генератор образцовых частот и выходной регистр, вход преобразуемой частоты Fx, вход опорной частоты преобразования F0 и выход результирующего кода Ny;

вводится блок памяти весовых коэффициентов, нейросетевой блок сравнения преобразуемой частоты с образцовыми, блок программируемых логических элементов, предназначенный для реализации логических функций "И", "ИЛИ", и блок обучения, вход тестовой последовательности; вход данных блока обучения соединен со входом тестовой последовательности, адресный вход блока памяти весовых коэффициентов соединен с шиной SA адреса весовых коэффициентов блока обучения, информационный вход блока памяти весовых коэффициентов соединен с шиной SD данных весовых коэффициентов блока обучения, вход разрешения записи блока памяти весовых коэффициентов соединен с выходом разрешения записи we блока обучения, выходы wi (i=1, 2, …, m) блока памяти весовых коэффициентов соединены со входами, задающими веса синаптических связей генератора образцовых частот, выходы θj (j=1, 2, …, m) блока памяти весовых коэффициентов соединены со входами, задающими пороговые значения блока сравнения преобразуемой частоты с образцовыми, выходы νp,r (р=1, 2, …, m, r=1, 2, …, k) блока памяти весовых коэффициентов соединены со входами, задающими тип реализуемой функции логических элементов блока программируемых логических элементов, предназначенного для реализации логических функций "И", "ИЛИ", вход эталонной частоты F0 преобразования соединен с частотным входом генератора образцовых частот, сигнал старт генератора образцовых частот соединен со входом преобразуемой частоты Fx, выходы генератора образцовых частот соединены с частотными входами нейросетевого блока сравнения преобразуемой частоты с образцовыми, вход преобразуемой частоты Fx соединен со входом преобразуемой частоты нейросетевого блока сравнения преобразуемой частоты с эталонными, выходы нейросетевого блока сравнения преобразуемой частоты с образцовыми соединены со входами логических элементов блока программируемых логических элементов, предназначенного для реализации логических функций "И", "ИЛИ", выходы программируемых логических элементов соединены со входами выходного регистра, вход съем соединен выходного регистра соединен со входом преобразуемой частоты Fx, выходы регистра являются выходами блока определения интервала.

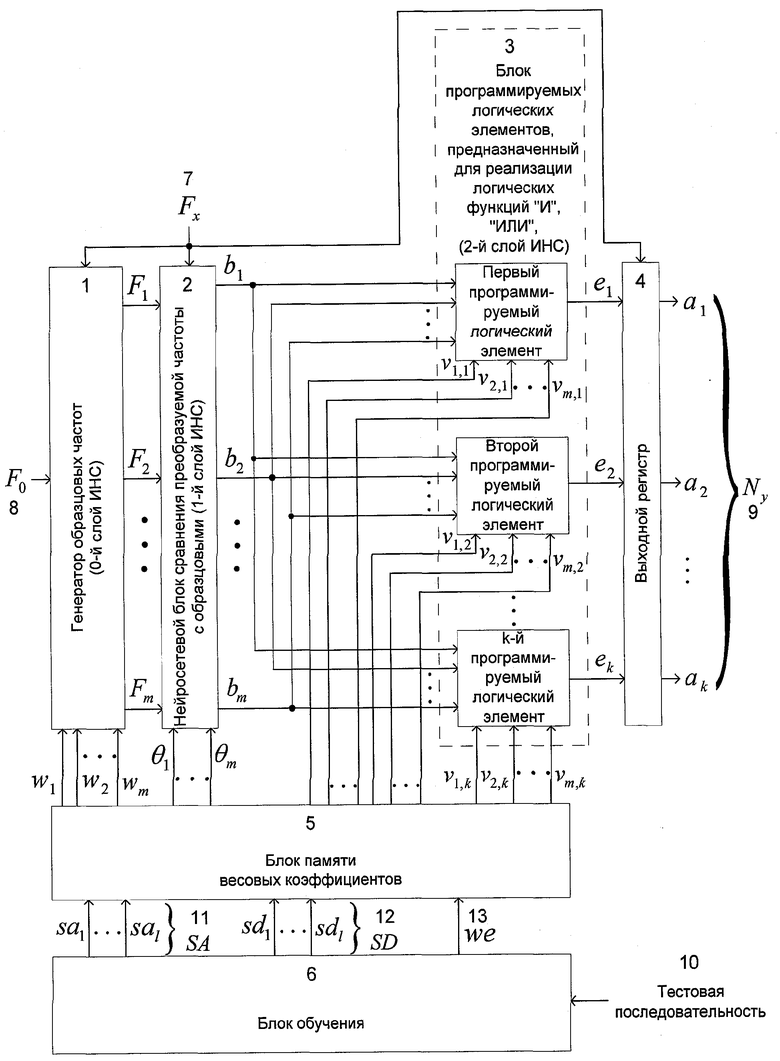

На чертеже представлена структурная схема предлагаемого устройства.

Нейросетевой блок определения интервала содержит генератор образцовых частот 1, нейросетевой блок сравнения преобразуемой частоты с образцовыми 2, блок программируемых логических элементов 3, предназначенный для реализации логических функций "И", "ИЛИ", выходной регистр 4, блок памяти весовых коэффициентов 5, блок обучения 6, вход преобразуемой частоты Fx 7, вход опорной (эталонной) частоты 8, выход результирующего кода Ny 9, вход тестовой последовательности 10, шину SA 11 адреса весовых коэффициентов блока обучения, шину SD 12 данных весовых коэффициентов блока обучения, выход разрешения записи we 13 блока обучения.

Генератор образцовых частот 1 является нулевым слоем искусственной нейронной сети устройства, являющейся двухслойным персептроном. Генератор образцовых частот 1 предназначен для формирования в течение каждого периода Тх входной частоты образцовых периодов T1, Т2, …, Тm, длительности которых обратно пропорциональны частотам F1, F2, …, Fm, соответствующим границам разбиения входного аргумента. Формирование периодов Т1, Т2, …, Тm осуществляется при помощи весовых коэффициентов w1, w2, …, wm, задающих веса синаптических связей для генератора образцовых частот 1: Ti=wi·T0 (i=1, 2, …, m), где Т0 - период эталонной частоты F0 преобразования. Задание различных значений коэффициентов wi (i=1, 2, …, m) позволяет использовать устройство для определения принадлежности входной частоты любым интервалам разбиения, которые можно изменять в ходе работы устройства.

Генератор образцовых частот 1 имеет входы эталонной частоты преобразования F0, входы коэффициентов wi (i=1, 2, …, m), задающих веса синаптических связей, вход старт и выходы частот Fi (i= 1, 2, …, m).

Нейросетевой блок сравнения преобразуемой частоты с образцовыми 2 предназначен для сравнения входной частоты Fx с частотными выходами генератора образцовых частот 1. Нейросетевой блок сравнения преобразуемой частоты с образцовыми 2 является первым слоем искусственной нейронной сети.

Нейросетевой блок сравнения преобразуемой частоты с образцовыми 2 имеет вход частоты Fx, для которой определяется интервал ее принадлежности, входы частот Fi (i=1, 2, …, m), входы θi (i=1, 2, …, m), задающие пороговые значения при сравнении частоты Fx с частотами Fi (i=1, 2, …, m), и логические выходы bi (i=1, 2, …, m), принимающие значения логического нуля или логической единицы.

Блок программируемых логических элементов 3, предназначенный для реализации логических функций "И", "ИЛИ", предназначен для формирования значений еj (j=1, 2, …, k) разрядов выходного кода Ny на основе логических переменных bi (i=1, 2, …, m). Блок программируемых логических элементов 3, предназначенный для реализации логических функций "И", "ИЛИ", является вторым (выходным) слоем искусственной нейронной сети. Блок программируемых логических элементов 3, предназначенный для реализации логических функций "И", "ИЛИ", состоит из k программируемых логических элементов. Программируемый логический элемент при помощи коэффициентов νij программируется на реализацию требуемой логической функции (например: 2-входовое логическое "ИЛИ", 2-входовое логическое "И", 2-входовое логическое "И" с одним прямым и с одним инверсным входом, 3-входовое логическое "ИЛИ" и т.д.). Программируемый логический элемент может быть, например, реализован на таблицах преобразования (Look-Up-Tables) программируемых логических интегральных схем.

Каждый j-й программируемый логический элемент имеет входы логических переменных bi (i=1, 2, …, m), входы коэффициентов νij (i=1, 2, …, m), задающих веса синаптических связей для второго слоя нейронной сети, и выход разряда еj выходного кода Ny.

Выходной регистр 4 предназначен для запоминания текущего значения результирующего кода Ny=a1a2 … ak (где a1, а2, …, ak - разряды кода Ny) до окончания следующего цикла определения интервала.

Входной регистр 4 имеет входы e1, е2, …, ek разрядов кода, выходы а1, а2, …, ak разрядов кода и вход съем.

Блок памяти весовых коэффициентов 5 предназначен для хранения коэффициентов, задающих веса wi (i=1, 2, …, m) и νij (i=1, 2, …, m, j=1, 2, …, k) синаптических связей искусственной нейронной сети и пороги θi (i=1, 2, …, m) ее нейронов.

Блок памяти весовых коээфициентов 5 имеет адресную входную шину, шину данных и вход разрешения записи, а также выходы коэффициентов, задающих веса wi (i=1, 2, …, m) синаптических связей генератора образцовых частот, выходы коэффициентов, задающих веса νij (i=1, 2, …, m, j=1, 2, …, k) синаптических связей между нейросетевым блоком сравнения преобразуемой частоты с образцовыми и блоком программируемых логических элементов, предназначенным для реализации логических функций "И", "ИЛИ", и выходы, задающие пороги θi (i=1, 2, …, m) нейронов нейросетевого блока сравнения преобразуемой частоты с образцовыми.

Блок обучения 6 предназначен для обучения нейронной сети блока определения интервала на реализацию требуемой функции разбиения входной частоты на ее диапазоны.

Блок обучения 6 имеет вход тестовой последовательности, выходную адресную шину, выходную шину данных и выход разрешения записи.

Нейросетевой блок определения интервала содержит генератор образцовых частот 1, нейросетевой блок сравнения преобразуемой частоты с образцовыми 2, блок программируемых логических элементов 3, предназначенный для реализации логических функций "И", "ИЛИ", выходной регистр 4, блок памяти весовых коэффициентов 5, блок обучения 6, вход преобразуемой частоты 7, вход опорной (эталонной) частоты преобразования 8, выход результирующего кода 9 и вход тестовой последовательности 10. Вход преобразуемой частоты Fx 7 нейросетевого блока определения интервала одновременно является входом преобразуемой частоты нейросетевого блока сравнения преобразуемой частоты с эталонными, входом старт генератора образцовых частот 8 и входом съем выходного регистра 4. Вход опорной (эталонной) частоты F0 8 нейросетевого блока определения интервала одновременно является входом опорной (эталонной) частоты генератора образцовых частот 1. Выходы Fi (i=1, 2, …, m) генератора образцовых частот 1 соединены с соответствующими частотными входами нейросетевого блока сравнения преобразуемой частоты с образцовыми 2. Выходы wi (i=1, 2, …, m) блока памяти весовых коэффициентов 5 соединены со входами, задающими веса синаптических связей генератора образцовых частот 1. Выходы θj (j=1, 2, …, m) блока памяти весовых коэффициентов 5 соединены со входами, задающими пороговые значения нейросетевого блока сравнения преобразуемой частоты с образцовыми 2. Выходы νp,r (р=1, 2, …, m, r=1, 2, …, k) блока памяти весовых коэффициентов 5 соединены со входами, задающими тип реализуемой функции логических элементов блока программируемых логических элементов 3, предназначенного для реализации логических функций "И", "ИЛИ". Каждый выход bi (i=1, 2, …, m) нейросетевого блока сравнения преобразуемой частоты с образцовыми 2 соединен со входом каждого логического элемента блока программируемых логических элементов 3, предназначенного для реализации логических функций "И", "ИЛИ". Выходы ej (j=1, 2, …, k) программируемых логических элементов блока программируемых логических элементов 3, предназначенного для реализации логических функций "И", "ИЛИ", соединены со входами выходного регистра 4. Выходы выходного регистра 4 являются выходами блока определения интервала и значениями разрядов aj (j=1, 2, …, k) выходного кода Ny 9 нейросетевого блока определения интервала. Вход данных блока обучения соединен со входом тестовой последовательности 12. Адресный вход блока памяти весовых коэффициентов 5 соединен с шиной SA 11 адреса весовых коэффициентов блока обучения 6. Информационный вход блока памяти весовых коэффициентов 5 соединен с шиной SD 12 данных весовых коэффициентов блока обучения 6. Вход разрешения записи блока памяти весовых коэффициентов 5 соединен с выходом разрешения записи we 13 блока обучения 6.

Нейросетевой блок определения интервала работает следующим образом.

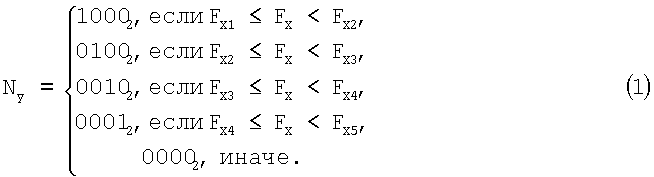

Пусть число разрядов к выходного кода нейросетевого блока определения интервала равно четырем. Тогда количество программируемых логических элементов блока программируемых логических элементов, предназначенного для реализации логических функций "И", "ИЛИ", также равно четырем. Такое устройство позволяет определить принадлежность входной частоты Fx 7 одному из четырех диапазонов. При этом выходной код Ny 9 примет следующие значения:

Для реализации зависимости (1) нейросетевой блок определения интервала должен быть обучен при помощи блока обучения 6. Обучения осуществляется при помощи подачи тестовой последовательности 10. Тестовая последовательность состоит из последовательно подаваемых значений входной частоты Fx 7 и соответствующих этим значениям значений выходного кода Ny 9. Пример тестовой последовательности приведен в таблице 1. Объем тестовой последовательности влияет на точность обучения. Чем больше тестовая последовательность, тем точнее обучения устройства на реализацию зависимости выходного кода Ny 9 от входной частоты Fx 7.

Блок обучения 6 может быть реализован, например, на внешней или внутренней плате расширения персонального компьютера.

При подаче тестовой последовательности 10 на вход блока обучения 6 начинается операция обучения. По окончании операции обучения осуществляется запись новых значений весовых коэффициентов и порогов нейронов в блок памяти весовых коэффициентов 5. Для этого на вход подтверждения записи блока памяти весовых коэффициентов 5 с выхода we 13 блока обучения 6 подается значение we=1. На вход шины адреса блока памяти весовых коэффициентов 5 с выхода SA 11 блока обучения 6 подается адрес соответствующего весового коэффициента. При этом на шину данных SD 12 подается значение весового коэффициента.

По шинам wi (i=1, 2, …, m), θj (j=1, 2, …, m) и νp,r (р=1, 2, …, m, r=1, 2, …, k) значения весовых коэффициентов и порогов нейронов подаются на соответствующие блоки устройства.

На вход Fx 7 устройства подаются частота, номера интервала принадлежности которой следует определить. На вход F0 8 подается опорная (эталонная) частота. Генератор образцовый частот 1 формирует частоты Fi (i=1, 2, …, m) со следующими периодами Ti (i=1, 2, …, m):

Ti=wi·T0,

где i=1, 2, …, m, T0=1/F0.

Частоты Fi (i=1, 2, …, m) будут начинать формировать по приходу импульса входной частоты Fx 7. Таким образом задается начало цикла определения интервала.

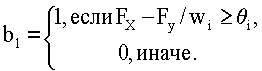

Элементы нейросетевого блока сравнения осуществляют операции сравнения следующего вида, в результате которых формируются значения bi (i=1, 2, …, m):

Элементы блока программируемых логических элементов 3, предназначенного для реализации логических функций "И", "ИЛИ", формируют значения ej (j=1, 2, …, k), которые являются промежуточными результатами формирования выходного кода. Так, например, значение e1 может быть вычислено следующим образом:

e1=b1 and(not b2), если ν1,1=1 и ν2,1=-1.

По приходу импульса входной частоты Fx 7 на вход съем выходного регистра 5 осуществляется запись значений еj (j=1, 2, …, k) в выходной регистр 5 путем формирования выходного кода Ny 9, равного Ny=a1a2…ak. Цикл преобразования на этом завершается.

Таким образом, применение предлагаемого нейросетевого блока определения интервала позволяет расширить функциональные возможности, а именно реализовать функциональное преобразование входной частоты в номер ее интервала изменения, а также позволяет повысить интеллектуальные способности устройства, заключающиеся в возможности реализации одним блоком нескольких функциональных зависимостей.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОСЕТЕВОЙ ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2009 |

|

RU2420804C1 |

| НЕЙРОСЕТЕВОЙ ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2013 |

|

RU2540823C1 |

| Нейропроцессор (NPU) | 2024 |

|

RU2825124C1 |

| Автоматический нейросетевой настройщик параметров ПИ-регулятора для управления нагревательными объектами | 2016 |

|

RU2644843C1 |

| НЕЙРОСЕТЕВОЙ ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2008 |

|

RU2380752C2 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 2006 |

|

RU2321946C1 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОПЕРАТОРОВ | 2005 |

|

RU2281561C1 |

| Система оперативной идентификации морских целей по их информационным полям на базе нейро-нечетких моделей | 2021 |

|

RU2763384C1 |

| Система обнаружения и классификации морских целей на базе нейросетевых технологий и элементов искусственного интеллекта | 2021 |

|

RU2780607C1 |

| УСТРОЙСТВО РЕГУЛИРОВАНИЯ ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА | 2011 |

|

RU2465716C1 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для определения интервала разбиения аргумента при проектировании частотно-импульсных функциональных преобразователей, и может быть использовано в измерительной технике в качестве устройства выбора диапазона при измерении частоты. Технический результат заключается в расширении функциональных возможностей за счет реализации нелинейной операции определения интервала входной частоты с использованием искусственной нейронной сети, обучаемой при помощи блока обучения, а также за счет реализации различных нелинейных зависимостей выходного кода от интервалов разбиения входной частоты. Наличие блока памяти весовых коэффициентов искусственной нейронной сети позволяет использовать один нейросетевой блок определения интервала для реализации нескольких функциональных зависимостей выходного кода от интервалов разбиения входной частоты. 1 ил., 1 табл.

Нейросетевой блок определения интервала, содержащий генератор образцовых частот и выходной регистр, вход преобразуемой частоты, вход опорной частоты преобразования и выход результирующего кода, отличающийся тем, что в устройство введены блок памяти весовых коэффициентов, нейросетевой блок сравнения преобразуемой частоты с образцовыми, блок программируемых логических элементов, предназначенный для реализации логических функций И, ИЛИ, и блок обучения, вход тестовой последовательности; вход данных блока обучения соединен со входом тестовой последовательности, адресный вход блока памяти весовых коэффициентов соединен с шиной SA адреса весовых коэффициентов блока обучения, информационный вход блока памяти весовых коэффициентов соединен с шиной SD данных весовых коэффициентов блока обучения, вход разрешения записи блока памяти весовых коэффициентов соединен с выходом разрешения записи we блока обучения, выходы wi(i=l, 2, …, m) блока памяти весовых коэффициентов соединены со входами, задающими веса синаптических связей генератора образцовых частот, выходы θj(j=1, 2, …, m) блока памяти весовых коэффициентов соединены cо входами, задающими пороговые значения блока сравнения преобразуемой частоты с образцовыми, выходы νp,r(p=1, 2, …, m, r=1, 2, …, k) блока памяти весовых коэффициентов соединены со входами, задающими тип реализуемой функции логических элементов блока программируемых логических элементов, предназначенного для реализации логических функций И, ИЛИ, вход опорной (эталонной) частоты F0 преобразования соединен со входом опорной (эталонной) частоты генератора образцовых частот, вход старт генератора образцовых частот соединен со входом преобразуемой частоты, выходы генератора образцовых частот соединены с частотными входами нейросетевого блока сравнения преобразуемой частоты с образцовыми, вход преобразуемой частоты Fx соединен со входом преобразуемой частоты нейросетевого блока сравнения преобразуемой частоты с эталонными, выходы нейросетевого блока сравнения преобразуемой частоты с образцовыми соединены со входами логических элементов блока программируемых логических элементов, предназначенного для реализации логических функций И, ИЛИ, выходы программируемых логических элементов соединены со входами выходного регистра, вход съем выходного регистра соединен со входом преобразуемой частоты, выходы регистра являются выходами блока определения интервала.

| БЛОК ОПРЕДЕЛЕНИЯ ИНТЕРВАЛА | 1972 |

|

SU425174A1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРА РАЦИОНАЛЬНОГО ВАРИАНТА | 2001 |

|

RU2202822C1 |

| Устройство для контроля и диагностики состояний объекта | 1989 |

|

SU1679468A1 |

| Устройство для измерения защищенности сигнала от помех | 1989 |

|

SU1658400A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| US 5428710 А, 27.06.1995. | |||

Авторы

Даты

2010-02-20—Публикация

2008-08-29—Подача