Изобретение относится к электронно-вычислительной технике и может эксплуатироваться при создании программно-аппаратных комплексов для автоматизированных систем управления технологическими процессами в горно-промышленной и нефтегазовой отрасли, в частности автоматизации теплообменных модулей аппаратов воздушного охлаждения, входящих в состав автоматизированных систем управления (АСУ) местного проветривания, где требуется оперативная организация данных при работе с постоянной энергонезависимой памятью плат управления промышленными объектами. Техническим результатом является повышение качества переходных процессов регулирования на основе нейро-нечеткого и адаптивного управления. Устройство включает в себя подсистему управления, буферный и выходной регистры, блок связи с исполнительными устройствами или ЭВМ верхнего уровня, постоянное запоминающее устройство (ПЗУ), умножители, сумматор, векторный процессор (ВП), блок автокодирования (АК), функцией активации нейросети является функция Leaky ReLU.

На сегодняшний день в горной и нефтегазовой промышленности все более широкое распространение получают автоматизированные системы управления технологическими процессами на основе нейро-нечеткого и адаптивного управления, способные без участия антропогенного фактора осуществлять регулирование переходных процессов, обрабатывать и конвертировать полученные данные, интерпретировать из исходных данных новые, наиболее оптимальные. Такие системы позволяют существенно сократить затраты на обслуживающий персонал, но требуют высокой квалификации в теории фаззификации данных и алгоритмах управления нечеткими системами.

Наряду с электронно-вычислительными устройствами систем автоматизированного управления (программируемыми логическими контроллерами, датчиками и исполнительными модулями) для аппаратного ускорения работы нейронных сетей применяются нейронные процессоры (NPU).

В задачах автоматизации дожимных компрессорных станций (ДКС) особое внимание должно уделяться времени задержки сигнала и подбору значений коэффициентов как пропорционально-интегрально-дифференциальных регуляторов (ПИД), так и регуляторов, основанных на аппарате нечеткой логики (Fuzzy Controller).

Центральная предельная теорема говорит, что в большинстве случаев отобранные коэффициенты нейросетью распределяются, как правило, распределением Гаусса (нормальным распределением случайной величины), основная проблема заключается в оптимизации и «отсекании» ненужных нейронных связей, вносящих энтропию в распределение и неудовлетворяющих требованиям модели обучения при задачах бинарной классификации и линейной регрессии, а также проблеме затухания градиента, когда градиенты слишком малы и вносят малый вес в обучение нейросети, а также проблему расслоения (кластеризации) нейронов, при которой нейронами учитываются только положительные значения, а отрицательные отсекаются.

По нейронным вычислителям известен нейропроцессор, содержащий блок управления, устройство ввода-вывода, сумматор и некоторую функцию активации [1] (См. статью А.Н. Горбань «Обобщенная апроксимационная теорема и вычислительные возможности нейронных сетей» / Сибирский журнал вычислительной математики 1998, Т1, №1, с. 12-24).

Однако данный нейропроцессор отличается отсутствием в составе аппаратных умножителей и средств задания коэффициентов для «обучения» сети, что является обязательным требованием при настройке вычисления конкретной функции. В противном случае быстрый расчет тригонометрических функций не представляется возможным. Следует также отметить, что в предложенных вариантах отсутствует рациональная организация работы энергонезависимой памяти с управляющим устройством связи и выходным регистром, что несет в себе проблему дополнительной латентности (задержки обмена данными), что увеличивает время вычисления функций. Кроме того, в силу отсутствия привязки к конкретной функции активации нейросети для тех или иных методов настройки полученные матричные значения на выходе могут иметь в себе совокупность неверных либо неточных значений коэффициентов.

Наиболее близким по исполнению к предлагаемому техническому решению является нейропроцессор, содержащий сумматор, блок связей, буферный и выходной регистры, умножители, блок управления [2].

В данном нейропроцессоре блок связи служит для обмена данным с центральным процессором верхнего уровня по двунаправленной шине. Нейропроцессор имеет управляющее устройство, буферный регистр для хранения аргумента, постоянное запоминающее устройство для хранения коэффициентов обучения (настройки) процессора, n-последовательно включенных умножителей для аргументов, сумматор значений и выходной регистр для записи значения вычисленной функции, выход которого является выходом процессора.

После включения питания в устройстве управления начинают работать задающие генераторы и формирователи, и через несколько (3-4) периодов высокой частоты на выход поступают сфазированные, прошедшие мажоритар, синхроимпульсы.

В соответствии с кодами, записанными в регистры 21-23 и счетчик 24, начальными значениями адреса из накопителя 25 начинают выбираться коды микрокоманд, которые после буферных элементов 26 начинают поступать на блоки процессора, а одновременно с ними из формирователей 28, пройдя мажоритар 29, в блоки начинают поступать синхроимпульсы. В запоминающем устройстве 4 записаны весовые коэффициенты для задания весов входов каждого слоя нейропреобразователей для разных функций.

После получения в блок связи значения аргумента и типа функции происходит перезапись по микропрограммным сигналам, начинающим поступать из накопителя 25, значения аргумента в буферный регистр 3 и кода операции в регистр 22 устройства управления, а также остальных начальных значений в остальные регистры, и счетчик для формирования первого адреса выборки микрокоманд из накопителя 25, дальнейшие адреса формируются как комбинация кодов, записанных в текущей микрокоманде и поступающих в регистр базы адреса и регистр смещения 21 совместно с внешними сигналами, обеспечивающими переход на ветки микропрограммы по условиям, которыми, в частности, являются контрольные сигналы запоминающего устройства 4.

В первом умножителе 5-1 производится умножение аргумента самого на себя, т.е. появляется значение х2, на втором умножителе происходит умножение полученного значения на аргумент, т.е. появляется третья степень аргумента х3. Далее происходит получение следующих степеней аргумента в соответствии с требуемой точностью. Полученные значения поступают на входы сумматора 6, на настроечные входы которого поступают значения весовых коэффициентов из запоминающего устройства 4.

В результате на выходе сумматора появляется значение вычисленной функции, которое может быть считано из выходного регистра 7. Такое построение обеспечивает достаточно быстрое вычисление функции, так как времена определяются только задержками комбинационных элементов умножителя и сумматора, которые при их реализации в виде БИС достаточно малы, так, например, при использовании в качестве умножителя БИС 1825 ВР5, а в качестве сумматора БИС 1825 ВСЗ функция sinx вычисляется за 2 мкс против нескольких миллисекунд при вычислении по программе бортовой вычислительной машины, что обеспечивает требуемую скорость решения задач БИНС.

Кроме того, введение резервирования накопителей ЗУ с контролем их исправности схемой сравнения 33 и определением места отказа с помощью контрольного суммирования массивов коэффициентов сумматорами 32-1 и 32-2 с последующим выбором исправного накопителя по микропрограмме в устройстве управления и подключении к выходу сигналов исправного накопителя позволяет нейтрализовать определенные отказы катастрофического характера в одном из основных узлов нейропроцессора - его запоминающем устройстве коэффициентов.

А наличие связи этого ЗУ через блок связи 1 с внешней подсистемой позволяет проводить настройку («обучение») процессора вычисления различных функций, что может быть сделано как на заводе-изготовителе аппаратуры, так и в процессе работы по программе бортовой вычислительной машины, а наличие контроля с отключением накопителя с искаженными коэффициентами исключает «переобучение» нейропроцессора.

Для сохранения работоспособности процессора и, более того, подбора оптимального для текущего состояния цифровых элементов быстродействия в блоке управления реализован режим перестройки частоты, для чего введено управление задающими генераторами заданием кодов требуемой частоты в счетчик кода частоты 45 и регистр кода частоты 4.

Поддержание требуемого номинала, выбранного, например, на основе проведения тестовых проверок, происходит автоматически изменением значения счетчика 45 по сигналам схемы сравнения, сравнивающей текущее значение частоты, определяемое счетчиком 44, со значением, заданным в регистр 47. Таким образом, предложенные решения позволяют не только существенно, примерно на порядок, сократить время вычисления функций, но и проводить изменение вида вычисляемых функций «обучением» процессора путем записи нужных массивов коэффициентов в запоминающее устройство 4.

Недостатком данной компоновки функциональной схемы нейропроцессора-прототипа является отсутствие вспомогательных модулей для быстрой организации работы памяти между управляющим устройством (УУ), постоянным запоминающим устройством (ПЗУ) и выходным регистром (ВР), а также дополнительных подсистем, повышающих на выходе качество обработки входных данных, способных обеспечить большее количество новых выходных значений функции активации. Кроме того, не детерминирована функция активации нейросети, от которой зависит качество переходного процесса обучения, что может существенно сказаться на производительности и качестве обрабатываемых данных в исходном прототипе.

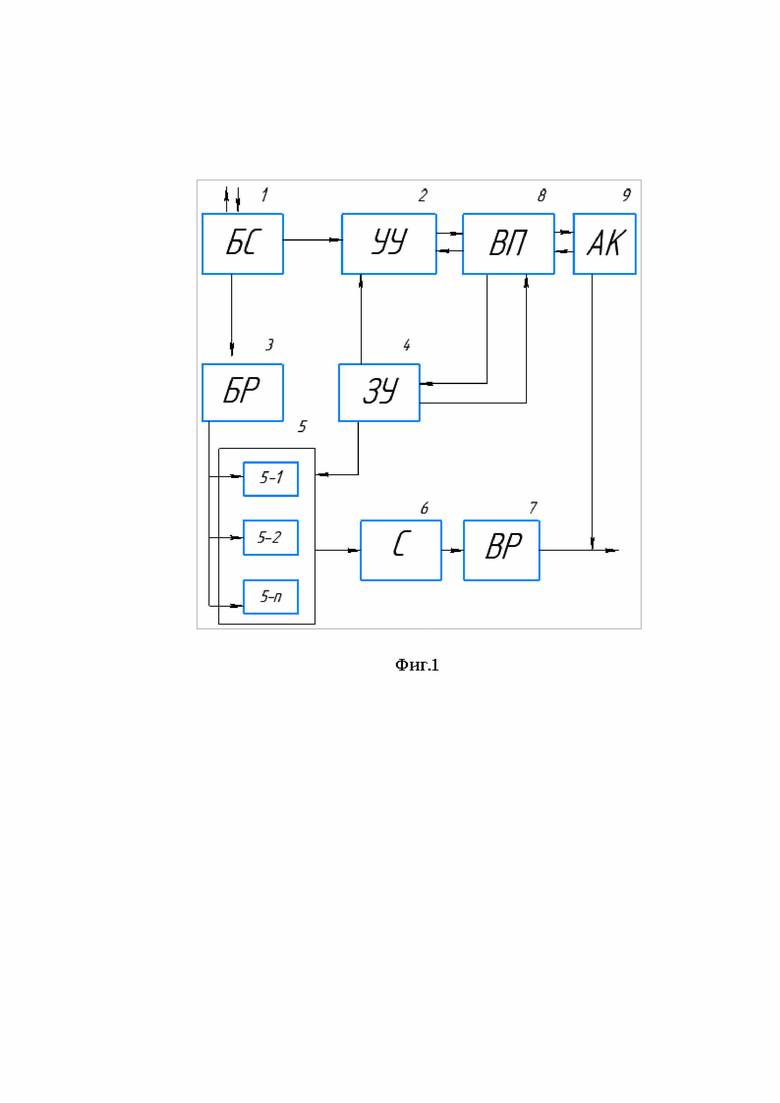

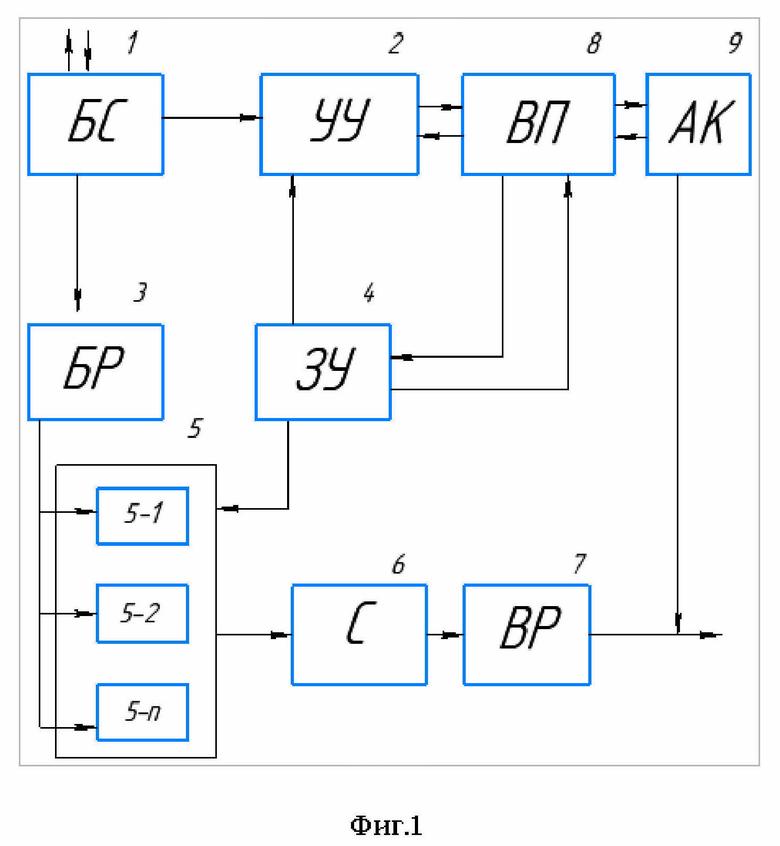

Цель изобретения заключается в обеспечении акселерации работы подсистемы энергонезависимой памяти за счет интеграции блока векторного процессора и аппаратного декодировщика. Для устранения данных недостатков предложена функциональная схема нейропроцессора, представленная на фиг. 1.

Указанная цель достигается тем, что в предложенном нейропроцессоре, содержащем блок связи (1), соединяющий нейропроцессор с главным процессорным модулем по двунаправленной шине, управляющее устройство (2), служащее для обмена данными между векторным процессором и запоминающим устройством, буферный регистр (3), служащий для хранения значений аргумента функций, запоминающее устройство (4) для хранения значений коэффициентов настройки процессора, умножители-мультиплексоры (5) для вычисления гиперпараметров функций, сумматор (6) для агрегирования данных на входе и поступлению этих данных на обработку функцией активации, выходной регистр (7), служащий для вывода итоговых матричных коэффициентов из нейросети.

Дополнительно интегрированы блок векторного процессора (8), служащего для акселерации работы подсистемы памяти, и блок автокодирования (9) для кодирования и декодирования данных в ПЗУ после обработки векторным процессором с целью оптимизации нейронов при обучении.

Кроме того, в топологической компоновке также строго детерминирована функция активации сети (Leaky ReLU), от которой зависит качество переходного процесса на выходе и точные матричные коэффициенты, решается проблема кластеризации нейронов, проблема затухания градиента.

Блоки векторного процессора (8) и автокодировщика (9) нейропроцессора работают следующим образом.

Операционное устройство векторного процессора (OU) выполняет арифметические и логические операции над словами и матрицей весов WOPER, значение весовых коэффициентов которой хранится в постоянном запоминающем устройстве (4). Циклический сдвигатель векторного процессора (RCS) сдвигает полученное слово вправо на один разряд. Векторный контроллер содержит узлы SU1, SU2, реализующие функцию активации (насыщения) над полученными при передаче словами. Память весовых коэффициентов имеет емкость M×N бит и позволяет хранить весовые коэффициенты, используя специальный регистр WBUF, служащий для подкачки извне новой весовой матрицы на фоне выполнения операций суммирования с использованием прежней весовой матрицы, которая хранится в WOPER. Такой механизм организации работы с памятью NPU позволяет осуществлять прямую адресацию, способствующую ускоренному чтению и записи в обоих направлениях при обмене, как с векторным процессором, так и с управляющим устройством (2), например, центральным процессором с уменьшенной предвыборкой данных (RISC-процессором).

Блок автокодировщика-автоэнкодера (9) получает на выходе блока (8) упакованные данные значений функции активации, выполняет их кодирование и декодирование. Такая надстройка позволяет повысить количество верных разностных решений, генерируемых нейросетевым алгоритмом, но в то же время не меняя качества полученных данных для нейронов от искусственных синапсов и значений весовых коэффициентов.

Из сумматора (6) агрегируются значения нейронов и формируются в аппроксимационную зависимость функции активации, известную как функцию Leaky ReLU, далее значения после обработки попадают в выходной регистр (7) в виде значений матричных коэффициентов.

Ключевой особенностью применения функции Leaky ReLU для задач бинарной классификации и линейной регрессии, применяемой при настройке коэффициентов программно-аппаратных комплексов аппаратов воздушного охлаждения газа на магистральных газопроводах, является способность оптимизировать задачу затухания градиента (в отличие от обычной функции RelU, градиенты не так малы и не мешают обрабатывать нейронной сети максимальное количество полезных данных).

Кроме того, данная кривая при обучении способна учитывать как положительные коэффициенты обученных нейронов, так и отрицательные, что априори решает проблему кластеризации нейронов. Основным преимуществом является то, что повышается качество обучения, что напрямую обуславливает достоверность полученных данных и способствует достижению заданного статистического распределения с минимальными квадратичными отклонениями.

Технический эффект рациональной организации подсистемы памяти позволяет рассчитывать функцию f(x)=sin(x) не более чем за 1,7 микросекунд по сравнению с существующим изобретением, где t=2 мкс.

Блок автокодирования и строго детерминированная функция активации под конкретную цель позволяют добиться до 25-30% лучшего качества полученных матричных значений на выходе, а следовательно, повышают точность регулирования переходных процессов при управлении сложным технологическим объектом (аппаратом воздушного охлаждения местного проветривания с теплообменным модулем).

Таким образом, предложенное решение по модернизации существующего нейропроцессора позволяет сократить время на обработку и вычисление значений коэффициентов функции активации благодаря добавлению в функциональную структуру блоков векторного процессора и автокодировщика, что позволило наиболее рационально организовать обмен данными между постоянным запоминающим устройством, управляющим устройством и выходным блоком, а так же расширить область генерации решений для функции активации на выходе нейронного процессора.

Для аппаратов воздушного охлаждения газа, применяемых на ДКС, нейропроцессор в составе системы автоматизации с программируемым логическим контроллером (ПЛК) за счет повышения быстродействия между обменом данными уровня PLC-NPU (программируемый контроллер-нейропроцессор) и модернизированной организацией подсистемы энергонезависимой памяти (EEPROM память) позволит увеличить скорость транзакции пакетов данных на 10-15% и позволит сократить время на обработку переходного процесса регулирования на 0,3-0,45 сек, что является критически важным и эффективным преимуществом при организации работы такого сложного технологического объекта.

Эти особенности процессора делают его более предпочтительным вариантом по сравнению с другими известными решениями.

Источники информации:

1. А.Н. Горбань «Обобщенная апроксимационная теорема и вычислительные возможности нейронных сетей» / Сибирский журнал вычислительной математики 1998.

2. Патент РФ 2011143912/08, 28.10.2011. Антимиров В.М. Нейропроцессор // Патент России № 2473126. 2011. Бюл. № 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОПРОЦЕССОР | 2011 |

|

RU2473126C1 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| Способ управления реакцией нейропроцессора на входные сигналы | 2018 |

|

RU2724784C2 |

| АНАЛОГОВАЯ АППАРАТНАЯ РЕАЛИЗАЦИЯ НЕЙРОННЫХ СЕТЕЙ | 2020 |

|

RU2796649C2 |

| УСТРОЙСТВО РЕГУЛИРОВАНИЯ ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА | 2011 |

|

RU2465716C1 |

| Оценка толщины стенки сердца по результатам ЭКГ | 2020 |

|

RU2767883C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ СОВМЕСТНОГО ВЫПОЛНЕНИЯ ДЕБАЙЕРИЗАЦИИ И УСТРАНЕНИЯ ШУМОВ ИЗОБРАЖЕНИЯ С ПОМОЩЬЮ НЕЙРОННОЙ СЕТИ | 2020 |

|

RU2764395C1 |

| МАТРИЧНО-ВЕКТОРНЫЙ УМНОЖИТЕЛЬ С НАБОРОМ РЕГИСТРОВ ДЛЯ ХРАНЕНИЯ ВЕКТОРОВ, СОДЕРЖАЩИМ МНОГОПОРТОВУЮ ПАМЯТЬ | 2019 |

|

RU2795887C2 |

| СПОСОБ ИНТЕРПРЕТАЦИИ ИСКУССТВЕННЫХ НЕЙРОННЫХ СЕТЕЙ | 2018 |

|

RU2689818C1 |

| ПОСТРОЕНИЕ НЕЙРОННОЙ СЕТИ НА ОСНОВЕ НЕЙРОНОВ С ФУНКЦИОНАЛЬНЫМ ПРЕОБРАЗОВАНИЕМ ПРОИЗВОЛЬНОГО ВИДА ДЛЯ ВХОДНЫХ СИГНАЛОВ | 2018 |

|

RU2727080C2 |

Изобретение относится к электронно-вычислительной технике. Технический результат заключается в увеличении быстродействия работы вычислительной системы. Технический результат достигается за счет того, что нейропроцессор содержит блок связи, служащий для обмена данными с центральным процессором по двунаправленной шине, управляющее устройство для согласования входных и выходных данных, буферный регистр для хранения значений аргумента, постоянное запоминающее устройство для хранения коэффициентов обучения процессора, n-последовательно включенных умножителей для аргументов, выходной сумматор значений для агрегирования полученной информации на входе, выходной регистр данных для записи значения вычисленной функции, выход которого является выходом процессора, а также регистров для управления операндами, причем в его состав дополнительно введен блок векторного процессора для быстрого обмена данными с постоянной энергонезависимой памятью, включающий в себя операционное устройство, узлы функции насыщения, регистр матрицы хранения весовых коэффициентов, регистр подкачки новой матрицы весов из буфера, циклический сдвигатель. 2 з.п. ф-лы, 1 ил.

1. Нейропроцессор, содержащий блок связи (1), служащий для обмена данными с центральным процессором по двунаправленной шине, управляющее устройство (2) для согласования входных и выходных данных, буферный регистр (3) для хранения значений аргумента, постоянное запоминающее устройство (4) для хранения коэффициентов обучения (настройки) процессора, n-последовательно включенных умножителей (5) для аргументов, выходной сумматор значений (6) для агрегирования полученной информации на входе, выходной регистр данных (7) для записи значения вычисленной функции, выход которого является выходом процессора, а также регистров 21-29 для управления операндами, отличающийся тем, что в его состав дополнительно введен блок векторного процессора для быстрого обмена данными с постоянной энергонезависимой памятью (EEPROM, flash), включающий в себя операционное устройство (OU), узлы функции насыщения (SU1, SU2), регистр матрицы хранения весовых коэффициентов (WOPER), регистр подкачки новой матрицы весов из буфера (WBUF), циклический сдвигатель (RCS).

2. Нейропроцессор по п.1, отличающийся тем, что в его состав дополнительно введен блок автокодировщика (AE), осуществляющего функции кодирования и декодирования с целью получения оптимальных новых значений функции насыщения (активации) при сохранении большинства полезных свойств нейронов, получающих качественные признаки от синапсов и весовых функций.

3. Нейропроцессор по п.1, отличающийся тем, что функцией активации нейросети является строго определенная функция (Leaky ReLU), которая является оптимальной для задач линейной регрессии и применима к проблеме вычисления значений нормального (гауссовского) распределения, решающая задачу кластеризации (расслоения) нейронов и проблему затухания градиента.

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| НЕЙРОПРОЦЕССОР | 2011 |

|

RU2473126C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Способ восстановления спиралей из вольфрамовой проволоки для электрических ламп накаливания, наполненных газом | 1924 |

|

SU2020A1 |

| US 11334402 B2, 17.05.2022. | |||

Авторы

Даты

2024-08-20—Публикация

2024-03-18—Подача