Изобретение относится к автоматике и вычислительной технике, в частности к устройствам нелинейного преобразования кода в частоту, и может быть использовано в вычислительных и управляющих комплексах в качестве нелинейного преобразователя кода в частоту, совмещающего функцию преобразования формы представления информации с ее математической переработкой по нелинейной зависимости.

Наиболее близким по совокупности признаков и по технической сущности к заявляемому устройству является нейросетевой преобразователь кода в частоту (патент на изобретение РФ №2420804, МПК G06N 99/00, 2009), который обеспечивает формирование выходной частоты, пропорциональной входному коду; содержащий счетчик, дешифратор, память кодов, четыре элемента "И", два элемента "ИЛИ", два элемента задержки, два сумматора, группа цифровых выходов счетчика соединена через дешифратор со входами памяти кодов, выходы памяти кодов соединены через первый и второй элементы "И" с первыми входами первого и второго элементов "ИЛИ" соответственно, вторые входы первого и второго элементов "ИЛИ" соединены через третий и четвертый элементы "И" соответственно с первым входом цифрового кода устройства, второй частотный вход устройства соединен с входом первого элемента "И" и через первый элемент задержки с входом третьего элемента "И", выход первого элемента "ИЛИ" соединен с первым суммирующим входом первого сумматора, выход первого сумматора соединен со вторым входом переноса второго сумматора, выход второго сумматора соединен со входом второго элемента "И" и через второй элемент задержки со входом четвертого элемента "И", выход второго элемента "ИЛИ" соединен с первым входом второго сумматора, выход второго сумматора соединен со входом счетчика, выход переноса которого одновременно является выходом устройства, отличающийся тем, что в преобразователь введены блок памяти весовых коэффициентов и блок обучения, вход данных блока обучения соединен со входом тестовой последовательности, адресный вход блока памяти весовых коэффициентов соединен с шиной SA адреса весовых коэффициентов блока обучения, информационный вход блока памяти весовых коэффициентов соединен с шиной SD данных весовых коэффициентов блока обучения, вход разрешения записи блока памяти весовых коэффициентов соединен с выходом разрешения записи we блока обучения, выходы w1 и w2 блока памяти весовых коэффициентов соединены соответственно со вторыми входами первого и второго сумматоров, задающими режим работы сумматоров (сумматоры могут работать в режимах суммирования и вычитания), выходы vi (i=1, 2, …, k) и ui (i=1, 2, …, k) блока памяти весовых коэффициентов соединены с третьими входными шинами первого и второго сумматоров, задающими начальное значение, используемое в операциях суммирования и вычитания, выходы si (i=1, 2, …, k) блока памяти весовых коэффициентов соединены со входами памяти кодов.

Недостатками прототипа являются его ограниченные функциональные возможности, а именно схемно-конструктивно не предусмотрены возможность использования в одном цикле преобразования разных функций активации нейронов в сети преобразователя для реализации широкого ряда функциональных зависимостей выходной частоты от входного кода и возможность коррекции мультипликативной составляющей погрешности датчиков, так как в качестве функций активации используются только дробно-рациональные функции с двумя настроечными коэффициентами.

Технический результат предлагаемого изобретения направлен на расширение функциональных возможностей и улучшение способности преобразователя корректировать мультипликативную составляющую погрешности датчиков, а именно на реализацию различных функциональных зависимостей выходной частоты от входного кода, достигаемый за счет использования в одном цикле преобразования разных типов функций активации нейронов в сети преобразователя и за счет введения третьего настроечного коэффициента в дробно-рациональные аппроксимирующие функции. Использование блока выбора функции активации позволяет использовать в одном цикле преобразования разные виды функций активации нейронов в сети преобразователя, выполняющиеся в разные такты преобразования, что позволяет расширить круг воспроизводимых функциональных зависимостей. Использование умножителя позволяет ввести третий настроечный коэффициент в дробно-рациональные аппроксимирующие функции для улучшения способности преобразователя корректировать мультипликативную составляющую погрешности датчиков.

Технический результат достигается тем, что в преобразователь кода в частоту, содержащий счетчик, дешифратор, память кодов, четыре элемента "И", два элемента "ИЛИ", два элемента задержки, два сумматора, блок памяти весовых коэффициентов и блок обучения, вход данных блока обучения соединен со входом тестовой последовательности, адресный вход блока памяти весовых коэффициентов соединен с шиной SA адреса весовых коэффициентов блока обучения, информационный вход блока памяти весовых коэффициентов соединен с шиной SD данных весовых коэффициентов блока обучения, вход разрешения записи блока памяти весовых коэффициентов соединен с выходом разрешения записи we блока обучения, выходы vi (i=1, 2, …, k) и ui (i=1, 2, …, k) блока памяти весовых коэффициентов соединены с третьими входными шинами первого и второго сумматоров, задающими начальное значение, используемое в операциях суммирования и вычитания, выходы si (i=1, 2, … k) блока памяти весовых коэффициентов соединены с первой группой входов памяти кодов, группа цифровых выходов счетчика соединена через дешифратор со второй группой входов памяти кодов, третий и первый выходы памяти кодов соединены через первый и второй элементы "И" с первыми входами первого и второго элементов "ИЛИ" соответственно, второй вход первого элемента "ИЛИ" соединен через третий элемент "И" с первым входом цифрового кода устройства, второй вход второго элемента "ИЛИ" соединен с выходом четвертого элемента "И", второй частотный вход устройства соединен с входом первого элемента "И" и через первый элемент задержки с входом третьего элемента "И", выход первого элемента "ИЛИ" соединен с первым суммирующим входом первого сумматора, выход первого сумматора соединен со вторым входом переноса второго сумматора, выход второго сумматора соединен со входом второго элемента "И" и через второй элемент задержки со входом четвертого элемента "И", выход второго элемента "ИЛИ" соединен с первым входом второго сумматора, выход второго сумматора соединен со входом счетчика, выход переноса которого одновременно является выходом устройства;

вводятся умножитель и блок выбора функции активации, входы умножителя соединены с первым входом цифрового кода устройства и со вторым выходом блока памяти кодов, выход умножителя соединен с входом четвертого элемента "И", четвертый выход памяти кодов соединен со входом блока выбора функции активации, выходы w1 и w2 блока выбора функции активации соединены соответственно со вторыми входами первого и второго сумматоров, задающими режим работы сумматоров (сумматоры могут работать в режимах суммирования и вычитания).

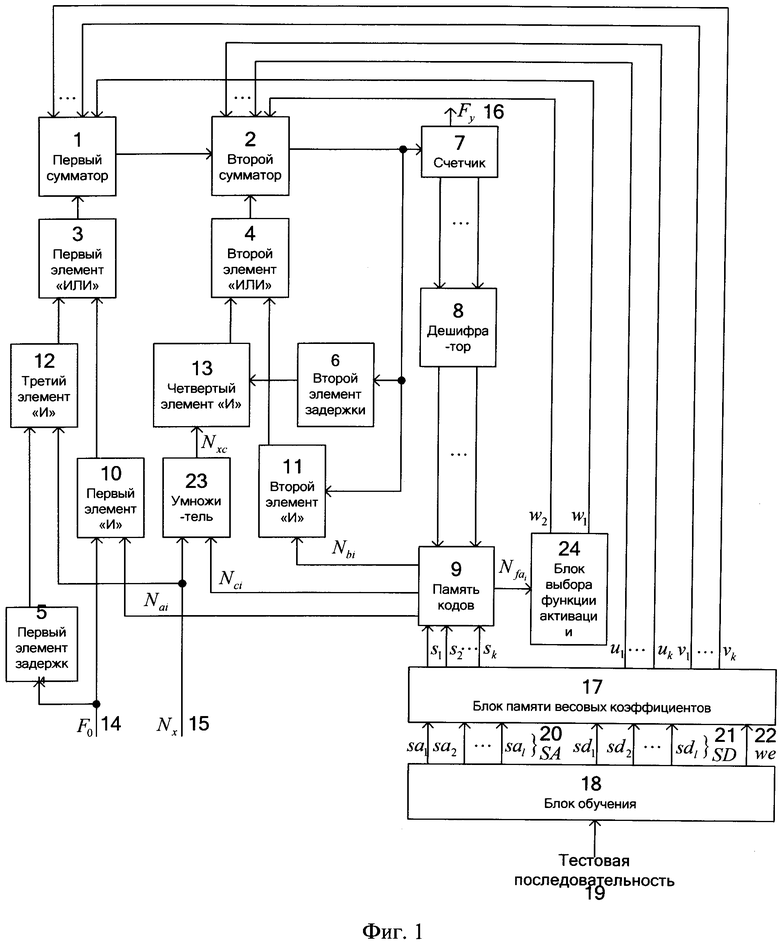

На фиг.1 представлена структурная схема предлагаемого устройства.

Нейросетевой преобразователь кода в частоту содержит первый сумматор 1, второй сумматор 2, первый элемент "ИЛИ" 3, второй элемент "ИЛИ" 4, первый элемент задержки 5, второй элемент задержки 6, счетчик 7, дешифратор 8, память кодов 9, первый элемент "И" 10, второй элемент "И" 11, третий элемент "И" 12, четвертый элемент "И" 13, вход опорной (эталонной) частоты F0 14, вход преобразуемого кода Nx 15, выход результирующей частоты Fy 16, блок памяти весовых коэффициентов 17, блок обучения 18, вход тестовой последовательности 19, шину SA 20 адреса весовых коэффициентов блока обучения, шину SD 21 данных весовых коэффициентов блока обучения, выход разрешения записи we 22 блока обучения, умножитель 23, блок выбора функции активации 24.

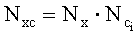

Умножитель 23 осуществляет операцию умножения кодов Nx и

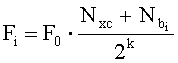

Первый сумматор 1 реализует операцию суммирования кодов Nxc и

Первый сумматор 1 имеет первый суммирующий вход, второй вход управления, определяющий тип операции (суммирование или вычитание), третью входную шину, задающую начальное значение суммы и выход переноса.

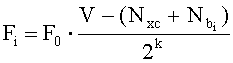

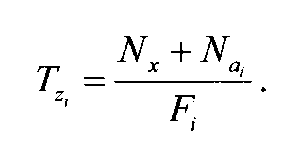

Второй сумматор 2 работает по принципу развертывающих структур. Формирование на его выходе периода

в режиме вычитания осуществляется путем линейной развертки кода

Второй сумматор 2 имеет первый суммирующий вход, второй вход управления, определяющий тип операции (суммирование или вычитание), третью входную шину, задающую начальное значение суммы и выход переноса. Второй сумматор 2 является неотъемлемой частью искусственной нейронной сети преобразователя.

Первый элемент "ИЛИ" 3 и второй элемент "ИЛИ" 4 имеют по два логических входа и одному логическому выходу.

Первый 10, второй 11, третий 12 и четвертый 13 элементы "И" имеют по два логических входа и одному логическому выходу.

Счетчик 7 имеет вход разрешения счета, группу цифровых выходов и выход переноса. С выхода переноса счетчика 7 снимается выходная частота преобразования Fy 16.

Дешифратор 8 имеет группу цифровых входов и группу цифровых выходов.

Память кодов 9 имеет группу цифровых входов и группу цифровых выходов и предназначена для промежуточного хранения цифровых коэффициентов

Блок памяти весовых коэффициентов 17 имеет адресную входную шину, шину данных и вход разрешения записи, а также выходы коэффициентов, задающих веса ui (i=1, 2, … k) и vi (i=1, 2, … k) синаптических связей первого и второго сумматоров.

Блок обучения 18 предназначен для обучения нейронной сети блока определения интервала на реализацию требуемой функции разбиения входной частоты на ее диапазоны.

Блок обучения 18 имеет вход тестовой последовательности, выходную адресную шину, выходную шину данных и выход разрешения записи.

Блок выбора функции активации 24 предназначен для переключения типа выполняемых операций первым и вторым сумматорами (суммирование и вычитание) на основе кода

Блок выбора функции активации 24 имеет один цифровой вход кода

Нейросетевой преобразователь кода в частоту содержит счетчик 7, дешифратор 8, память кодов 9, первый элемент "И" 10, второй элемент "И" 11, третий элемент "И" 12, четвертый элемент "И" 13, первый элемент задержки 5, второй элемент задержки 6, блок памяти весовых коэффициентов 17, блок обучения 18, первый сумматор 1, второй сумматор 2, первый элемент "ИЛИ" 3, второй элемент "ИЛИ" 4, первый вход цифрового кода устройства 15, второй частотный вход устройства 14, выход устройства 16, вход тестовой последовательности 19, шину SA 20 адреса весовых коэффициентов, шину SD 21 данных весовых коэффициентов, выход разрешения записи we 22, умножитель 23, блок выбора функции активации 24. Группа цифровых выходов счетчика 7 соединена через дешифратор 8 со входами памяти кодов 9. Первый и третий выходы памяти кодов 9 соединены через первый элемент "И" 10 и второй элемент "И" 11 с первыми входами первого элемента "ИЛИ" 3 и второго элемента "ИЛИ" 4 соответственно. Второй вход первого элемента "ИЛИ" 3 соединен через третий элемент "И" 12 с первым входом цифрового кода Nx устройства 15. Второй вход второго элемента "ИЛИ" 4 соединен с выходом умножителя 23. Входы умножителя 23 соединены с первым входом цифрового кода Nx устройства 15 и со вторым выходом блока памяти кодов 9. Четвертый выход памяти кодов 9 соединен со входом блока выбора функции активации 24. Выходы w1 и w2 блока выбора функции активации 24 соединены соответственно со вторым входом первого сумматора 1 и со вторым входом второго сумматора 2. Второй частотный вход F0 устройства 14 соединен с входом первого элемента "И" 3 и через первый элемент задержки 5 с входом третьего элемента "И" 12. Выход первого элемента "ИЛИ" 3 соединен с первым суммирующим входом первого сумматора 1. Выход первого сумматора 1 соединен со вторым входом переноса второго сумматора 2. Выход второго сумматора 2 соединен со входом второго элемента "И" 11 и через второй элемент задержки 6 со входом четвертого элемента "И" 13. Выход второго элемента "ИЛИ" 4 соединен с первым входом второго сумматора 2. Выход второго сумматора 2 соединен со входом счетчика 7, выход переноса которого одновременно является выходом устройства. Вход данных блока обучения 18 соединен со входом тестовой последовательности 19. Адресный вход блока памяти весовых коэффициентов 17 соединен с шиной SA 20 адреса весовых коэффициентов блока обучения 18. Информационный вход блока памяти весовых коэффициентов 17 соединен с шиной SD 21 данных весовых коэффициентов блока обучения 18. Вход разрешения записи блока памяти весовых коэффициентов 17 соединен с выходом разрешения записи we 22 блока обучения 18. Выходы w1 и w2 блока выбора функции активации 24 соединены со вторыми входами первого сумматора 1 и второго сумматора 2 соответственно, задающими тип функции активации путем задания режимов работы сумматоров. Первый сумматор 1 и второй сумматор 2 могут работать в режимах суммирования и вычитания. Выходы vi (i=1, 2, …, k) и ui (i=1, 2, …, k) блока памяти весовых коэффициентов 17 соединены с третьими входными шинами первого сумматора 1 и второго сумматора 2 соответственно, задающими начальное значение, используемое в операциях суммирования и вычитания. Выходы si (i=1, 2, …, k) блока памяти весовых коэффициентов 17 соединены со входами памяти кодов 9.

Нейросетевой блок определения интервала работает следующим образом.

Для реализации нелинейной зависимости преобразования нейросетевой преобразователь кода в частоту должен быть обучен при помощи блока обучения 18. Обучение осуществляется при помощи подачи тестовой последовательности 19. Тестовая последовательность состоит из последовательно подаваемых значений входного кода Nx 15 и соответствующих этим значениям значения выходной частоты Fy 16. Объем тестовой последовательности влияет на точность обучения. Чем больше тестовая последовательность, тем точнее обучения устройства на реализацию зависимости выходной частоты Fy 16 от входного кода Nx 15.

Блок обучения 18 может быть реализован, например, на внешней или внутренней плате расширения персонального компьютера.

При подаче тестовой последовательности 19 на вход блока обучения 18 начинается операция обучения. По окончании операции обучения осуществляется запись новых значений весовых коэффициентов и порогов нейронов в блок памяти весовых коэффициентов 17. Для этого на вход подтверждения записи блока памяти весовых коэффициентов 17 с выхода we 22 блока обучения 18 подается значение we=1. На вход шины адреса блока памяти весовых коэффициентов 17 с выхода SA 20 блока обучения 18 подается адрес соответствующего весового коэффициента. При этом на шину данных SD 21 подается значение весового коэффициента.

На входы устройства поступает входной код Nx и опорная частота F0.

Формирование сумм

Описываемый нейросетевой преобразователь относится к классу гибридных вычислительных устройств с дискретно-управляемыми параметрами (в том числе с использованием цифровых весовых коэффициентов искусственной нейронной сети), использующих принцип многократного использования импульсно-цифровых решающих элементов, входящих в состав операционного блока. Управление последовательностью выполнения отдельных операций производится счетчиком 7 и дешифратором 8.

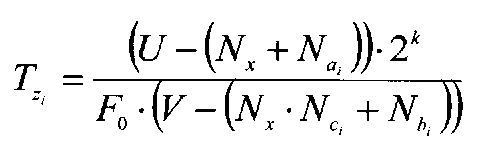

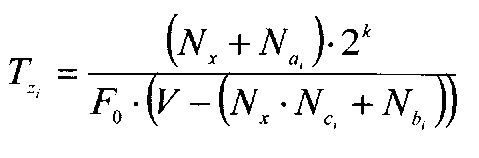

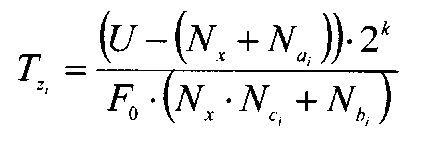

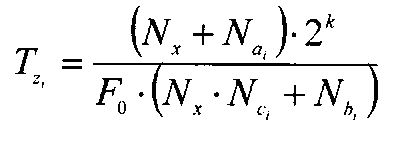

Операционный блок, моделирующий в каждом i-м такте (i=1, 2, …, n) простую дробь вида (x+a

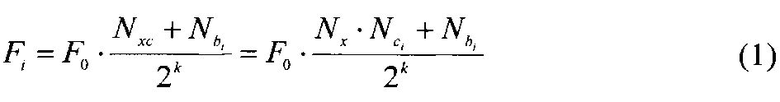

i)/(x·ci+bi), состоит из последовательного соединения линейных преобразователей (Пр) "код-частота" (N→F) и "код-период" (N→T). Преобразователь "N→F" построен на основе первого сумматора 1, реализующего операцию суммирования кодов

(режим суммирования) или

(режим вычитания), представляющую собой последовательность импульсов переполнения на выходе первого сумматора 1, образуемых путем переноса на его вход кодов

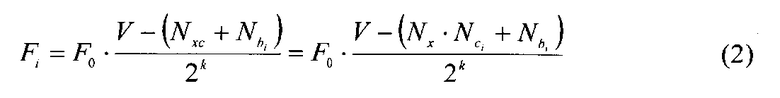

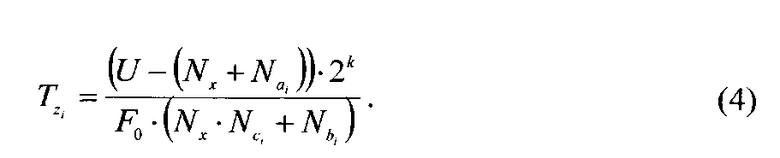

Пр "N→Т" построен на основе второго сумматора 2 и работает по принципу развертывающихся структур. Формирование на его выходе периода

в режиме вычитания (весовой коэффициент w2=0, а весовой коэффициент 0≤U<2k задает максимальную границу) осуществляется путем линейной развертки кода

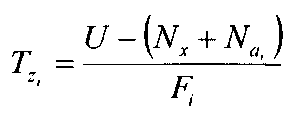

В момент формирования импульса окончания периода

Учитывая возможные комбинации режимов функционирования (режимы суммирования и вычитания) первого и второго сумматоров 1 и 2, преобразователь реализует функциональную зависимость путем ее приближения с использованием аппроксимирующих функций представленных в таблице 1. Аппроксимирующие функции являются функциями активации нейронов сети преобразователя.

Процесс формирования следующего периода

При этом результирующая частота Fz на выходе нейросетевого преобразователя соответственно равна

Для реализации нелинейной зависимости нейросетевой преобразователь кода в частоту должен быть обучен при помощи блока обучения 18. Обучение осуществляется при помощи подачи тестовой последовательности 19. Тестовая последовательность состоит из последовательно подаваемых значений входного кода Nx 15 и соответствующих этим значениям значений выходной частоты Fy 16. Пример тестовой последовательности приведен в таблице 2. Объем тестовой последовательности влияет на точность обучения. Чем больше тестовая последовательность, тем точнее обучения устройства на реализацию зависимости выходной частоты Fy 16 от входного кода Nx 15.

При подаче тестовой последовательности 19 на вход блока обучения 18 начинается операция обучения. По окончании операции обучения осуществляется запись новых значений весовых коэффициентов и порогов нейронов в блок памяти весовых коэффициентов 17. Для этого на вход подтверждения записи блока памяти весовых коэффициентов 17 с выхода we 22 блока обучения 18 подается значение we=1. На вход шины адреса блока памяти весовых коэффициентов 17 с выхода SA 20 блока обучения 18 подается адрес соответствующего весового коэффициента. При этом на шину данных SD 21 подается значение весового коэффициента.

Таким образом, применение предлагаемого нейросетевого преобразователя кода в частоту позволяет расширить функциональные возможности, а именно расширить диапазон воспроизводимых функциональных зависимостей при реализации функционального преобразования входного кода в частоту, а также улучшить способность преобразователя корректировать мультипликативную составляющую погрешности датчиков.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОСЕТЕВОЙ ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2009 |

|

RU2420804C1 |

| НЕЙРОСЕТЕВОЙ БЛОК ОПРЕДЕЛЕНИЯ ИНТЕРВАЛА | 2008 |

|

RU2382413C1 |

| Нейропроцессор (NPU) | 2024 |

|

RU2825124C1 |

| ИСКУССТВЕННЫЙ НЕЙРОН | 2014 |

|

RU2579958C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 2006 |

|

RU2321946C1 |

| УСТРОЙСТВО РЕГУЛИРОВАНИЯ ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА | 2011 |

|

RU2465716C1 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ ИНФОРМАЦИОННО-ПРЕОБРАЗУЮЩИХ ЭЛЕМЕНТОВ БОРТОВОГО ОБОРУДОВАНИЯ ВОЗДУШНОГО СУДНА НА ОСНОВЕ МАШИННОГО ОБУЧЕНИЯ | 2022 |

|

RU2802976C1 |

| РАСПОЗНАЮЩЕЕ УСТРОЙСТВО ДЛЯ НЕЧЕТКИХ НЕЙРОННЫХ СЕТЕЙ | 2007 |

|

RU2340940C1 |

| Система обнаружения гидроакустических сигналов и их нейросетевой классификации | 2018 |

|

RU2681252C1 |

| Автоматический нейросетевой настройщик параметров ПИ-регулятора для управления нагревательными объектами | 2016 |

|

RU2644843C1 |

Изобретение относится к области устройств преобразования кода в частоту. Техническим результатом является реализация различных функциональных зависимостей выходной частоты от входного кода и улучшение способности преобразователя корректировать мультипликативную составляющую погрешности датчиков. Устройство содержит два сумматора, два элемента ИЛИ, два элемента задержки, счетчик, дешифратор, память кодов, четыре элемента И, блок памяти весовых коэффициентов, блок обучения, блок памяти весовых коэффициентов, блок обучения, умножитель, блок выбора функции активации. 2 табл., 1 ил.

Нейросетевой преобразователь кода в частоту, содержащий счетчик, дешифратор, память кодов, четыре элемента "И", два элемента "ИЛИ", два элемента задержки, два сумматора, блок памяти весовых коэффициентов и блок обучения, вход данных блока обучения соединен со входом тестовой последовательности, адресный вход блока памяти весовых коэффициентов соединен с шиной SA адреса весовых коэффициентов блока обучения, информационный вход блока памяти весовых коэффициентов соединен с шиной SD данных весовых коэффициентов блока обучения, вход разрешения записи блока памяти весовых коэффициентов соединен с выходом разрешения записи we блока обучения, выходы vi (i=1, 2, …, k) и ui (i=1, 2, … k) блока памяти весовых коэффициентов соединены с третьими входными шинами первого и второго сумматоров, задающими начальное значение, используемое в операциях суммирования и вычитания, выходы si (i=1, 2, …, l) блока памяти весовых коэффициентов соединены с первой группой входов памяти кодов, группа цифровых выходов счетчика соединена через дешифратор со второй группой входов памяти кодов, третий и первый выходы памяти кодов соединены через первый и второй элементы "И" с первыми входами первого и второго элементов "ИЛИ" соответственно, второй вход первого элемента "ИЛИ" соединен через третий элемент "И" с первым входом цифрового кода устройства, второй вход второго элемента "ИЛИ" соединен с выходом четвертого элемента "И", второй частотный вход устройства соединен с входом первого элемента "И" и через первый элемент задержки с входом третьего элемента "И", выход первого элемента "ИЛИ" соединен с первым суммирующим входом первого сумматора, выход первого сумматора соединен со вторым входом переноса второго сумматора, выход второго сумматора соединен со входом второго элемента "И" и через второй элемент задержки со входом четвертого элемента "И", выход второго элемента "ИЛИ" соединен с первым входом второго сумматора, выход второго сумматора соединен со входом счетчика, выход переноса которого одновременно является выходом устройства, отличающийся тем, что в преобразователь введены умножитель и блок выбора функции активации, входы умножителя соединены с первым входом цифрового кода устройства и со вторым выходом блока памяти кодов, выход умножителя соединен с входом четвертого элемента "И", четвертый выход памяти кодов соединен со входом блока выбора функции активации, выходы w1 и w2 блока выбора функции активации соединены соответственно со вторыми входами первого и второго сумматоров, задающими режим работы сумматоров (сумматоры могут работать в режимах суммирования и вычитания).

| НЕЙРОСЕТЕВОЙ ПРЕОБРАЗОВАТЕЛЬ КОДА В ЧАСТОТУ | 2009 |

|

RU2420804C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЦИФРОВОГО КОДА В ЧАСТОТУ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1992 |

|

RU2037960C1 |

| Преобразователь цифрового кода в частоту | 1987 |

|

SU1520663A1 |

| Преобразователь кода в частоту с переменным коэффициентом преобразования | 1984 |

|

SU1179542A1 |

| 0 |

|

SU400991A1 | |

| JP 54013708 A, 01.02.1979 | |||

Авторы

Даты

2015-02-10—Публикация

2013-12-16—Подача