Изобретение относится к области вычислительной техники и может быть использовано в КМДП интегральных схемах для реализации логических и арифметических устройств.

Известен тактируемый двухкаскадный логический элемент с парафазными входами и выходами (Патент США №4570084, Н03К 19/017, 19/20, НКИ 307/452 от 11.02.1986). Он содержит предзарядовые и дополнительные транзисторы p-типа, ключевые цепи на транзисторах n-типа, тактовые транзисторы n-типа и выходные статические инверторы. Недостатком элемента является его сложность (10 транзисторов, помимо логических) и ограниченное быстродействие при двухкаскадном пути прохождения логического сигнала с дополнительными нагрузками на выходах инверторов.

Наиболее близким техническим решением к предлагаемому является однокаскадный тактируемый парафазный логический элемент (Патент США №6661257, Н03К 19/096, НКИ 326/95 от 09.12.2003). Это устройство, принятое за прототип, содержит два инвертора с обратными связями, тактовый транзистор, тактируемый транзисторный ключ и логический блок в виде ключевых цепей, выполненных на транзисторах n-типа с парафазным потенциальным и токовым управлением. Недостаток этого устройства - избыточная сложность устройства за счет использования для тактирования двух дополнительных транзисторов.

Технической задачей, решаемой изобретением, является упрощение устройства.

Поставленная цель достигается тем, что парафазный логический элемент, содержащий первый и второй КМДП инверторы и логический блок, содержащий прямые и инверсные ключевые цепи, выполненные на транзисторах n-типа, затворы которых подключены к потенциальным парафазным логическим входам устройства, выход первого КМДП инвертора, к которому подключены первые выводы прямых ключевых цепей, соединен с входом второго КМДП инвертора и с прямым выходом устройства, выход второго КМДП инвертора, к которому подключены первые выводы инверсных ключевых цепей, соединен с входом первого КМДП инвертора и с дополняющим выходом устройства, вторые выводы прямых и инверсных ключевых цепей подключены к соответствующим токовым парафазным логическим входам устройства, причем на логические входы устройства подаются парафазные сигналы таким образом, что только одна прямая и одна инверсная ключевые цепи нормально замкнуты, а все другие разомкнуты, а КМДП инверторы включены между шиной питания и тактовой шиной устройства.

Существенными отличительными признаками в указанной совокупности признаков является включение КМДП инверторов между шиной питания и тактовой шиной устройства.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - упрощение устройства. В элементах такого типа в выключенном состоянии при их каскадном применении напряжения на его выходах должны соответствовать уровню напряжения логической ″1″ для транзисторов n-типа, т.к. эти напряжения, поданные на токовые логические входы последующего логического каскада, обеспечивают сохранность напряжений логической ″1″ на его выходах. В известном устройстве это условие достигается за счет выключения тактового транзистора n-типа и включения тактируемого ключа. При этом напряжения на выходах инверторов выравниваются или имеют отличие на величину порогового напряжения тактируемого ключа. Для этих целей используются два дополнительных транзистора, а также шина земли и одна или две из тактовых шин.

В предложенном устройстве одна единственная тактовая шина выполняет функцию шины земли при установке инверторов в рабочее парафазное состояние, а при высоком уровне напряжения на шине обеспечивает режим предзаряда - повышение напряжения на выходе одного из инверторов за счет открытого транзистора n-типа самого инвертора от напряжения логического ″0″ до напряжения питания минус пороговое напряжение транзистора n-типа. Таким образом реализуется исходное состояние выравнивания напряжений на выходах обоих инверторов до высокого уровня, обеспечивающих непроводящее состояние ключевых цепей последующего каскада. При этом устройство требует на два транзастора и одну шину управления меньше, чем устройство-прототип.

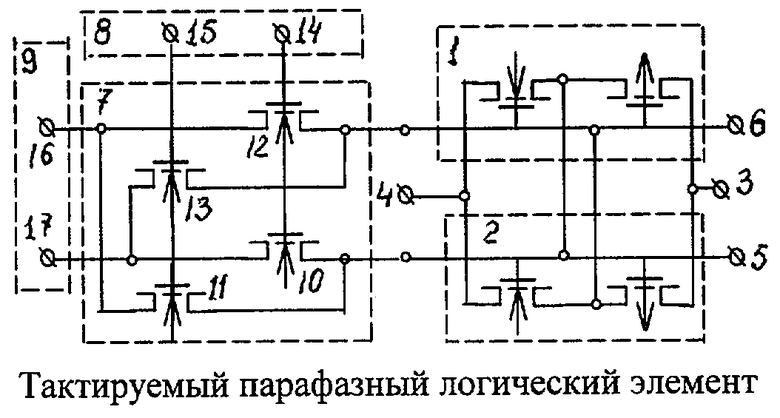

На чертеже приведена принципиальная схема заявляемого тактируемого парафазного логического элемента и качестве примера принципиальная схема логического блока для реализации функции ИСКЛЮЧАЮЩЕЕ ИЛИ.

Тактируемый парафазный логический элемент содержит первый 1 и второй 2 КМДП инверторы, которые включены между шиной питания 3 и тактовой шиной 4. Выход первого инвертора 1 подключен к входу второго инвертора 2 и является прямым выходом 5 устройства. Выход второго инвертора 2 подключен к входу первого инвертора 1 и является дополняющим выходом 6 устройства.

Логический блок 7 содержит прямые и инверсные ключевые цепи, выполненные на транзисторах n-типа, затворы которых подключены к потенциальным парафазным логическим входам 8 устройства. Первые выводы прямых и инверсных ключевых цепей соединены соответственно с прямым 5 и дополняющим 6 выходами устройства. Вторые выводы прямых и инверсных ключевых цепей соединены с соответствующими токовыми парафазными логическими входами 9 устройства.

Логический блок 8 при реализации функции ИСКЛЮЧАЮЩЕЕ ИЛИ содержит 4 транзистора 10-13 n-типа, которые составляют две прямые и две инверсные однотранзисторные ключевые цепи: первая и вторая прямые ключевые цепи содержат соответственно первый 10 и второй 11 транзисторы n-типа, первая и вторая инверсные ключевые цепи цепи содержат соответственно третий 12 и четвертый 13 транзисторы n-типа. Затворы первого 10 и третьего 12 транзисторов n-типа подключены к прямому потенциальному логическому входу 14 устройства, а затворы второго 11 и четвертого 13 транзисторов n-типа подключены к дополняющему потенциальному логическому входу 15 устройства. Вторые выводы первой инверсной и второй прямой ключевых цепей подключены к первому токовому логическому входу 16 устройства, а вторые выводы первой прямой и второй инверсной ключевых цепей подключены к второму токовому логическому входу 17 устройства.

Количество ключевых цепей соответствует числу логических состояний элемента - в данном случае 4 от двух переменных.

Ключевые цепи строятся по правилам Булевой алгебры и на потенциальные 8 и токовые 9 логические входы подаются парафазные сигналы, соответствующие логическим значениям входных переменных таким образом, что только одна прямая и одна инверсная ключевые цепи были нормально замкнуты, а все другие - разомкнуты. Для функции суммирования трех переменных имеет место 8 двухтранзисторных ключевых цепей по числу логических состояний, причем на потенциальные логические входы подаются парафазные сигналы двух переменных, а на токовые логические входы - парафазные сигналы третьей переменной, например, переноса.

Устройство работает следующим образом.

В исходном состоянии - на первом полутакте, при единичном сигнале на тактовой шине 4, транзистор n-типа, например, первого инвертора 1 с низким уровнем напряжения открыт, т.к. на его затворе напряжение питания с выхода второго 2 инвертора. Поэтому напряжение на выходе первого 1 инвертора нарастает до величины напряжения питания минус пороговое напряжение транзистора n-типа. Таким образом реализуется исходное состояние выравнивания напряжений на выходах обоих инверторов до высокого уровня. Сигналы на выходах 5 и 6 устройства также высокого уровня.

На втором полутакте на потенциальных логических входах 8 устройства устанавливаются парафазные сигналы, соответствующие входным переменным. Например, на прямой вход 14 подан сигнал высокого уровня, на дополняющий вход 15 - сигнал низкого уровня, что соответствует логической "1" первой переменной X. На токовых логических входах 9 устанавливаются сигналы, соответствующие второй переменной Y, например при Y="1" на первом входе 16 сохраняется сигнал высокого уровня, на втором входе 17 устанавливается сигнал низкого уровня. Первая прямая ключевая цепь (первый транзистор 10 n-типа) начинает проводить ток, поскольку на ее выводах перепад напряжений, а первая инверсная ключевая цепь (третий транзистор 12 также открыт) ток не проводит, поскольку напряжения на обоих выводах высокого уровня. При подаче на тактовую шину 4 сигнала нулевого уровня возникают токи разряда емкостей нагрузок инверторов 1 и 2 через транзисторы n-типа инверторов и напряжения на выходах 5 и 6 устройства снижаются. Но поскольку ток разряда емкости прямого выхода 5 увеличен за счет тока через открытый первый транзистор 10 n-типа, а ток разряда емкости дополняющего выхода 6 частично компенсируется обратным током открытого третьего 12 транзистора n-типа, и поскольку данные инверторы объединены обратными связями по схеме триггера, процесс приводит к формированию нулевого напряжения на прямом выходе 5 устройства (значение функции равно 0 при X=Y). На дополняющем выходе 6 устройства напряжение возрастает до напряжения питания за счет тока через открытый транзистор p-типа первого 1 инвертора при закрытом транзисторе n-типа этого инвертора.

При логическом неравенстве переменных в замкнутом состоянии находятся первая инверсная ключевая цепь и первая прямая ключевые цепи (при Х=1).

После срабатывания элемента на потенциальных логических входах 8 устройства устанавливаются сигналы низкого уровня и таким образом все ключевые цепи размыкаются. При подаче сигнала высокого уровня на тактовую шину 4 исходное состояние элемента восстанавливается.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2515225C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2007 |

|

RU2355104C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КАСКАДНЫХ УСТРОЙСТВ НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209508C1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

Изобретение относится к области вычислительной техники и может быть использовано в МДП интегральных схемах при реализации логических и арифметических устройств. Технический результат заключается в упрощении устройства. Устройство содержит первый и второй КМДП инверторы, которые включены между шиной питания и тактовой шиной. Выход первого КМДП инвертора подключен к входу второго КМДП инвертора и является прямым выходом устройства. Выход второго КМДП инвертора подключен к входу первого КМДП инвертора и является дополняющим выходом устройства. Логический блок содержит прямые и инверсные ключевые цепи, выполненные на транзисторах n-типа, затворы которых подключены к потенциальным парафазным логическим входам устройства. Первые выводы прямых и инверсных ключевых цепей соединены с входами соответственно второго и первого КМДП инверторов. Вторые выводы прямых и инверсных ключевых цепей соединены с соответствующими токовыми парафазными логическими входами устройства. 1 ил.

Тактируемый парафазный логический элемент, содержащий первый и второй КМДП инверторы и логический блок, содержащий прямые и инверсные ключевые цепи, выполненные на транзисторах n-типа, затворы которых подключены к потенциальным парафазным логическим входам устройства, выход первого КМДП инвертора, к которому подключены первые выводы прямых ключевых цепей, соединен с входом второго КМДП инвертора и с прямым выходом устройства, выход второго КМДП инвертора, к которому подключены первые выводы инверсных ключевых цепей, соединен с входом первого КМДП инвертора и с дополняющим выходом устройства, вторые выводы прямых и инверсных ключевых цепей подключены к соответствующим токовым парафазным логическим входам устройства, причем на логические входы устройства подаются парафазные сигналы таким образом, что только одна прямая и одна инверсная ключевые цепи нормально замкнуты, а все другие - разомкнуты, отличающийся тем, что КМДП инверторы включены между шиной питания и тактовой шиной устройства.

| US 2003117177 A1, 26.06.2003 | |||

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КАСКАДНЫХ УСТРОЙСТВ НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209508C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| Многоканальный коммутатор | 1985 |

|

SU1246362A1 |

Авторы

Даты

2010-02-20—Публикация

2009-03-27—Подача