Изобретение относится к области вычислительной техники и может быть использовано в КМДП интегральных схемах для реализации логических устройств.

Известен тактируемый двухкаскадный логический элемент с парафазными входами и выходами (Патент США №4570084, Н03К 19/017, 19/20, НКИ 307/452 от 11.02.1986). Он содержит предзарядовые и дополнительные транзисторы p-типа, ключевые цепи на транзисторах n-типа, тактовые транзисторы n-типа и выходные статические инверторы. Недостатком элемента является его сложность (10 транзисторов, помимо логических) и ограниченное быстродействие при двухкаскадном пути прохождения логического сигнала с дополнительными нагрузками на выходах инверторов.

Наиболее близким техническим решением к предлагаемому является однокаскадный тактируемый парафазный логический элемент (Патент США №6002270, Н03К 19/096, 19/017, НКИ 326/98 от 14.12.1999). Это устройство, принятое за прототип, содержит два инвертора с обратными связями, тактируемый ключ и логический блок в виде комбинационных цепей, выполненных на последовательно соединенных транзисторах n-типа. Недостаток этого устройства - избыточное потребление мощности, т.к. в выключенном состоянии для обеспечения низкого уровня напряжения на обоих выходах элемента через открытые транзисторы p-типа обоих инверторов от постоянно включенного источника питания протекают токи, которые замыкаются на шину земли через проводящую комбинационную цепь, а также через замкнутый ключ.

Технической задачей, решаемой в изобретении, является уменьшение мощности потребляемой устройством.

Поставленная цель достигается тем, что парафазный логический элемент на КМДП транзисторах, содержащий первый и второй инверторы, включенные между клеммой питания и шиной земли, и логический блок, содержащий по меньшей мере две комбинационные цепи, выполненные каждая из последовательно соединенных транзисторов n-типа, затворы которых подключены к парафазным логическим входам устройства таким образом, что только одна комбинационная цепь нормально замкнута, а все другие - нормально разомкнуты, при этом первые выводы комбинационных цепей соединены с шиной земли, а вторые являются соответственно прямыми или дополняющими выходами устройства, причем прямой выход устройства соединен дополнительно с выходом первого и входом второго инверторов, а дополняющий выход устройства соединен с выходом второго и входом первого инверторов, содержит тактирующий инвертор, включенный между шиной питания и шиной земли, и первый и второй транзисторы сброса n-типа, которые включены между клеммой питания и соответственно прямым и дополняющим выходами, устройства и затворы которых подключены к тактовому входу, с которым соединен также вход тактирующего инвертора, выход которого подключен к клемме питания.

Существенными отличительными признаками в указанной совокупности признаков является наличие тактирующего инвертора в цепи питания логического элемента и двух транзисторов сброса n-типа, которые включены между клеммой питания и соответственно прямым и дополняющим выходами устройства, а затворы которых подключены к тактовому входу, с которым соединен также вход тактирующего инвертора, выход которого подключен к клемме питания.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - уменьшение мощности потребляемой устройством. В элементах такого типа при их каскадном применении в выключенном состоянии напряжения логического "0" на его выходах не должны превышать порогового напряжения транзисторов n-типа. В известном устройстве это условие достигается за счет наличия тактируемого ключа и одной из цепей на транзисторах n-типа логического блока, которая находится в проводящем состоянии. Поскольку транзисторы p-типа обоих инверторов при этом открыты, через указанные цепи протекают токи и потребляется избыточная мощность от постоянно включенного источника питания, которая не связана с быстродействием самого элемента. Причем сопротивление данных цепей должно быть много меньше сопротивления обоих транзисторов p-типа, что ограничивает быстродействие элемента при малых размерах транзисторов. В заявленном устройстве при выключении напряжение на клемме питания плавно уменьшается от величины напряжения шины питания до нуля и установка нулевых сигналов на выходах происходит за счет открытых транзисторов сброса n-типа и транзистора n-типа тактирующего инвертора. При этом рассеивается только та мощность, которая была затрачена на возбуждение элемента в рабочем состоянии. В статическом состоянии элемент мощности не потребляет за счет прерывания цепи источника питания. Транзисторы сброса n-типа работают в режиме, когда напряжения на затворе и стоке изменяются в противофазе, что исключает броски токов при переключении и уменьшает потребление мощности. Быстродействие элемента при этом определяется только тактирующим инвертором, т.к. остальные части устройства, выполненные на транзисторах минимальных размеров, работают синхронно и отслеживают напряжение на клемме питания.

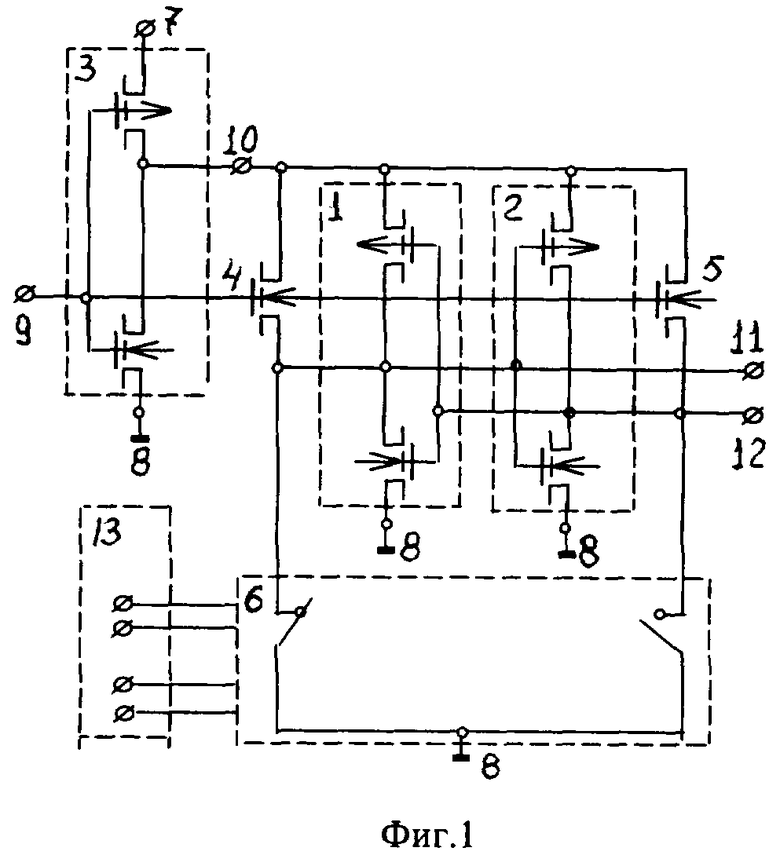

На фиг.1 приведена принципиальная схема заявляемого парафазного логического элемента на КМДП транзисторах. На фиг.2 приведена в качестве примера принципиальная схема логического блока для реализации функции Исключающее ИЛИ.

Парафазный логический элемент на КМДП транзисторах (Фиг.1) содержит первый 1 второй 2 и тактирующий 3 инверторы, первый 4 и второй 5 транзисторы сброса n-типа и логический блок 6.

Тактирующий инвертор 3 включен между шиной питания 7 и шиной земли 8. Вход тактирующего инвертора 3 подключен к тактовому входу 9 и соединен с затворами транзисторов сброса 4 и 5 n-типа, а его выход соединен с клеммой питания 10, которая может служить тактовым выходом устройства. Выход первого инвертора 1 подключен к входу второго инвертора 2 и соединен с прямым выходом 11 устройства. Выход второго инвертора 2 подключен к входу первого инвертора 1 и соединен с дополняющим выходом 12 устройства. Первый 1 и второй 2 инверторы включены между клеммой питания 10 и шиной земли 8, а первый 4 и второй 5 транзисторы сброса n-типа включены между клеммой питания 10 и соответственно прямым 11 и дополняющим 12 выходами устройства.

Логический блок 6 содержит по меньшей мере две комбинационные цепи, выполненные из последовательно соединенных транзисторов n-типа каждая, затворы которых подключены к парафазным логическим входам 13 устройства таким образом, что только одна комбинационная цепь нормально замкнута, а все другие - нормально разомкнуты, причем первые выводы комбинационных цепей соединены с шиной земли, а вторые являются соответственно прямым 11 или дополняющим 12 выходами устройства.

Логический блок 6 при реализации функции Исключающее ИЛИ (Фиг.2) содержит 6 транзисторов 14-19 n-типа, которые включены попарно последовательно и составляют 4 комбинационные цепи логического блока: первая содержит первый 14 и второй 15 транзисторы n-типа, вторая - третий 16 и четвертый 17 транзисторы n-типа, третья - четвертый 17 и пятый 18 транзисторы n-типа, четвертая - шестой 19 и второй 15 транзисторы n-типа. Количество комбинационных цепей соответствует числу логических состояний элемента - в данном случае 4 от двух переменных. Затворы первого 14 и пятого 18 транзисторов n-типа подключены к первому 20 логическому входу устройства, затворы третьего 16 и шестого 19 транзисторов n-типа подключены к второму 21 логическому входу, затворы второго 15 и четвертого 17 подключены соответственно к третьему 22 и четвертому 23 логическим входам устройства. Первая и вторая комбинационные цепи включены между прямым 11 выходом устройства и шиной земли 8, а третья и четертая комбинационные цепи включены между дополняющим 12 выходом устройства и шиной земли 8.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при единичном сигнале на тактовом входе 9 напряжение на выходе тактирующего инвертора 3 и на клемме питания 10 равно нулю, транзисторы сброса 4 и 5 открыты и сигналы на выходах 11 и 12 устройства также нулевые. На логических входах 13 устройства устанавливаются парафазные сигналы, соответствующие входным переменным. На первый 20 и второй 21 логические входы для заданной в данном случае функции Исключающее ИЛИ поданы соответственно прямой и дополняющий сигналы первой переменной X, а на третий 22 и четвертый 23 логические входы поданы соответственно прямой и дополняющий сигналы второй переменной Y. При равенстве переменных Х=Y в замкнутом состоянии находятся первая (при 1) или вторая (при 0) комбинационные цепи логического блока. При логическом неравенстве переменных в замкнутом состоянии находятся третья или четвертая комбинационные цепи.

На втором полутакте после подачи нулевого сигнала на тактовый вход 9 транзисторы сброса 4 и 5 n-типа закрываются, а на выходе тактирующего инвертора 3 и клемме питания 10 напряжение нарастатает до величины напряжения на шине питания 7. Одновременно через открытые транзисторы p-типа инверторов 1 и 2 начинает расти напряжение на емкостях нагрузок, связанных с выходами этих инверторов. Если в замкнутом состоянии находится первая или вторая комбинационные цепи, то благодаря току через них напряжение на выходе первого инвертора 1 ростет медленнее, чем на выходе второго инвертора 2. Поскольку данные инверторы объединены обратными связями по схеме триггера, процесс приводит к формированию нулевого напряжения на выходе первого инвертора 1 и на прямом выходе 11 устройства, а выходе второго инвертора 2 и дополняющем выходе 12 устройства - положительного напряжения, соответствующего логической 1 при X=Y.

При подаче единичного сигнала на тактовый вход 9 напряжение на выходе тактирующнго инвертора 3 и на клемме питания 10 убывает, а первый 4 и второй 5 транзисторы сброса n-типа открываются и независимо от состояния проводимости комбинационных цепей логического блока 6 напряжение на выходе второго инвертора 2 и на дополняющем выходе 12 устройства падает от напряжения шины питания до нуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2515225C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

| ТАКТИРУЕМЫЙ ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2382490C1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КАСКАДНЫХ УСТРОЙСТВ НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209508C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

Изобретение относится к области вычислительной техники и может быть использовано в МДП интегральных схемах при реализации логических устройств. Техническим результатом изобретения является уменьшение потребляемой мощности. Этот результат достигается тем, что в устройство, содержащее первый 1, второй 2 инверторы и логический блок 6, содержащий по меньшей мере две комбинационные цепи, выполненные из последовательно соединенных транзисторов n-типа, дополнительно включены тактирующий инвертор 3, первый 4 и второй 5 транзисторы сброса n-типа. 2 ил.

Парафазный логический элемент на КМДП транзисторах, содержащий первый и второй инверторы, включенные между клеммой питания и шиной земли, и логический блок, содержащий по меньшей мере две комбинационные цепи, выполненные каждая из последовательно соединенных транзисторов n-типа, затворы которых подключены к парафазным логическим входам устройства таким образом, что только одна комбинационная цепь нормально замкнута, а все другие - нормально разомкнуты, при этом первые выводы комбинационных цепей соединены с шиной земли, а вторые являются соответственно прямым или дополняющим выходами устройства, причем прямой выход устройства соединен дополнительно с выходом первого и входом второго инверторов, а дополняющий выход устройства соединен с выходом второго и входом первого инверторов, отличающийся тем, что содержит тактирующий инвертор, включенный между шиной питания и шиной земли, и первый и второй транзисторы сброса n-типа, которые включены между клеммой питания и соответственно прямым и дополняющим выходами устройства и затворы которых подключены к тактовому входу, с которым соединен также вход тактирующего инвертора, выход которого подключен к клемме питания.

| US 6002270 A, 14.12.1999 | |||

| US 4570084 A, 11.02.1986 | |||

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КАСКАДНЫХ УСТРОЙСТВ НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209508C1 |

| Логический элемент "исключающее или" на кмдп-транзисторах | 1979 |

|

SU790340A1 |

Авторы

Даты

2009-05-10—Публикация

2007-10-22—Подача