Изобретение относится к области вычислительной техники и может быть использовано для реализации каскадных логических устройств конвейерного типа.

Известен тактируемый логический элемент типа «домино» на КМДП транзисторах с запоминанием результата на полутакте (патент США № 7429880, H03K 19/094, 19/20 НКИ 326/98 от 30.09.2008). В нем используется тактируемый элемент И-ИЛИ-НЕ с предзарядом, выход которого подключен к входам инвертирующего элемента, а также содержит 3 инвертора и 5 тактируемых транзисторов. Недостатком элемента является его сложность. Наиболее близким техническим решением к предлагаемому является тактируемый логический элемент на КМДП транзисторах типа «домино» с запоминанием результата на полутакте (патент США № 7417465, Fig.1, МКИ H03K 19/096, 19/20, НКИ 326/95 от 26.08.2008). Это устройство, принятое за прототип, содержит содержит логический блок в виде ключевых цепей на транзисторах n-типа, включенных между тактовыми транзисторами, тактируемый инвертор, выходной инвертирующий элемент, два инвертора с обратными связями и транзистор обратной связи.

Недостаток этого устройства - избыточная сложность устройства вследствие реализации функции запоминания результата на полутакте с использованием инверторов с обратными связями и тактируемых инвертирующих элементов, содержащих каждый по 3 транзистора.

Технической задачей, решаемой в изобретении, является упрощение устройства.

Поставленная цель достигается тем, что тактируемый логический элемент, содержащий предзарядовый транзистор p-типа и тактовый транзистор n-типа, затворы которых подключены к тактовый шине, транзистор обратной связи p-типа, выходной инвертирующий элемент и логический блок, содержащий ключевые цепи, первые выводы которых объединены и через предзарядовый транзистор p-типа подключены к шине питания, вторые их выводы объединены и через тактовый транзистор n-типа подключены к шине земли, каждая ключевая цепь состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к логическим входам элемента, выходной инвертирующий элемент включен между шинами питания и земли, а его выход является выходом устройства, содержит также тактовый транзистор p-типа, ключевой транзистор n-типа и ключевой транзистор p-типа, а выходной инвертирующий элемент выполнен как КМДП инвертор, тактовый транзистор p-типа включен между шиной питания и вторым выводом ключевых цепей, ключевые транзисторы включены параллельно между первым выводом ключевых цепей и входом КМДП инвертора, затворы тактового транзистора p-типа и ключевого транзистора n-типа соединены с тактовой шиной, а затвор ключевого транзистора p-типа соединен с вторым выводом ключевых цепей, транзистор обратной связи p-типа, затвор которого соединен с выходом устройства, включен между шиной питания и входом КМДП инвертора.

Существенными отличительными признаками в указанной совокупности признаков является наличие тактового транзистор p-типа, тактируемых ключевых транзисторов с соответствующими связями, а также выполнение выходного инвертирующего элемента в виде КМДП инвертора.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - упрощение устройства.

В устройствах данного типа решается техническая задача запоминания на полутакте результата, полученного на выходе элемента во время предыдущего рабочего полутакта. В известном устройстве этот результат достигается с использованием триггерного элемента на двух инверторах с обратными связями, вход которого на полутакте запоминания блокируется тактовым сигналом, а выход которого блокирует возможность изменения сигнала на выходе устройства. При этом используются два инвертирующих элемента по 3 МДП транзистора в каждом и два инвертора. В целом, помимо логического блока для реализации необходимы 13 МДП транзисторов (каждый инвертор содержит 2 транзистора).

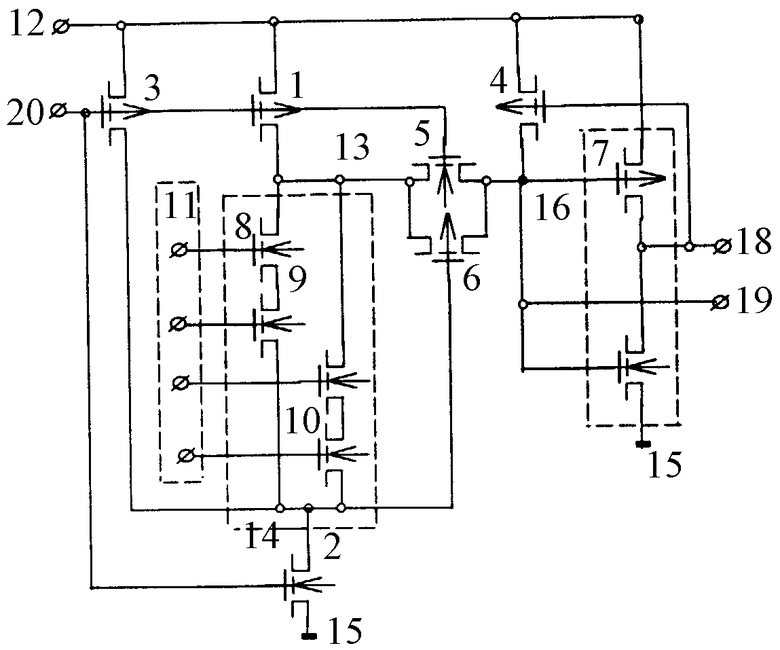

В заявленном устройстве запоминание результата, полученного на выходе элемента во время предыдущего рабочего полутакта, реализуется на ключевых транзисторах, которые изолируют вход КМДП инвертора на полутакте. Транзистор обратной связи с минимальной шириной канала обеспечивает в статическом режиме только сохранение высокого уровня сигнала на входе инвертора при нулевом значении на выходе. Введенный в устройство тактовый транзистор p-типа совместно с известным тактовым транзистором n-типа и тактовой шиной формируют парафазный тактовый сигнал, необходимый для полной передачи сигнала (как высокого, так и нулевого уровней), формируемого логическим блоком, через открывающиеся по такту ключевые транзисторы дополняющего типа на вход КМДП инвертора. При этом для реализации технического приема используется всего 8 МДП транзисторов, включая инвертор. Таким образом, в изобретении достигается положительный эффект - упрощение устройства. На чертеже приведена принципиальная схема заявляемого тактируемого логического элемента на примере ключевых цепей, содержащих по два последовательно соединенных транзистора n-типа (элемент 2И-ИЛИ).

Тактируемый логический элемент содержит предзарядовый транзистор 1 p-типа, тактовый транзистор 2 n-типа, тактовый транзистор 3 p-типа, транзистор обратной связи 4 p-типа, ключевой транзистор 5 n-типа, ключевой транзистор 6 p-типа, КМДП инвертор 7, логический блок 8, содержащий ключевые цепи 9-10, выполненные на последовательно соединенных транзисторах n-типа, затворы которых подключены к логическим входам 11 элемента.

Предзарядовый транзистор 1 p-типа включен между шиной питания 12 и первым выводом 13 ключевых цепей 9-10, второй вывод 14 которых через тактовый транзистор 2 n-типа подключен к шине земли 15. Тактовый транзистор 3 p-типа включен между шиной питания 12 и вторым выводом 14 ключевых цепей 9-10. Ключевые транзисторы 5 n-типа и 6 p-типа включены параллельно между первым выводом 13 ключевых цепей 9-10 и входом 16 КМДП инвертора 7, выход которого 18 является выходом устройства и соединен дополнительно с затвором транзистора обратной связи 4 p-типа, который включен между шиной питания 12 и входом КМДП инвертора 7, выход которого может является инверсным выходом 19 устройства.

Затворы предзарядового транзистора 1 p-типа, тактового транзистора 2 n-типа, тактового транзистора 5 n-типа и ключевого транзистора 5 n-типа подключены к тактовой шине 20, а затвор ключевого транзистора 6 p-типа подключен к второму выводу 14 ключевых цепей 9-10.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при нулевом сигнале на тактовой шине 20 тактовый транзистор 2 n-типа закрыт, а предзарядовый транзистор 1 p-типа открыт, и на первом выводе 13 ключевых цепей 8 и 10 формируется высокий уровень сигнала. Ключевые цепи независимо от сигналов на логических входах 11 находятся в непроводящем состоянии. Ключевые транзисторы 5-6 при этом закрыты парафазными сигналами на их затворах. На этом полутакте на логических входах 11 устанавливаются сигналы, соответствующие входным переменным.

На втором полутакте после подачи сигнала высокого уровня на тактовую шину 20 предзарядовый 1 и тактовый 3 транзисторы p-типа закрываются, а тактовый транзистор 2 n-типа открывается. Ключевые транзисторы 5-6 при этом открываются. Если сигналы, подаваемые на логические входы 11, соответствуют значению функции, равной 0, ключевые цепи 9-10 остаются в непроводящем состоянии, и на вход 16 инвертора 7 передается высокий уровень сигнала, в результате чего на выходе 18 устройства формируется логический 0. Открытый при этом транзистор 4 обратной связи p-типа надежно обеспечивает состояние КМДП инвертора 7 на втором полутакте.

Когда на затворы транзисторов n-типа хотя бы одной из ключевых цепей 9 или 10 от логических входов 11 поданы сигналы логической 1, что соответствует функции И, равной 1, соответствующая ключевая цепь оказывается в проводящем состоянии и узловая емкость первого вывода 13 ключевых цепей логического блока 8 разряжается до нулевого уровня, т.к. тактовый транзистор 2 n-типа открыт. На вход 16 КМДП инвертора 7 при этом через ключевые транзисторы 5-6 передается сигнал низкого уровня, и на выходе 18 устройства формируется высокий уровень сигнала, соответствующий логической 1. Транзистор 4 обратной связи p-типа при этом закрывается.

Восстановление исходного состояния происходит при подаче на тактовую шину 20 сигнала низкого уровня. Ключевые транзисторы 5-6 изолируют вход КМДП инвертора на полутакте, т.к. они закрываются раньше, чем за счет предзарядового транзистора 1 p-типа, и изменится уровень сигнала на первом выводе 13 ключевых цепей логического блока 8.

Логический блок 6 может содержать более двух ключевых цепей, включенных параллельно с различным числом последовательно включенных транзисторов n-типа, что позволяет реализовывать многофункциональные логические устройства от большего числа входных переменных.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОВХОДОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И НА КМДП ТРАНЗИСТОРАХ | 2006 |

|

RU2319299C1 |

| ТАКТИРУЕМЫЙ МНОГОВХОДОВЫЙ ЭЛЕМЕНТ И | 2009 |

|

RU2412542C1 |

| Многовходовый логический элемент И | 2015 |

|

RU2613853C2 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ НА КМДП ТРАНЗИСТОРАХ | 2008 |

|

RU2368072C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2012 |

|

RU2515702C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

| ТАКТИРУЕМЫЙ ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2382490C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2007 |

|

RU2334354C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| ДИНАМИЧЕСКИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2015 |

|

RU2580095C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в упрощении устройства. Тактируемый логический элемент, содержащий предзарядовый транзистор р-типа, тактовый транзистор n-типа, тактовый транзистор р-типа, транзистор обратной связи р-типа, ключевой транзистор n-типа, ключевой транзистор р-типа, КМДП инвертор, логический блок, содержащий ключевые цепи, выполненные на последовательно соединенных транзисторах n-типа, затворы которых подключены к логическим входам элемента. Предзарядовый транзистор включен между шиной питания и первым выводом ключевых цепей, второй вывод которых через тактовый транзистор подключен к шине земли. Тактовый транзистор включен между шиной питания и вторым выводом ключевых цепей. Ключевые транзисторы включены параллельно между первым выводом ключевых цепей и входом КМДП инвертора, выход которого является выходом устройства и соединен дополнительно с затвором транзистора обратной связи, который включен между шиной питания и входом КМДП инвертора. Затворы предзарядового транзистора, тактовых транзисторов, ключевого транзистора подключены к тактовой шине, а затвор ключевого транзистора подключен ко второму выводу ключевых цепей. 1 ил.

Тактируемый логический элемент, содержащий предзарядовый транзистор р-типа и тактовый транзистор n-типа, затворы которых подключены к тактовый шине, транзистор обратной связи р-типа, выходной инвертирующий элемент и логический блок, содержащий ключевые цепи, первые выводы которых объединены и через предзарядовый транзистор р-типа подключены к шине питания, вторые их выводы объединены и через тактовый транзистор n-типа подключены к шине земли, каждая ключевая цепь состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к логическим входам элемента, выходной инвертирующий элемент включен между шинами питания и земли, а его выход является выходом устройства, отличающийся тем, что содержит тактовый транзистор р-типа, ключевой транзистор n-типа и ключевой транзистор р-типа, а выходной инвертирующий элемент выполнен как КМДП инвертор, тактовый транзистор р-типа включен между шиной питания и вторым выводом ключевых цепей, ключевые транзисторы включены параллельно между первым выводом ключевых цепей и входом КМДП инвертора, затворы тактового транзистора р-типа и ключевого транзистора n-типа соединены с тактовой шиной, а затвор ключевого транзистора р-типа соединен с вторым выводом ключевых цепей, транзистор обратной связи р-типа, затвор которого соединен с выходом устройства, включен между шиной питания и входом КМДП инвертора.

| US 7417465 B2, 26.08.2008 | |||

| US 7429880 B2, 30.09.2008 | |||

| US 7212039 B2, 01.05.2007 | |||

| ТАКТИРУЕМЫЙ ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2382490C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ НА КМДП ТРАНЗИСТОРАХ | 2008 |

|

RU2368072C1 |

| Функциональный коммутатор на КМДП-транзисторах | 1988 |

|

SU1506540A1 |

Авторы

Даты

2011-08-20—Публикация

2010-05-24—Подача