Изобретение относится к области вычислительной техники и может быть использовано в КМДП интегральных схемах для реализации логических устройств.

Известен тактируемый двухкаскадный логический элемент с парафазными входами и выходами (Патент США №4570084, Н03К 19/017, 19/20, НКИ 326/98 от 11.02.1986). Он содержит предзарядовые и дополнительные транзисторы р-типа, ключевые цепи на транзисторах n-типа, тактовые транзисторы n-типа и выходные статические инверторы. Недостатком элемента является ограниченное быстродействие за счет дополнительных емкостных нагрузок на выходах и тактового транзистора в ключевых цепях.

Наиболее близким техническим решением к предлагаемому является парафазный логический элемент (Патент РФ №2209508, Н03К 19/017, от 13.05.2002). Это устройство, принятое за прототип, содержит два предзарядовых транзистора р-типа, два инвертора, тактовый транзистор n-типа и логический блок в виде ключевых цепей на транзисторах n-типа. Недостаток этого устройства - избыточное потребление мощности, т.к. в начальной фазе выключения элемента от источника питания протекает сквозной ток на шину земли за счет частично открытого состояния транзисторов инвертора и тактовых транзисторов.

Технической задачей, решаемой в изобретении, является уменьшение мощности, потребляемой устройством.

Поставленная цель достигается тем, что в парафазном логическом элементе, содержащем два предзарядовых транзистора р-типа, затворы которых подключены к тактовой шине, два логических транзистора р-типа, два предзарядовых транзистора n-типа, затворы которых объединены, тактовый транзистор n-типа и логический блок, содержащий прямые и инверсные ключевые цепи, каждая из которых состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к парафазным логическим входам устройства таким образом, что только одна ключевая цепь нормально замкнута, а все другие - нормально разомкнуты, при этом первые выводы всех ключевых цепей объединены, вторые выводы прямых ключевых цепей подключены к затвору первого логического транзистора р-типа и через первый предзарядовый транзистор р-типа соединены с шиной питания, вторые выводы инверсных ключевых цепей подключены к затвору второго логического транзистора р-типа и через второй предзарядовый транзистор р-типа соединены с шиной питания, первый и второй предзарядовые транзисторы n-типа включены между шиной земли и соответственно прямым и дополняющим выходами устройства, согласно изобретению первые выводы ключевых цепей подключены к противофазной тактовой шине, первый и второй логические транзисторы р-типа включены между тактовой шиной и соответственно прямым и дополняющим выходами устройства, а тактовый транзистор n-типа, затвор которого соединен с шиной питания, включен между противофазной тактовой шиной и затворами предзарядовых транзисторов n-типа.

Существенными отличительными признаками в указанной совокупности признаков является подключение первых выводов ключевых цепей непосредственно к противофазной тактовой шине, подключение логических транзисторов р-типа между тактовой шиной и соответственно прямым и дополняющим выходами устройства и наличие тактового транзистора в качестве элемента задержки в цепи затворов предзарядовых транзисторов n-типа.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - уменьшение мощности, потребляемой устройством. В известном устройстве на полутакте выключения элемента через инвертор протекает сквозной ток от шины питания на шину земли, который связан с неодновременным открыванием или закрыванием транзисторов n- и р-типов инвертора. Временной интервал, соответствующий частично открытому состоянию обоих транзисторов инвертора, зависит от скорости перезаряда узловых емкостей элемента, т.е. от изменения потенциалов на их затворах и определяется параметрами транзисторов - предзарядовых р-типа, транзисторов ключевых цепей и тактового транзистора n-типа. Это обуславливает зависимость дополнительного потребления мощности от длительности фронта тактового сигнала, размеров транзисторов и сложности логического блока.

В заявленном устройстве осуществляется прерывание цепи источника питания по сигналу на тактовой шине как предзарядовых транзисторов р-типа, так и логических транзисторов р-типа. Одновременно от противофазной тактовой шины тактируются предзарядовые транзисторы n-типа и ключевые цепи. При этом исключаются сквозные токи через одновременно открытые транзисторы, зависимые от скорости перезаряда узловых емкостей элемента. При рассогласовании фронтов сигналов на тактовой и противофазной тактовой шинах возможно открытие предзарядового транзистора n-типа до того, как существенно снизится потенциал тактовой шины. Поэтому тактовый транзистор n-типа включен в цепь управления затворами предзарядовых транзисторов n-типа. Постоянно открытый по затвору этот транзистор играет роль элемента задержки, т.к. создает дополнительное сопротивление в цепи заряда емкостей затворов этих транзисторов. Это замедление открывания предзарядовых транзисторов n-типа не влияет на включение элемента, которое определяется сигналами на тактовых шинах, т.к. логический транзистор р-типа открывается по затвору с задержкой в логическом блоке. Но при выключении элемента тактовый транзистор n-типа обеспечивает дополнительную задержку открытия предзарядовых транзисторов n-типа при неполном спаде потенциала на тактовой щине при еще открытом логическом транзисторе. Таким образом минимизируются сквозные токи при переключении и уменьшается потребление мощности.

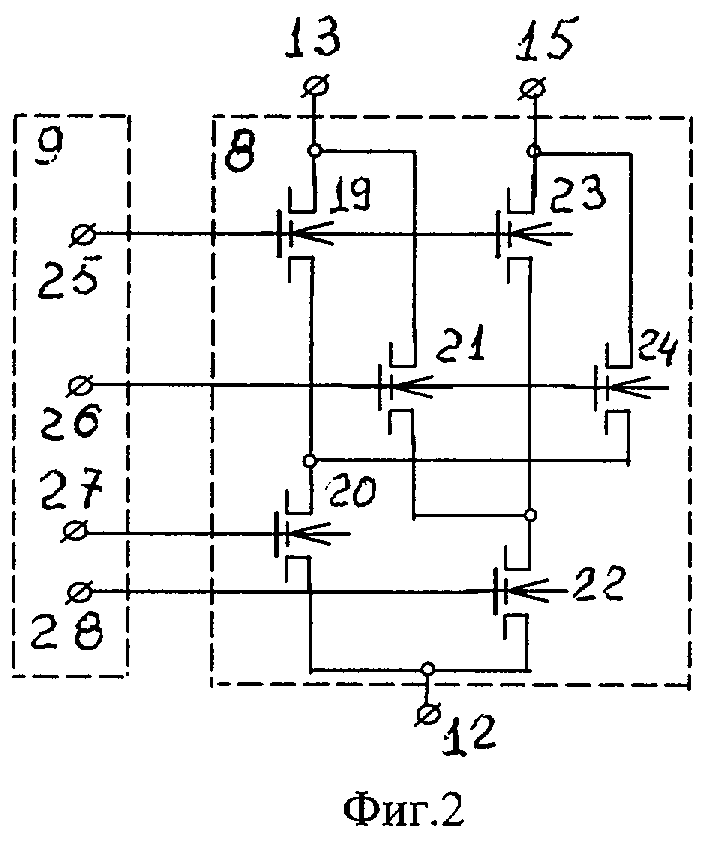

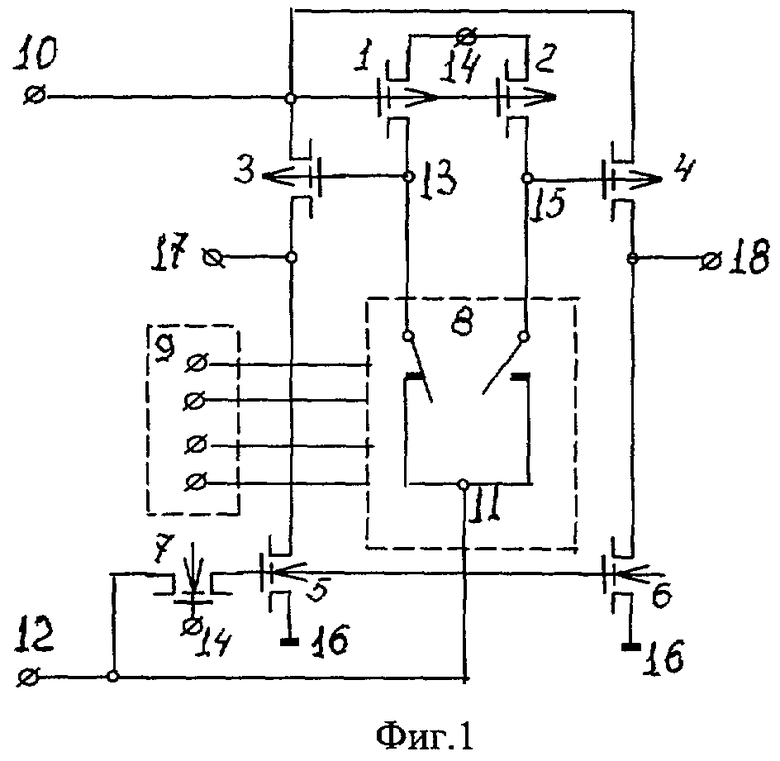

На фиг.1 приведена принципиальная схема заявляемого парафазного логического элемента. На фиг.2 приведена в качестве примера принципиальная схема логического блока для реализации функции ′Исключающее ИЛИ′.

Парафазный логический элемент (фиг.1) содержит первый 1 и второй 2 предзарядовые транзисторы р-типа, первый 3 и второй 4 логические транзисторы р-типа, первый 5 и второй 6 предзарядовые транзисторы n-типа, тактовый транзистор 7 n-типа и логический блок 8, содержащий прямые и инверсные ключевые цепи, каждая из которых состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к парафазным логическим входам 9 устройства таким образом, что только одна ключевая цепь нормально замкнута, а все другие - нормально разомкнуты.

Затворы предзарядовых транзисторов р-типа подключены к тактовой шине 10, а первые выводы 11 всех ключевых цепей подключены к противофазной тактовой шине 12, вторые выводы 13 прямых ключевых цепей подключены к затвору первого логического транзистора 3 р-типа и через первый предзарядовый транзистор 1 р-типа соединены с шиной питания 14, вторые выводы 15 инверсных ключевых цепей подключены к затвору второго логического транзистора 4 р-типа и через второй предзарядовый транзистор 2 р-типа соединены с шиной питания 14. Первый 5 и второй 6 предзарядовые транзисторы n-типа включены между шиной земли 16 и соответственно прямым 17 и дополняющим 18 выходами устройства. Первый 3 и второй 4 логические транзисторы р-типа включены между тактовой шиной 10 и соответственно прямым 17 и дополняющим 18 выходами устройства. Тактовый транзистор 7 n-типа, затвор которого соединен с шиной питания 14, включен между противофазной тактовой шиной 12 и объединенными затворами предзарядовых транзисторов 5 и 6 n-типа.

Логический блок 8 при реализации функции ′Исключающее ИЛИ′ (фиг.2) содержит 6 транзисторов 19-24 n-типа, которые включены попарно последовательно и составляют 4 ключевые цепи логического блока: первая прямая содержит первый 19 и второй 20 транзисторы, вторая прямая - третий 21 и четвертый 22 транзисторы, третья - инверсная - четвертый 22 и пятый 23 транзисторы, четвертая инверсная - шестой 24 и второй 20 транзисторы. Количество ключевых цепей соответствует числу логических состояний элемента - в данном случае 4 от двух переменных. Затворы первого 19 и пятого 23 транзисторов n-типа подключены к первому 25 логическому входу устройства, затворы третьего 21 и шестого 24 транзисторов подключены к второму 26 логическому входу, затворы второго 20 и четвертого 22 подключены соответственно к третьему 27 и четвертому 28 логическим входам устройства.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте - при единичном сигнале на противотактовой шине 12 и нулевом сигнале на тактовой шине 10 предзарядовые транзисторы р-типа 1 и 2 открыты, ключевые цепи логического блока 8 не проводят ток, потенциалы затворов логических транзисторов 3 и 4 р-типа равны напряжению на шине питания 14 и поэтому они закрыты, предзарядовые транзисторы 5 и 6 n-типа открыты и сигналы на выходах 17 и 18 устройства нулевые. На логических входах 9 устанавливаются парафазные сигналы, соответствующие входным переменным. На первый 25 и второй 26 логические входы для заданной, в данном случае, функции ′Исключающее ИЛИ′ поданы соответственно прямой и дополняющий сигналы первой переменной X, а на третий 27 и четвертый 28 логические входы поданы соответственно прямой и дополняющий сигналы второй переменной Y. При равенстве переменных X=Y в замкнутом состоянии находятся первая (при Х=1) или вторая (при Х=0) ключевые цепи логического блока. При логическом неравенстве переменных в замкнутом состоянии находятся третья или четвертая комбинационные цепи. Нулевые потенциалы выходов устройства в исходном состоянии обеспечивают непроводящее состояние всех ключевых цепей логических блоков последующих логических каскадов.

На втором полутакте после подачи напряжения питания на тактовую шину 10 и нулевого потенциала на противофазную тактовую шину 12 предзарядовые транзисторы 1-2 р-типа и предзарядовые транзисторы 5-6 n-типа закрываются и начинает протекать ток через ключевую цепь, находящуюся в проводящем состоянии. Если в замкнутом состоянии находится первая или вторая ключевые цепи, то благодаря току узловая емкость второго вывода 13 прямых ключевых цепей разряжается и потенциал затвора первого логического транзистора 3 р-типа падает, в результате чего он открывается. При этом начинает рости потенциал на емкости нагрузки, связанной с прямым выходом 17 устройства, что соответствует логической 1 при X=Y. На дополняющем выходе 18 устройства при этом сохраняется нулевой потенциал, соответствующий неравенству входных переменных.

При выключении устройства и восстановлении исходного состояния падает потенциал на тактовой шине 10 и растет потенциал на противофазной тактовой шине 12. Первый предзарядовый транзистор 5 n-типа постепенно открывается с задержкой относительно изменения потенциала тактовой шины 10, обусловленной сопротивлением тактового транзистора 7 n-типа. Тем самым исключается значительный сквозной ток в цепи открытого логического транзистора 3 р-типа на фронте спада потенциала на тактовой шине 10, который может обладать большой проводимостью при работе на соответствующую емкостную нагрузку. Предзарядовые транзисторы n- и р-типа при этом могут иметь минимальную проводимость с соответственно минимальными размерами ширины каналов. Восстановление исходного высокого потенциала на затворе первого логического транзистора 3 р-типа осуществляется как током соответствующего предзарядового транзистора р-типа, так и обратным током одной из ключевых цепей логического блока. Полный разряд емкости нагрузки прямого выхода 17 устройства до нулевого потенциала происходит за счет тока предзарядового транзистора n-типа уже при отсутствии напряжения на тактовой шине 10. Таким образом, противофазное тактирование при минимальных размерах предзарядовых транзисторов обоих типов и наличии элемента задержки позволяет минимизировать потребление мощности независимо от длительности фронтов тактовых сигналов и их рассогласований во времени.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2258303C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2014 |

|

RU2542660C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| МНОГОРАЗРЯДНОЕ УСТРОЙСТВО ЛОГИЧЕСКОГО СРАВНЕНИЯ | 2007 |

|

RU2328026C1 |

| ТАКТИРУЕМЫЙ ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2382490C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ПЕРЕНОСА В СУММАТОРЕ | 2013 |

|

RU2525111C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КАСКАДНЫХ УСТРОЙСТВ НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209508C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ | 2012 |

|

RU2515702C1 |

Изобретение относится к области вычислительной техники и может быть использовано в МДП интегральных схемах для реализации логических устройств. Достигаемый технический результат - уменьшение потребляемой мощности. Парафазный логический элемент содержит предзарядовые и логические транзисторы р-типа, предзарядовые и тактовый транзистор n-типа, логический блок, содержащий прямые и инверсные ключевые цепи на последовательно соединенных транзисторах n-типа. 2 ил.

Парафазный логический элемент, содержащий два предзарядовых транзистора р-типа, затворы которых подключены к тактовой шине, два логических транзистора р-типа, два предзарядовых транзистора n-типа, затворы которых объединены, тактовый транзистор n-типа и логический блок, содержащий прямые и инверсные ключевые цепи, каждая из которых состоит из последовательно соединенных транзисторов n-типа, затворы которых подключены к парафазным логическим входам устройства таким образом, что только одна ключевая цепь нормально замкнута, а все другие нормально разомкнуты, при этом первые выводы всех ключевых цепей объединены, вторые выводы прямых ключевых цепей подключены к затвору первого логического транзистора р-типа и через первый предзарядовый транзистор р-типа соединены с шиной питания, вторые выводы инверсных ключевых цепей подключены к затвору второго логического транзистора р-типа и через второй предзарядовый транзистор р-типа соединены с шиной питания, первый и второй предзарядовые транзисторы n-типа включены между шиной земли и соответственно прямым и дополняющим выходами устройства, отличающийся тем, что первые выводы ключевых цепей подключены к противофазной тактовой шине, первый и второй логические транзисторы р-типа включены между тактовой шиной и соответственно прямым и дополняющим выходами устройства, а тактовый транзистор n-типа, затвор которого соединен с шиной питания, включен между противофазной тактовой шиной и затворами предзарядовых транзисторов n-типа.

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КАСКАДНЫХ УСТРОЙСТВ НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209508C1 |

| US 4570084 А, 11.02.1986 | |||

| Многофункциональный парафазный логический модуль | 1988 |

|

SU1621017A1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

Авторы

Даты

2010-06-27—Публикация

2009-03-06—Подача