Изобретение относится к технике формирования и передачи изображений, а точнее к тепловидению, и может использоваться для поиска и идентификации потерь тепла и анализа выхода из строя в тепловых машинах и сетях, жилых и производственных помещениях с целью энергосбережения, а также для контроля электросетей для предотвращения аварийных ситуаций.

Известен тепловизор, в котором отсутствует ручная регулировка по эталонному источнику, так как опорная температура автоматически вводится в алгоритм обработки сигнала. [1] Указанный тепловизор содержит зеркало, служащее оптическим переключателем, с датчиком положения и приводом вращения, оптически связанный с ним источник эталонного излучения, с датчиком температуры, находящимся с ним в тепловом контакте, последовательно расположенные по ходу оптического сигнала объектив и фотоприемник (ФП), а также последовательно соединенные с ФП усилитель, аналого-цифровой преобразователь (АЦП) и микропроцессорный контроллер с блоком памяти. Сигнал с датчика температуры эталонного источника поступает в микропроцессорный контроллер и используется для вычисления температуры объекта. Оптический зеркальный переключатель попеременно направляет на ФП поток от объекта и эталонного источника. ФП преобразует оптический сигнал в электрический, который после усиления поступает на АЦП, где преобразуется в цифровую форму и заносится в память микропроцессорного контроллера. В свою очередь, в память микропроцессорного контроллера записана калибровочная кривая зависимости амплитуды сигнала, поступающего на АЦП от температуры. Сигнал с эталонного источника и сигнал с датчика температуры эталонного источника используется для автоматической корректировки калибровочной кривой сигнала по оси температур. Таким образом, достигается соответствие (привязка) выходного сигнала опорной температуре.

Недостатками известного прибора являются увеличенные габариты, обусловленные наличием эталонного источника, и связанное с этим повышенное энергопотребление, а также наличие ошибки, возникающей в результате дрейфа параметров ФП. Эта ошибка в описанном тепловизоре не может быть устранена, так как автоматическая корректировка калибровочной кривой в нем возможна только по одной точке.

Известен тепловизор на основе «смотрящей» матрицы из Cd0,2Hg0,8Те формата 128×128. [2]

Указанный тепловизор содержит матрицу фотоприемников (МФП), микрокриогенную систему типа Сплит-Стирлинга, ИК-объектив с фокусным расстоянием 70 мм и относительным отверстием 1:1,5, аналого-цифровой преобразователь (АЦП) и блок цифровой обработки, первый выход которого соединен с первым входом МФП, второй вход которой соединен со вторым выходом блока цифровой обработки, третий выход которого соединен с телевизором, причем первый вход блока цифровой обработки соединен с первым выходом МФП, третий вход которой соединен с выходом объектива, вход которого является входом тепловизора, четвертый вход МФП соединен с микрокриогенной системой, вход которой соединен с блоком управления микрокриогенной системы, причем блок цифровой обработки, состоящий из центрального процессора (ЦП), ОЗУ и ПЗУ, выполняет двухточечную коррекцию неравномерности чувствительности и осуществляет алгоритм устранения из изображения дефектных элементов. На выходе блока формируется стандартный телевизионный сигнал с частотой кадров 25 Гц. Описанное устройство, как наиболее близкое к предлагаемому, принято за прототип и представлено на фиг.1.

Данное устройство имеет следующие недостатки:

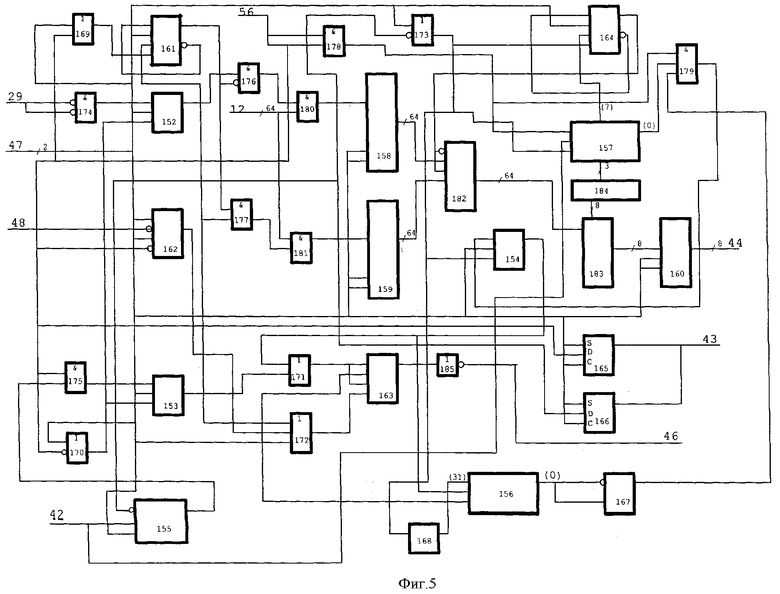

- не слишком высокая предельная температурная чувствительность;

- недостаточная контрастность изображения;

- недостаточное качество изображения.

Задачей изобретения является увеличение предельной температурной чувствительности, контрастности и качества изображения.

Увеличение предельной температурной чувствительности достигается за счет увеличения разрядности АЦП (14 разрядов).

Увеличение контрастности в области относительной интенсивности, близкой к нулю, достигается за счет некоторого сокращения квантов, выделенных для кодирования интенсивностей вне этой области.

Увеличение качества изображения достигается за счет увеличения матрицы и за счет более точных калибровок механизмов обнаружения и исправления дефектных точек.

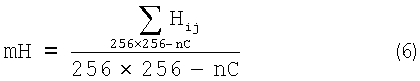

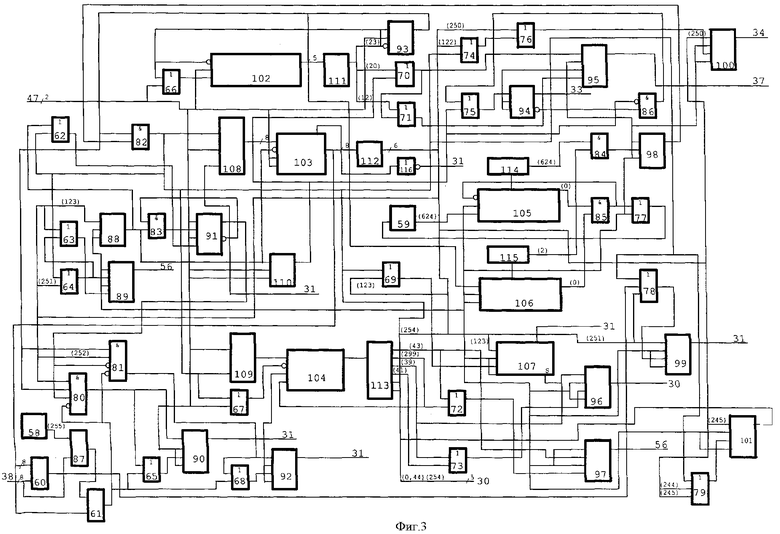

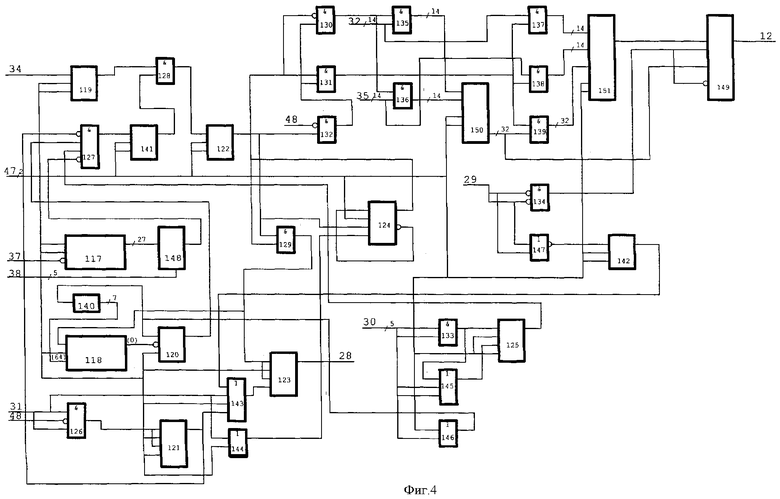

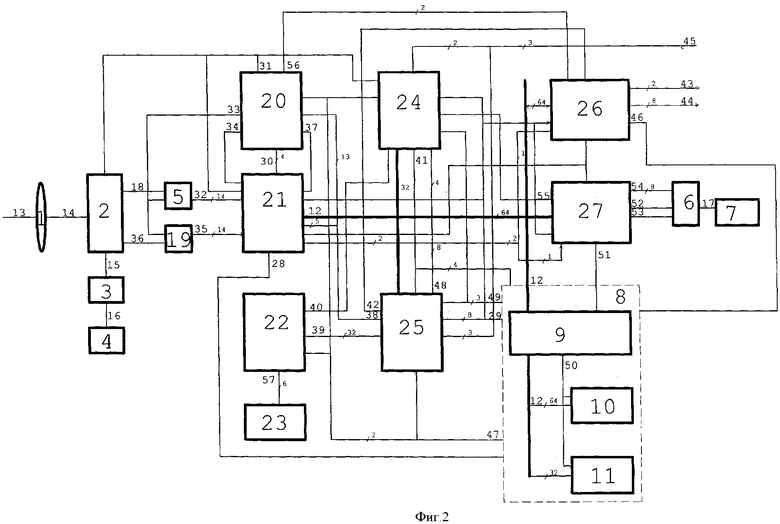

Сущность заявляемого изобретения, возможность его осуществления и промышленного использования поясняются чертежами, представленными на фиг.2-11, где

- на фиг.2 представлена структурная схема тепловизора;

- на фиг.3 представлена функциональная схема блока управления МФП;

- на фиг.4 представлена функциональная схема блока формирования данных;

- на фиг.5 представлена функциональная схема блока формирования цифровых сигналов;

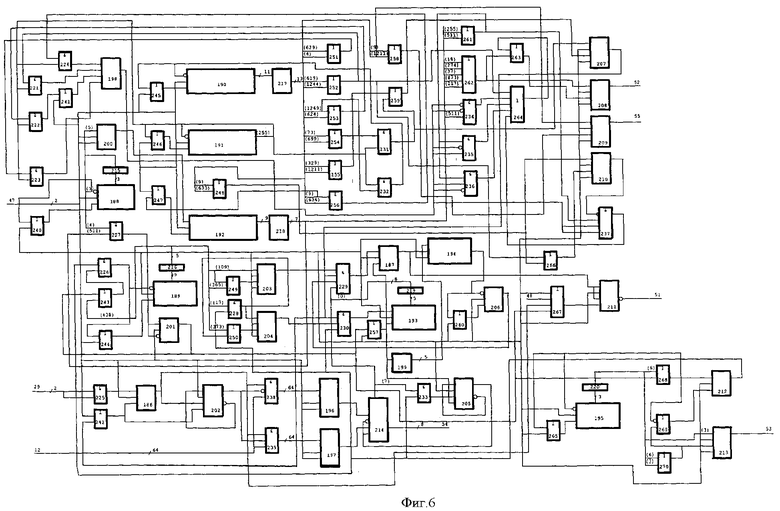

- на фиг.6 представлена функциональная схема блока формирования телевизионных сигналов;

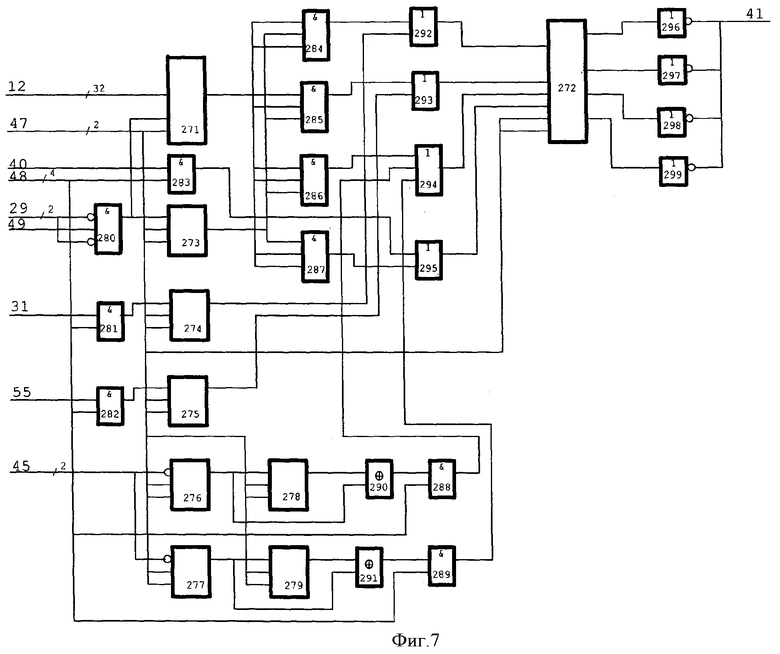

- на фиг.7 представлена функциональная схема блока прерываний;

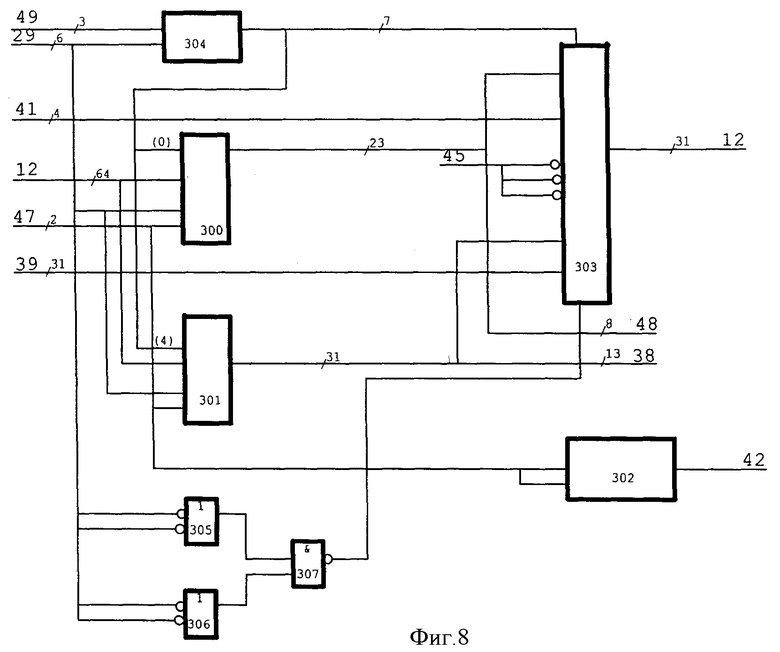

- на фиг.8 представлена функциональная схема блока управления;

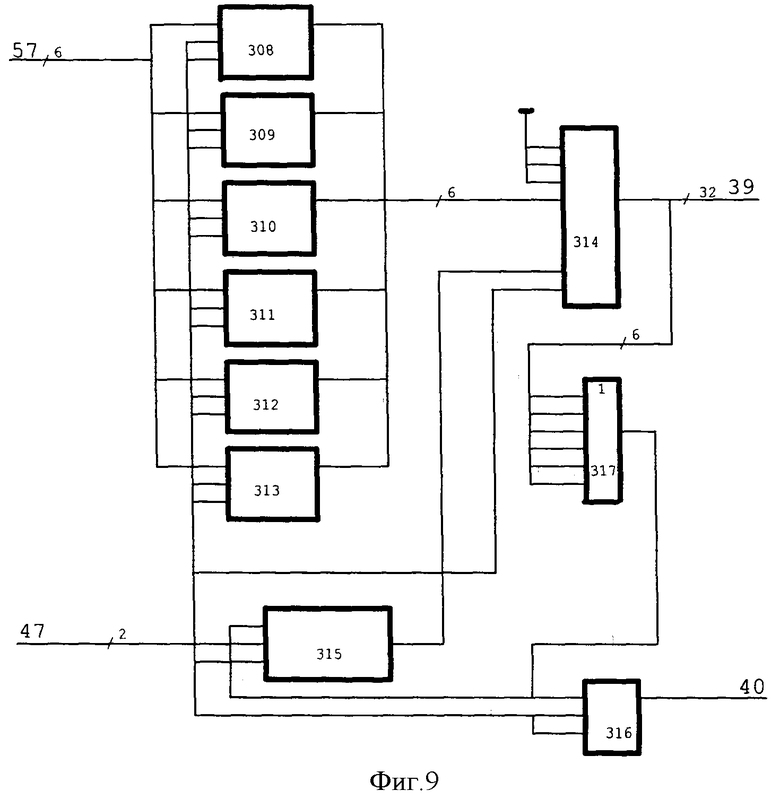

- на фиг.9 представлена функциональная схема блока управления с клавиатуры;

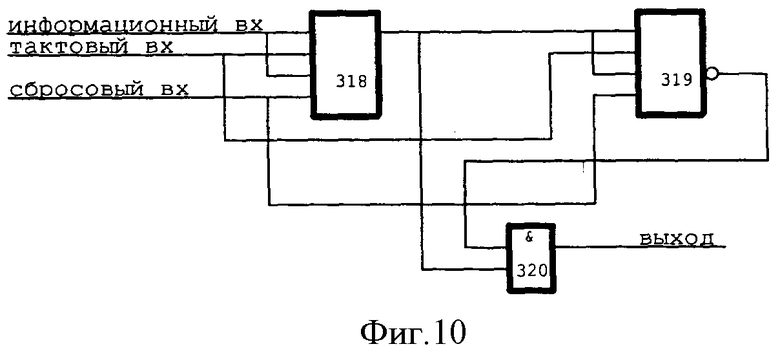

- на фиг.10 представлена функциональная схема формирователя одиночного импульса;

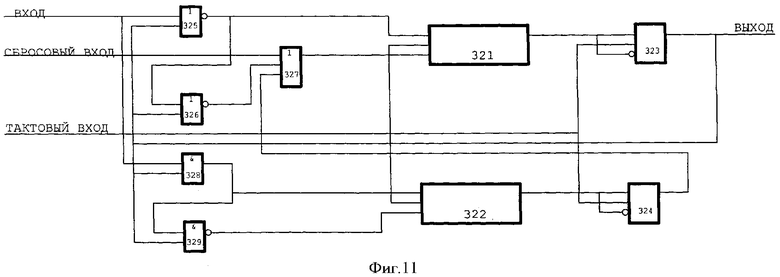

- на фиг.11 представлена функциональная схема узла устранения дребезга;

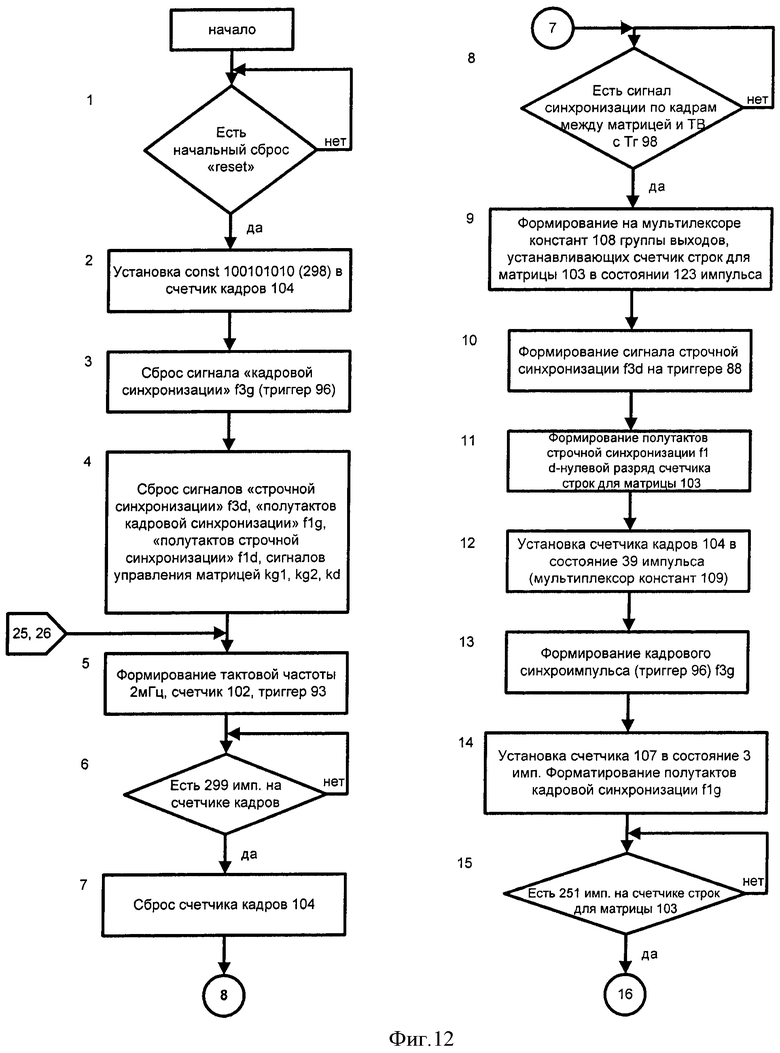

- на фиг.12 представлен алгоритм формирования управляющих импульсов на МФП 2 в блоке управления МФП 20;

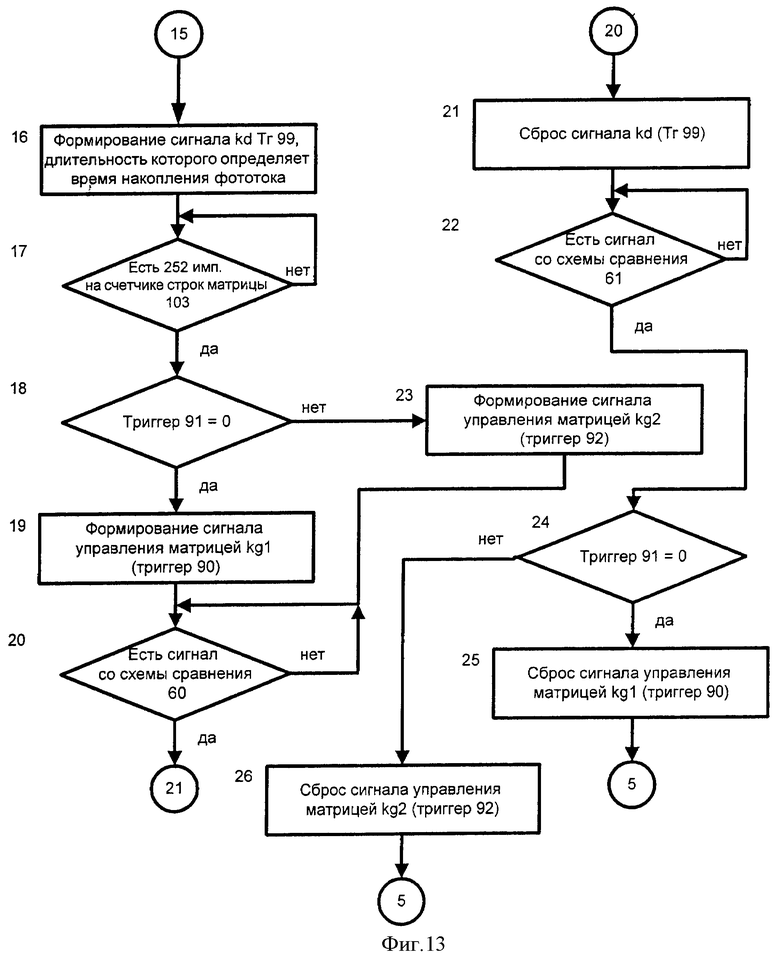

- на фиг.13 представлено продолжение алгоритма формирования управляющих импульсов на МФП 2 в блоке управления МФП 20;

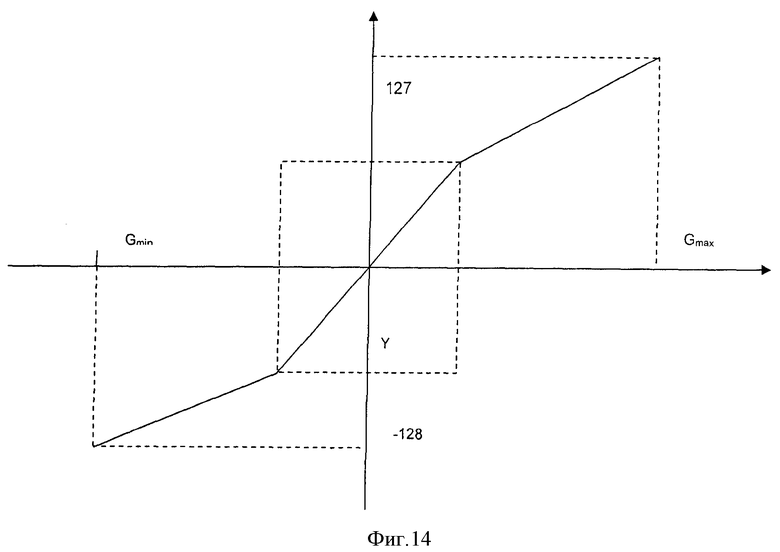

- на фиг.14 представлен график кусочно-линейного контрастирования с подстройкой параметров в реальном времени.

Указанные преимущества заявляемого устройства перед прототипом достигаются за счет того, что в тепловизор, содержащий объектив 1, матрицу фотоприемников (МФП) 2, микрокриогенную систему (МКС) 3, блок управления МКС 4, АЦП 5, ЦАП 6, телевизор 7, блок цифровой обработки 8, состоящий из центрального процессора 9, ОЗУ 10, ПЗУ 11, группа входов-выходов 12 которого соединена с группами входов-выходов ОЗУ 10 и центрального процессора 9, причем вход тепловизора является входом 13 объектива, выход 14 которого соединен с первым входом МФП 2, второй вход 15 которой соединен с выходом МКС 3, вход 16 которой соединен с блоком управления МКС 4, выход ЦАП 17 соединен с входом телевизора 7, причем первый выход 18 МФП соединен с первым входом первого АЦП 5, дополнительно введены второе АЦП 19, блок управления матрицей фотоприемников 20, блок формирования данных 21, блок управления с клавиатуры 22, клавиатура 23, блок прерываний 24, блок управления 25, блок формирования цифровых сигналов 26, блок формирования телевизионных сигналов 27, группа входов-выходов 12 которого соединена с группами входов-выходов блока цифровой обработки 8, блока управления 25, блока формирования цифровых сигналов 26, блока прерываний 24 и блока формирования данных 21, выход 28 которого соединен с первым входом центрального процессора 9, первая группа выходов 29 которого соединена с первыми группами входов блока управления 25 и блока прерываний 24, блока формирования цифровых сигналов 26, блока формирования телевизионных сигналов 27 и блока формирования данных 21, вторая группа 30 входов которого соединена с первой группой выходов блока управления МФП 20, вторая группа выходов 31 которого соединена с первой группой входов МФП 2, с первым входом блока прерываний 24 и с третьей группой входов блока формирования данных 21, четвертая группа входов 32 которого соединена с группой выходов первого АЦП 5, второй вход 33 которого соединен с первым входом второго АЦП 19 и первым выходом блока управления МФП 20, второй выход 34 которого соединен с первым входом блока формирования данных 21, пятая группа входов 35 которого соединена с группой выходов второго АЦП 19, второй вход 36 которого соединен со вторым выходом МФП 2, причем третий выход 37 блока управления МФП 20 соединен со вторым входом блока формирования данных 21, шестая группа входов 38 которого соединена с первой группой входов блока управления МФП 20 и с первой группой выходов блока управления 25, вторая группа входов 39 которого соединена с первой группой выходов блока управления с клавиатуры 22, выход 40 которого соединен со вторым входом блока прерываний 24, первая группа выходов 41 которого соединена с первой группой входов центрального процессора 9 и третьей группой входов блока управления 25, первый выход 42 которого соединен с первым входом блока формирования цифровых сигналов 26, первая 43 и вторая 44 группы выходов которого являются первой и второй группами выходов тепловизора соответственно, группа входов 45 которого соединена со второй группой входов блока прерываний 24 и четвертой группой входов блока управления 25, причем выход 46 блока формирования цифровых сигналов 26 соединен со вторым входом центрального процессора 9, вторая группа выходов 47 которого соединена с первой группой входов блока управления с клавиатуры 22, со вторыми группами входов блока формирования цифровых сигналов 26 и блока формирования телевизионных сигналов 27, с третьими группами входов блока прерываний 24, блока управления МФП 20, с пятой группой входов блока управления 25 и седьмой группой входов блока формирования данных 21, восьмая группа входов 48 которого соединена со вторым входом блока формирования цифровых сигналов 26 и первым входом блока формирования телевизионных сигналов 27, с четвертой группой входов блока прерываний 24 и второй группой выходов блока управления 25, шестая группа входов 49 которого соединена с пятой группой входов блока прерывания 24 и с третьей группой выходов центрального процессора 9, четвертая группа выходов 50 которого соединена с первыми группами входов ОЗУ 10 и ПЗУ 11. причем третий вход 51 центрального процессора 9 соединен с первым выходом блока формирования телевизионных сигналов 27, второй 52 и третий 53 выходы которого соединены с первым и вторым входами ЦАП 6 соответственно, группа входов которого соединена с группой выходов 54 блока формирования телевизионных сигналов 27, четвертый выход 55 которого соединен с третьим входом блока прерываний 24, причем третья группа выходов 56 блока управления МФП 20 соединена с третьей группой входов блока формирования цифровых сигналов 26, а первая группа выходов 57 клавиатуры 23 соединена со второй группой входов блока управления с клавиатуры 22.

Блок управления МФП 20 состоит из первой 58 константы, второй 59 константы, первой 60 схемы сравнения, второй 61 схемы сравнения, первого 62 элемента ИЛИ, второго 63 элемента ИЛИ, третьего 64 элемента ИЛИ, четвертого 65 элемента ИЛИ, пятого 66 элемента ИЛИ, шестого 67 элемента ИЛИ, седьмого 68 элемента ИЛИ, восьмого 69 элемента ИЛИ, девятого 70 элемента ИЛИ, десятого 71 элемента ИЛИ, одиннадцатого 72 элемента ИЛИ, двенадцатого 73 элемента ИЛИ, тринадцатого 74 элемента ИЛИ, четырнадцатого 75 элемента ИЛИ, пятнадцатого 76 элемента ИЛИ, шестнадцатого 77 элемента ИЛИ, семнадцатого 78 элемента ИЛИ, восемнадцатого 79 элемента ИЛИ, первого 80 элемента И, второго 81 элемента И, третьего 82 элемента И, четвертого 83 элемента И, пятого 84 элемента И, шестого 85 элемента И, седьмого 86 элемента И, сумматора 87, первого 88 триггера, второго 89 триггера, третьего 90 триггера, четвертого 91 триггера, пятого 92 триггера, шестого 93 триггера, седьмого 94 триггера, восьмого 95 триггера, девятого 96 триггера, десятого 97 триггера, одиннадцатого 98 триггера, двенадцатого 99 триггера, тринадцатого 100 триггера, четырнадцатого 101 триггера, первого 102 счетчика, второго 103 счетчика, третьего 104 счетчика, четвертого 105 счетчика, пятого 106 счетчика, шестого 107 счетчика, первого 108 мультиплексора констант, второго 109 мультиплексора констант, формирователя одиночного импульса 110, первого 111 дешифратора, второго 112 дешифратора, третьего 113 дешифратора, четвертого 114 дешифратора, пятого 115 дешифратора, элемента НЕ 116, выход которого является первым сигналом второй группы выходов 31 блока управления МФП 20, второй сигнал второй группы выходов 31 блока управлений МФП 20 соединен с выходом первого 88 триггера, первыми входами первого 62 элемента ИЛИ, четвертого 83 элемента И, первого 108 мультиплексора констант, с инверсным, информационным входом второго 103 счетчика и информационным входом формирователя одиночного импульса 110, третий сигнал второй группы выходов 31 блока управления МФП 20 соединен с выходом девятого 96 триггера, четвертый сигнал второй группы выходов 31 блока управления МФП 20 соединен с выходом шестого 107 счетчика, пятый, шестой и седьмой сигналы второй группы выходов 31 блока управления МФП 20 соединены с выходами третьего 90 триггера, пятого 92 триггера и двенадцатого 99 триггера, информационный вход которого соединен с первыми входами семнадцатого 78 элемента ИЛИ и третьего 64 элемента ИЛИ и является первым сигналом группы выходов второго 112 дешифратора, второй сигнал которой соединен с первым входом тринадцатого 74 элемента ИЛИ, третий сигнал группы выходов второго 112 дешифратора соединен с первыми входами второго 63 и восьмого 69 элементов ИЛИ, с информационными входами первого 88 триггера и шестого 107 счетчика, четвертый сигнал группы выходов второго 112 дешифратора соединен с первым входом пятнадцатого 76 элемента ИЛИ и информационным входом тринадцатого 100 триггера, пятый сигнал группы выходов второго 112 дешифратора соединен с первыми входами первого 80 и второго 81 элементов И, шестой сигнал группы выходов второго 112 дешифратора соединен с первым входом восемнадцатого 79 элемента ИЛИ, седьмой сигнал группы выходов второго 112 дешифратора соединен со вторым входом восемнадцатого 79 элемента ИЛИ и информационным входом четырнадцатого 101 триггера, восьмой сигнал группы выходов второго 112 дешифратора является первым сигналом первой группы выходов 30 блока управления МФП 20, второй сигнал которой соединен с выходом четырнадцатого 101 триггера, третий и четвертый сигналы первой группы выходов 30 блока управления МФП 20 соединены с первым и вторым выходами третьего 113 дешифратора, пятый сигнал первой группы выходов 30 блока управления МФП 20 соединен с выходом третьего 82 элемента И, со вторыми входами первого 108 мультиплексора констант, первого 62, третьего 64, восьмого 69, тринадцатого 74, семнадцатого 78 элементов ИЛИ, с первыми входами второго 109 мультиплексора констант и шестого 67 элемента ИЛИ и третьим входом восемнадцатого 79 элемента ИЛИ, выход которого соединен с разрешающим входом четырнадцатого 101 триггера, тактовый вход которого соединен с тактовыми входами первого 102, второго 103, третьего 104, четвертого 105, пятого 106, шестого 107 счетчиков, первого 88, второго 89, третьего 90, четвертого 91, пятого 92, шестого 93, седьмого 94, восьмого 95, девятого 96, десятого 97, одиннадцатого 98, двенадцатого 99, тринадцатого 100, четырнадцатого 101 триггеров, формирователя одиночного импульса 110 и является первым сигналом третьей группы входов 47 блока управления МФП 20, второй сигнал которой соединен со сбросовыми входами первого 88, третьего 90, пятого 92, девятого 96, двенадцатого 99, тринадцатого 100, четырнадцатого 101 триггеров, второго 103, пятого 106, шестого 107 счетчиков, с первыми входами пятого 66 и шестнадцатого 77 элементов ИЛИ, со вторыми входами второго 109 мультиплексора констант и шестого 67 элемента ИЛИ, с третьим входом первого 108 мультиплексора констант, причем выход первого 62 элемента ИЛИ соединен с разрешающим входом четвертого 91 триггера, инверсный выход которого соединен со вторым входом четвертого 83 элемента И, выход которого соединен с информационным входом четвертого 91 триггера, выход второго 63 элемента ИЛИ соединен с разрешающим входом второго 89 триггера, выход которого является первым сигналом третьей группы выходов 56, второй сигнал которой соединен с выходом десятого 97 триггера, информационный вход которого соединен с первым входом одиннадцатого 72 элемента ИЛИ и третьим выходом третьего 113 дешифратора, четвертый выход которого соединен со вторым входом одиннадцатого 72 элемента ИЛИ и сбросовым входом третьего 104 счетчика, группа выходов которого соединена с группой входов третьего 113 дешифратора, пятый выход которого соединен с первым входом двенадцатого 73 элемента ИЛИ, установочным входом шестого 107 счетчика и информационным входом девятого 96 триггера, разрешающий вход которого соединен с выходом двенадцатого 73 элемента ИЛИ, второй вход которого соединен с шестым выходом третьего 113 дешифратора, группа выходов блока констант 58 соединена с первой группой входов сумматора 87, группа выходов которого соединена с первой группой входов второй 61 схемы сравнения, выход которой соединен с инверсными входами первого 80 и второго 81 элементов И и первыми входами четвертого 65 и седьмого 68 элементов ИЛИ, выход седьмого 68 элемента ИЛИ соединен с разрешающим входом пятого 92 триггера, информационный вход которого соединен со вторым входом седьмого 68 элемента ИЛИ и выходом второго 81 элемента И, второй инверсный вход которого соединен со вторым входом первого 80 элемента И и выходом четвертого 91 триггера, первая группа входов 38 блока управления МФП 20 соединена со второй группой входов сумматора 87 и первой группой входов первой 60 схемы сравнения, выход которой соединен с третьим входом семнадцатого 78 элемента ИЛИ, выход которого соединен с разрешающим входом двенадцатого 99 триггера, первый выход 33 блока управления МФП 20 соединен с выходом седьмого 94 триггера, инверсный выход которого соединен с седьмым 86 элементом И, выход которого соединен с первым входом четырнадцатого 75 элемента ИЛИ, выход которого соединен с информационным входом седьмого 94 триггера, второй выход 34 блока управления МФП 20 соединен с выходом тринадцатого 100 триггера, разрешающий вход которого соединен с выходом пятнадцатого 76 элемента ИЛИ, второй вход которого соединен с выходом тринадцатого 74 элемента ИЛИ, третий выход 37 блока управления МФП 20 соединен с выходом восьмого 95 триггера, информационный вход которого соединен с первым входом десятого 71 элемента ИЛИ и выходом девятого 70 элемента ИЛИ, первый вход которого является первым сигналом группы выходов первого 111 дешифратора, второй сигнал которой соединен с инверсным сбросовым и информационным входами шестого 93 триггера, вторым входом пятого 66 элемента ИЛИ и инверсным разрешающим входом первого 102 счетчика, третий сигнал которой соединен со вторым входом десятого 71 элемента ИЛИ, выход которого соединен с разрешающим входом восьмого 95 триггера, причем группа выходов второго 103 счетчика соединена с группой входов второго 112 дешифратора и вторыми группами входов первой 60 и второй 61 схем сравнения, третий вход первого 80 элемента И соединен со вторым входом второго 81 элемента И, с первым входом третьего 82 элемента И, с разрешающим входом пятого 106 счетчика и выходом шестого 93 триггера, выход первого 80 элемента И соединен со вторым входом четвертого 65 элемента ИЛИ и информационным входом третьего 90 триггера, разрешающий вход которого соединен с выходом четвертого 65 элемента ИЛИ, второй вход третьего 82 элемента И соединен с выходом одиннадцатого 98 триггера, информационный вход которого соединен с выходом пятого 84 элемента И, первый вход которого соединен с выходом четвертого 114 дешифратора, группа входов которого соединена с группой выходов четвертого 105 счетчика, выход которого соединен с первым входом шестого 85 элемента И, выход которого соединен со вторым входом шестнадцатого 77 элемента ИЛИ и инверсным разрешающим входом четвертого 105 счетчика, сбросовый вход которого соединен с выходом второй 59 константы, вход которой соединен с выходом шестнадцатого 77 элемента ИЛИ, выход пятого 66 элемента ИЛИ соединен со сбросовым входом первого 102 счетчика, группа выходов которого соединена с группой входов первого 111 дешифратора, группа выходов первого 108 мультиплексора констант соединена с группой установочных входов второго 103 счетчика, выход которого соединен с входом элемента НЕ 116, выход формирователя одиночного импульса 110 соединен со вторыми входами девятого 70 и четырнадцатого 75 элементов ИЛИ и инверсным входом седьмого 86 элемента И, группа выходов второго 109 мультиплексора констант соединена с группой установочных входов третьего 104 счетчика, инверсный разрешающий вход которого соединен с выходом шестого 67 элемента ИЛИ, выход восьмого 69 элемента ИЛИ соединен с разрешающим входом шестого 107 счетчика, выход пятого 106 счетчика соединен со вторым входом шестого 85 элемента И, выход одиннадцатого 72 элемента ИЛИ соединен с разрешающим входом десятого 97 триггера, выход пятого 115 дешифратора соединен со вторым входом пятого 84 элемента И.

Блок формирования данных 21 состоит из сдвигового регистра 117 счетчика 118, первого 119, второго 120, третьего 121, четвертого 122, пятого 123, шестого 124, седьмого 125 триггеров, первого 126 элемента И, второго 127 элемента И, третьего 128 элемента И, четвертого 129 элемента И, пятого 130 элемента И, шестого 131 элемента И, седьмого 132 элемента И, восьмого 133 элемента И, девятого 134 элемента И, первой 135 группы элементов И, второй 136 группы элементов И, третьей 137 группы элементов И, четвертой 138 группы элементов И, пятой 139 группы элементов И, константы 140, первого 141 формирователя одиночного импульса, второго 142 формирователя одиночного импульса, первого 143 элемента ИЛИ, второго 144 элемента ИЛИ, третьего 145 элемента ИЛИ, четвертого 146 элемента ИЛИ, пятого 147 элемента ИЛИ, первого 148 мультиплексора, второго 149 мультиплексора, первого 150 регистра, второго 151 регистра, группа выходов которого соединена с первой группой входов второго 149 мультиплексора, вторая группа входов которого соединена с группой входов пятой 139 группы элементов И и с группой выходов первого 150 регистра, первая группа входов которого соединена с группой выходов первой 135 группы элементов И, группа входов которых соединена с группой входов третьей 137 группы элементов И и является четвертой 32 группой входов блока формирования данных 21, группа выходов 12 которого соединена с группой выходов второго 149 мультиплексора, вход которого соединен с инверсным входом второго 149 мультиплексора и выходом девятого 134 элемента И, первый и второй инверсные входы которого соединены с первым и вторым входами пятого 147 элемента ИЛИ соответственно и являются первым и вторым сигналами первой 29 группы входов блока формирования данных 21, выход которого соединен с выходом пятого 123 триггера, информационный вход которого соединен с разрешающим входом пятого 123 триггера, с разрешающим входом счетчика 118 и с выходом четвертого 129 элемента И, первый вход которого соединен с разрешающим входом шестого 124 триггера, первым входом седьмого 132 элемента И и выходом четвертого 122 триггера, информационный вход которого соединен с выходом третьего 128 элемента И, первый вход которого соединен с выходом первого 119 триггера, информационный вход которого является первым 34 входом блока формирования данных 21, первый, второй, третий, четвертый, пятый сигналы второй 30 группы входов которого соединены соответственно с первым входом восьмого 133 элемента И, с первым входом четвертого 146 элемента ИЛИ. с первым входом третьего 145 элемента ИЛИ, со вторым входом восьмого 133 элемента И, со вторым входом третьего 145 элемента ИЛИ, выход которого соединен с разрешающим входом седьмого 125 триггера, выход которого соединен с первым входом второго 127 элемента И, выход которого соединен с информационным входом первого 141 формирователя одиночного импульса, выход которого соединен со вторым входом третьего 128 элемента И, второй сигнал третьей 31 группы входов блока формирования данных 21 соединен с первым входом первого 126 элемента И, третий сигнал третьей 31 группы входов блока формирования данных 21 соединен со вторым входом первого 126 элемента И и с первыми входами первого 143 элемента ИЛИ и второго 144 элемента ИЛИ, выход которого соединен со сбросовым входом шестого 124 триггера, выход которого соединен со вторым входом четвертого 129 элемента И, инверсным входом пятого 130 элемента И и первым входом шестого 131 элемента И, выход которого соединен с первыми входами третьей 137 группы элементов И, четвертой 138 группы элементов И и пятой 139 группы элементов И, группы выходов которых соединены с первой, второй и третьей группами входов второго 151 регистра, пятая 35 группа входов блока формирования данных 21 соединена с группой входов второй 136 группы элементов И и с группой входов четвертой 138 группы элементов И, тактовый вход второго 151 регистра является первым сигналом седьмой 47 группы входов и соединен с тактовыми входами первого 150 регистра, первого 141 и второго 142 формирователей одиночного импульса, сдвигового регистра 117, счетчика 118, первого 119, второго 120, третьего 121, четвертого 122, пятого 123, шестого 124, седьмого 125 триггеров, сбросовый вход которого является вторым сигналом седьмой 47 группы входов и соединен со сбросовыми сигналами первого 119, третьего 121, четвертого 122, седьмого 125 триггеров, сдвигового регистра 117, первого 150 регистра, второго 151 регистра, первого 141 и второго 142 формирователей одиночного импульса, со вторыми входами второго 144, четвертого 146 элементов ИЛИ и первого 143 элемента ИЛИ, выход которого соединен со сбросовым входом пятого 123 триггера, причем шестая 38 группа входов блока формирования данных 21 соединена с первой группой входов первого 148 мультиплексора, выход которого соединен с первым инверсным входом второго 127 элемента И, второй инверсный вход которого соединен с третьим входом первого 143 элемента ИЛИ и выходом третьего 121 триггера, информационный и разрешающий входы которого соединены с выходом первого 126 элемента И, инверсный вход которого является первым сигналом восьмой 48 группы входов, второй сигнал которой соединен с инверсным входом седьмого 132 элемента И, выход которого соединен со вторым входом шестого 131 элемента И и первым входом пятого 130 элемента И, выход которого соединен с входами первой группы 135 элементов И и второй группы 136 элементов И, группа выходов которой соединена с информационной группой входов первого 150 регистра, причем группа выходов константы 140 соединена с установочной группой входов счетчика 118, выход которого соединен с информационным, инверсным входом второго 120 триггера, выход которого соединен со вторым входом второго 127 элемента И, причем вход константы соединен с установочным входом второго 120 триггера и выходом четвертого 146 элемента ИЛИ, второй вход 37 блока формирования данных 21 соединен с информационным, инверсным входом сдвигового регистра 117, группа выходов которого соединена со второй группой входов первого 148 мультиплексора, инверсный выход пятого 147 элемента ИЛИ соединен с информационным входом второго 142 формирователя одиночного импульса, выход которого соединен с четвертым входом первого 143 элемента ИЛИ, инверсный выход шестого 124 триггера соединен с его информационным входом, выход восьмого 133 элемента И соединен с третьим входом третьего 145 элемента ИЛИ и информационным входом седьмого 125 триггера.

Блок формирования цифровых сигналов состоит из первого 152 формирователя одиночного импульса, второго 153 формирователя одиночного импульса, третьего 154 формирователя одиночного импульса, сдвигового регистра 155, первого 156 счетчика, второго 157 счетчика, первого 158 регистра, второго 159 регистра, третьего 160 регистра, первого 161 триггера, второго 162 триггера, третьего 163 триггера, четвертого 164 триггера, пятого 165 триггера, шестого 166 триггера, седьмого 167 триггера, константы 168, первого 169 элемента ИЛИ, второго 170 элемента ИЛИ, третьего 171 элемента ИЛИ, четвертого 172 элемента ИЛИ, пятого 173 элемента ИЛИ, первого 174 элемента И, второго 175 элемента И, третьего 176 элемента И, четвертого 177 элемента И, пятого 178 элемента И, шестого 179 элемента И, первой группы 180 элементов И, второй группы 181 элементов И, первого 182 мультиплексора, второго 183 мультиплексора, дешифратора 184 и элемента НЕ 185, выход 46 которого соединен с выходом блока формирования цифровых сигналов 26, второй и третий сигналы первой группы входов 29 которого соединены с первым и вторым инверсными входами первого элемента И 174, выход которого соединен с информационным входом первого 152 формирователя одиночного импульса, выход которого соединен с первыми входами третьего 176 и четвертого 177 элементов И, четвертого 172 элемента ИЛИ и разрешающим входом первого 161 триггера, выход которого соединен с инверсным входом третьего 176 элемента И и вторым входом четвертого 177 элемента И, выход которого соединен с группой входов второй группы 181 элементов И, группа выходов которых соединена с информационной группой входов второго 159 регистра, группа выходов которого соединена с первой группой входов первого 182 мультиплексора, группа выходов которого соединена с первой группой входов второго 183 мультиплексора, группа выходов которого соединена с информационной группой входов третьего 160 регистра, группа выходов которого является второй группой выходов 44 блока формирования цифровых сигналов 26, первая группа 43 выходов которого соединена с выходами пятого 165 и шестого 166 триггеров, установочные входы которых соединены со сбросовыми входами первого 158, второго 159 и третьего 160 регистров, установочным входом второго 162 триггера, первыми входами первого 169, второго 170 и пятого 173 элементов ИЛИ, вторым входом четвертого 172 элемента ИЛИ, сбросовым входом сдвигового регистра 155 и является вторым сигналом второй 47 группы входов блока формирования цифровых сигналов 26, первый сигнал которой соединен с тактовыми входами первого 152, второго 153 и третьего 154 формирователей одиночного импульса, первого 161, второго 162, третьего 163, четвертого 164, пятого 165 и шестого 166 триггеров, первого 156 счетчика, третьего 160, второго 159 и первого 158 регистров, группа выходов которого соединена со второй группой входов первого 182 мультиплексора, прямой и инверсный входы которого соединены с выходом четвертого 164 триггера, инверсный выход которого соединен с информационным входом четвертого 164 триггера, разрешающий вход которого соединен с первым выходом второго 157 счетчика, второй выход которого соединен с первым входом шестого 179 элемента И, выход которого соединен с информационным входом третьего 154 формирователя одиночного импульса, выход которого соединен с первым входом третьего 171 элемента ИЛИ и разрешающим входом первого 156 счетчика, выход которого соединен с прямым и инверсным входами седьмого 167 триггера, выход которого соединен со вторым входом шестого 179 элемента И, третий вход которого соединен с выходом пятого 178 элемента И и разрешающим входом второго 157 счетчика, группа выходов которого соединена с группой входов дешифратора 184, группа выходов которого соединена с группой входов второго 183 мультиплексора, причем первый сигнал третьей 56 группы входов блока формирования цифровых сигналов 26 соединен с инверсным входом пятого 173 элемента ИЛИ и инверсным, информационным входом сдвигового регистра 155, информационным входом шестого 166 триггера и первым входом пятого 178 элемента И, второй сигнал третьей 56 группы входов блока формирования цифровых сигналов 26 соединен со вторыми входами пятого 178 элемента И и первого 169 элемента ИЛИ, инверсным, разрешающим входом второго 162 триггера, первым входом второго 175 элемента И, инверсным входом второго 170 элемента ИЛИ и информационным входом пятого 165 триггера, группа входов-выходов 12 блока формирования цифровых сигналов 26 соединена с группами входов второй группы 184 элементов И и первой группы 180 элементов И, группа выходов которой соединена с информационной группой входов первого 158 регистра, первый 42 вход блока формирования цифровых сигналов 26 соединен с тактовыми входами сдвигового регистра 155 и второго 157 счетчика, сбросовый вход которого соединен с выходом пятого 173 элемента ИЛИ, со сбросовым входами четвертого 164 триггера и третьего 154 формирователя одиночного импульса и входом константы 168, группа выходов которой соединена с группой установочных входов первого 156 счетчика, второй 48 вход блока формирования цифровых сигналов 26 соединен с инверсным информационным входом второго 162 триггера, выход которого соединен с третьим входом четвертого 172 элемента ИЛИ, выход которого соединен со сбросовым входом третьего 163 триггера, выход которого соединен со входом элемента НЕ 185, причем выход первого 169 элемента ИЛИ соединен со сбросовым входом первого 161 триггера, инверсный выход которого соединен с его информационным входом, выход второго 175 элемента И соединен с информационным входом второго 153 формирователя одиночного импульса, выход которого соединен со вторым входом третьего 171 элемента ИЛИ, выход которого соединен с информационным и разрешающим входами третьего 163 триггера, второй вход второго 175 элемента И соединен с выходом сдвигового регистра 155, выход второго 170 элемента ИЛИ соединен со сбросовыми входами первого 152 и второго 153 формирователей одиночного импульса, выход третьего 176 элемента И соединен с группой входов первой группы 180 элементов И.

Блок формирования телевизионных сигналов 27 состоит из первого 186 формирователя одиночного импульса, второго 187 формирователя одиночного импульса, первого 188 счетчика, второго 189 счетчика, третьего 190 счетчика, четвертого 191 счетчика, пятого 192 счетчика, шестого 193 счетчика, седьмого 194 счетчика, восьмого 195 счетчика, первого 196 регистра, второго 197 регистра, кодера 198, константы 199, первого 200 триггера, второго 201 триггера, третьего 202 триггера, четвертого 203 триггера, пятого 204 триггера, шестого 205 триггера, седьмого 206 триггера, восьмого 207 триггера, девятого 208 триггера, десятого 209 триггера, одиннадцатого 210 триггера, двенадцатого 211 триггера, тринадцатого 212 триггера, четырнадцатого 213 триггера, мультиплексора 214, первого 215 дешифратора, второго 216 дешифратора, третьего 217 дешифратора, четвертого 218 дешифратора. пятого 219 дешифратора, шестого 220 дешифратора, первого 221 элемента И, второго 222 элемента И. третьего 223 элемента И, четвертого 224 элемента И, пятого 225 элемента И, шестого 226 элемента И, седьмого 227 элемента И, восьмого 228 элемента И, девятого 229 элемента И, десятого 230 элемента И, одиннадцатого 231 элемента И, двенадцатого 232 элемента И, тринадцатого 233 элемента И, четырнадцатого 234 элемента И, пятнадцатого 235 элемента И, шестнадцатого 236 элемента И, семнадцатого 237 элемента И, первой группы 238 элементов И, второй группы 239 элементов И, первого 240 элемента ИЛИ, второго 241 элемента ИЛИ, третьего 242 элемента ИЛИ, четвертого 243 элемента ИЛИ, пятого 244 элемента ИЛИ, шестого 245 элемента ИЛИ, седьмого 246 элемента ИЛИ, восьмого 247 элемента ИЛИ, девятого 248 элемента ИЛИ, десятого 249 элемента ИЛИ, одиннадцатого 250 элемента ИЛИ, двенадцатого 251 элемента ИЛИ, тринадцатого 252 элемента ИЛИ, четырнадцатого 253 элемента ИЛИ, пятнадцатого 254 элемента ИЛИ, шестнадцатого 255 элемента ИЛИ, семнадцатого 256 элемента ИЛИ, восемнадцатого 257 элемента ИЛИ, девятнадцатого 258 элемента ИЛИ, двадцатого 259 элемента ИЛИ, двадцать первого 260 элемента ИЛИ, двадцать второго 261 элемента ИЛИ, двадцать третьего 262 элемента ИЛИ, двадцать четвертого 263 элемента ИЛИ, двадцать пятого 264 элемента ИЛИ, двадцать шестого 265 элемента ИЛИ, двадцать седьмого 266 элемента ИЛИ, двадцать восьмого 267 элемента ИЛИ, двадцать девятого 268 элемента ИЛИ, тридцатого 269 элемента ИЛИ, тридцать первого 270 элемента ИЛИ, выход тридцать первого 270 элемента ИЛИ соединен с разрешающим входом четырнадцатого 213 триггера и входом тридцатого 269 элемента ИЛИ, выход которого соединен со сбросовым входом тринадцатого 212 триггера, выход которого соединен с первыми входами шестого 226, восьмого 228, десятого 230 и тринадцатого 233 элементов И, выход тринадцатого 233 элемента И соединен с разрешающим входом шестого 205 триггера, выход которого соединен с прямым и инверсным входами мультиплексора 214, группа выходов которого является первой 54 группой выходов блока формирования телевизионных сигналов 27, первый 51 выход которого соединен с инверсным выходом двенадцатого 211 триггера, информационный и разрешающий входы которого соединены с выходом второго 187 формирователя одиночного импульса и разрешающим входом седьмого 194 счетчика, выход которого соединен с инверсным информационным входом седьмого 206 триггера и первым входом двадцать первого 260 элемента ИЛИ, выход которого соединен со сбросовым входом седьмого 206 триггера, выход которого соединен с первым входом девятого 229 элемента И, выход которого соединен с информационным входом второго 187 формирователя одиночного импульса, сбросовый вход которого соединен со сбросовыми входами шестого 193 счетчика и шестого 205 триггера, со входом константы 199 и выходом восемнадцатого 257 элемента ИЛИ, первый вход которого соединен с первыми входами четвертого 243, двадцать восьмого 267, двадцать девятого 268 элементов ИЛИ и выходом второго 201 триггера, информационный и инверсный, сбросовый входы которого соединены с выходом седьмого 227 элемента И, первый вход которого является первым сигналом группы выходов первого 215 дешифратора, второй сигнал которой соединен с инверсным, разрешающим входом первого 188 счетчика, со вторым входом первого 240 элемента ИЛИ и с информационным входом первого 200 триггера, выход которого соединен с разрешающим входом пятого 192 счетчика, группа выходов которого соединена с группой входов четвертого 218 дешифратора, первый сигнал группы выходов которого соединен с первым входом двадцать второго 261 элемента ИЛИ, второй сигнал группы выходов четвертого 218 дешифратора соединен со вторыми входами двадцать второго 261 элемента ИЛИ и седьмого 227 элемента И и входом четырнадцатого 234 элемента И, третий, четвертый, пятый, шестой и седьмой сигналы группы выходов соединены с первым, вторым, третьим, четвертым и пятым входами двадцать третьего 262 элемента ИЛИ соответственно, выход которого соединен с первым входом двадцать четвертого 263 элемента ИЛИ и информационным входом девятого 208 триггера, выход которого является вторым 52 выходом блока формирования телевизионных сигналов 27, третий 53 выход которого соединен с выходом четырнадцатого 213 триггера, информационный вход которого соединен с первым входом тридцать первого 270 элемента ИЛИ и является первым сигналом группы выходов шестого 220 дешифратора, второй сигнал группы выходов соединен со вторыми входами тридцать первого 270 элемента ИЛИ и двадцать девятого 268 элемента ИЛИ, выход которого соединен с инверсным входом тридцатого 269 элемента ИЛИ, с инверсным, информационным входом восьмого 195 счетчика, вторым входом двадцать шестого 265 элемента ИЛИ и с информационным входом тринадцатого 212 триггера, тактовый вход которого соединен с тактовыми входами первого 188, второго 189, третьего 190, четвертого 191, пятого 192, шестого 193, седьмого 194 счетчиков, с тактовыми входами первого 200, второго 201, третьего 202, четвертого 203, пятого 204, шестого 205, седьмого 206, восьмого 207, девятого 208, десятого 209, одиннадцатого 210, двенадцатого 211, тринадцатого 212, четырнадцатого 213 триггеров, с тактовыми входами первого 186 и второго 187 формирователей одиночного импульса, с тактовыми входами первого 196 и второго 197 регистров и является первым сигналом второй 47 группы входов блока формирования телевизионных сигналов 27, второй сигнал второй 47 группы входов соединен со сбросовыми сигналами первого 200 триггера, первого 196 и второго 197 регистров, четвертого 203, пятого 204, восьмого 207, девятого 208, десятого 209, одиннадцатого 210, четырнадцатого 213 триггеров, с первыми входами первого 240, второго 241, третьего 242, пятого 244, седьмого 246, восьмого 247 элементов ИЛИ и вторыми входами шестого 245, восемнадцатого 257, двадцать первого 260 элементов ИЛИ и двадцать восьмого 267 элемента ИЛИ, выход которого соединен со сбросовым входом двенадцатого 211 триггера, а третий вход двадцать восьмого 267 элемента ИЛИ соединен с первыми входами первой группы 238 элементов И и второй группы 239 элементов И, с разрешающим входом третьего 202 триггера и выходом первого 186 формирователя одиночного импульса, информационный вход которого соединен с выходом пятого 225 элемента И, первый и второй входы которого являются четвертым и вторым сигналами первой 29 группы входов блока формирования телевизионных сигналов 27, группа 12 входов-выходов которого соединена с группами входов первой 238 и второй 239 группами элементов И, группы выходов которых соединены с группами информационных входов первого 196 и второго 197 регистров соответственно, группы выходов которых соединены с первой группой входов и второй группой входов мультиплексора 214 соответственно, четвертый 55 выход блока формирования телевизионных сигналов 27 соединен с выходом десятого 209 триггера, информационный вход которого соединен с первыми входами девятнадцатого 258 и шестнадцатого 255 элементов ИЛИ и является первым сигналом группы выходов третьего 217 дешифратора, второй сигнал которой соединен с первыми входами девятого 248 и семнадцатого 256 элементов ИЛИ и вторыми входами восьмого 247 и девятнадцатого 258 элементов ИЛИ, третий сигнал которой соединен с первым входом двенадцатого 251 элемента ИЛИ, четвертый сигнал которой соединен со вторым входом двенадцатого 251 элемента ИЛИ, пятый сигнал которой соединен со вторым входом тринадцатого 252 элемента ИЛИ, шестой сигнал которой соединен с первыми входами четырнадцатого 253 элемента ИЛИ и двенадцатого 232 элемента И, седьмой сигнал которой соединен со вторым входом четырнадцатого 253 элемента ИЛИ, восьмой и девятый сигналы которой соединены с первым и вторым входами пятнадцатого 254 элемента ИЛИ соответственно, десятый сигнал которой соединен с первым входом шестнадцатого 255 элемента ИЛИ, одиннадцатый сигнал которой соединен со вторым входом тринадцатого 252 элемента ИЛИ, двенадцатый сигнал которой соединен со вторым входом семнадцатого 256 элемента ИЛИ, тринадцатый сигнал которой соединен со вторым входом девятого 248 элемента ИЛИ, выход которого соединен с первым входом двадцать седьмого 266 элемента ИЛИ и информационным входом одиннадцатого 210 триггера, выход которого соединен с инверсным входом семнадцатого 237 элемента И, выход которого соединен с первым входом двадцать пятого 264 элемента ИЛИ, выход которого соединен со вторым входом двадцать четвертого 263 элемента ИЛИ, выход которого соединен с разрешающим входом девятого 208 триггера, причем выход четвертого 191 счетчика соединен со своим инверсным разрешающим входом с первыми входами первого 221, второго 222, третьего 223, четвертого 224 и одиннадцатого 231 элементов И и со вторыми входами седьмого 246 элемента ИЛИ и двенадцатого 232 элемента И, выход которого соединен с инверсным разрешающим входом третьего 190 счетчика и первым входом шестого 245 элемента ИЛИ, выход которого соединен со сбросовым входом третьего 190 счетчика, группа выходов которого соединена с группой входов третьего 217 дешифратора, причем выход первого 221 элемента И соединен с первым входом кодера 198, первый сигнал группы выходов которого соединен с первым инверсным входом четырнадцатого 234 элемента И, с инверсным входом пятнадцатого 235 элемента И и с первыми входами шестнадцатого 236 элемента И и семнадцатого 237 элемента И, второй вход которого соединен с инверсным входом шестнадцатого 236 элемента И, с первым входом пятнадцатого 235 элемента И и вторым инверсным входом четырнадцатого 234 элемента И и является вторым сигналом группы выходов кодера 198, второй, третий и четвертый входы которого соединены соответственно с выходом четвертого 224 элемента И, с выходом второго 241 элемента ИЛИ и с выходом третьего 223 элемента И, второй вход которого соединен с выходом двенадцатого 251 элемента ИЛИ, второй вход первого 221 элемента И соединен с выходом тринадцатого 252 элемента ИЛИ и со вторыми входами двадцать седьмого 266 элемента ИЛИ и двадцать пятого 264 элемента ИЛИ, третий, четвертый, пятый входы которого соединены соответственно с выходом четырнадцатого 234 элемента И, с выходом пятнадцатого 235 элемента И и с выходом шестнадцатого 236 элемента И, второй вход которого соединен со вторым входом пятнадцатого 235 элемента И, с выходом двадцать второго 261 элемента ИЛИ и третьим входом семнадцатого 237 элемента И, выход и второй вход второго 222 элемента И соединены соответственно со вторым входом второго 241 элемента ИЛИ и выходом четырнадцатого 253 элемента ИЛИ, выход первого 240 элемента ИЛИ соединен со сбросовым входом первого 188 счетчика, группа выходов которого соединена с группой входов первого 215 дешифратора, второй вход четвертого 224 элемента И соединен с выходом семнадцатого 256 элемента ИЛИ, второй вход шестого 226 элемента И соединен с выходом четвертого 243 элемента ИЛИ, второй вход которого является первым сигналом группы выходов второго 216 дешифратора, второй, третий, четвертый и пятый сигналы которой соединены соответственно с информационным входом четвертого 203 триггера и первым входом десятого 249 элемента ИЛИ, вторым входом десятого 249 элемента ИЛИ, вторым входом восьмого 228 элемента И, первым входом одиннадцатого 250 элемента ИЛИ, выход которого соединен с разрешающим входом пятого 204 триггера, информационный вход и выход которого соединены соответственно с выходом восьмого 228 элемента И и вторым входом одиннадцатого 250 элемента ИЛИ, со вторым входом десятого 230 элемента И, выход которого соединен с разрешающим входом шестого 193 счетчика, группа выходов которого соединена с группой входов пятого 219 дешифратора, группа выходов которого соединена с группой входов мультиплексора 214, причем первый сигнал дополнительно соединен со вторым входом девятого 229 элемента И, а восьмой сигнал соединен со вторым входом тринадцатого 233 элемента И, выход шестого 226 элемента И соединен с инверсным, разрешающим входом второго 189 счетчика и вторым входом пятого 244 элемента ИЛИ, выход которого соединен со сбросовым входом второго 189 счетчика, группа выходов которого соединена с группой входов второго 216 дешифратора, выход третьего 242 элемента ИЛИ соединен со сбросовыми входами первого 186 формирователя одиночного импульса и третьего 202 триггера, прямой выход которого соединен с инверсным входом первой группы 238 элементов И и со вторым входом второй группы 239 элементов И, группа выходов которой соединена с группой информационных входов второго 197 регистра, второй вход третьего 242 элемента ИЛИ соединен с третьими входами девятого 229 и десятого 230 элементов И и выходом восьмого 207 триггера, информационный вход которого соединен с выходом одиннадцатого 231 элемента И и первым входом двадцатого 259 элемента ИЛИ, выход и второй вход которого соединены соответственно с разрешающим входом восьмого 207 триггера и выходом шестнадцатого 255 элемента ИЛИ, выходы седьмого 246 и восьмого 247 элементов ИЛИ соединены со сбросовыми входами четвертого 191 счетчика и пятого 192 счетчика, группа выходов которого соединена с группой входов четвертого 218 дешифратора, инверсный выход третьего 202 триггера соединен со своим информационным входом, выход десятого 249 элемента ИЛИ соединен с разрешающим входом четвертого 203 триггера, выход которого соединен с четвертым входом девятого 229 элемента И, группа выходов первой группы 238 элементов И соединена с группой информационных входов первого 196 регистра, выход пятнадцатого 254 элемента ИЛИ соединен со вторым входом одиннадцатого 231 элемента И, выход девятнадцатого 258 элемента ИЛИ соединен с разрешающим входом десятого 209 триггера, группа выходов константы 199 соединена с группой установочных входов седьмого 194 счетчика, инверсный выход шестого 205 триггера соединен со своим информационным входом, выход двадцать седьмого 266 элемента ИЛИ соединен с разрешающим входом одиннадцатого 210 триггера, первый вход 48 блока формирования телевизионных сигналов 27 соединен с четвертым входом двадцать восьмого 267 элемента ИЛИ, выход двадцать шестого 265 элемента ИЛИ соединен со сбросовым входом восьмого 195 счетчика, группа выходов которого соединена с группой входов шестого 220 дешифратора.

Блок прерываний 24 содержит первый 271 регистр, второй 272 регистр, первый 273 формирователь одиночного импульса, второй 274 формирователь одиночного импульса, третий 275 формирователь одиночного импульса, первый 276 триггер, второй 277 триггер, третий 278 триггер, четвертый 279 триггер, первый 280 элемент И, второй 281 элемент И, третий 282 элемент И, четвертый 283 элемент И, пятый 284 элемент И, шестой 285 элемент И, седьмой 286 элемент И, восьмой 287 элемент И, девятый 288 элемент И, десятый 289 элемент И, первый 290 элемент исключающего ИЛИ, второй 291 элемент исключающего ИЛИ, первый 292 элемент ИЛИ, второй 293 элемент ИЛИ, третий 294 элемент ИЛИ, четвертый 295 элемент ИЛИ, первый 296 элемент НЕ, второй 297 элемент НЕ, третий 298 элемент НЕ, четвертый 299 элемент НЕ, выходы которых являются первым, вторым, третьим, четвертым сигналами группы выходов 41 соответственно, входы первого 296, второго 297, третьего 298 и четвертого 299 элементов НЕ соединены с первым, вторым, третьим и четвертым выходами второго 272 регистра, первый, второй, третий и четвертый информационные входы соединены соответственно с выходами первого 292, второго 293, третьего 294, четвертого 295 элементов ИЛИ, первые входы которых соединены с выходами пятого 284, шестого 285, седьмого 286, восьмого 287 элементов И, первые и вторые входы которых соединены с группой выходов первого 271 регистра, группа информационных входов которого соединена с группой входов-выходов 12 блока прерываний 24, первый и второй сигналы первой 29 группы входов которого соединены с первым и вторым инверсными входами первого 280 элемента И, выход которого соединен с тактовым входом первого 271 регистра и информационным входом первого 273 формирователя одиночного импульса, выход которого соединен с третьими входами пятого 284, шестого 285, седьмого 286 и восьмого 287 элементов И, вторая 45 группа входов блока прерываний 24 соединена с инверсными, информационными входами первого 276 и второго 277 триггеров, выходы которых соединены соответственно с информационными и первыми входами третьего 278 триггера и первого 290 исключающего ИЛИ и четвертого 279 триггера и второго 291 исключающего ИЛИ, выходы которых соединены с первыми входами девятого 288 и десятого 289 элементов И соответственно, выходы которых соединены со вторым и третьим входами третьего 294 элемента ИЛИ, первый сигнал третьей 47 группы входов блока прерываний 24 соединен с тактовыми входами первого 273, второго 274, третьего 275 формирователей одиночного импульса, первого 276, второго 277, третьего 278 и четвертого 279 триггеров и второго 272 регистра, второй сигнал третьей 47 группы входов блока прерываний 24 соединен со сбросовыми входами первого 273, второго 274, третьего 275 формирователей одиночного импульса, первого 276, второго 277, третьего 278, четвертого 279 триггеров, первого 271 и второго 272 регистров, пятый сигнал четвертой 48 группы входов блока прерываний 24 соединен с первым входом второго 281 элемента И, шестой сигнал четвертой 48 группы входов блока прерываний 24 соединен с первым входом третьего 282 элемента И, седьмой сигнал четвертой 48 группы входов блока прерываний 24 соединен со вторыми входами девятого 288 и десятого 289 элементов И, восьмой сигнал четвертой 48 группы входов блока прерываний 24 соединен с первым входом четвертого 283 элемента И, выход которого соединен со вторым входом четвертого 295 элемента ИЛИ, первый сигнал пятой 49 группы входов блока прерываний 24 соединен с входом первого 280 элемента И, причем первый вход 31 блока прерываний 24 соединен со вторым входом второго 281 элемента И, выход которого соединен с информационным входом второго 274 формирователя одиночного импульса, выход которого соединен со вторым входом первого 292 элемента ИЛИ, второй 40 вход блока прерываний 24 соединен со вторым входом четвертого 283 элемента И, третий 55 вход блока прерываний 24 соединен со вторым входом третьего 282 элемента И, выход которого соединен с информационным входом третьего 275 формирователя одиночного импульса, выход которого соединен со вторым входом второго 293 элемента ИЛИ.

Блок управления 25 содержит первый 300 регистр, второй 301 регистр, счетчик 302, мультиплексор 303, дешифратор 304, первый 305 элемент ИЛИ, второй 306 элемент ИЛИ, элемент И-НЕ 307, выход которого соединен с первым входом мультиплексора 303, группа выходов которого соединена с группой входов-выходов 12 блока управления 25 и с информационными группами входов первого 300 и второго 301 регистров, группы входов которых соединены соответственно с первой и второй группами входов мультиплексора 303 и являются второй 48 и первой 38 группами выходов блока управления 25, выход 42 которого соединен с выходом счетчика 302, тактовый вход которого является первым сигналом пятой 47 группы входов блока управления 25, второй сигнал которой соединен со сбросовыми входами счетчика 302, первого 300 и второго 301 регистров, тактовые входы которых соединены между собой и являются пятым сигналом первой 29 группы входов, шестой сигнал которой соединен с входом дешифратора 304 и первым инверсным входом первого 305 элемента ИЛИ, первый сигнал которой соединен с первым инверсным входом второго 306 элемента ИЛИ, седьмой и восьмой сигналы которой соединены соответственно со вторыми входами первого 305 и второго 306 элементов ИЛИ, выходы которых соединены соответственно с первым и вторым входами элемента И-НЕ 307, вторая 39 группа входов блока управления 25 соединена с третьей группой входов мультиплексора 303, четвертая группа входов которого является третьей 41 группой входов блока управления 25, четвертая 45 группа входов которого соединена с первым, вторым, третьим инверсными входами мультиплексора 303, пятая группа входов которого соединена с группой выходов дешифратора 304, первый и пятый сигналы которой еще соединены с разрешающими входами первого 300 и второго 301 регистров соответственно, группа входов дешифратора 304 является шестой 49 группой входов блока управления 25.

Блок управления с клавиатуры 22 содержит первый 308, второй 309, третий 310, четвертый 311, пятый 312, шестой 313 узлы устранения дребезга, регистр 314, счетчик 315, формирователь одиночного импульса 316 и элемент ИЛИ 317, выход которого соединен с информационными входами счетчика 315 и формирователя одиночного импульса 316, выход которого является выходом 40 блока управления с клавиатуры 22, группа выходов 39 которого соединена с группой выходов регистра 314, а первые шесть сигналов которой дополнительно соединены с шестью входами элемента ИЛИ 317, первый сигнал первой 47 группы входов блока управления с клавиатуры 22 соединен с тактовыми входами счетчика 315, первого 308, второго 309, третьего 310, четвертого 311, пятого 312, шестого 313 узлов устранения дребезга, второй сигнал первой 47 группы входов соединен со сбросовыми входами первого 308, второго 309, третьего 310, четвертого 311, пятого 312, шестого 313 узлов устранения дребезга, счетчика 315, регистра 314, группа информационных входов которого соединена с выходами первого 308, второго 309, третьего 310, четвертого 311, пятого 312, шестого 313 узлов устранения дребезга, входы которых являются второй 57 группой входов блока управления с клавиатуры 22, причем выход счетчика 315 соединен с тактовым входом регистра 314.

Блок формирования одиночного импульса содержит первый 318 и второй 319 триггеры и элемент И 320, выход которого является выходом формирователя одиночного импульса, информационный вход которого соединен с информационным и разрешающим входами первого 318 триггера, выход которого соединен с информационным и разрешающим входами второго 319 триггера и первым входом первого элемента И 320, второй вход которого соединен с инверсным выходом второго 319 триггера, тактовый вход которого соединен с тактовым входом первого 318 триггера и является тактовым входом формирователя одиночного импульса, сбросовый вход которого соединен со сбросовыми входами первого 318 и второго 319 триггеров.

Узел устранения дребезга содержит первый 321 счетчик, второй 322 счетчик, первый 323 триггер, второй 324 триггер, первый 325 элемент ИЛИ-НЕ, второй 326 элемент ИЛИ-НЕ, элемент ИЛИ 327, элемент И 328, элемент И-НЕ 329, выход которого соединен со сбросовым входом второго 322 счетчика, выход которого соединен с информационным и инверсным сбросовым входами второго 324 триггера, выход которого соединен с первым входом элемента ИЛИ 327, выход которого соединен со сбросовым входом первого 321 счетчика, выход которого соединен с информационным и инверсным сбросовым входами первого 323 триггера, выход которого соединен с первыми входами первого 325 и второго 326 элементов ИЛИ-НЕ, элемента И 328, элемента И-НЕ 329 и является выходом узла устранения дребезга, вход которого соединен со вторыми входами первого элемента ИЛИ-НЕ 325 и элемента И 328, выход которого соединен со вторым входом элемента И-НЕ 329 и разрешающим входом второго 322 счетчика, тактовый вход которого соединен с тактовыми входами первого 321 счетчика, первого 323 и второго 324 триггеров и является тактовым входом узла устранения дребезга, сбросовый вход которого соединен со вторым входом элемента ИЛИ 327, третий вход которого соединен с выходом второго 326 элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого 325 элемента ИЛИ-НЕ и разрешающим входом первого счетчика.

Тепловизор работает следующим образом.

Блок управления МФП 20 после синхронизации по кадрам между матрицей 2 и телевизором (ТВ) 7 (каждый полукадр 50 Гц) формирует в соответствии с алгоритмом формирования управляющих импульсов, представленном на фиг.12 и 13, группу 31 управляющих импульсов, поступающих на матрицу 2 МФП для синхронной работы регистров и секций накопления кремниевой интегральной схемы считывания и создания оптимального режима работы фотодиодной матрицы. Причем вторая группа выходов 31 блока управления МФП 20 состоит из:

первый сигнал - f1d;

второй сигнал - f3d;

третий сигнал - f3g;

четвертый сигнал - f1g;

пятый сигнал - kg1;

шестой сигнал - kg2;

седьмой сигнал - kd.

Прием и усиление фотосигналов до уровня, необходимого для последующего аналого-цифрового преобразования. Для привязки к началу кадра используется сигнал внешнего прерывания IRQ0 41, который формируется в блоке прерываний 24 на элементах И 281, И 284, формирователе одиночного импульса 274, элементе ИЛИ 292, регистре 287 и элементе НЕ 296, если данное прерывание разрешено (4 разряд регистра управления находится в 1). С некоторой задержкой из МФП 2 начинает поступать информация 18, 36 на соответствующие АЦП 5 и АЦП 19. Далее информация с помощью АЦП преобразуется в цифровой 14-разрядный двоичный код, при этом преобразование обеспечивается без потерь динамического диапазона и отношения сигнал/шум.

Из блока управления МФП 20 поступают два сигнала 33 и 34: по первому сигналу стробируется прием данных в АЦП, по второму в блоке формирования данных 21 на триггерах 119, 122 и элементах И 128, И 130 формируется сигнал, обеспечивающий прием данных 32 с АЦП 5 и данных 35 с АЦП 19 с помощью групп элементов И 135 и групп элементов И 136 в буферный регистр 150, по следующему синхроимпульсу, данные из АЦП запишутся в регистр 151, затем формируется запрос на прямой доступ 98 на триггере 123, поступающий на блок цифровой обработки, а в частности на центральный процессор (1892 ВМ5). [3]

Данные из МФП вводятся в систему обработки строками.

Архитектура центрального процессора 1892 ВМ5 специально адаптирована для поддержания, параллельно с обработкой, прием интенсивных потоков данных 1892 В5 имеет мощный встроенный программируемый контроллер порта внешней памяти и многоканальный DMA-процессор.

ЦП позволяет подключать и программировать различные типы внешней памяти, настраивать их объем и расположение в адресном пространстве, циклы ожидания, разрядность данных (от 8 до 64 бит). Ширина адресной шины - 32 бита. Непосредственный ввод данных во внешнюю память обеспечивается режимом «Flyby», управляющим обменами с внешними устройствами.

DMA - каналы (каналы прямого доступа) могут работать поочередно или одновременно, запускаться программно или аппаратно (от DMA либо от ЦП), поддерживают разнообразные режимы адресации (двумерную, двоично-инверсную).

Получив запрос на прямой доступ центральный процессор 9 принимает данные во внутреннюю память 10, формируя сигналы разрешения на прямой доступ (flyby) и выборку (NCSI00), первый и второй сигналы соответственно первой группы управляющих выходов 29 блока цифровой обработки, по которым в блоке формирования данных 21 разрешается выдача 64 разрядного слова (элементы И 134 и мультиплексор 149) и выполняется сброс запроса на прямой доступ 28 (триггер 123), формируемый на элементе ИЛИ 147, формирователе одиночного импульса 142 и элементе ИЛИ 143. Затем вычитается "1" из счетчика количества обменов по прямому доступу 118 и снова устанавливается в "1" запрос на прямой доступ (триггер 123), и так происходит, пока ЦП не передаст 64 слова (256 точек), затем по переполнению счетчика 118 триггер 120 устанавливается в "0", блокируя прием данных с АЦП. По 245 импульсу со счетчика строк для матрицы 103 блока управления МФП 20 устанавливается в "1" триггер 101, снова разрешая формирование синхроимпульсов для следующей строки. В ЦП канал прямого доступа ДМА0 отсчитывает по 64 слова, загружает их во внутреннюю память ЦП и перезапускается для ввода следующей строки.

Загрузка выполняется в двухбуферном режиме с тем, чтобы совмещать обработку и пересылки данных. Параллельно с DMA0 работают каналы DMA1, DMA2 и DMA3. Последний построчно загружает из ОЗУ в память ЦП таблицы, необходимые для выполнения обработки, канал DMA2 (с задержкой на 5-10 строк) выгружает обработанные строки из памяти ЦП в блок формирования цифровых сигналов. Оба канала также работают в двухбуферном режиме.

По сигналам "целеуказания" или "захвата и слежения" 45, поступающим из блока вторичной обработки, в блоке прерываний 24 по переднему фронту и по заднему фронту формируется сигнал прерывания IRQ2 41 (на элементах триггера 276…279, элементы исключающего ИЛИ 290, 291, элементы И 288, И 289 и ИЛИ 294, регистр 272, элемент НЕ 298), если оно не замаскировано, т.е. 15р регистра управления равен "1" (седьмой сигнал группы входов 48).

По первому сигналу (кадровая синхронизация) группы управляющих выходов 31, блока управления МФП 20 в блоке прерываний 24 на элементе И 281, формирователе одиночного импульса 274, элементе ИЛИ 292 формируется сигнал прерывания IRQ0 первый сигнал группы выходов 41, поступающий на ЦП, если он разрешен (пятый сигнал четвертой группы входов 48 равен "1").

ЦП прерывается и в случае готовности данных для вывода на цифровой видеосигнал инициирует прямой доступ по каналу Memch2.

Из блока управления МФП 20 по задержанному сигналу кадровой сигнализации на триггере 97 формируется сигнал 56, по которому в блоке формирования цифрового сигнала 26 на задержке 155, элементе И 175, формирователе одиночного импульса 153, элементе ИЛИ 171, триггере 163 и элементе НЕ 185 формируется сигнал 46 запроса на прямой доступ nDMAR2. ЦП в режиме FLYBY обеспечивает передачу из внешней памяти 10 в блок формирования цифровых сигналов 26 данных, сопровождая их сигналами nFLYBY и nCSIO2 (второй и третий сигналы первой группы управляющих выходов 29 из ЦП 9), по которым в блоке формирования цифровых сигналов 26 на элементе И 174, формирователе одиночного импульса 152, элементе И 176 и группе элементов И 180 обеспечивается прием данных на регистр 1 158 и сброс триггера запроса на прямой доступ 163.

По первому импульсу DCLK 42, синхронизирующему выдачу данных на цифровой выход видеосигнала 44 поступит младший байт с регистра 1 158 в зависимости от состояния счетчика 157, дешифратора 184, мультиплексора 183 и регистра 160. По второму и последующим 6 импульсам DCLK 42 состояние счетчика 157 меняется и происходит передача байтов в порядке их возрастания в блок вторичной обработки. Во время передачи первого слова по второму сигналу (строчная синхронизация) группы входов 56 формируется одиночный импульс на элементах И 178, И 179 и формирователе одиночного импульса 154 и устанавливается следующий сигнал запрос на прямой доступ (триггер 163). За время передачи первого слова из ЦП передается второе слово и поступает на регистр 2 159. После передачи каждого слова (1-го и всех последующих слов) в блоке формирования цифровых сигналов 26 счетчик 156 вычитает единицу. Обмен данными продолжается до тех пор, пока содержимое счетчика 156 не будет равно нулю, после передачи 32 слов в счетчик 156 производится запись константы "31", формируемой константой 169. Сигналы кадровой и строчной синхронизации формируются на триггерах 165, 166 соответственно и передаются как группа выходных сигналов 43 в блок вторичной обработки.

Блок формирования телевизионных сигналов обеспечивает формирование сигналов синхросмеси 52 по ГОСТ 7845-92, данных 54 и синхроимпульса 53, сопровождающего данные. Для формирования этих сигналов необходимы три счетчика: счетчик полустрок 190, счетчик импульсов в полустроке 191 и счетчик импульсов в строке 192.

Частота кадров ввода составляет 50 Гц, а вывода - 25 Гц.

Выдаваемый кадр должен учитывать чресстрочную развертку. Выдаваться должны сначала нечетные строки (1, 3, 5…511 - первое поле), а затем - четные (2, 4, 6…512 - второе поле). Так как обработка входных кадров происходит на частоте 50 Гц, то каждому полю вывода на ТВ должен соответствовать новый кадр ввода. При этом происходит масштабирование на 2 по вертикали (входной кадр имеет 256×256 элементов изображения). Масштабирование по горизонтали происходит аппаратно за счет выбора тактовой частоты (6 МГц) в 2 раза ниже разрешающей способности по горизонтали.

По тысяча двести одиннадцатому импульсу со счетчика полустрок 190 устанавливается в "1" триггер 209 и формируется сигнал прерывания 55 RQ 1, по которому в блоке прерываний 24, если это прерывание разрешено (5 р регистра управления находится в "1", шестой сигнал четвертой группы входов 48), на элементе И 282, формирователе одиночного импульса 275, элементе ИЛИ 293, регистре 272, элементе НЕ 297 формируется сигнал прерывания IRQ1 (второй сигнал группы выходов 41 блока прерываний 24), по которому в ЦП 9 обеспечивается привязка к началу кадров телевизора, инициализируется прямой доступ по каналу MemCh1. Одновременно выполняется блокировка выдачи данных на время кадровой синхронизации.

По 73 импульсу на счетчике полустрок 190 устанавливается в "1" триггер 207, разрешающий установку триггера 258 (nDMAR1 запрос на прямой доступ по выводу данных на ТВ). При нулевом состоянии счетчика обменов DMA 194 и счетчика, управляющего передачей данных 193, срабатывает элемент И 229 и формирователь одиночного импульса 187 и устанавливает триггер 211 в "1", если прямой доступ разрешен, т.е. 8 разряд регистра управления находится в "1".

ЦП 9 в режиме FLYBY обеспечивает передачу данных из внешней памяти 10 в блок формирования телевизионных сигналов 27. При передаче данных в режиме FLYBY ЦП 9 отключается от шины данных 12 и активизирует внешнюю память 10 и блок формирования телевизионных сигналов 27 одновременно. По сигналам nFLYBY и nCSIO1 (второй и четвертый сигналы первой группы выходов 31 ЦП) через элемент И 225, формирователь одиночного импульса 186 и элемент И 238 обеспечивается прием данных на регистр 196 данных 1 и выполняется сброс триггера 211 запроса на прямой доступ, одновременно устанавливается в "1" триггер 202. По нулевому состоянию счетчика 193, управляющего передачей данных, снова устанавливается в "1" триггер 211 запроса на прямой доступ и вычитается "1" из счетчика обменов DMA 194. Прием следующего слова данных осуществляется на регистр 197 данных 2 через элементы И 225, формирователь одиночного импульса 186 и элемент И 239. Таким образом, обмен данными продолжается до тех пор, пока содержимое счетчика 194 обменов DMA не будет равно "0".

Триггер 206 устанавливается в "0", блокируя продолжение обменов с ЦП 9, после 511 импульса со счетчика импульсов в строке 192 устанавливается в "1" триггер 201, по которому в счетчик обменов DMA 194 заносится константа "32" (константа 199). Управление работой тепловизора со стороны ЦП обеспечивается программируемыми регистрами.

Физические адреса внутренних регистров тепловизора указаны в таблице.

Все регистры 32-разрядные.

Назначение разрядов регистра управления 300 блока управления 25:

5,4 р. - "1" - разрешение прерывания IRQ1 и IRQ0 соответственно или "0" - их блокировка (программный сброс каждого прерывания осуществляется в регистре прерываний QR;

6 р. - "0" - блокировка синхросмеси на ТВ;

7 р. - разрешение формирования запроса прямого доступа nDMAR0 по вводу из АЦП в ЦП (необходимо установить в "1" после программирования прямого доступа и сбросить в "0" по окончании обмена);

8 р. - разрешение формирования запроса прямого доступа в nDMAR1 по выводу на ТВ из ЦП (необходимо установить в "1" после программирования прямого доступа и сбросить в "0" по окончании обмена);

9 р. - режим калибровки (выход);

10 р. - тепловизионная камера исправна (выход);

11 р. - триггер целеуказания (вход), при смене полярности вызывает прерывание IRQ2 и доступен по опросу;

12 р. - триггер захвата и слежения (вход), при смене полярности вызывает прерывание IRQ2 и доступен по опросу;

13 р. - триггер блокировки калибровки (вход), доступен по опросу;

14 р. - GOTOVT (вход), доступен по опросу;

16,15 р. - "1" - разрешение прерываний IRQ3 и IRQ2 соответственно или "0" - их блокировка (программный сброс каждого прерывания осуществляется в регистре прерываний QR);

17 р. - разрешение формирования запроса прямого доступа nDMAR2 по цифровому выводу (необходимо установить в "1" после программирования прямого доступа и сбросить в "0" по окончании обмена);

18 р. - кадровый синхроимпульс по цифровому выводу (резерв);

20 р. - расфокусировка (выход);

21 р. - остановка МКС (выход);

22 р. - дежурный режим МКС (выход);

31…24 р. - уровень белого в тестовом режиме (0…255);

Назначение разрядов регистра прерывания 271 блока прерываний 24:

3…0 р. - разряды прерываний IRQ3, IRQ2, IRQ1 и IRQ0 соответственно;

19…16 р. - разряды маски записи в соответствующие разряды прерываний.

Назначение разрядов регистра задержек 301 блока управления 25:

По reset имеет значение = 0×BF17;

4…0 р. - разряды задержки тактовой частоты АЦП. Полутакт F1D разбит на 12 дискретов тактовой частоты 24 МГц. Аккумулирование происходит по 4 дискретам:

0×В - 1, 2, 3, 4

0×D - 2, 3, 4, 5

0×F - 3, 4, 5, 6

0×11 - 4, 5, 6, 7

0×13 - 5, 6, 7, 8

0×15 - 6, 7, 8, 9

0×17 - 7, 8, 9, 10

0×19 - 8, 9, 10, 11

0×3 - 9, 10, 11, 12

0×5 - 10, 11, 12, 1

0×7 - 11, 12, 1, 2

0×9 - 12, 1, 2, 3

15…8 p. - разряды длительности сигналов KD, KG1, KG2 (0×7F - 64 мкс,

0×CF - 24 мкс, (KD=0×FF-(0×CF)=48F1D ~ 24 мкс));

Назначение разрядов регистра клавиатуры 314 блока управления с клавиатуры 22:

По reset имеет значение = 0×00;

5…0 р. - код клавиш;

0×1 - холодная калибровка;

0×2 - горячая калибровка;

0×4 - увеличение яркости;

0×8 - уменьшение яркости;

0×10 - увеличение контрастности;

0×20 - уменьшение контрастности.

Назначение разрядов регистра переполнения АЦП:

По reset имеет значение = 0×00;

16 р. - переполнение первого АЦП;

17 р. - переполнение второго АЦП;

Триггеры переполнения АЦП устанавливаются в ′1′, если в любом месте кадра было переполнение АЦП. Триггеры сбрасываются в ′0′ по кадровому импульсу.

Блок управления с клавиатуры 22 предназначен для управления режимами работы.

Число управляющих команд технологического пульта не более 8, в т.ч.:

- сброс;

- калибровка по уровню фоновых сигналов элементов МФП;

- поиск, запись в память дефектных элементов и замена их сигналов по алгоритму деселекции;

- увеличение контраста;

- уменьшение контраста;

- стоп-кадр.

По нажатию любой кнопки (с 0 по 5) формируется сигнал 40, поступающий в блок прерываний 24 для формирования прерывания IRQ3 41, если он разрешен, т.е. 16 р регистра управления 300 (CR) равен "1", ЦП 9 прерывается, считывает регистр клавиатуры KB 314 и приступает к выполнению заданного режима, одновременно записывая нуль (сброс команды с пульта) в те разряды, которые находились в единицах. При отжатии клавиши через 0,1 с соответствующий разряд в регистре клавиатуры 314 установится в "0".

Блок цифровой оперативной обработки данных тепловизора, состоящий из центрального процессора 1892ВМ5 с тактовой частотой 80 МГц, ОЗУ и ПЗУ обеспечивает надежную и высокопроизводительную обработку сигналов и изображений в реальном времени и одновременную поддержку интенсивных входных и выходных потоков данных.

На центральный процессор возлагаются следующие задачи:

1. Обслуживание потоков входных данных от МФП и выходных данных на телевизор и блок вторичной обработки;

2. Цифровая обработка данных МФП в реальном времени;

3. Периодическая калибровка МФП для вычисления коэффициентов, используемых в цифровой обработке.

Причем цифровая обработка должна происходить в реальном времени, на фоне работающих входных и выходных потоков.

Основными сложностями в цифровой обработке тепловизионных изображений являются значительная неравномерность чувствительности по каждому кадру, высокий уровень и нестабильность пьедестала, большой динамический диапазон (74 дБ), а также существенные требования к задержке обработки (5-10 строк входного кадра). Обработка должна происходить без пропусков кадров.

В блоке цифровой обработки обслуживаются следующие потоки данных:

1. Поток входных данных с МФП;

2. Поток выходных данных из тепловизора в телевизор;

3. Поток выходных данных из тепловизора в блок вторичный обработки.

Каждый из трех потоков имеет собственную синхронизацию и обслуживается отдельным каналом прямого доступа к памяти (Direct Memory Access, DMA).

С МФП поступают тепловизионные кадры размером 256×256 точек с частотой 50 Гц. Разрядность яркости каждой точки - 14 бит, яркость передается 16-разрядным кодом. Интенсивность входного потока от МФП равна 6,25 Мб/с.

Обработанные данные выводятся на телевизор кадрами размера 512×512 точек, с чересстрочной разверткой, частотой вывода полукадров в 50 Гц, разрядностью 1 б на каждую точку.

Кроме того, обработанные данные также выводятся на блок вторичной обработки кадрами размера 256×256 точек, с частотой вывода 50 Гц, разрядностью 1 б на каждую точку.

ОПИСАНИЕ АЛГОРИТМА ЭЛЕКТРОННОЙ ОБРАБОТКИ ВИДЕОСИГНАЛА

Обработка тепловизионных данных происходит в ядре центрального процессора 1892 ВМ5.

Для этого по каналу DMA3 во внутреннюю память ЦП построчно вводятся тепловизионные данные и необходимые для обработки коэффициенты (см. ниже). Обработка включает в себя:

1) улучшение качества тепловизионного изображения;

2) приведение к нужному формату и динамическому диапазону потребителей тепловизионных данных;

3) формирование и организация выходных потоков.

Дополнительной особенностью центрального процессора 1892 ВМ5 является наличие режима SIMD («single instruction, multiple data», «один поток инструкций, множественные потоки данных»). Данный режим позволяет выполнять один и тот же блок линейных арифметических операций параллельно над несколькими блоками данных. В 1892 ВМ5 существует 2 секции SIMD, таким образом, есть возможность ускорить линейные участки обработки в два раза. В случае если обработка происходит нелинейно (есть операции условных переходов и ветвлений), используется стандартный режим SISD («single instruction, single data», «один поток инструкций, один поток данных»).

Рассмотрим все процедуры последовательной обработки каждой строки кадра.

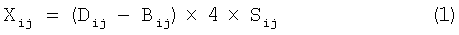

А. Нормализация

Ввиду неоднородной чувствительности датчиков МФП, а также высокого уровня постоянной составляющей, входные данные подвергаются нормализации (1)

где i, j - координаты обрабатываемой точки, D - матрица входного кадра, В - матрица постоянных составляющих, вычисленных для каждого датчика на этапе калибровки, S - матрица чувствительностей, также вычисленных на этапе калибровки.

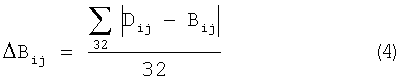

Б. Коррекция бракованных точек

На данном этапе производится коррекция нормализованного кадра Х в соответствии с таблицей коррекции С, построенной на этапе калибровки. В зависимости от содержимого таблицы коррекции, значение забракованной точки заменяется. В качестве замены берется либо полусумма двух соседних не бракованных точек, занимающих относительно данной симметричное положение, либо значение ближайшей не бракованной точки, если пары соседних точек тоже бракованы.

В. Приведение кадра к диапазону [-4096; 4095]

Поскольку уровни постоянной составляющей датчиков МФП изменяются (колеблются) во времени, в результате нормализации кадра матрица Х вполне может содержать отрицательные значения, поэтому необходимо вычислить минимальное значение по кадру, вычесть его из каждого элемента матрицы X, а затем ограничить элементы Х сверху значением 4095 (2).

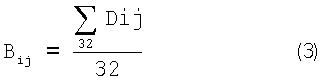

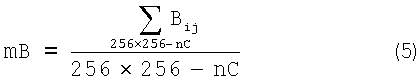

Г. Обновление гистограммы кадра

При обработке каждого кадра постоянно строится его гистограмма Hz, используемая в дальнейшем для построения таблицы преобразования Т. Гистограмма Hz дает частоту появления значений яркости в диапазоне [-4096; 4095] в текущем кадре, гисторамма обновляется по каждой обрабатываемой строке кадра.

КУСОЧНО-ЛИНЕЙНОЕ КОНТРАСТИРОВАНИЕ

В методе кусочно-линейного контрастирования параметры переходной характеристики к выходному диапазону вычисляются в зависимости от динамических характеристик изображения. Ручная регулировка контрастности не предусматривается.

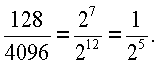

Суть метода заключается в том, чтобы сохранить при переквантовании контрастность в области относительной интенсивности, близкой к нулю, за счет некоторого сокращения квантов, выделенных для кодирования интенсивностей вне этой области. При этом контрастирование в этой области всегда будет осуществляться по коэффициентам, кратным отношению входного и выходного диапазонов. Поскольку гистограмма строится в диапазоне [0; 4095] по модулю (отдельно для положительной и отрицательной части), то коэффициент и для положительной, и для отрицательной области, близкой к нулю, всегда будет кратен

Регулировка параметров осуществляется в два этапа. На первом этапе осуществляется построение гистограммы и вычисление значений ее границ Gmin и Gmax. Границы Gmin и Gmax определяются как точки гистограммы, для которых сумма ее значений слева и справа соответственно превышает установленное пользователем значение Р.

Определение контрастирования в положительном и отрицательном диапазонах относительной интенсивности происходит отдельно, одним и тем же способом.

Рассмотрим построение отрезков контрастирования для положительной области. В первую очередь значение Gmax представляется в виде формулы:

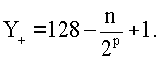

Gmax=128·2^p+n, где р≥0, n<=128·2^p

Затем определяется значение Y+, т.е количество точек в выходном диапазоне от нуля, в которых возможно осуществление переквантования исходных значений в окрестности нуля с коэффициентом k+=2-p. Значение Y+ вычисляется по формуле:

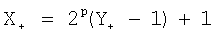

Соответствующая точка во входном диапазоне Х+ определяется по формуле:

.

.

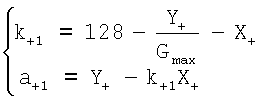

Тогда параметры прямой, образующей второй отрезок контрастирования положительной области, определяются следующей системой:

В результате проведения аналогичных операций для отрицательной части преобразуемого диапазона определяется кусочно-линейная функция из четырех отрезков, по которой и будет осуществляться контрастирование (см. фиг.14).

Результирующая функция контрастирования описывается системой: