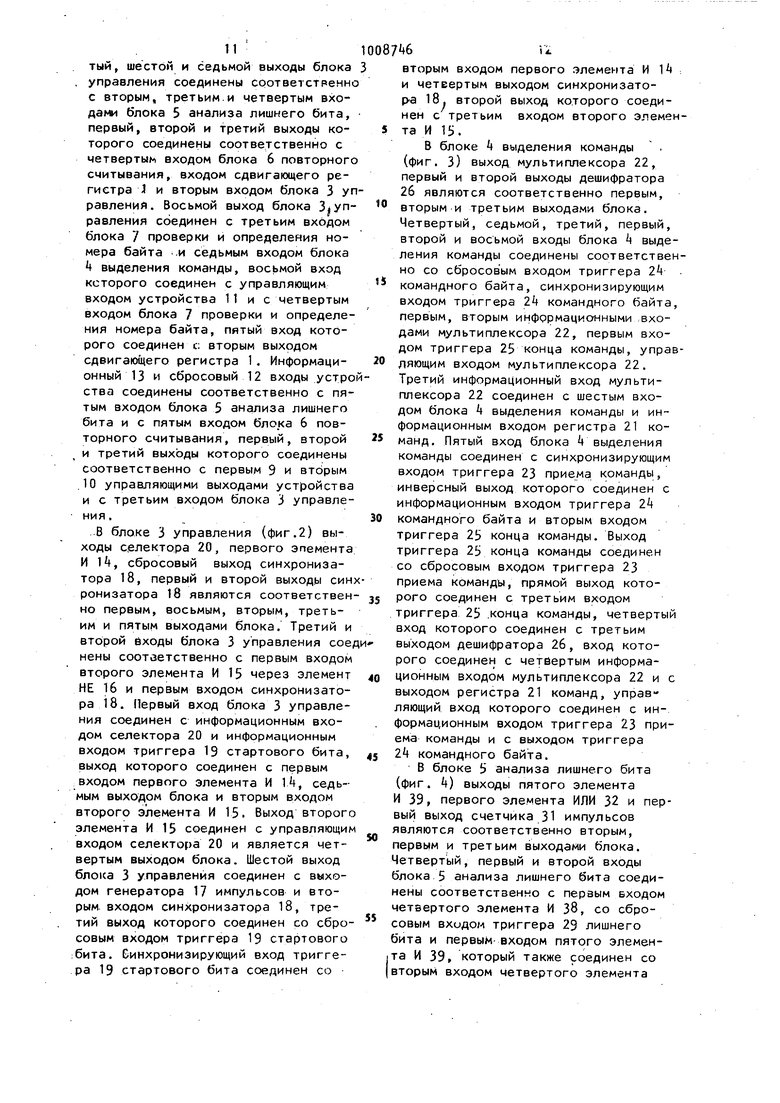

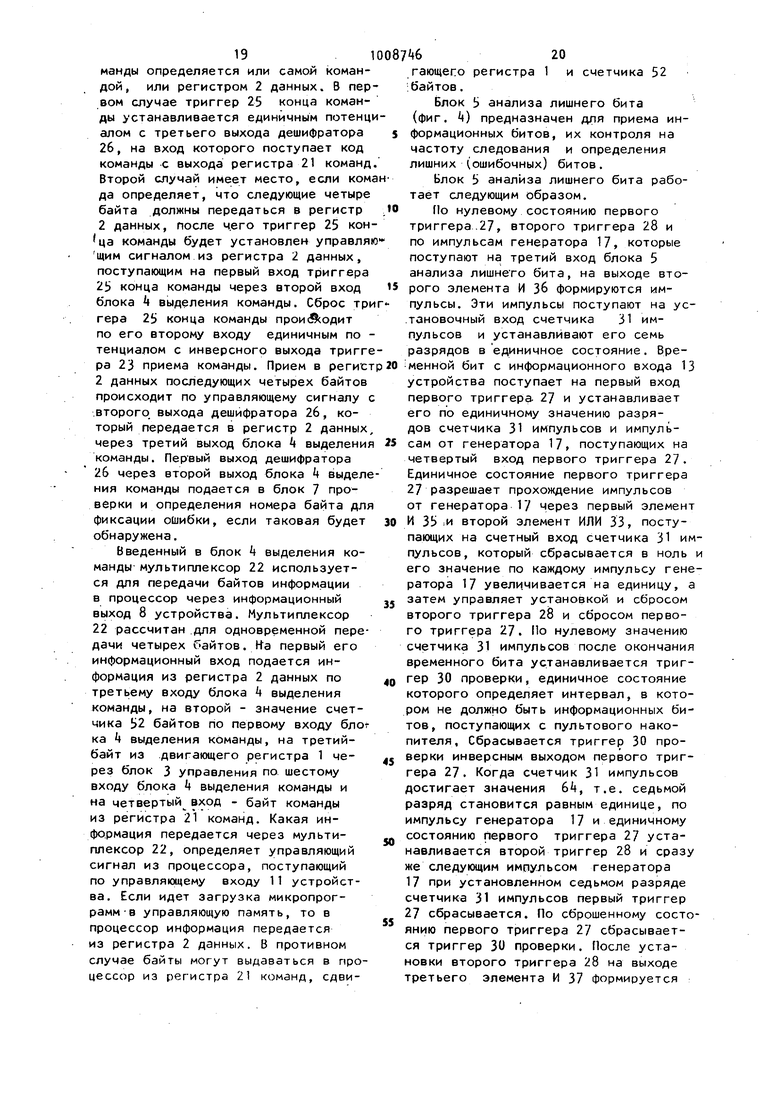

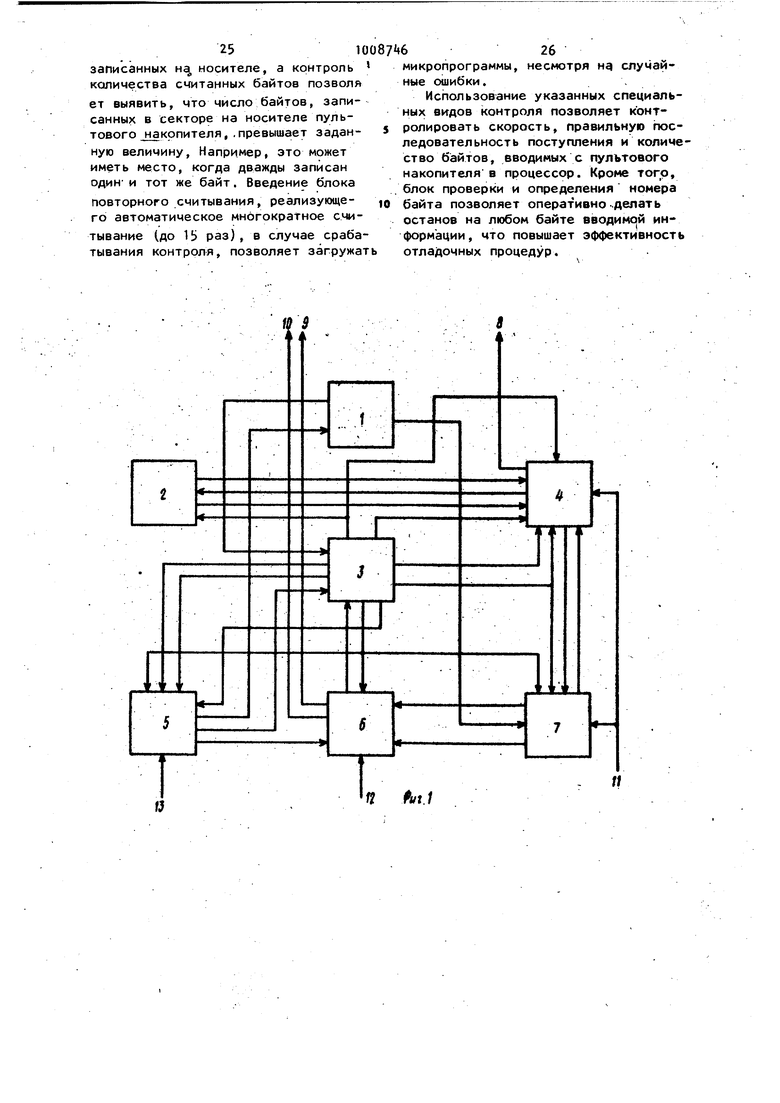

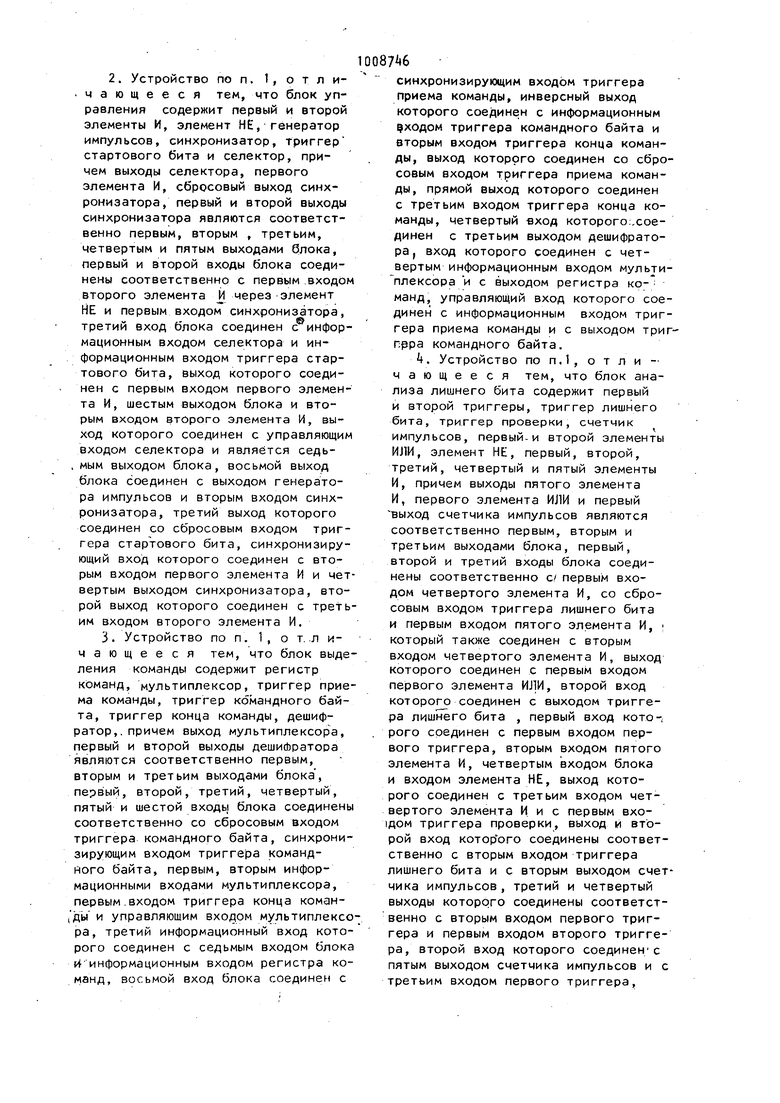

2. Устройство по п. 1, о т л и.чающееся тем, что блок управления содержит первый и второй элементы И, элемент НЕ, генератор импульсов, синхронизатор, триггер стартового бита и селектор, причем выходы селектора, первого элемента И, сбросовый выход синхронизатора, первый и второй выходы синхронизатора являются соответственно первым, вторым , третьим, четвертым и пятым выходами блока, первый и второй входы блока соединены соответственно с первым .входом второго элемента через элемент НЕ и первым входом синхронизатора, третий вход блока соединен с информационным входом селектора и информационным входом триггера стартового бита, выход которого соединен с первым входом первого элемента И, шестым выходом блока и вторым входом второго элемента И, выход которого соединен с управляющим входом селектора и является седь, мым выходом блока, восьмой выход блока соединен с выходом генератора импульсов и вторым входом синхронизатора, третий выход которого соединен со сбросовым входом триггера стартового бита, синхронизирующий вход которого соединен с вторым входом первого элемента И и четвертым выходом синхронизатора, второй выход которого соединен с Tpetbим входом второго элемента И.

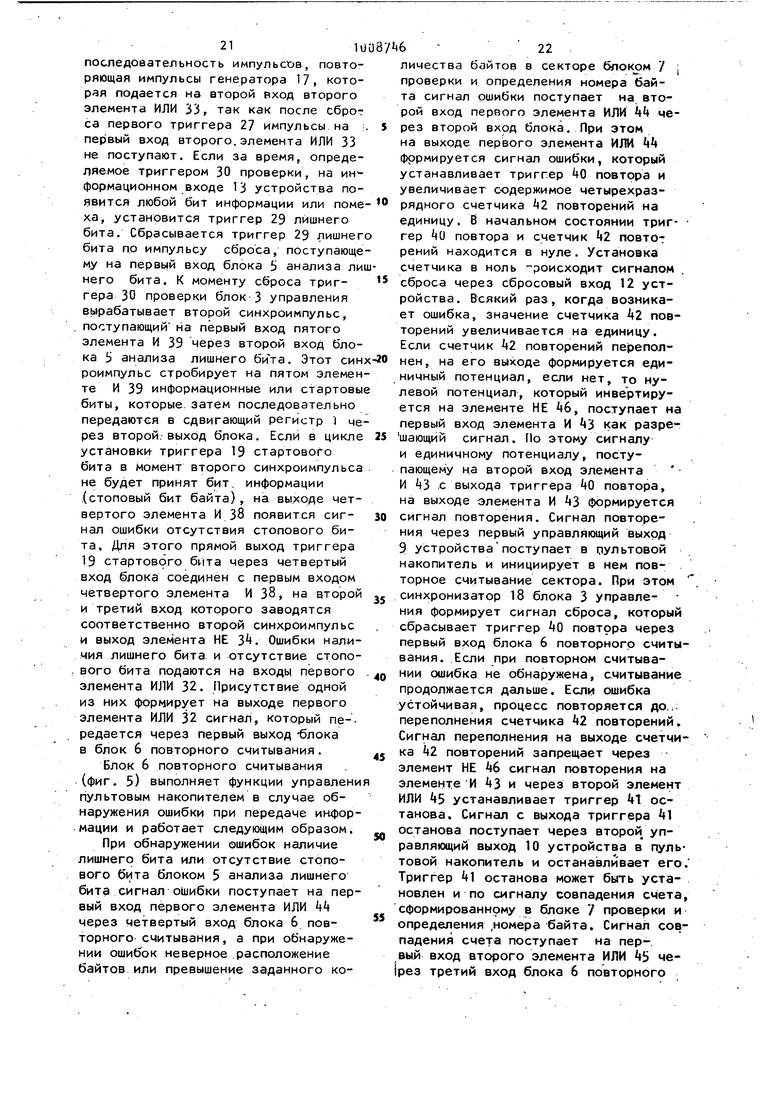

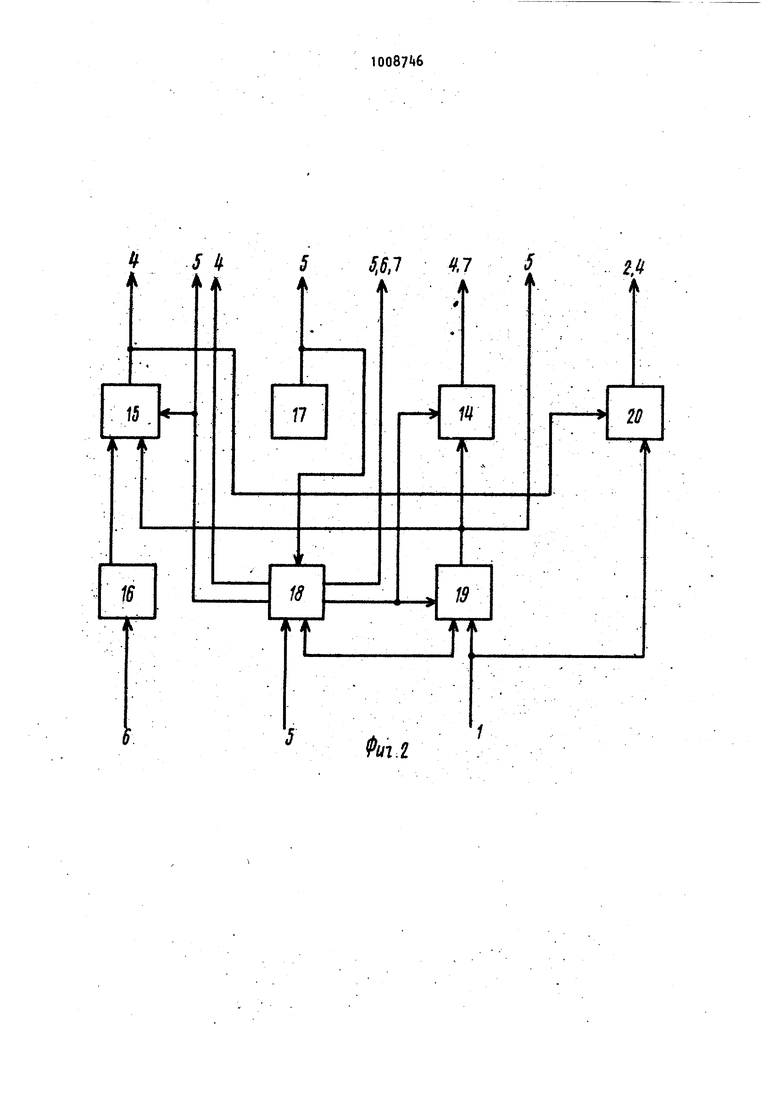

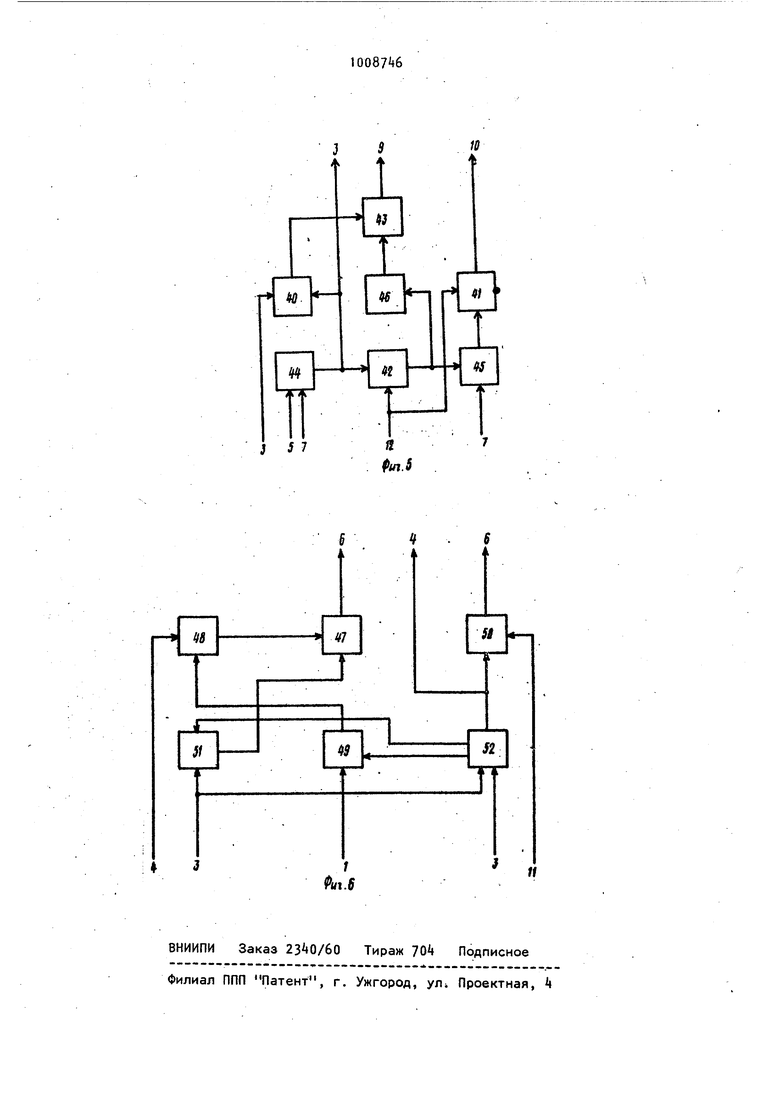

3. Устройство по п. 1, о т. ,л ичающееся тем, что блок выделения команды содержит регистр команд, мультиплексор, триггер приема команды, триггер командного байта, триггер конца команды, дешифратор,, причем выход мультиплексора, первый и второй выходы дешифратора являются соответственно первым, вторым и третьим выходами блока, первый, второй, третий, четвертый, пятый и шестой входы блока соединены соответственно со сбросовым входом триггера командного байта, синхронизирующим входом триггера командного байта, первым, вторым информационными входами мультиплексора, первым.входом триггера конца коман|ды и управляющим входом мультиплексора, третий информационный вход которого соединен с седьмым входом блока f4 информационным входом регистра команд, восьмой вход блока соединен с

синхронизирующим входом триггера приема команды, инверсный выход которого соединен с информационным уходом триггера командного байта и вторым входом триггера конца команды, выход которого соединен со сбросовым входом триггера приема команды, прямой выход которого соединен с третьим входом триггера конца команды, четвертый вход которого;,соединен с третьим выходом дешифратора, вход которого соединен с четвертым информационным входом мультиплексора и с выходом регистра ко- манд, управляющий вход которого соединен с информационным входом триггера приема команды и с выходом трипрра командного байта.

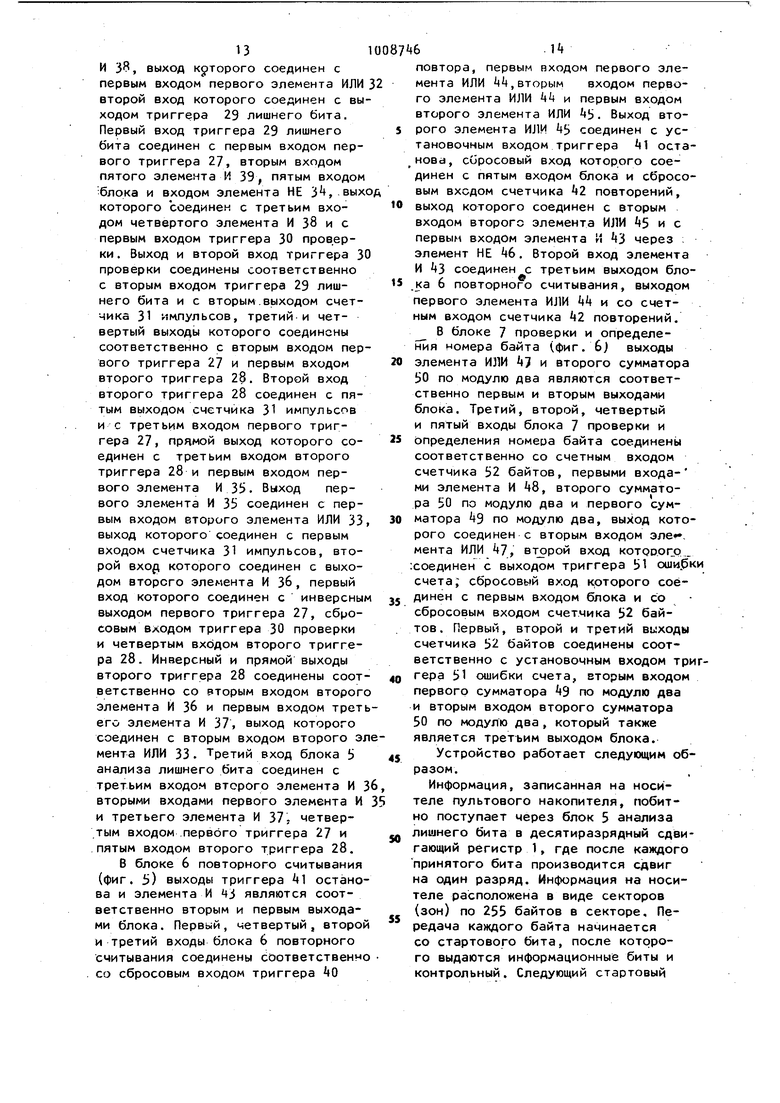

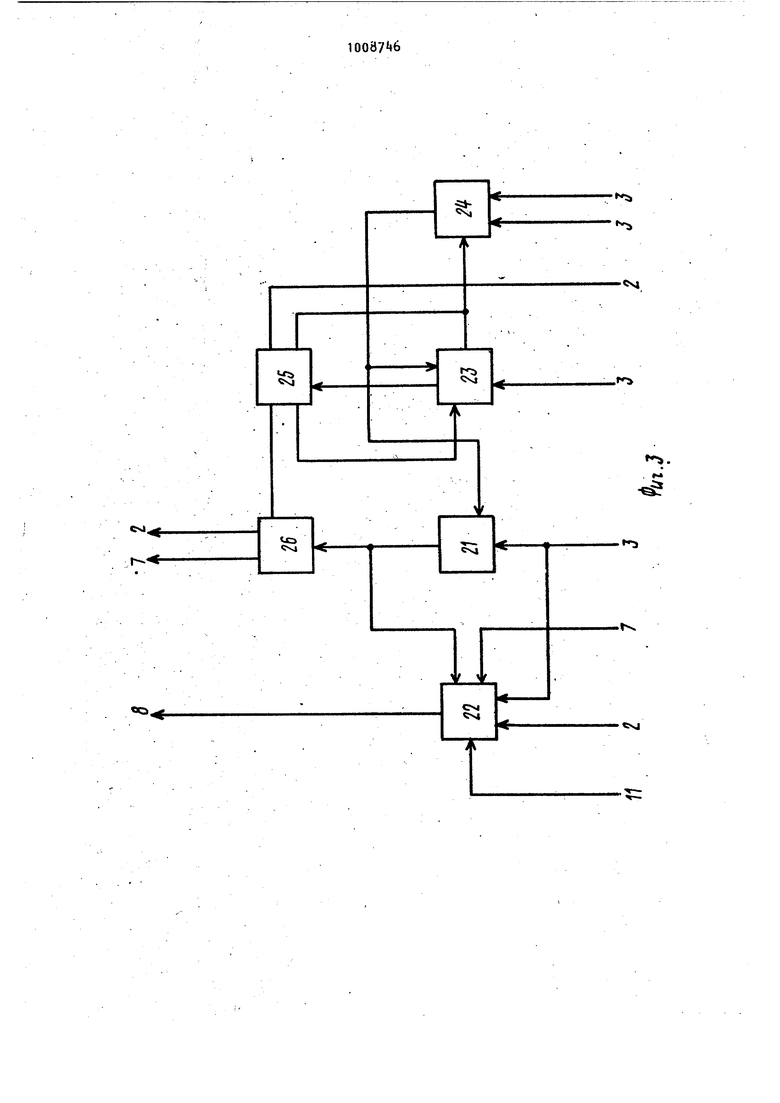

t. Устройство по п. 1, о т л и чающееся тем, что блок анализа лишнего бита содержит первый и второй триггеры, триггер лишнего бита, триггер проверки, счетчик импульсов, первый-и второй элементы ИЛИ, элемент НЕ, первый, второй, третий, четвертый и пятый элементы И, причем выходы пятого элемента И, первого элемента ИЛИ и первый выход счетчика импульсов являются соответственно первым, вторым и третьим выходами блока, первый, второй и третий входы блока соединены соответственно с/ первым входом четвертого элемента И, со сбросовым входом триггера лишнего бита и первым входом пятого элемента И, который также соединен с вторым входом четвертого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом триггера лишнего бита , первый вход кото-, рого соединен с первым входом первого триггера, вторым входом пятого элемента И, четвертым входом блока и входом элемента НЕ, выход которого соединен с третьим входом четвертого элемента И и с первым вхо1ДОМ триггера проверки, выход и второй вход которого соединены соответственно с вторым входом триггера лишнего бита и с вторым выходом счетчика импульсов, третий и четвертый выходы которого соединены соответственно с вторым входом первого триггера и первым входом второго триггера, второй вход которого соединенс пятым выходом счетчика импульсов и с третьим входом первого триггера.

прямой выход которого соединен с третьим входом второго триггера и первым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с пррвым входом счетчика импульсов, второй вход которого соединен с выходом второго элемента И, первый вход которого соединен

.с инверсным выходом первого триггера и четвертым входом второго триггера, инверсный и прямой выходы которого соединены соответственно с вторым входом второго элемента.И и первым входом третьего элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, пятый вход блока соединен с третьим вхо дом второго элемента И, вторыми входами первого и Tpetbero элементов И, четвертым входом первого триггера и пятым входом второго триггера, сбросовый вход триггера проверки соединен с вторым входом первого триггера. .

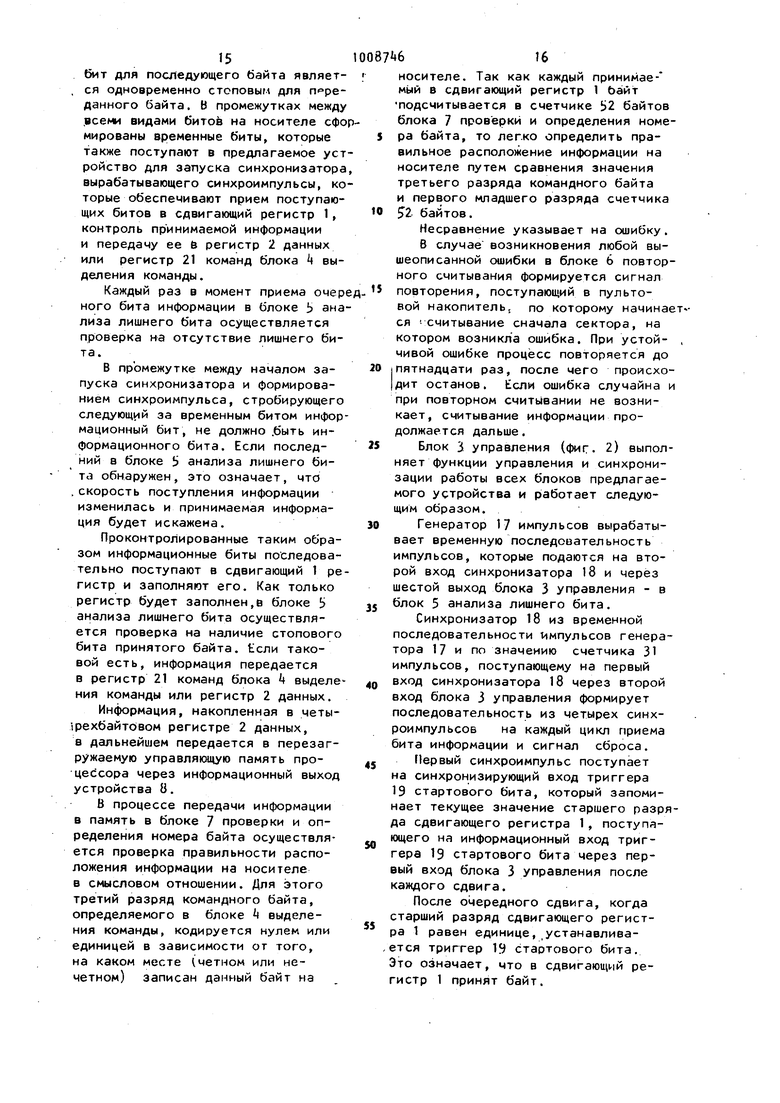

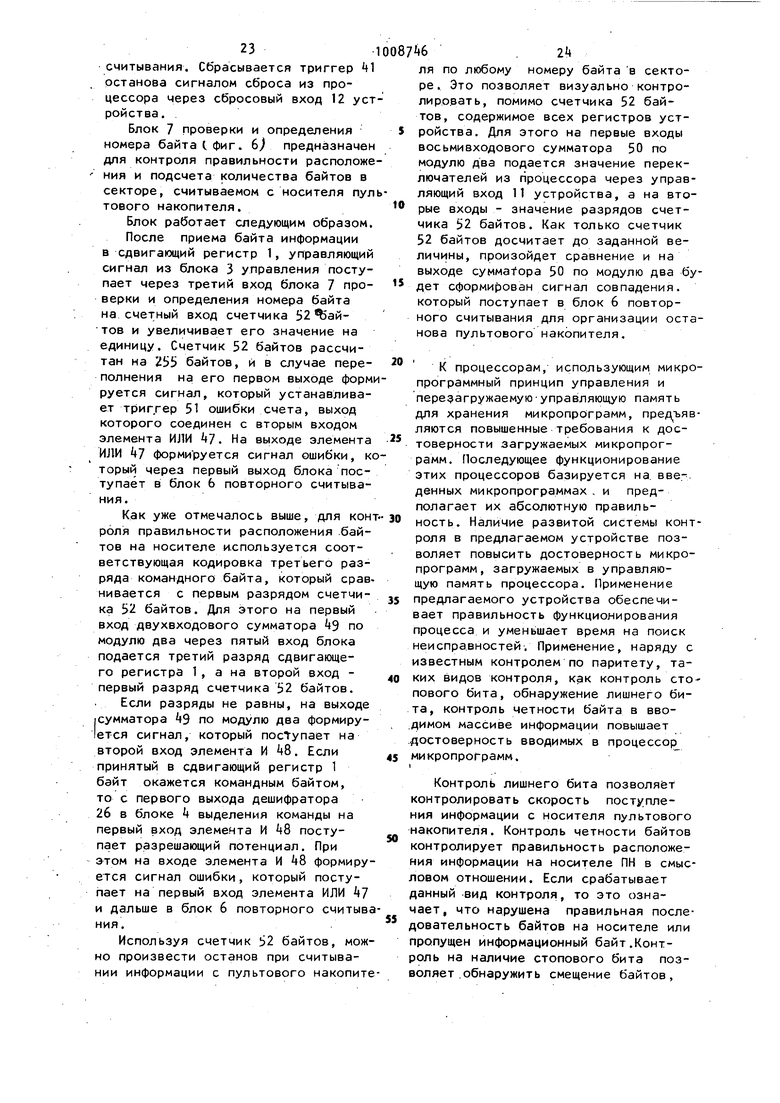

Ь. Устройство по п. 1, о т л и.чающееся тем, что блок повторного считывания содержит триггер повтора и триггер останова, счетчик повторений, элемент И, первый и второй элементы ИЛИ, элемент НЕ, причем выходы триггера останова и элемента И являются соответственно первым и вторым выходами блока, первый, второй, третий и четвертый входы блока соединены соответственно со сбросовым входом триггера првтора, первым входом первого элемента ИЛИ, вторым входом первого элемента ИЛИ и с первым входом второго элемента ИЛИ, выход которого соединен с установочным входом триггера останова, сбросовый вход которого соединен с пятым входом блока и сбросовым входом счетчика повторений, аыход которого соединен с вторым входом второго элемента ИЛИ и с первым вхо- дом элеменда И через элемент НЕ, второй вход элемента И соединен с выходом триггера повтора, установочный вход которого соединен с третьим вы;ходом блока, выходом первого элемента ИЛИ и со счетным входом счетчика повторений.

6. Устройство по п. 1, о т л ичающееся тем, что блок проверки и определения номера байта содержит элемент ИЛИ, элемент И, первый и второй сумматоры по модулю два триггер ошибки счета и счетчик байтов, причем выходы элемента ИЛИ и второго сумматора по модулю два являются соответственно первым и вторым выходами блока, первый, второй, третий и четвертый входы блока соединены соответственно со счетным вхр-дом счетчика байтов, первыми входами элемента И, втррого сумматора по модулю два и первого сумматора по модулю два , выход которого соединен с вторым входом элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом триггера ошибки счета, сбросовый вход которого соединен с пятым входом блока и со сбросовым входом счетчика байтов, первый, второй и третий выходы которого соединены соответственно с установочным входом триггера ошибки счета, вторым .входом первого сумматора по модулю два и вторым входом второго сумматора по модулю два, подключенным к третьему выходу блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1978 |

|

SU798779A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Устройство для распаковки команд | 1981 |

|

SU972507A1 |

| Устройство для контроля монтажа | 1990 |

|

SU1785001A1 |

| Устройство для контроля логическихблОКОВ | 1979 |

|

SU842821A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

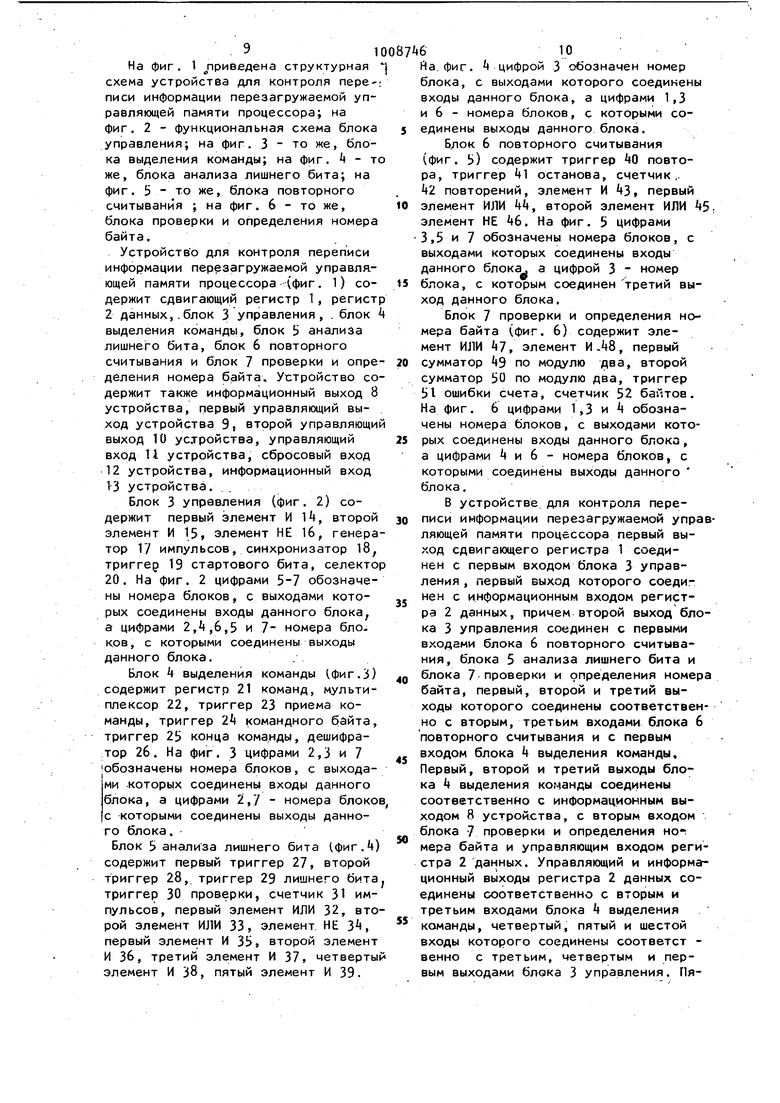

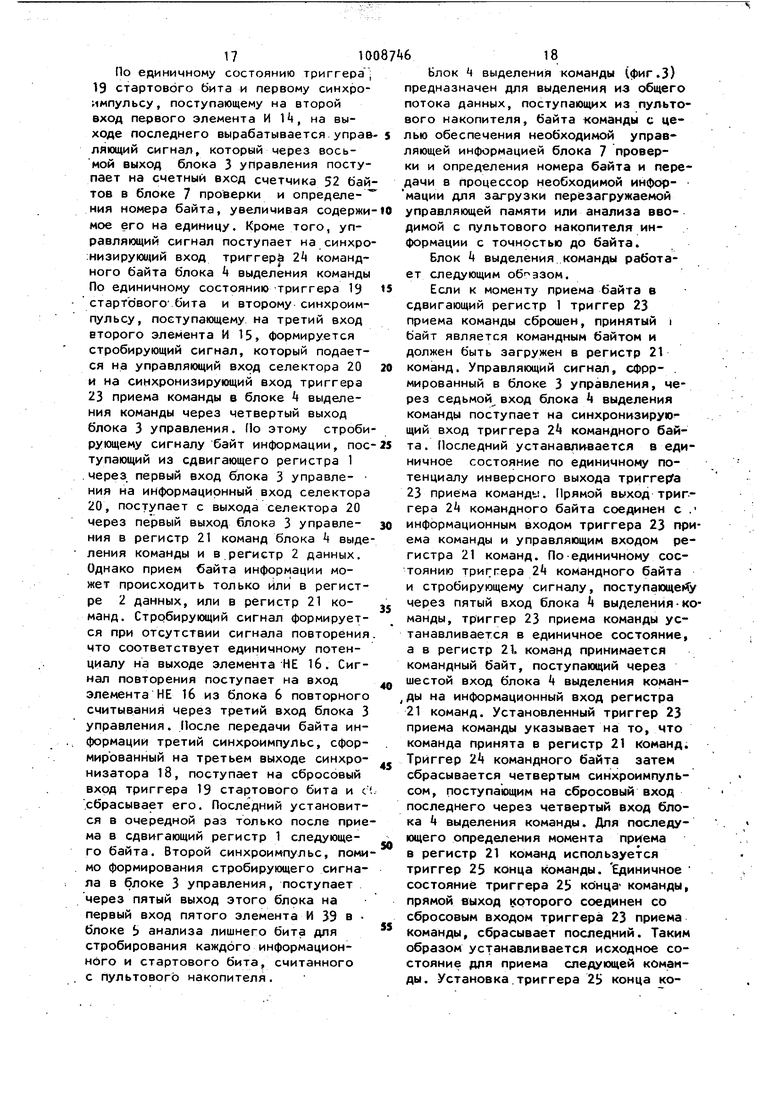

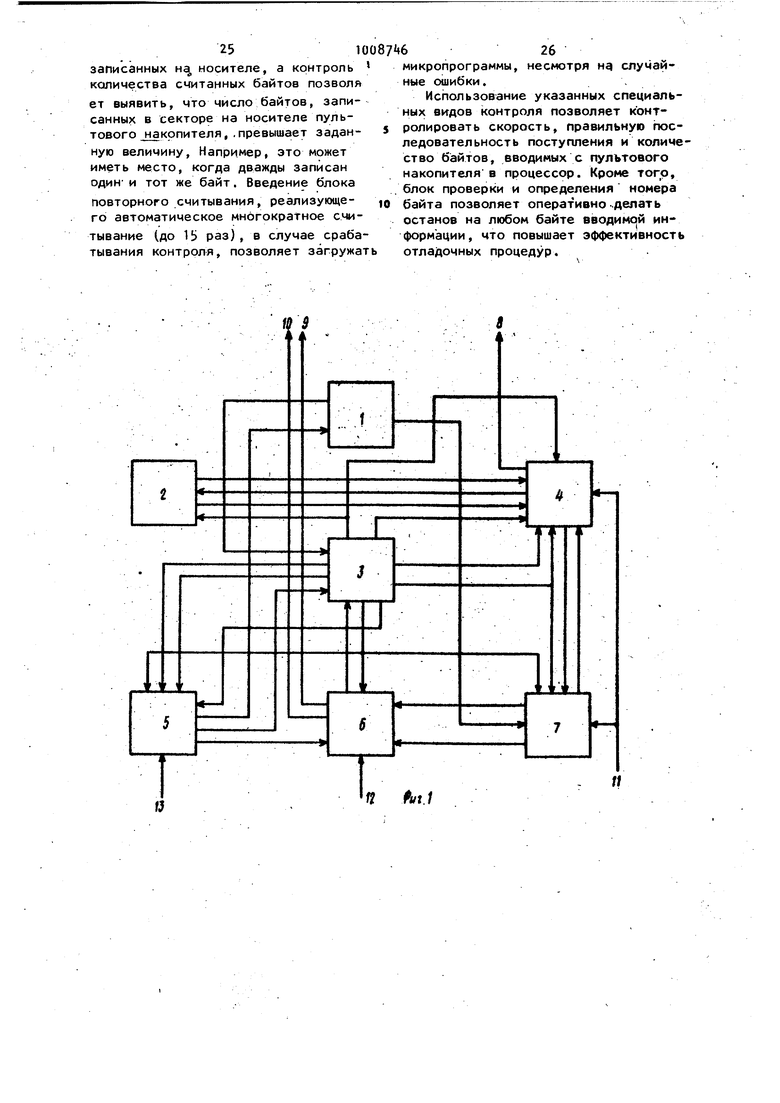

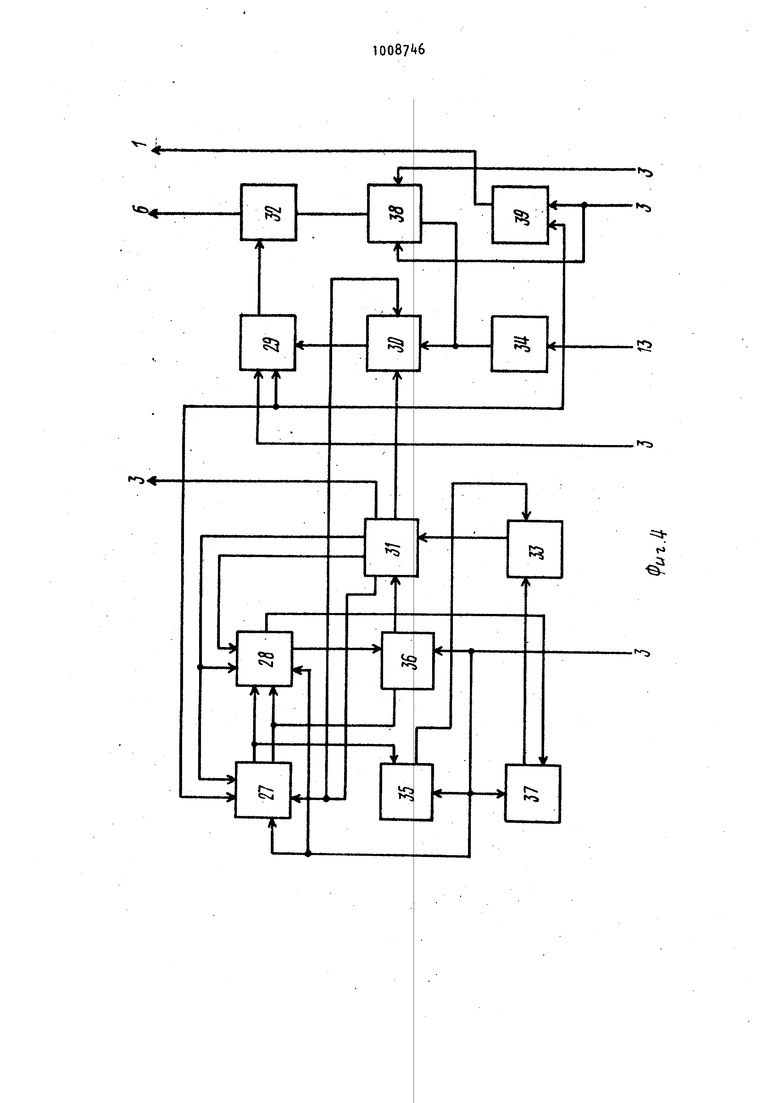

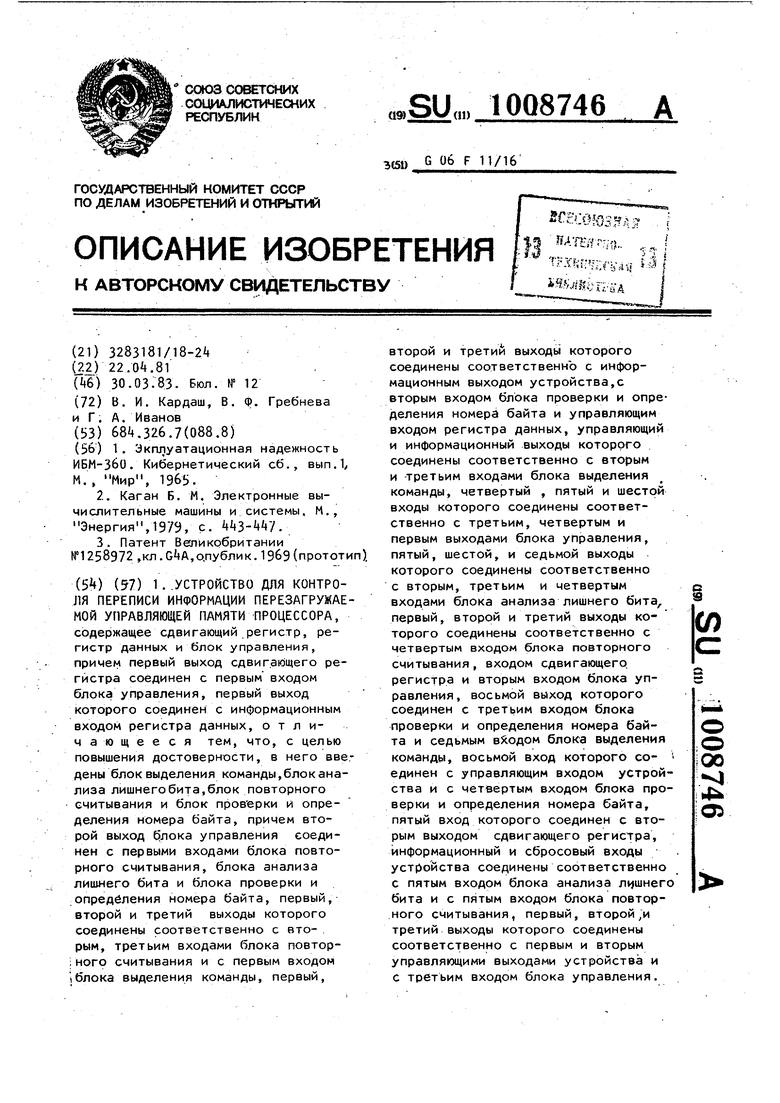

1. .УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПЕРЕПИСИ ИНФОРМАЦИИ ПЕРЕЗАГРУЖАЕМОЙ УПРАВЛЯЮЩЕЙ ПАМЯТИ ПРОЦЕССОРА, содержащее сдвигающий регистр, регистр данных и блок управления, причем первый выход сдвигающего регистра соединен с первым входом блока управления, первый выход которого соединен с информационным входом регистра данных, отличающееся тем, что, с целью повышения достоверности, в него введены блок выделения команды,блок анализа лишнегобита,блок повторного считывания и блок проверки и определения номера байта, причем второй выход блока управления соединен с первыми входами блока повторного считывания, блока анализа лишнего бита и блока проверки и определения номера байта, первый, второй и третий выходы которого соединены соответственно с вторым, третьим входами блока повтор;ного считывания и с первым входом яблока выделения команды, первый. второй и третий выходы которого соединены соответственно с информационным выходом устройства,с вторым входом блока проверки и определения номере байта и управляющим входом регистра данных, управляющий и информационный выходы которого соединены соответственно с вторым и третьим входами блока выделения команды, четвертый , пятый и шестой входы которого соединены соответственно с третьим, четвертым и первым выходами блока управления, пятый, шестой, и седьмой выходы которого соединены соответственно с вторым, третьим и четвертым входами блока анализа лишнего бита, (Л первый, второй и третий выходы которого соединены соответственно с четвертым входом блока повторного считывания, входом сдвигающего, регистра и вторым входом блока управления, восьмой выход которого соединен с третьим входом блока проверки и определения номера байта и седьмым в5содом блока выделения команды, восьмой вход которого со- оо единен с управляющим входом устройства и с четвертым входом блока про4 верки и определения номера байта, О5 пятый вход которого соединен с вторым выходом сдвигающего регистра, информационный и сбросовый входы устройства соединены соответственно с пятым входом блока анализа лишнего бита и с пятым входом блока повторного считывания, первый, второй ,и третий выходы которого соединены соответственно с первым и вторым управляющими выходами устройства и с третьим входом блока управления.

V .

1

Изобретение относится к вычи слительной технике и может быть применено в процессорах и устройствах, использующ14Х микропрограммный принцип работы Vi перезагружаемую с помощью пультового накопителя управляю|цую память.

Известно устройство для контроля неисправностей с помощью тестов, находящихся во внешних запоминающих устройствах. При этом группа тестов, обнаруживающих неисправность, считывается через канал в оперативное запоминающее устройство , и Последующими действиями центрального

процессора управляет специальная дополнительная схема, которая предназначена для проверки машины на примерах этих тестов t О

Недостатком указанного устройства является наличие лишь стандартных видов контроля ( по паритету, контрольное суммирование/, которые не позволяют переписывать в память информацию с высокой достоверностью, так как значительная часть системы (канал, оперативное запоминающее устройство, дополнительные схемы, необходимая для переписи информации в память, не должна вносить ошибку, что в деист1вительности не всегда имеет место. Все это осложняет контроль и требует обслуживающего персонала высокой квалификации. Известно устройство для контроля и диагностики процессора, использующее метод раскрутки, позволяющий использовать микропрограммнлг управление для диагностики неисправностей. При проверке исправности оборудования этапу микродиагностики предшествует подготовительный этап, которым управляет оператор с пульта машины. В устройство входит включаемая с пульта процессора диагностическая аппаратура: сдвиговый регистр, счет чик адреса и схема управления, обес печивающие проверку некоторой облас ти памяти в режимах . записи, считывания О (1); селекторный кйнал (который предварительно не проверяется) , запоминающее устройство на магнитной ленте с записанными на ней тестами,и специальный регистр для кодов тестовых операций. Дальше процесс контроля и диагностики проц сора на базе этого оборудования про текает автоматически по методу раск рутки 2 . Одним из недостатков устройства является значительный объем непрове ряемого оборудования, используемый в. качестве диагностического ядра (канал, память, диагностическая апп ратура) , вторым - необходимость участия человека с достаточно высокой квалификацией для проверки и на ладки ядра. Кроме того, загружаемые диагностические тесты не имеют специального контроля, а контролируются V. W стандартной аппаратурой по паритету (так как используются общие сред ства для загрузки и память). Наиболее близким к предлагаемому является устройство для контроля и диагностики неисправностей процессо ра, включающее блок сдвигающего регистра, вентили для приема байта, однобайтовый регистр, дешифратор и блок регистра данных, содержащий i трехбайтовый регистр и логику управления. Устройство позволяет диагностировать центральный процессор и загружать микропрограммы в перезагружаемую управляющую память посредством ввода управляющей информации и данных через блок сдвигающего регистра и блок регистра данных. С помощью управляющего регистра процессора производится воздействие на различные контролируемые элементы процессора и результат воздействия записывается в память для последующего анализа з. Недостатком известного устройства является отсутствие специальных видов контроля, контролирующих расположение информации на носителе и перепись в перезагружаемую управляющую память с высокой достоверностью. Известно, что уменьшить потери от сбоев и отказов, порождающих ошибки, можно, предотвратив распространение ошибки в вычислительном процессе, так как в противном случае усложняется и удлиняется процедура проверки правильности работы и определение неисправностей. Для этого необходимо обнаружить появление ошибки возможно ближе к моменту ее возникновения. Используемый в устройстве контроль, включающий только контроль по паритету, не позволяет с высокой достоверностью контролировать процессор и вводимую в него информацию. Цель изобретения - повышение достоверности. Поставленная цель достигается тем, что в устройство, содержащее сдвигающий регистр, регистр данных и блок управления, причем первый выход сдвигающего регистра соединен с первым входом блока управления, первый выход которого соединен с информационным входом регистра данных, дополнительно введены блок выделения командь блок анализа лишнего бита, блок повторного считывания и блок проверки и определения номера байта, причем второй выход блока управления соединен с первыми входами блока повторного считывания, блока анализа лишнего бита и блока проверки и определения номера байта, первый, ВТОРОЙ и третий выходы кото-. рого соединены соответственно с BTOрым, третьим входами блока повторного считывания и с первым входом блока выделения команды, первый, второй и третий выходы которого.сое динены соответственно с информационным- входом устройства, с вторым входом блока проверки и определения но мера байта и управляющим входом регистра данных, управляющий и информационный. выходы которого соединены соответственно с вторым и третьим , входами блока выделения команды, чет вертый, пятый и шестой входы которого соединены соответственно с третьим, четвертым и первым выходами блока управления, пятый, шестой и седьмой выходы которого соединены со .ответственно с вторым, третьим и четвертым входами блока анализа лиш него бита, первый, второй и третий выходы которого соединены соответственно с четвертым входом блока по торного считывания, входом сдвигающего регистра и вторым входом блока управления, восьмой выход которого единен с третьим входом блока проверки и определения номера байта и седьмым входом блока выделенг я команды, восьмой вход которого соединен с управляющим входом устройства и с четвертым входом блока проверки и определения номера байта, пятый вход которого соединен с вторым выходом сдвигающего регистра, информационный и сбросовый входы устройства соединены соответственно с пятымвходом блока анализа лишнего бита и с пятым входом блока првторного считывания, первый, второй и третий выходы которого соединены со ответственно с первым и вторым управляющими выходами устройства и с третьим входом блока управления. Блок управления содержит первый и второй элементы И, элемент НЕ, ге нератор |и мпульсов, синхронизатор, триггер стартового бита и селектор причем выходы селектора,первого элемента И, сбросовый выход синхронизатора, первый и второй выходы синхронизатора являются.соответственно первым, вторым, третьим, четвертым .и пятым выходами блока, первый и вторюй входы блока сое динены соответственно с первым входом второго элемента И через элемен НЕ V) первым входом синхрониза тора, третий вход блока соединен с информационным входом селектора и информационным входом триггера стартового бита, выход которого со(единен с первым входом первого элемента И, шестым выходом блока и вторым входом .второго элемента И, вы- .. ход которого соединен с управляющим входом селектора и является седьмым выходом блока восьмой выход блока соединен с выходом генератора импульсов и вторым входом синхронизатора, третий выход которого соединен со сбросовым входом триггера, стартс ого бита, синхрон 1зирующий вход которого соединен с вторым входом первого элемента И и четвертым выходом синхронизатора, второй выход которого соединен с третьим входом второго элемента И. Блок выделения команды содержитрегистр команд, мультиплексор, . триггер.приема команды, триггер командного байта, триггер конца-ка, манды, дешифратор, причем выход мультиплексора, первый и второй выходы дешифратора являются соответственно первым, вторым и третьим выходами блока, первый, второй, третий, четвертый, пятый и шестой входы блока соединены соответственно со сбросовым входом триггера командного байта, синхронизирующим входом триггера командного байта, первым, вторым информационными входами мультиплексора, первым входом триггера конца команды и управляюи и входом мультиплексора, третий информационный вход которого соединен с седьмым входом блока и информационным входом регистра команд, восьмой вход блока соединен с синхронизирующим входом триггера приема команды, инверсный выход которого соединен с информационным входом триггера командного байта и вторым входом -триггера конца команды, выход . которого соединен со сбросовым входом триггера приёма команды, прямой .выход которого соединен с третьим входом триггера конца команды,,четвертый вход которого соединен с третьим выходом дешифратора, вход которого соединен с четверым информационным входом мультиплексора и с выходом регистра команд, управляющий вход которого соединен с информационным входом триггера приема команды и с выходом триггера командного байта. 7 При этом блок, анализа лишнего бита содержит первый и второй триггеры, триггер лишнего бита, триггер проверки,-счетчик импульсов, первый и второй элементы ИЛИ, элемент НЕ, первый, второй, третий , четвертый и пятый элементы И, причем выходы п того элемента И, первого элемента ИЛИ и первый выход счетчика импульсов являются соответственно первым, вторым и третьим выходами блока, первый., второй и третий вхоДы блока соединены соответственно с первым входом четвертого элемента И, котор также соединен с вторым входом четв того элемента И, выход кото|эрго сое динен с первым входом первог элемента ИЛИ, второй вход которого соединен с выходом триггера лишнего бита, первый вход которого соединен с первым входом первого триггера, вторым входом пятого элемента И, че вертым входом блока и входом элемен та НЕ, выход которого соединен с третьим входом четвертого элемента , и с первь1м входом триггера проверки выход и второй вход которого соединены -соответственно с вторым входом .триггера лишнего бита и.с вторым выходом счетчика импульсов, третий четвертыйвыходы которого соединены соответственно с вторым входом первого триггера и первым входом второго триггера, второй вход которого соединен с пятым выходом счетчика импульсов и с третьим входом первого триггера, прямой выход которого соединен с третьим входом второго триггера и первым входом первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ,выход которого соединен с первым входом счетчика импульсов второй вход которого соединен с выходом второго элемента И, первый вход которого соединен с инверсным выходом первого триггера и четвертым входом .второго триггера, инверсный и прямой выходы которого соединены соответственно с вторым входом второго Jэлeмeнтa И и первым входом третьего, элемента И, выход которого соединен с вто(эым входом второго элемента ИЛИ, пятый вход блока соединен с третьим входом второго элемента И, вторыми входами первого и третьего элементов И, четвертым входом первого триггера и пятым входом второго триггера, сбросовый вход триггера 8 с вторым входом пер 6проверки соединен вого триггера. Кроме того, блок повторного счит ывания содержит триггер повтора tИ; триггерf останова, счетчик повторений, элемент И, первый и второй элементы ИЛИ, элемент НЕ, причем выходы триггера останова и элемента И являются соответственно первым и вторым выходами блока, первы.й, второй, третий , четверты.й входы блока соединены соответственно со сбросовым входом триггера повтрра., первым входом первого элемента ИЛИ, вторым )входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, выход которого соединен с установочным входом триггера останова, сбросовый вход которого соединен с пятым входом блока И сбросовым входом счетчика повторений , выход которого соединен с вторым входом второго элемента ИЛИ и с Первым входом элемента И через. элемент НЕ, вторЬй вход элемента И соединен с выходом триггера повтора, установочный вход которого соединен с третьим выходом блока, выходом первого элемента ИЛИ и со счетным входом счетчика повторений; Блок проверки и определения номера байта содержит элемент ИЛИ. элемент И, первый и второй сумматоры по модулю два , триггер ошибки счета и счетчик байтов, причем выходы элемента ИЛИ и второго сумматора по модулю два являются соответственно первым и вторым выходами блока, первый, второй, третий и чехвертый входы блока соединены соответственно со счетным входом счетчика байтов, первыми входами элемента И, второго, сумматора по модулю два и первого сумматора по модулю два, выход которого соединен с вторым входом элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с вь1ходом триггера ошибки счета, сбросовый вход которого соединен с пятым входом блока и со сбросовым входом счетчика байтов, первый, второй и третий выходы которого соединены соответственно с установочным :входом триггера ошиб ки счета, вторым входом первого сумматора по модулю два и вторым входом второго сумматора по модулю два подключе.нным к третьему выходу блока. На фиг, 1 приведена структурная схема устройства для контроля переписи информации перезагружаемой управляющей памяти процессора; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - то же, блока выделения команды; на фиг. - т же, блока анализа лишнего бита; на фиг. 5 - то же, блока повторного считывания ; на фиг. 6 - то же, блока проверки и определения номера байта. Устройство для контроля переписи информации перезагружаемой управляющей памяти процессора -(фиг. 1) содержит сдвигающий регистр 1 регист . блок 2 данных,.блок 3 управления, выделения команды, блок 5 анализа лишнего бита, блок 6 повторного считывания и блок 7 проверки и опре деления номера байта. Устройство со держит также информационный выход 8 устройства, первый управлякяций выход устройства 9| второй управляющи выход 10 ус.тройства, управляющий вход 11 устройства, сбросовый вход 12устройства, информационный вход 13устройства. . Блок 3 управления (фиг. 2) содержит первый элемент И 1, второй элемент И 15, элемент НЕ 16, генера тор Г/ импульсов, синхронизатор 18, триггер 19 стартового бита, селекто 20. На фиг. 2 цифрами 5-7 обозначены номера блоков, с выходами которых соединены входы данного блока, а цифрами 2,,6,5 и 7- номера бло. К.О8, с которыми соединены выходы данного блока. . Блок k выделения команды (фиг.З) содержит регистр 21 команд, мультиплексор 22, триггер 23 приема команды, триггер 2 командного бййта, триггер 25 конца команды, дешифратор 2б. На фиг. 3 цифрами 2,3 и 7 обозначены номера блоков, с выходами .которых соединены входы данного блока, а цифрами 2,7 - номера блоко с которыми соединены выходы данного блока. Блок 5 анализа лишнего бита (фиг.) содержит первый триггер 27, второй триггер 28, триггер 29 лишнего бита триггер 30 проверки, счетчик 31 импульсов, первый элемент ИЛИ 32, вто рой элемент ИЛИ 33, элемент. НЕ 3, первый элемент И 35, второй элемент И 36, третий элемент И 37, четверты элемент И 38, пятый элемент И 39. 1 6 На.фиг. цифрой 3 обозначен номер блока, с выходами которого соединены входы данного блока, а цифрами 1,3 и 6 - номера блоков, с которыми соединены выходы данного блока. БЛОК 6 повторного считывания (фиг. 5) содержит триггер Q повтора, триггер 4 останова, счетчик,. k2 повторений, элемент И , первый элемент ИЛИ kk, второй элемент ИЛИ k. элемент НЕ 46. На фиг. 5 цифрами 3,5 и 7 обозначены номера блоков, с выходами которых соединены входы данного блока а цифрой 3 - номер блока, с которым соединен третий выход данного блока. Блок 7 проверки и определения номера байта (фиг. 6) содержит элемент ИЛИ 7, элемент И .48, первый сумматор ЦЭ по модулю два, второй сумматор 50 по модулю два, триггер 51 ошибки счета, счетчик 52 байтов. На фиг. 6 цифрами 1,3 и 4 обозначены номера блоков, с выходами которых соединены входы данного блока, а цифрами 4 и 6 - номера блоков, с которыми соединены выходы данного блока. В устройстве для контроля переписи информации перезагружаемой управляющей памяти процессора первый выход сдвигающего регистра 1 соединен с первым входом блока 3 управления , первый выход которого соединен с информационным входом регистра 2 данных, причем второй выход блока 3 управления соединен с первыми входами блока 6 повторного считывания, блока 5 анализа лишнего бита и блока 7 проверки и определения номера байта, первый, второй и третий выходы которого соединены соответственно с вторым, третьим входами блока 6 повторного считывания и с первым входом блока 4 выделения команды. Первый, второй и третий выходы блока 4 выделения команды соединены соответственно с информационным выходом 8 устройства, с вторым входом блока 7 проверки и определения номера байта и управляющим входом регистра 2 данных. Управляющий и информационный выходы регистра 2 данных соединены соответственно с вторым и третьим входами блока 4 выделения команды, четвертый, пятый и шестой входы которого соединены соответст венно с третьим, четвертым и первым выходами блока 3 управления. Пятый, шестб 1 и седьмой выходы блока , управления соединены соответстренно с вторым, третьим.и четвертым входами блока 5 анализа лишнего бита, первый, второй и третий выходы которого соединены соответственно с четвертым входом блока 6 повторного считывания, входом сдвигающего регистра 1 и вторым входом блока 3 уп равлений. Восьмой выход блока 3«управления соединен с третьим входом блока 7 проверки и определения номера байта .и седьмым входом блока t выделения команды, восьмой вход которого соединен с управляющим входом устройства 11 и с четвертым входом блока 7 проверки и определения номера байта, пятый вход которого соединен с вторым выходом сдвигающего регистра 1. Информационный 13 и сбросовый 12 входы устро ства соединены соответственно с пятым входом блока 5 анализа лишнего бита и с пятым входом блока 6 повторного считывания, первый, второй и третий выходы которого соединены соответственно с первым 9 и вторым .10 управляющими выходами устройства и с третьим входом блока 3 управления. ..В блоке 3 управления (фиг.2) выходы селектора 20, первого элемента И I, сбросовый выход синхронизатора 18, первый и второй выходы син ронизатора 18 являются соответствен но первым, восьмым, вторым, третьим и пятым выходами блока. Третий и второй входы блока 3 управления сое нены соответственно с первым входом второго элемента И 15 через элемент НЕ 16 и первым входом синхронизатора 18. Первый вход блока 3 управления соединен с информационным входом селектора 20 и информационным входом триггера 19 стартового бита, выход которого соединен с первым входом первого элемента И 1Л, седьмым выходом блока и вторым входом второго элемента И 15. Выход второг элемента И 15 соединен с управляющим входом селектора 20 и является четвертым выходом блока. Шестой выход блока 3 управления соединен с выходом генератора 17 импульсов и вторым, входом синхронизатора 18, третий выход которого соединен со сбро совым входом триггера 19 стартового ;бита. Синхронизирующий вход триггера 19 стартового бита соединен со вторым входом первого элемента И Т ; и четвертым выходом синхронизатора 18. второй выход которого соединен с третьим входом второго элемента И 15. В блоке выделения команды (фиг. 3) выход мультиплексора 22, первый и второй выходы дешифратора 2б являются соответственно первым, вторым и третьим выходами блока. Четвертый, седьмой, третий, первый, второй и восьмой входы блока k выделения команды соединены соответственно со сбросовым входом триггера 2А командного байта, синхронизирующим входом триггера 2 командного байта, первым, вторым информационными входами мультиплексора 22, первым входом триггера 25 конца команды, управляющим входом мультиплексора 22. Третий информационный вход мультиплексора 22 соединен с шестым входом блока k выделения команды и информационным входом регистра 21 команд. Пятый вход блока 4 выделения команды соединен с синхронизирующим входом триггера 23 приема команды, инверсный выход которого соединен с информационным входом триггера 2 командного байта и вторым входом триггера 25 конца команды. Выход триггера 25 конца команды соединен со сбросовым входом триггера 23 приема команды, прямой выход которого соединен с третьим входом триггера 25 .конца команды, четвертый вход которого соединен с третьим выходом дешифратора 2б, вход которого соединен с четвертым информационным входом мультиплексора 22 и с выходом регистра 21 команд, управляющий вход которого соединен с информационным входом триггера 23 приема команды и с выходом триггера командного байта. В блоке 5 анализа лишнего бита (фиг. k) выходы пятого элемента И 39, первого эле.мента ИЛИ 32 и первый выход счетчика 31 импульсов являются соответственно вторым, первым и третьим выходами блока. Четвертый, первый и второй входы блока 5 анализа лишнего бита соединены соответственно с первым входом четвертого элемента И 38, со сбросовым входом триггера 29 лишнего бита и первым- входом пятого элемента И 39, который также соединен со вторым входом четвертого элемента 13 и 3, выход ксрторого соединен с первым входом первого элемента ИЛИ второй вход которого соединен с вы ходом триггера 29 лишнего бита. Первый вход триггера 29 лишнего бита соединен с первым входом первого триггера 27, вторым входом пятого элемента И 39, пятым входом Яблока и входом элемента НЕ 3, вых которого соединен с третьим входом четвертого элемента И 38 и с первым входом триггера 30 проверки. Выход и второй вход триггера 3 проверки соединены соответственно с вторым входом триггера 29 лишнего бита и с вторым.выходом счетчика 31 импульсов, третий и четвертый выходы которого соединены соответственно с вторым входом пер вого триггера 27 и первым входом второго триггера 28. Второй вход второго триггера 28 соединен с пятым выходом счетчика 31 импульсов и с третьим входом первого триггера 27, прямой выход которого соединен с третьим входом второго триггера 28 и первым входом первого элемента И 3i). Выход первого элемента И 35 соединен с первым входом второго элемента ИЛИ 33 выход которого соединен с первым входом счетчика 31 импульсов, второй вхор которого соединен с выходом второго элемента И Зб, первый вход которого соединен с инверсны выходом первого триггера 27, сбросовым входом триггера 30 проверки и четвертым входом второго триггера 28. Инверсный и прямой выходы второго триггера 28 соединены соот ветственно со вторым входом второг элемента И Зб и первым входом трет его элемента И 37, выход которого соединен с вторым входом второго э мента ИЛИ 33 . Третий вход блока i анализа лишнего бита соединен с третьим входом второго элемента И вторыми входами первого элемента И и третьего элемента И 37, четвертым входом первого триггера 27 и пятым входом второго триггера 28. В блоке 6 повторного считывания (фиг. 5) выходы триггера 41 остано ва и элемента И 43 являются соответственно вторым и первым выходами блока. Первый, четвертый, второ и третий входы блока 6 повторного считывания соединены соответственн со сбросовым входом триггера 0 б повтора, первым входом первого элемента ИЛИ 4, вторым входом первого элемента ИЛИ 4 и первым входом второго элемента ИЛИ ij. Выход второго элемента ИЛИ 5 соединен с установочным входом триггера 41 останова, сиросовый вход которого соединен с пятым входом блока и сбросовым входом счетчика 42 повторений, выход которого соединен с вторым входом второго элемента ИЛИ 45 и с первым входом элемента И 43 через ; элемент НЕ 46. Второй вход элемента И 43 соединен с третьим выходом блока 6 повторного считывания, выходом первого элемента ИЛИ 44 и со счетным входом счетчика 42 повторений. В блоке 7 проверки и определения номера байта (фиг. 6) выходы элемента ИЛИ 4 и второго сумматора 50 по модулю два являются соответственно первым и вторым выходами блока. Третий, второй, четвертый и пятый входы блока 7 проверки и определения номера байта соединены соответственно со счетным входом счетчика 52 байтов, первыми входами элемента И 48, второго сумматора 50 по модулю два и первого сумматора 49 по модулю два, выход которого соединен с вторым входом . мента ИЛИ 47, второй вход котоорг о.. соединен с выходом триггера 51 оши.бки счета; сбросовь й вход которого соединен с первым входом блока и со сбросовым входом счетчика 52 байтов. Первый, второй и третий выходы счетчика 52 байтов соединены соответственно с установочным входом триггера 51 ошибки счета, вторым входом первого сумматора 49 по модулю два и вторым входом второго сумматора 50 по модулю два , который также является третьим выходом блока. Устройство работает следующим образом. Информация, записанная на носителе пультового накопителя, побитно поступает через блок 5 анализа лишнего бита в десятиразрядный сдвигающий регистр 1, где после каждого принятого бита производится сдвиг на один разряд. Информация на носителе расположена в виде секторов (зон) по 255 байтов в секторе. Передача каждого байта начинается со стартового бита, после которого выдаются информационные биты и контрольный. Следующий стартовый бит для последующего байта является одновременно стоповыгл для п реданного байта. В промежутках между .всеми видами битов на носителе сфо мированы временные биты, которые также поступают в предлагаемое уст ройство для запуска синхронизатора вырабатывающего синхроимпульсы, ко торые обеспечивают прием поступающих битов в сдвигающий регистр 1, контроль принимаемой информации и передачу ее 6 регистр 2 данных или регистр 21 команд блока 4 выделения команды. Каждый раз в момент приема очер ного бита информации в блоке Ь ана лиза лишнего бита осуществляется проверка на отсутствие лишнего бита. В промежутке между началом запуска синхронизатора и формированием синхроимпульса, стробирующего следующий за временным битом инфор мационный бит, не должно .быть информационного бита. Если последний в блоке J анализа лишнего бита обнаружен, это означает, что . скорость поступления информации изменилась и принимаемая информация будет искажена. Проконтролированные таким образом информационные биты последовательно поступают в сдвигающий 1 ре гистр и заполняют его. Как только регистр будет заполнен,в блоке Ij анализа лишнего бита осуществляется проверка на наличие стопового бита принятого байта, сли таковой есть, информация передается в регистр 21 команд блока k выделе ния команды или регистр 2 данных. Информация, накопленная в четыфехбайтовом регистре 2 данных, в дальнейшем передается в перезагружаемую управляющую память процессора через информационный выход устройства 8. В процессе передачи информации в память в блоке 7 проверки и определения номера байта осуществляется проверка правильности расположения информации на носителе в смысловом отношении. Для этого третий разряд командного байта, определяемого в блоке 4 выделения команды, кодируется нулем или единицей в зависимости от того, на каком месте (четном или нечетном) записан данный байт на носителе. Так как каждый принимае- мый в сдвигающий регистр 1 байт подсчитывается в счетчике Ь2 байтов блока 7 проверки и определения номера байта, то легко определить правильное расположение информации на носителе путем сравнения значения третьего разряда командного байта и первого младшего разряда счетчика 2 байтов. Несравнение указывает на ошибку. В случае возникновения любой вышеописанной ошибки в блоке 6 повторного считывания формируется сигнал повторения, поступающий в пультовой накопитель, по которому начинает ся считывание сначала сектора, на котором возникла ошибка. При устой- , чивой ошибке процесс повторяется до пятнадцати раз, после чего происходит останов, tcnn ошибка случайна и при повторном считывании не возникает, считывание информации продолжается дальше. Блок 3 управления (фиг. 2) выполняет функции управления и синхронизации работы всех блоков предлагаемого устройства и р аботает следующим образом. Генератор 17 импульсов вырабатывает временную последовательность импульсов, которые подаются на второй вход синхронизатора 18 и через шестой выход блока 3 управления - в блок 5 анализа лишнего бита. Синхронизатор 18 из временной последовательности 11мпульсов генератора 17 и по значению счетчика 31 импульсов, поступающему на первый вход синхронизатора 18 через второй вход блока 3 управления формирует последовательность из четырех синхроимпульсов на каждый цикл приема бита информации и сигнал сброса. Первый синхроимпульс поступает на синхронизирующий вход триггера 19 стартового бита, который запоминает текущее значение старшего разряда сдвигающего регистра 1, поступающего на информационный вход триггера 19 стартового бита через первый вход блока 3 управления после каждого сдвига. После очередного сдвига, когда старший разряд сдвигающего регистра 1 равен единице, устанавливается триггер 19 стартового бита. Это означает, что в сдвигающий регистр 1 принят байт. 1710 По единичному состоянию триггера ; 19 стартового бита и первому синхроимпульсу, поступающему на второй вход первого элемента И , на выходе последнего вырабатывается управ лягаций сигнал, который через восьмой выход блока 3 управления поступает на счетный вход счетчика 52 бай тов в блоке 7 проверки и определе- ния номера байта, увеличивая содержи мое его на единицу. Кроме того, управляющий сигнал поступает на синхро :низируюи ий вход триггерй 2k командного байта блока k выделения команды По единичному состоянию триггера 1Э стартЪвого бита и второму синхроимпульсу, поступающему на третий вход второго элемента И 15, формируется стробирующий сигнал, который подается на управляющий вход селектора 20 и на синхронизирующий вход триггера 23 приема команды в блоке Ц выделения команды через четвертый выход блока 3 управления. По этому строби рующему сигналу байт информации, пос тупающий из сдвигающего регистра 1 .через первый вход блока 3 управле- ния на информационный вход селектора 20, поступает с выхода селектора 20 через первый выход блока 3 управления в регистр 21 команд блока 4 выде ления команды и в регистр 2 данных, Однако прием байта информации может происходить только или в регистре 2 данных, или в регистр 21 команд, Стробирующий сигнал формируется при отсутствии сигнала повторения что соответствует единичному потенциалу на выходе элемента НЕ 1б, Сигнал повторения поступает на вход элемента НЕ 16 из блока 6 повторного считывания через третий вход блока 3 управления. После передачи байта информации третий синхроимпульс, сформированный на третьем выходе синхронизатора 18, поступает на сбросовый вход триггера 19 стартового бита и с .сбрасывает его. Последний установится в очередной раз только после прие ма в сдви гающий регистр 1 следующего байта. Второй синхроимпульс, поми мо формирования стробирующего сигнала в блоке 3 управления, поступает через пятый выход этого блока на первый вход пятого элемента И 39 в блоке Ь анализа лишнего бита для стробирования каждого информационного и стартового бита, считанного с пультового накопителя. Блок 4 выделения команды (фиг.З) редназначен для выделения из общего отока данных, поступающих из пультоого накопителя, байта команды с цеью обеспечения необходимой управяющей информацией блока 7 проверки и определения номера байта и переачи в процессор необходимой информации для загрузки перезагружаемой управляющей памяти или анализа вводимой с пультового накопителя информации с точностью до байта. Блок 4 выделения команды работает следующим . Если к моменту приема байта в сдвигающий регистр 1 триггер 23 приема команды сброшен, принятый i байт является командным байтом и должен быть загружен в регистр 21 команд. Управляющий сигнал, сфрр- . мированный в блоке 3 управления, через седьмой вход блока k выделения команды поступает на синхронизирую щий вход триггера 2k командного байта , Последний устанавли вается в единичное состояние по единичному потенциалу инверсного выхода триггеров 23 приема команды. Прямой выход триггера 2k командного байта соединен с . информационным входом триггера 23 г риема команды и управляющим входом регистра 21 команд. По-единичному состоянию триггера 2 командного байта и стробирующему сигналу, поступающему через пятый вход блока 4 выделениякоманды, триггер 23 приема команды устанавливается в единичное состояние, а в регистр 21. команд принимается командный байт, поступающий через шестой вход блока Ц выделения команды на информационный вход регистра 21 команд. Установленный триггер 23 приема команды указывает на то, что команда принята в регистр 21 команд. Триггер 2 командного байта затем сбрасывается четвертым синхроимпульсом, поступающим на сбросовый вход последнего через четвертый вход блока k выделения команды. Для последующего определения момента приема в регистр 21 команд используется триггер 25 конца команды. Единичное состояние триггера 25 кЬнца команды, прямой выход которого соединен со сбросовым входом триггера 23 приема команды, сбрасывает последний. Таким образом устанавливается исходное состояние для приема следующей команды. Установка.триггера 25 конца команды определяется или самой командой, или регистром 2 данных. В пер вом случае триггер 25 конца команды устанавливается единичным потенц алом с третьего выхода дешифратора 26, на вход которого поступает код команды с выхода регистра 21 команд Второй случай имеет место, если ком да определяет, что следующие четыре байта должны передаться в регистр 2 данных, после ч.его триггер 25 кон ца команды будет установлен управля щим сигналом из регистра 2 данных, поступающим на первый вход триггера 25конца команды через второй вход блока выделения команды. Сброс тр гера 25 конца команды проис5содит по его второму входу единичным по тенциалом с инверсного выхода тригг ра 23 приема команды. Прием в регис 2 данных последующих четырех байтов происходит по управляющему сигналу второго выхода дешифратора 2б, который передается в регистр 2 данных через третий выход блока 4 выделени команды. Первый выход дешифратора 26через второй выход блока k выдел ния команды подается в блок 7 проверки и определения номера байта дл фиксации ошибки, если таковая будет обнаружена. Введенный в блок k выделения команды мультиплексор 22 используется для передачи байтов информации в процессор через информационный выход 8 устройства. Мультиплексор 22 рассчитан для одновременной пере дачи четырех байтов. На первый его информационный вход подается информация из регистра 2 данных по третьему входу блока k выделения команды, на второй - значение счетчика 52 байтов по первому входу блог ка 4 выделения команды, на третийбайт из .двигающего регистра 1 через блок 3 управления по шестому входу блока k выделения команды и на четвертый вход - байт команды из регистра 21 команд. Какая информация передается через мультиплексор 22, определяет управляющий сигнал из процессора, поступающий по управляющему входу 11 устройства. Если идет загрузка микропрограмм -в управляющую память, то в процессор информация передается из регистра 2 данных. В противном случае байты могут выдаваться в процессор из регистра 21 команд, сдвигающего регистра 1 и счетчика 52 ; байтов. Блок 5 анализа лишнего бита (фиг. 4) предназначен для приема информационных битов, их контроля на частоту следования и определения лишних (ошибочных) битов. Ьлок 5 анализа лишнего бита работает следующим образом. flo нулевому состоянию первого триггера.27, второго триггера 28 и по импульсам генератора 17, которые поступают на третий вход блока 5 анализа лишнего бита, на выходе второго элемента И Зб формируются импульсы. Эти импульсы поступают на ус.тановочный вход счетчика 31 импульсов и устанавливают его семь разрядов в единичное состояние. Вре менной бит с информационного входа 13 устройства поступает на первый вход первого триггера 27 и устанавливает его по единичному значению разрядов счетчика 31 импульсов и импульсам от генератора 17, поступающих на четвертый вход первого триггера 27. Единичное состояние первого триггера 27 разрешает прохождение импульсов от генератора Г/ через первый элемент И 35 :И второй элемент ИЛИ 33, поступающих на счетный вход счетчика 31 импульсов, который сбрасывается в ноль и его значение по каждому импульсу генератора 17 увеличивается на единицу, а затем управляет установкой и сбросом второго триггера 28 и сбросом первого триггера 27. Но нулевому значению счетчика 31 импульсов после окончания временного бита устанавливается триггер 30 проверки, единичное состояние которого определяет интервал, в котором не должно быть информационных битов, поступающих с пультового накопителя. Сбрасывается триггер 30 проверки инверсным выходом первого триггера 27. Когда счетчик 31 импульсов достигает значения 64, т.е. седьмой разряд становится равным единице, по импульсу генератора 17 и единичному состоянию riepBoro триггера 27 устанавливается второй триггер 28 и сразу же следующим импульсом генератора 17 при установленном седьмом разряде счетчика 31 импульсов первый триггер 27 сбрасывается. По сброшенному состоянию первого триггера 27 сбрасывается триггер 30 проверки. После установки второго триггера 28 на выходе третьего элемента И 37 формируется последовательность импульсов, повторяющая импульсы генератора 17, которая подается на второй вход второго элемента ИЛИ 33, так как после сброса первого триггера 27 импульсы, на ; первый вход второго.элемента ИЛИ 33 не поступают. Если за время, определяемое триггером 30 проверки, на ин формационном входе 13 устройства появится любой бит информации или поме ха, установится триггер 29 лишнего бита. Сбрасывается триггер 29 лишнег бита по импульсу сброса, поступающе му на первь|й вход блока 5 анализа ли него бита. К моменту сброса триггера 30 проверки блок 3 управления вырабатывает второй синхроимпульс, поступающий на первый вход пятого элемента И 39 через второй вход блока 5 анализа лишнего бита. Этот син роимпульс стробирует на пятом элемен те И 39 информационные или стартовы биты, которые, затем последовательно передаются в сдвигающий регистр 1 че рез второй, выход блока. Если в цикле установки триггера 19 стартового бита в момент второго синхроимпульса не будет принят бит. информации .{стоповый бит байта), на выходе четвертого элемента И 38 появится сигнал ошибки отсутствия стопового бита. Для этого прямой выход триггера 19 стартового бита через четвертый вход блока соединен с первым входом четвертого элемента И 38, на второй и третий вход которого заводятся соответственно второй синхроимпульс и выход элемента НЕ З. Ошибки нали.чия лишнего бита, и отсутствие стопового бита подаются на входы первого элемента ИЛИ 32. Присутствие одной из них формирует на выходе первого элемента ИЛИ 32 сигнал, который пе-редается через первый выход -блока в блок 6 повторного считывания. Блок 6 повторного считывания (фиг. 5) выполняет функции управлени пультовым накопителем в случае обнаружения ошибки при передаче информации и работает следующим образом. При обнаружении ошибок наличие лишнего бита или отсутствие стопового бита блоком 5 анализа лишнего бита сигнал ошибки поступает на первый вход первого элемента ИЛИ kk через четвертый вход блока 6 повторного считывания, а при обнаружении ошибок неверное .расположение байтов или превышение заданного количества байтов в секторе блоком 7 . проверки и определения номера байта сигнал ошибки поступает на второй вход первого элемента ИЛИ kk через второй вход блока. При этом на выходе первого элемента ИЛИ А формируется сигнал ошибки, который устанавливает триггер kQ повтора и увеличивает содержимое четырехразрядного счетчика 2 повторений на единицу, б начальном состоянии триг- гер kU повтора и счетчик повтот рений находится в нуле. Установка счетчика в ноль -роисходит сигналом сброса через сбросовый вход 12 устройства. Всякий раз, когда возникает ошибка, значение счетчика 42 повторений увеличивается на единицу. Если счетчик k2 повторений переполнен, на его выходе формируется единичный потенциал, если нет, то нулевой потенциал, который инвертируется на элементе НЕ 46, поступает на первый вход элемента И 43 как разрешающий сигнал, flo этому сигналу и единичному потенциалу, поЬтупающему на второй вход элемента И 43 .с выхода триггера 40 повтора, на выходе элемента И 43 формируется сигнал повторения. Сигнал повторения через первый управляющий выход 9 устройствапоступает в пультовой накопитель и инициирует в нем повторное считывание сектора. При этом синхронизатор 18 блока 3 управления формирует сигнал сброса, который сбрасывает триггер 40 повтора через первый вход блока 6 повторного считывания. Если при повторном считывании ошибка не обнаружена, считывание продолжается дальше. Если ошибка устойчивая, процесс повторяется до.:; переполнения счетчика 42 повторений. Сигнал переполнения на выходе счетчика 42 повторений запрещает через элемент НЕ 46 сигнал повторения на элементе И 43 и через второй элемент ИЛИ 45 устанавливает триггер 41 останова. Сигнал с выхода триггера 41 останова поступает через второй/управляющий выход 10 устройства в пультовой накопитель и останавливает его. Триггер 41 останова может быть установлен и по сигналу совпадения счета, сформированнрму в блоке 7 проверки и определения ,номера байта. Сигнал совпадения счета поступает на пер-. вый вход второго элемента ИЛИ 45 че|рез третий вход блока 6 повторного считывания. Сбрасывается триггер tl останова сигналам сброса из процессора через сбросовый вход 12 уст ройства. . Блок 7 проверки и определения номера байта (. фиг. 6) предназначен для контроля правильности расположе ния и подсчета количества байтов в секторе, считываемом с носителя пул тового накопителя. Блок работает следующим образом. После приема байта информации в сдвигающий регистр 1, управляющий сигнал из блока 3 управления поступает через третий вход блока 7 проверки и определения номера байта на счетный вход счетчика 52 байтов и увеличивает его значение на единицу. Счетчик 52 байтов рассчитан на 255 байтов, и в случае переполнения на его первом выходе форм руется сигнал, который устанавливает три г,г ер 51 ошибки счета, выход которого соединен с вторым входом элемента ИЛИ 7. На выходе элемента ИЛИ kl формируется сигнал ошибки, к торый через первый выход блока поступает в блок 6 повторного считывания. Как уже отмечалось выше, для кон ролен правильности расположения .байтов на носителе используется соответствующая кодировка третьего разряда командного байта, который срав нивается с первым разрядом счетчика 52 байтов. Для этого на первый вход двухвходового сумматора k по модулю два через пятый вход блока подается третий разряд сдвигающеГО регистра 1, а на второй вход первый разряд счетчика 52 байтов. . Если разряды не равны, на выходе Сумматора k по модулю два формиру ется сигнал, который поступает на второй вход элемента И 48. Если принятый в сдвигающий регистр 1 байт окажется командным байтом, то с первого выхода дешифратора 26 в блоке выделения команды на первый вход элемента И 48 поступает разрешающий потенциал. При этом на входе элемента И 48 формиру ется сигнал ошибки, который поступает на первый вход элемента ИЛИ 47 и дальше в блок 6 повторного считыв ния. Используя счетчик 52 байтов, мож но произвести останов при считывании информации с пультового накопит ЛЯ по любому номеру байта в секторе . Это позволяет визуально контролировать, помимо счетчика 52 байтов, содержимое всех регистров устройства. Для этого на первые входы восьмивходового сумматора 50 по модулю два подается значение переключателей из процессора через управляющий вход 11 устройства, а на вторые входы - значение разрядов счетчика 52 байтов. Как только счетчик 52 байтов досчитает до заданной величины, произойдет сравнение и на выходе cyMMafopa 50 по модулю два будет сформирован сигнал совпадения, который поступает в блок 6 повторного считывания для организации останова пультового накопителя. К процессорам, использующим микропрограммный принцип управления и перезагружаемую-управляющую память для хранения микропрограмм, пред ъявляются повышенные требования к достоверности загружаемых микропрограмм. Последующее функционирование этих процессоров базируется на. вве.-. денных микропрограммах, и предполагает их абсолютную правильность. Наличие развитой системы контроля в предлагаемом устройстве позволяет повысить достоверность микропрограмм, загружаемых в управляющую память процессора. Применение предлагаемого устройства обеспечивает правильность функционирования процесса и уменьшает время на поиск неисправностей. Применение, наряду с известным контролем по паритету, таких видов контроля, как контроль стопового бита, обнаружение лишнего бита, контроль четности байта в вводимом массиве информации повышает достоверность вводимых в процессор микропрограмм. Контроль лишнего бита позволяет контролировать скорость поступления информации с носителя пультового накопителя. Контроль четности байтов контролирует правильность расположения информации на носителе ПН в смысовом отношении. Если срабатывает данный вид контроля, то это означает, что нарушена правильная последовательность байтов на носителе или пропущен информационный байт.Контроль на наличие стопового бита позволяет .обнаружить смещение байтов.

записанных н носителе, а контроль количества считанных байтов позволя ет выявить, что число байтов, записанных в секторе на носителе пультового лакрпителя, .превышает заданную величину. Например, это может иметь место, когда дважды записан ОДИН и тот же байт. Введение блока повторного считывания, реализующего автоматическое многократное считывание (до 1i) раз) , в случае срабатывания контроля, позволяет загружать

а

микропрограммы, несмотря нд случайные ошибки..

Использование указанных специальных видов контроля позволяет контролировать скорость, правильную последовательность поступления и количество байтов, вводимых с пультового накопителяв процессор. Кроме , блок проверки и определения номера байта позволяет оперативно-.делать останов на любом байте вводимой информации, что повышает эффективность отладочных процедур.

fl

fut.l

5 «

i

t5

Г7

f(

/ff

.

.7

M

f

Iff

fui.2

if

«41

«tsl

Р чх

.

.f

«.

«

. k «N4

см

«VI

J9

1Ц).

м

11 Т

J 5

W

«;

ff

fia.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Экплуатационная надежность ИБМ-ЗбО | |||

| Кибернетический сб., вып.1/ М., Мир, 1965 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Каган Б | |||

| М | |||

| Электронные вычислительные машины и системы | |||

| М., Энергия, 1979, с | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Теплица | 1983 |

|

SU1258972A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| (S) | |||

Авторы

Даты

1983-03-30—Публикация

1981-04-22—Подача