Предлагаемое изобретение относится к области аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых устройствах - операционных усилителях, стабилизаторах напряжения, нормирующих преобразователях и т.п.

В современной микроэлектронике находят массовое применение неинвертирующие усилители тока [1-42] с включением биполярного (BJT) транзистора по схеме с общей базой или полевого транзистора с управляющим p-n переходом (JFET) и CMOS транзисторов по схеме с общим истоком. В структуре операционных усилителей данные схемотехнические решения называют также «перегнутыми» каскодами [1-42], которые реализуются по BJT [14-31], JFET [32-37], а также по CMOS [32-41] технологиям. Это одно из перспективных направлений аналоговой схемотехники, которое вошло во многие издания учебной литературы для вузов [42].

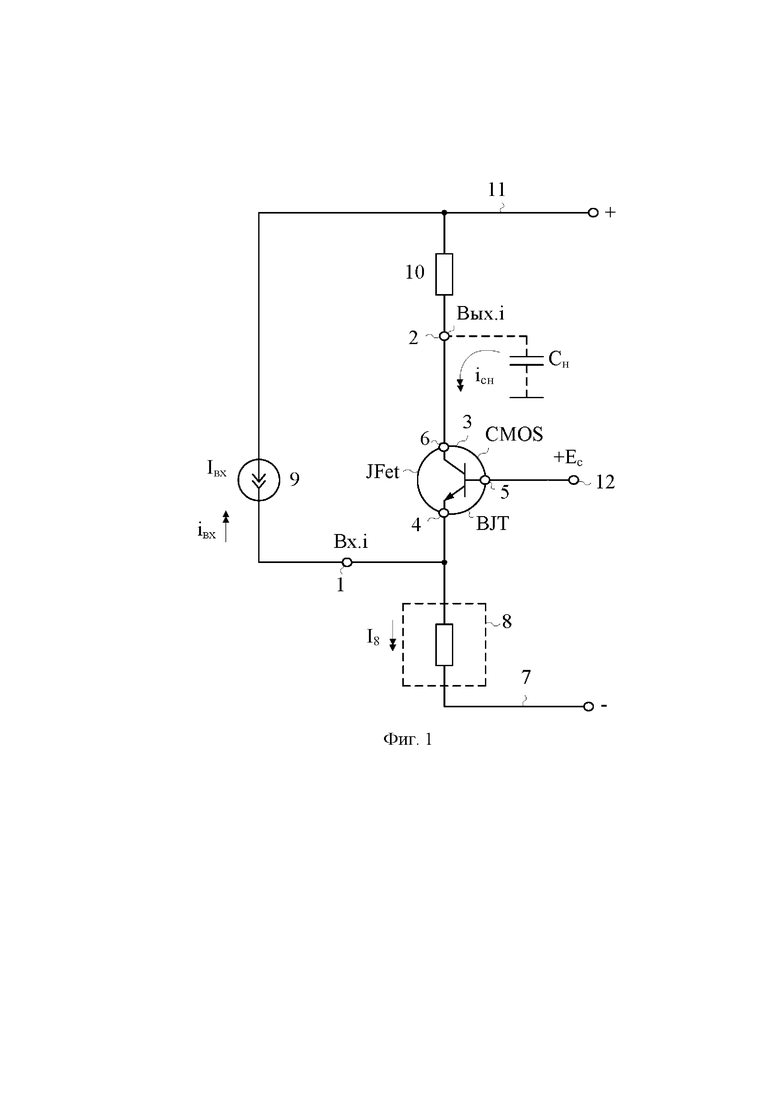

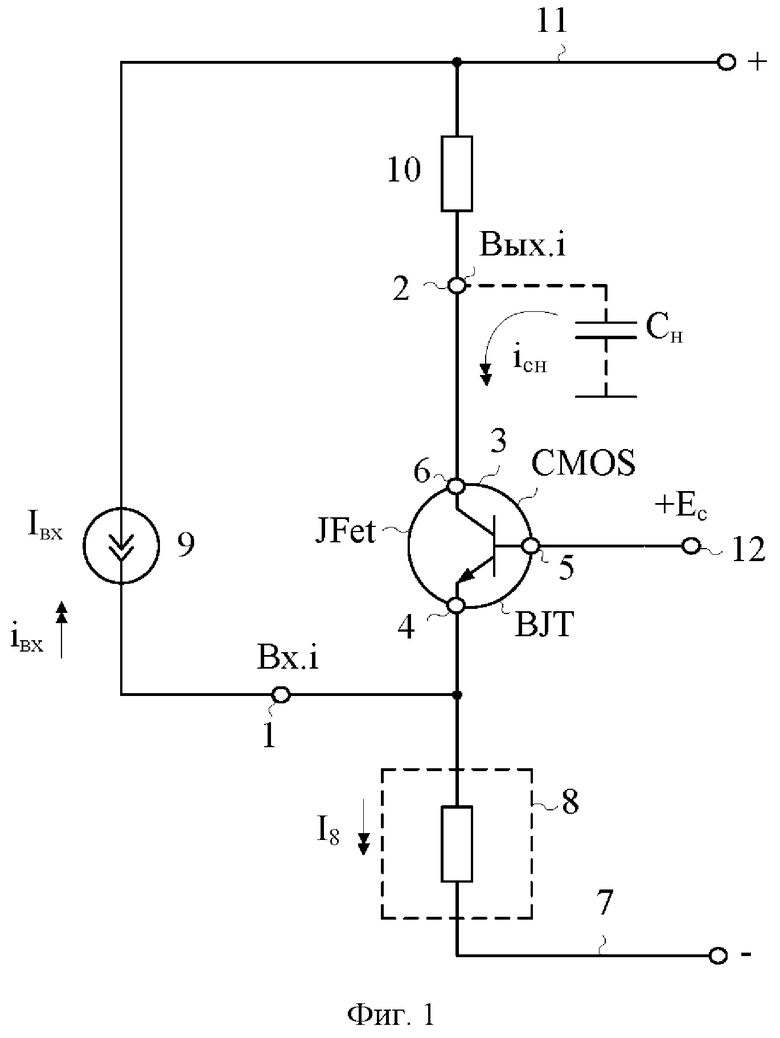

Ближайшим прототипом заявляемого устройства является неинвертирующий усилитель тока, представленный в учебном пособии «Основы электроники, радиотехники и связи: Учебное пособие для вузов /А.Д. Гуменюк, В.И. Журавлев, Ю.Ю. Мартюшев и др.; Под редакцией Г.Д. Петрухина. - М.: Горячая линия - Телеком, 2008. - 480 с.», рис. 8.27, С. 95, а также в патенте RU 2374760, фиг. 1, 2009 г. Он содержит (фиг. 1) токовый вход 1 и токовый выход 2 устройства, выходной транзисторный трехполюсник 3 с низкоомным 4 и высокоомным 5 входами, а также высокоомным выходом 6, соединенным с токовым выходом 2 устройства, первую 7 шину источника питания, токостабилизирующий двухполюсник 8, первый вывод которого связан с первой 7 шиной источника питания, источник входного тока 9, подключенный к токовому входу 1 устройства, цепь нагрузки 10, включенную между токовым выходом 2 устройства и второй 11 шиной источника питания, цепь смещения потенциалов 12, связанную с высокоомным входом 5 выходного транзисторного трехполюсника 3.

Существенный недостаток неинвертирующего усилителя тока - прототипа состоит в том, что он всегда работает в режиме класса «А», так как его выходной ток не может превышать статическое значение тока I8 токостабилизирующего двухполюсника 8. Это не позволяет реализовать на основе данной весьма популярной схемы цепи нелинейной коррекции переходных процессов, которые форсируют перезаряд емкости Cн в цепи нагрузки и тем самым повышают быстродействие устройств, в которых они применяются.

Основная задача предполагаемого изобретения состоит в создании условий, при которых максимально возможный выходной ток Iвых.max заявляемого устройства превышает в 5-10 раз статический ток I8 токостабилизирующего двухполюсника 8. Как следствие, заявляемое устройство, в отличие от прототипа, работает в режиме класса «АВ».

Поставленная задача достигается тем, что в неинвертирующем усилителе тока фиг. 1, содержащем токовый вход 1 и токовый выход 2 устройства, выходной транзисторный трехполюсник 3 с низкоомным 4 и высокоомным 5 входами, а также высокоомным выходом 6, соединенным с токовым выходом 2 устройства, первую 7 шину источника питания, токостабилизирующий двухполюсник 8, первый вывод которого связан с первой 7 шиной источника питания, источник входного тока 9, подключенный к токовому входу 1 устройства, цепь нагрузки 10, включенную между токовым выходом 2 устройства и второй 11 шиной источника питания, цепь смещения потенциалов 12, связанную с высокоомным входом 5 выходного транзисторного трехполюсника 3, предусмотрены новые элементы и связи - в схему введен дополнительный транзисторный трехполюсник 13 с низкоомным 14 и высокоомным 15 входами, а также высокоомным выходом 16, который согласован с первой 7 шиной источника питания, причем токовый вход 1 устройства связан со вторым выводом токостабилизирующего двухполюсника 8 через дополнительный резистор 17 и подключен к высокоомному входу 15 дополнительного транзисторного трехполюсника 13, а низкоомный вход 14 дополнительного трехполюсника 13 соединен с низкоомным 4 входом выходного транзисторного трехполюсника 3.

На фиг. 1 представлена схема неинвертирующего усилителя тока - прототипа, у которого выходной транзисторный трехполюсник 3 может быть выполнен на основе BJT, JFet или CMOS транзисторов. В технической литературе данный усилитель тока известен как схема включения с общей базой (для BJT) или с общим затвором (для JFet и CMOS транзисторов). Известно и другое наиболее популярное название схемы прототипа фиг.1 в структуре операционных усилителей - «перегнутый» каскод.

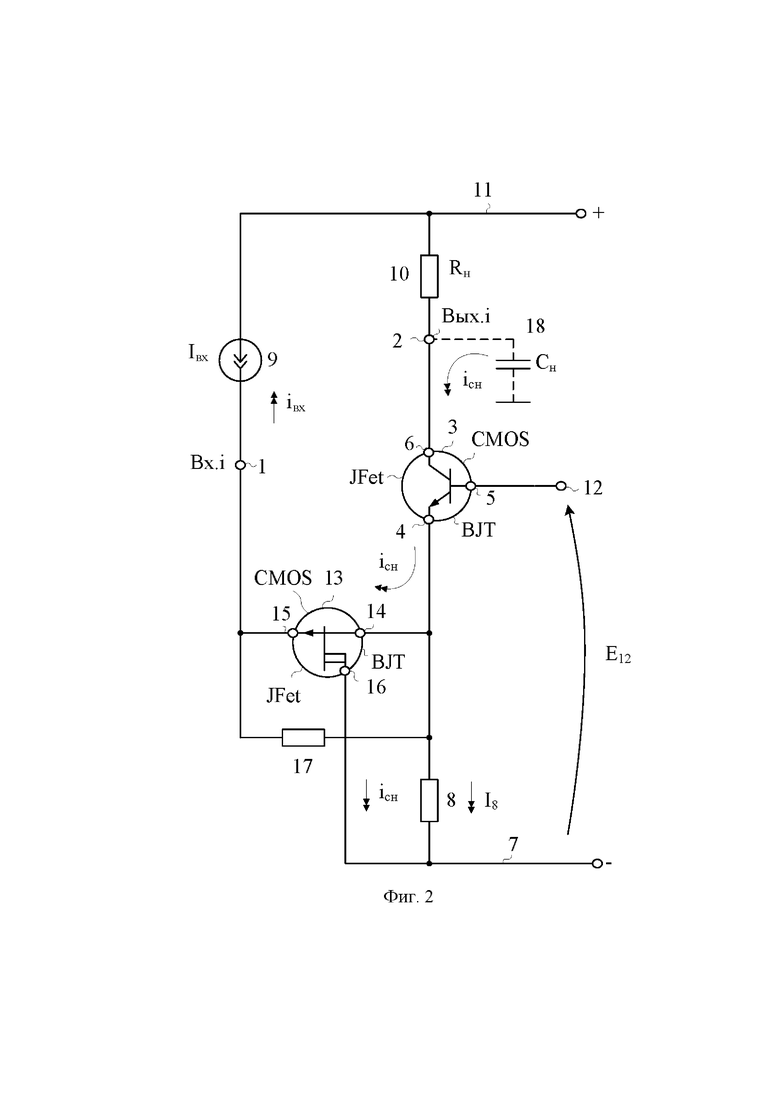

На фиг. 2 представлена схема заявляемого устройства в соответствии с п. 1, п. 2 и п. 3 формулы изобретения. При этом выходной транзисторный трехполюсник 3 и дополнительный транзисторный трехполюсник 13 могут в общем случае выполняться как на биполярных (BJT), так и на полевых (JFET, CMOS) транзисторах.

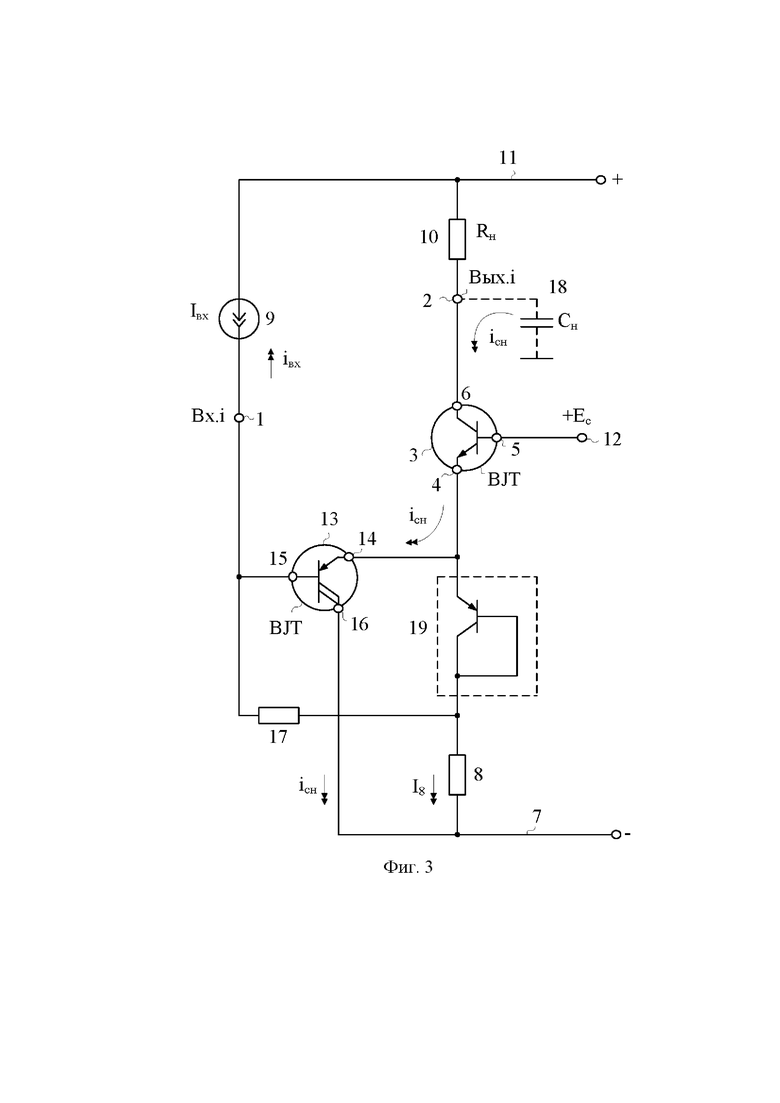

На фиг. 3 представлена схема заявляемого устройства в соответствии с п. 2 и п. 6 формулы изобретения для случая, когда выходной транзисторный трехполюсник 3, дополнительный транзисторный трехполюсник 13, а также цепь согласования потенциалов 19 выполнены на биполярных (BJT) транзисторах.

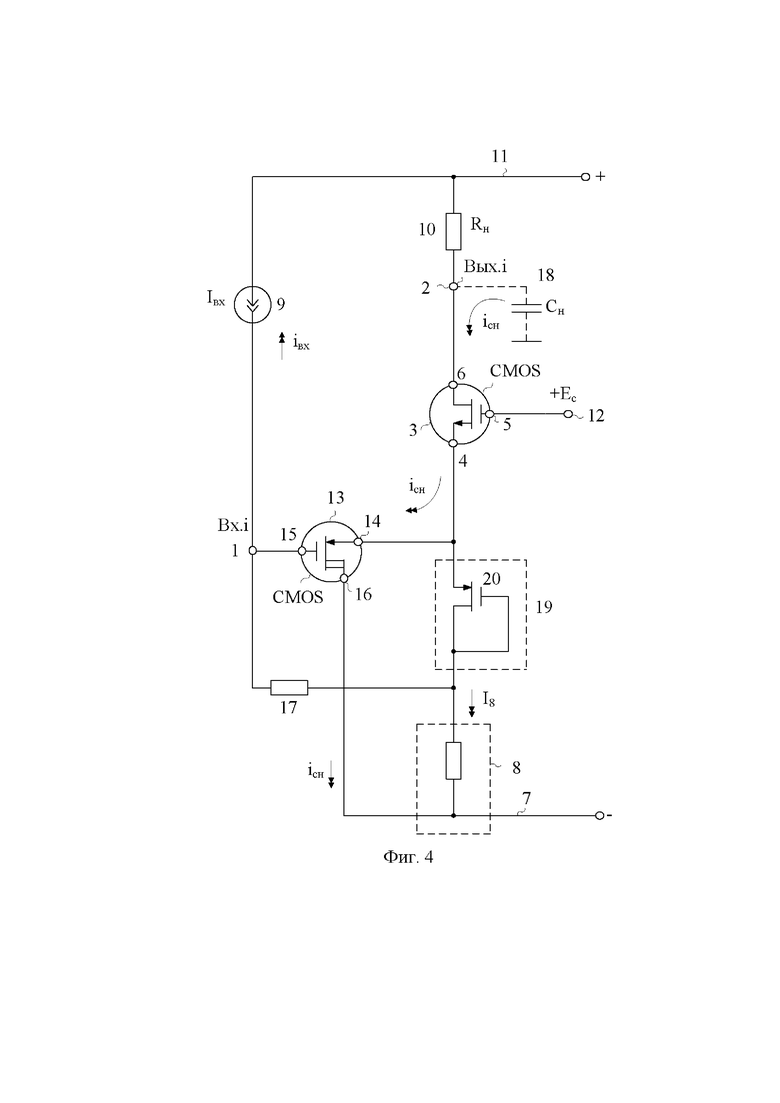

На фиг. 4 представлена схема заявляемого устройства в соответствии с п. 3, п. 4 и п. 7 формулы изобретения для случая, когда выходной транзисторный трехполюсник 3, дополнительный транзисторный трехполюсник 13 выполняются на CMOS полевых транзисторах с изолированным затвором. Кроме этого, здесь цепь согласования потенциалов 19 реализована в частном случае на CMOS полевом транзисторе 20 с изолированным затвором.

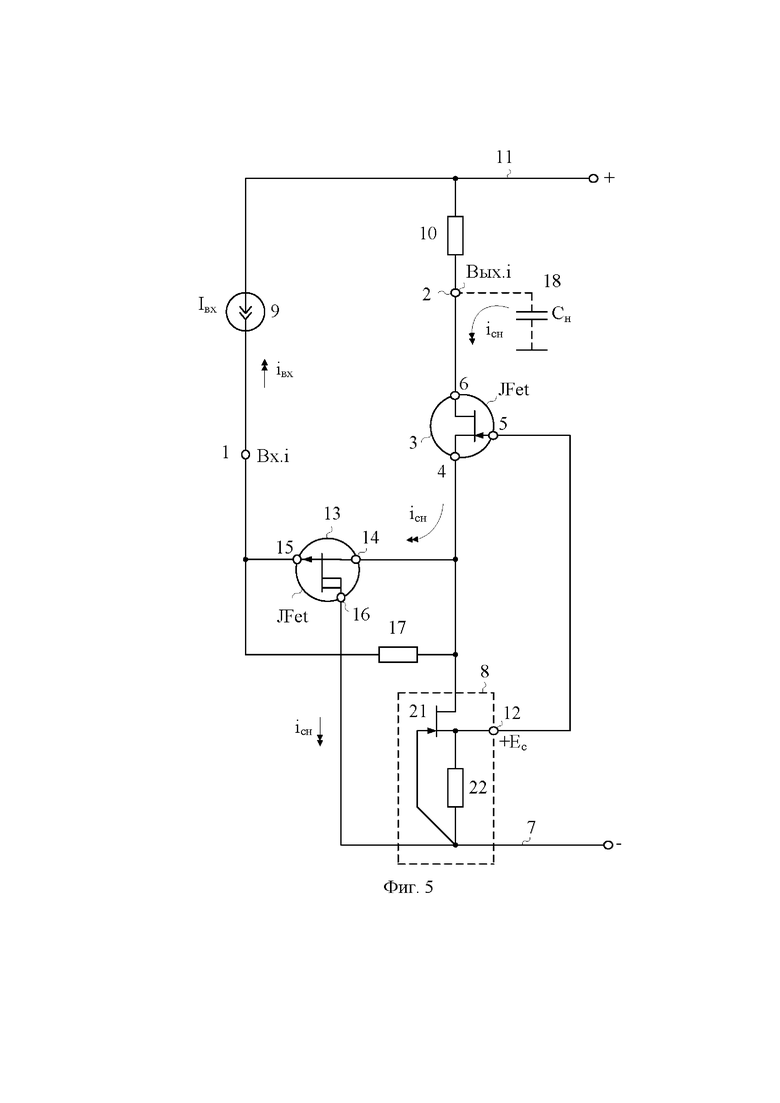

На фиг. 5 представлена схема заявляемого устройства в соответствии с п. 3, п. 5, п. 8 формулы изобретения для случая, когда выходной транзисторный трехполюсник 3, дополнительный транзисторный трехполюсник 13, а также токостабилизирующий двухполюсник 8 выполняются на полевых транзисторах с управляющим p-n переходом.

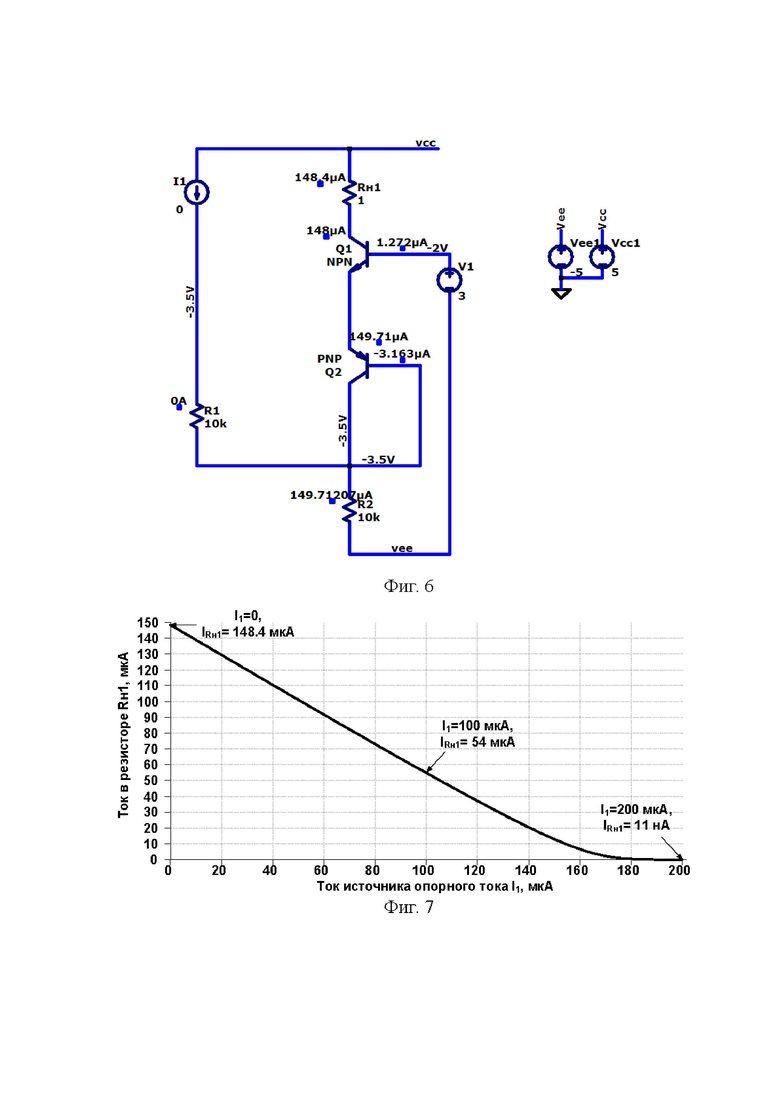

На фиг. 6 приведен статический режим усилителя-прототипа фиг.1 в среде компьютерного моделирования LTSpice при его выполнении на биполярном транзисторе Q1 (t=27°C, I1=0 А, R1=R2=10 кОм, Rн1=1 Ом, V1=3 В).

На фиг. 7 приведена зависимость выходного тока усилителя-прототипа фиг. 6 от входного тока Iвх=I1 при t=27°C, R1=R2=10 кОм, Rн1=1 Ом, V1=3 В. Данный график показывает, что максимальный выходной ток схемы фиг. 6 не превышает статический ток в токостабилизирующем двухполюснике 8. То еесть известная схема усилителя-прототипа работает в режиме класса «А».

На фиг. 8 приведен статический режим заявляемого усилителя тока фиг.3 в среде компьютерного моделирования LTSpice при t=27°C, I1=0 А, R1=R2=10 кОм, Rн1=1 Ом, V1=3 В и количестве параллельно включенных транзисторов Q3 N=5 шт.

На фиг. 9 приведена зависимость выходного тока заявляемого усилителя фиг. 8 от входного тока I1=Iвх.

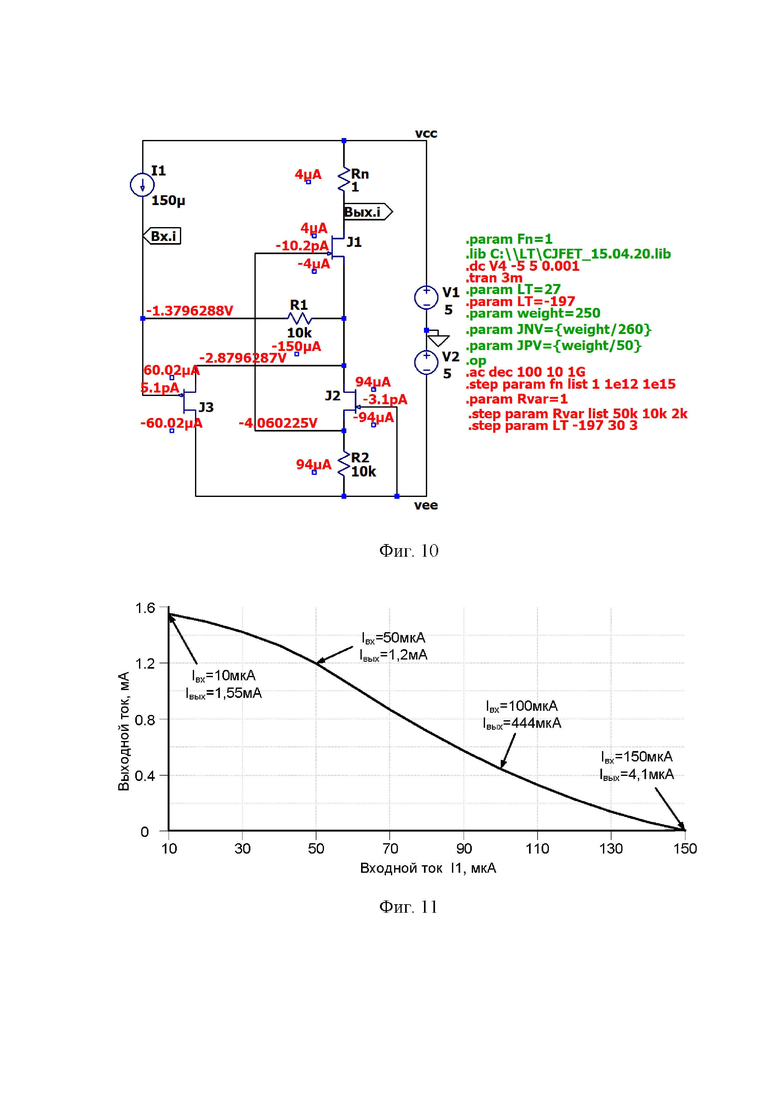

На фиг. 10 приведен статический режим заявляемого усилителя тока фиг.5 в среде компьютерного моделирования LTSpice на моделях CJFet транзисторов (ОАО «Интеграл» г. Минск, Беларусь) при 27°С, R1=R=10кОм, Rn=1Ом, источнике входного тока Iвх =I1=150мкА.

На фиг. 11 приведена зависимость выходного тока заявляемого усилителя тока фиг. 10 от входного тока Iвх=I1. Данный график показывает, что максимальный выходной ток Iвых.max усилителя тока фиг. 10 более чем в 10 раз превышает статический ток токостабилизирующего двухполюсника 8. Таким образом, неинвертирующий усилитель тока фиг. 10 работает в режиме класса «АВ».

Неинвертирующий усилитель тока класса «АВ» фиг. 2 содержит токовый вход 1 и токовый выход 2 устройства, выходной транзисторный трехполюсник 3 с низкоомным 4 и высокоомным 5 входами, а также высокоомным выходом 6, соединенным с токовым выходом 2 устройства, первую 7 шину источника питания, токостабилизирующий двухполюсник 8, первый вывод которого связан с первой 7 шиной источника питания, источник входного тока 9, подключенный к токовому входу 1 устройства, цепь нагрузки 10, включенную между токовым выходом 2 устройства и второй 11 шиной источника питания, цепь смещения потенциалов 12, связанную с высокоомным входом 5 выходного транзисторного трехполюсника 3. В схему введен дополнительный транзисторный трехполюсник 13 с низкоомным 14 и высокоомным 15 входами, а также высокоомным выходом 16, который согласован с первой 7 шиной источника питания, причем токовый вход 1 устройства связан со вторым выводом токостабилизирующего двухполюсника 8 через дополнительный резистор 17 и подключен к высокоомному входу 15 дополнительного транзисторного трехполюсника 13, а низкоомный вход 14 дополнительного трехполюсника 13 соединен с низкоомным 4 входом выходного транзисторного трехполюсника 3.

На фиг. 2 конденсатор 18 с емкостью Сн моделирует емкостную составляющую цепи нагрузки, которая подключается к токовому выходу устройства 2.

На фиг. 2, в соответствии с п. 2 формулы изобретения, в качестве выходного транзисторного трехполюсника 3 используется биполярный транзистор, эмиттер которого соответствует низкоомному 4 входу выходного транзисторного трехполюсника 3, база - высокоомному 5 входу выходного транзисторного трехполюсника 3, а коллектор - высокоомному выходу 6 выходного транзисторного трехполюсника 3.

Кроме этого, на фиг. 2, в соответствии с п. 5 формулы изобретения, в качестве дополнительного транзисторного трехполюсника 13 используется полевой транзистор с управляющим p-n переходом, исток которого соответствует низкоомному 14 входу дополнительного транзисторного трехполюсника 13, затвор - высокоомному 15 входу дополнительного транзисторного трехполюсника 13, а сток - высокоомному выходу 16 дополнительного транзисторного трехполюсника 13.

На фиг. 3, в соответствии с п. 6 формулы изобретения, в качестве дополнительного транзисторного трехполюсника 13 используется биполярный транзистор, эмиттер которого соответствует низкоомному 14 входу дополнительного транзисторного трехполюсника 13, база - высокоомному 15 входу дополнительного транзисторного трехполюсника 13, а коллектор - высокоомному выходу 16 дополнительного транзисторного трехполюсника 13, причем общий узел дополнительного резистора 17 и токостабилизирующего двухполюсника 8 связан с низкоомным входом 4 выходного транзисторного трехполюсника 3 через цепь согласования потенциалов 19, реализованную в частном случае на биполярном транзисторе.

На фиг. 4, в соответствии с п. 4 формулы изобретения, в качестве выходного транзисторного трехполюсника 3 используется CMOS полевой транзистор с изолированным затвором, исток которого соответствует низкоомному 4 входу выходного транзисторного трехполюсника 3, затвор - высокоомному 5 входу выходного транзисторного трехполюсника 3, а сток - высокоомному выходу 6 выходного транзисторного трехполюсника 3.

Кроме этого, на фиг. 4, в соответствии с п. 7 формулы изобретения, в качестве дополнительного транзисторного трехполюсника 13 используется полевой CMOS транзистор с изолированным затвором, исток которого соответствует низкоомному 14 входу дополнительного транзисторного трехполюсника 13, затвор - высокоомному 15 входу дополнительного транзисторного трехполюсника 13, а сток - высокоомному выходу 16 дополнительного транзисторного трехполюсника 13, причем общий узел дополнительного резистора 17 и токостабилизирующего двухполюсника 8 связан с низкоомным входом 4 выходного транзисторного трехполюсника 3 через цепь согласования потенциалов 19, реализованную в частном случае на CMOS транзисторе 20.

На фиг. 5, в соответствии с п. 3 формулы изобретения, в качестве выходного транзисторного трехполюсника 3 используется полевой транзистор с управляющим p-n переходом, исток которого соответствует низкоомному 4 входу выходного транзисторного трехполюсника 3, затвор - высокоомному 5 входу выходного транзисторного трехполюсника 3, а сток - высокоомному выходу 6 выходного транзисторного трехполюсника 3.

Кроме этого, на фиг. 5, в соответствии с п. 8 формулы изобретения, токостабилизирующий двухполюсник 8 выполнен на вспомогательном полевом транзисторе с управляющим p-n переходом 21, затвор которого соединен с первой 7 шиной источника питания и через первый 22 вспомогательный резистор связан с истоком вспомогательного полевого транзистора 21, причем в качестве цепи смещения потенциалов 12 используется исток вспомогательного полевого транзистора с управляющим p-n переходом 21, а в качестве выходного транзисторного трехполюсника 3 и дополнительного транзисторного трехполюсника 13 используются полевые транзисторы с управляющим p-n переходом.

Рассмотрим работу неинвертирующего усилителя тока класса «АВ», показанного на фиг. 2.

Основная особенность схемы УТ фиг. 2 состоит в создании за счет введения новых элементов и связей между ними условий, при которых уменьшение тока источника входного тока 9 от начального статического значения до нуля приводит к формированию дополнительного тока по низкоомному входу 4 выходного транзисторного трехполюсника 3. Это обеспечивается введением дополнительного транзисторного трехполюсника 13. В частном случае в схеме фиг. 2 возможны любые сочетания BJT, JFET и CMOS транзисторов, что обеспечивается конкретной реализацией выходного транзисторного трехполюсника 3 и дополнительного транзисторного трехполюсника 13 с использованием следующих сочетаний транзисторов: BJT-BJT, JFET-BJT, CMOS-BJT, JFET-BJT, JFET-JFET, JFET-CMOS, BJT-CMOS, CMOS-CMOS, CMOS-JFET.

Статический режим неинвертирующего усилителя тока фиг. 3 устанавливается цепью смещения потенциалов 12 и токостабилизирующим двухполюсником 8, в качестве которого могут использоваться как резисторы, так и специальные транзисторные источники опорного тока.

При максимальных значениях входного тока (Iвх.max) Iвх = Iвх.max > I8 биполярный транзистор выходного транзисторного трехполюсника 3 заперт по цепи эмиттера. За счет выбора сопротивления дополнительного резистора 17 в отсечке находится также и биполярный транзистор в структуре выходного транзисторного трехполюсника 3.

В частных случаях функции источника входного тока Iвх может выполнять дифференциальный каскад (на схеме не показан), выходной ток которого зависит от входного дифференциального напряжения.

При уменьшении входного тока Iвх уменьшается падение напряжение на дополнительном резисторе 17, что приводит к переходу в активный режим биполярного транзистора в структуре транзисторного трехполюсника 13 и появлению дополнительного тока, который передается в низкоомный вход 4 выходного транзисторного трехполюсника 3, вызывая увеличение его эмиттерного и, следовательно, выходного тока устройства. Как только Iвх примет нулевые значения, эмиттерный ток биполярного транзистора по низкоомному входу 14 дополнительного трехполюсника 13 принимает максимальные значения, что приводит (как это следует из фиг. 9) к увеличению выходного тока заявляемого устройства. При этом численные значения Iвых.max зависят от сопротивления дополнительного резистора 17 (R1) и могут изменяться (по усмотрению разработчика) за счет увеличения числа параллельно включенных транзисторов в дополнительном транзисторном трехполюснике 13, а также применения BJT с повышенным коэффициентом усиления по току базы.

Цепь согласования потенциалов 19 необходима только для биполярных транзисторов в структуре дополнительного транзисторного трехполюсника 13.

В схеме неинвертирующего усилителя тока фиг. 5 на JFET транзисторах и его компьютерной модели на фиг. 10 закрытое состояние дополнительного транзисторного трехполюсника 13 (транзистор J3) обеспечивается выбором сопротивления резистора R1 (17). При этом уменьшение входного тока Iвх=I1 устройства приводит к «открыванию» транзистора J3, который создает по цепи истока дополнительный ток истока выходного транзисторного трехполюсника 3 (J1), и как следствие увеличивает выходной ток устройства.

Как следует из графика фиг. 11, максимальный выходной ток неинвертирующего усилителя тока фиг. 10 (при Iвх=0) более чем на порядок превышает статический ток токостабилизирующего двухполюсника 8, что характерно для режима класса «АВ».

Работа схемы неинвертирующего усилителя тока на CMOS транзисторах (фиг. 4) ничем не отличается от работы схемы на BJT (фиг. 3). Для получения больших выходных токов в токовом выходе устройства 2 CMOS транзистор в структуре дополнительного транзисторного трехполюсника 13 может содержать несколько элементарных CMOS (или соответствующим образом выбранные геометрические размеры каналов).

Наиболее ярко достоинства заявляемого устройства проявляется при импульсном изменении входного тока Iвх=I1 от максимального значения до нуля, при котором в цепи токового выхода устройства 2 формируются значительные токи, формирующие перезаряд емкости нагрузки 18. Это повышает быстродействие различных аналоговых устройств, в которых используется предлагаемый перегнутый каскод (стабилизаторов напряжения, операционных усилителей, буферных усилителей, СВЧ транзисторных каскадов и др.).

Предлагаемый усилитель тока работает в режиме класса «АВ» и может быть рекомендован для практического использования в быстродействующих аналоговых устройствах, в т.ч. для космического приборостроения и физики высоких энергий.

Таким образом, рассмотренный неинвертирующий усилитель тока имеет существенные преимущества в сравнении с усилителем тока - прототипом.

ОСНОВНОЙ БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. А.с. СССР 711665, 1980 г.

2. Патент US 3.500.220, 1970 г.

3. Патент US 3.972.003, 1976 г.

4. Патент US 4.277.756, 1981 г.

5. Патентная заявка US 2005/0218994, fig. 3b, 2005 г.

6. Патент US 4.887.047, 1989 г.

7. Патент RU 2460206, fig. 4, fig. 1, 2011 г.

8. Патент FR 2337969, 1977 г.

9. Патент ФРГ (DE) 2720614, 1978 г.

10. Патент ES 2079397, fig. 9, 1996 г.

11. Патентная заявка US 2008/0018403, fig. 4, 2008 г.

12. Патент RU 2374760, fig. 1, 2009 г.

13. Патент SU 1529410, 1989 г.

ДОПОЛНИТЕЛЬНЫЙ БИБЛИОГРАФИЧЕСКИЙ СПИСОК

Перегнутые каскоды на BJT

14. Патент США № 5.420.540, 1995 г.

15. Патент США № 5.323.121, 1994 г.

16. Патент США № 4.293.824, 1981 г.

17. Патент США № 4.406.990, 1983 г.

18. Патент РФ 2592429, 2016 г.

19. Патент США 4.390.850, 1983 г.

20. Патент США № 5.952.882, 1999 г.

21. Патент US 5.323.121, 1994 г.

22. Патент РФ № 2615070, 2017 г.

23. Патент США № 4.406.990, 1983 г., Fig. 6

24. Патент США № 7.215.200, 2007 г. Fig. 6

25. Патент США № 5.963.085, 1999 г.

26. Патент РФ № 2513482, 2014 г.

27. Патент РФ № 2595926, 2016 г.

28. Патент РФ № 2668968, 2018 г.

29. Патент РФ № 2684500, 2019 г., Fig. 1, Fig. 2

30. Патент РФ № 2319291, 2008 г.

31. Close J. P., Santos F. A JFET input single supply operational amplifier with rail-to-rail output //IEEE Bipolar Circuits and Technology Meeting. - 1993. - pp. 149-150.

Перегнутые каскоды на JFET

32. Dimitri Danyuk "Linear Integrated Systems Headphone Amplifier Evaluation Board", Linear Integrated Systems, p. 1-17. URL: http://www.linearsystems.com/lsdata/others/Headphone_Amplifier_Evaluation_Board.pdf

33. Патент США № 6.750.715, 2004 г.

34. Патент США № 6.714.076, 2004 г.

35. Патент РФ № 2624565, 2017 г.

36. Патент РФ № 2621286, 2017 г.

37. Prokopenko N. N., Pakhomov I. V., Zhuk A. A. Low temperature and radiation resistant JFET differential amplifiers circuits synthesis with increased common-mode rejection ratio // IOP Conference Series: Materials Science and Engineering. - IOP Publishing, 2020. - Т. 862. - №. 3. - С. 032109.

Перегнутые каскоды на CMOS

38. Патент США № 6.825.721, 2004 г.

39. Патент США № 6.788.143, 2004 г.

40. Патент США № 7.570.113, 2009 г.

41. Shor J. S., Luria K. Miniaturized BJT-based thermal sensor for microprocessors in 32-and 22-nm technologies //IEEE journal of solid-state circuits. - 2013. - Т. 48. - №. 11. - С. 2860-2867.

Учебная литература

42. Основы электроники, радиотехники и связи: Учебное пособие для вузов /А.Д. Гуменюк, В.И. Журавлев, Ю.Ю. Мартюшев и др.; Под редакцией Г.Д. Петрухина. - М.: Горячая линия - Телеком, 2008. - 480 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С «ПЕРЕГНУТЫМ» КАСКОДОМ КЛАССА АВ | 2022 |

|

RU2786512C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ С ТОКОВЫМ ВЫХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2710298C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ТОКОВОЕ ЗЕРКАЛО НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2720557C1 |

| Безрезистивный арсенид-галлиевый дифференциальный каскад и операционный усилитель на его основе с малым напряжением смещения нуля | 2023 |

|

RU2815912C1 |

Предлагаемое изобретение относится к области аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых устройствах – операционных усилителях, стабилизаторах напряжения, нормирующих преобразователях и т.п. Технический результат: повышение быстродействия устройства за счет создания условий, при которых максимально возможный выходной ток Iвых.max заявляемого устройства превышает в 5-10 раз статический ток I8 токостабилизирующего двухполюсника 8. Как следствие, заявляемое устройство, в отличие от прототипа, работает в режиме класса «АВ». Неинвертирующий усилитель тока класса «АВ» содержит токовый вход (1) и токовый выход (2) устройства, выходной транзисторный трехполюсник (3) с низкоомным (4) и высокоомным (5) входами, а также высокоомным выходом (6), соединенным с токовым выходом (2) устройства, первую (7) шину источника питания, токостабилизирующий двухполюсник (8), первый вывод которого связан с первой (7) шиной источника питания, источник входного тока (9), подключенный к токовому входу (1) устройства, цепь нагрузки (10), включенную между токовым выходом (2) устройства и второй (11) шиной источника питания, цепь смещения потенциалов (12), связанную с высокоомным входом (5) выходного транзисторного трехполюсника (3). В схему введен дополнительный транзисторный трехполюсник (13) с низкоомным (14) и высокоомным (15) входами, а также высокоомным выходом (16), который согласован с первой (7) шиной источника питания. Токовый вход (1) устройства связан со вторым выводом токостабилизирующего двухполюсника (8) через дополнительный резистор (17) и подключен к высокоомному входу (15) дополнительного транзисторного трехполюсника (13), а низкоомный вход (14) дополнительного трехполюсника (13) соединен с низкоомным (4) входом выходного транзисторного трехполюсника (3). 7 з.п. ф-лы, 11 ил.

1. Неинвертирующий усилитель тока класса «АВ», содержащий токовый вход (1) и токовый выход (2) устройства, выходной транзисторный трехполюсник (3) с низкоомным (4) и высокоомным (5) входами, а также высокоомным выходом (6), соединенным с токовым выходом (2) устройства, первую (7) шину источника питания, токостабилизирующий двухполюсник (8), первый вывод которого связан с первой (7) шиной источника питания, источник входного тока (9), подключенный к токовому входу (1) устройства, цепь нагрузки (10), включенную между токовым выходом (2) устройства и второй (11) шиной источника питания, цепь смещения потенциалов (12), связанную с высокоомным входом (5) выходного транзисторного трехполюсника (3), отличающийся тем, что в схему введен дополнительный транзисторный трехполюсник (13) с низкоомным (14) и высокоомным (15) входами, а также высокоомным выходом (16), который согласован с первой (7) шиной источника питания, причем токовый вход (1) устройства связан со вторым выводом токостабилизирующего двухполюсника (8) через дополнительный резистор (17) и подключен к высокоомному входу (15) дополнительного транзисторного трехполюсника (13), а низкоомный вход (14) дополнительного трехполюсника (13) соединен с низкоомным (4) входом выходного транзисторного трехполюсника (3).

2. Неинвертирующий усилитель тока класса «АВ» по п.1, отличающийся тем, что в качестве выходного транзисторного трехполюсника (3) используется биполярный транзистор, эмиттер которого соответствует низкоомному (4) входу выходного транзисторного трехполюсника (3), база – высокоомному (5) входу выходного транзисторного трехполюсника (3), а коллектор – высокоомному выходу (6) выходного транзисторного трехполюсника (3).

3. Неинвертирующий усилитель тока класса «АВ» по п.1, отличающийся тем, что в качестве выходного транзисторного трехполюсника (3) используется полевой транзистор с управляющим p-n переходом, исток которого соответствует низкоомному (4) входу выходного транзисторного трехполюсника (3), затвор – высокоомному (5) входу выходного транзисторного трехполюсника (3), а сток – высокоомному выходу (6) выходного транзисторного трехполюсника (3).

4. Неинвертирующий усилитель тока класса «АВ» по п.1, отличающийся тем, что в качестве выходного транзисторного трехполюсника (3) используется CMOS полевой транзистор с изолированным затвором, исток которого соответствует низкоомному (4) входу выходного транзисторного трехполюсника (3), затвор – высокоомному (5) входу выходного транзисторного трехполюсника (3), а сток – высокоомному выходу (6) выходного транзисторного трехполюсника (3).

5. Неинвертирующий усилитель тока класса «АВ» по п.1, отличающийся тем, что в качестве дополнительного транзисторного трехполюсника (13) используется полевой транзистор с управляющим p-n переходом, исток которого соответствует низкоомному (14) входу дополнительного транзисторного трехполюсника (13), затвор – высокоомному (15) входу дополнительного транзисторного трехполюсника (13), а сток – высокоомному выходу (16) дополнительного транзисторного трехполюсника (13).

6. Неинвертирующий усилитель тока класса «АВ» по п.1, отличающийся тем, что в качестве дополнительного транзисторного трехполюсника (13) используется биполярный транзистор, эмиттер которого соответствует низкоомному (14) входу дополнительного транзисторного трехполюсника (13), база – высокоомному (15) входу дополнительного транзисторного трехполюсника (13), а коллектор – высокоомному выходу (16) дополнительного транзисторного трехполюсника (13), причем общий узел дополнительного резистора (17) и токостабилизирующего двухполюсника (8) связан с низкоомным входом (4) выходного транзисторного трехполюсника (3) через цепь согласования потенциалов (19), реализованную в частном случае на биполярном транзисторе.

7. Неинвертирующий усилитель тока класса «АВ» по п.1, отличающийся тем, что в качестве дополнительного транзисторного трехполюсника (13) используется полевой CMOS транзистор с изолированным затвором, исток которого соответствует низкоомному (14) входу дополнительного транзисторного трехполюсника (13), затвор – высокоомному (15) входу дополнительного транзисторного трехполюсника (13), а сток – высокоомному выходу (16) дополнительного транзисторного трехполюсника (13), причем общий узел дополнительного резистора (17) и токостабилизирующего двухполюсника (8) связан с низкоомным входом (4) выходного транзисторного трехполюсника (3) через цепь согласования потенциалов (19), реализованную в частном случае на CMOS транзисторе (20).

8. Неинвертирующий усилитель тока класса «АВ» по п.1, отличающийся тем, что токостабилизирующий двухполюсник (8) выполнен на вспомогательном полевом транзисторе с управляющим p-n переходом (21), затвор которого соединен с первой (7) шиной источника питания и через первый (22) вспомогательный резистор связан с истоком вспомогательного полевого транзистора (21), причем в качестве цепи смещения потенциалов (12) используется исток вспомогательного полевого транзистора с управляющим p-n переходом (21), а в качестве выходного транзисторного трехполюсника (3) и дополнительного транзисторного трехполюсника (13) используются полевые транзисторы с управляющим p-n переходом.

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374760C1 |

| WO 2006095416 A1, 14.09.2006 | |||

| УСИЛИТЕЛЬ ТОКА | 1991 |

|

RU2020729C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ НЕИНВЕРТИРУЮЩЕГО УСИЛИТЕЛЯ ТОКА | 2012 |

|

RU2488955C1 |

| Иммунобиологическое средство и способ его использования для индукции специфического иммунитета против вируса тяжелого острого респираторного синдрома SARS-CoV-2 (варианты) | 2020 |

|

RU2720614C1 |

| Усилитель тока | 1987 |

|

SU1480095A1 |

| Повторитель тока | 1987 |

|

SU1529410A1 |

Авторы

Даты

2022-11-08—Публикация

2022-05-06—Подача