Область техники, к которой относится изобретение

Настоящее изобретение относится к полупроводниковому запоминающему устройству с последовательным доступом и касается способа управления записью данных в полупроводниковое запоминающее устройство с последовательным доступом.

Уровень техники

В качестве запоминающих устройств в различном электронном оборудовании широко используют перезаписываемые полупроводниковые запоминающие устройства, такие как электрически стираемое программируемое ПЗУ (EEPROM), флэш-ПЗУ (flash ROM) и т. п. В электронных устройствах возможности полупроводникового запоминающего устройства такого типа не ограничиваются записью входных данных поверх запомненных ранее, когда входные данные удовлетворяют заранее установленным для них условиям; в некоторых случаях эти полупроводниковые запоминающие устройства желательно использовать с условиями, которые ограничивают запись входных данных поверх запомненных ранее, когда эти данные не удовлетворяют указанным условиям для данных. Например, указанные условия могут включать в себя: «выполнение записи только в том случае, если данные для записи больше данных, которые записаны в полупроводниковом запоминающем устройстве (далее их называют «данные, подлежащие перезаписи»)» или условие «выполнять запись только в том случае, если данные для записи меньше данных, подлежащих перезаписи».

Однако в стандартных перезаписываемых полупроводниковых запоминающих устройствах нет системы, которая бы ограничивала перезапись данных, и поскольку при выполнении установленной последовательности для записи данных можно осуществлять запись поверх ранее запомненных данных, то ввести условия на перезапись (например, вышеописанные условия) не представляется возможным.

Заметим, что в качестве технологий для управления записью данных в запоминающее устройство применяют известную технологию, предполагающую использование для запоминающего устройства внешнего для него устройства предотвращения записи, и известную технологию для предотвращения записи в область хранения данных, когда в запоминающее устройство записывают данные, указывающие на запрещение записи в область хранения данных с адресом за конкретной областью хранения данных в запоминающем устройстве.

Кроме того, известны полупроводниковые запоминающие устройства, которые позволяют осуществлять только последовательный доступ к простейшим элементам данных матрицы памяти, например EEPROM. Такого рода полупроводниковое запоминающее устройство относительно дешево, и поэтому его используют в качестве запоминающего устройства для хранения данных, относящихся к оставшемуся объему или потребленному объему потребительских товаров. Объем потребительских товаров сокращается по мере их использования, так что, когда данные, используемые для обновления, в частности данные, записанные в матрицу памяти, представляют собой данные, относящиеся к потребленному объему, значение записываемых данных должно быть больше значения уже существующих данных, запомненных в матрице памяти. В то же время, когда данные, записанные в матрице памяти, представляют собой данные, относящиеся к оставшемуся объему, значение записываемых данных должно быть меньше значения уже существующих данных, запомненных в матрице данных.

Сущность изобретения

Однако встречаются, например, случаи, когда происходят изменения в данных во время пересылки данных, вводимых в полупроводниковое запоминающее устройство, и в таком случае даже при правильной перезаписи данных в полупроводниковом запоминающем устройстве в нем окажутся данные с ошибками. В частности, например, когда данные характеризуются их возрастанием, существует опасность того, что в полупроводниковое запоминающее устройство будут записаны данные, значение которых меньше значения существующих данных. Здесь при использовании данных, относящихся к оставшемуся объему или потребленному объему потребительских товаров, для уменьшения или предотвращения ущерба или проблем с устройством, которое использует потребительские товары, когда данные, относящиеся к оставшемуся объему или потребленному объему потребительских товаров, которые изначально характеризовались возрастанием или убыванием, начинают изменяться в противоположном направлении, с устройством, использующим эти потребительские товары, возникают проблемы.

Настоящее изобретение было создано для решения вышеуказанных проблем, и его целью является ограничение записи данных, значения которых противоречат особенности изменения данных, состоящей в их возрастании или убывании, которая поддерживается данными для записи для полупроводникового запоминающего устройства. Другой целью настоящего изобретения является запрещение записи в полупроводниковом запоминающем устройстве входных данных, которые не удовлетворяют конкретным требованиям для данных.

Первый аспект настоящего изобретения, связанный с решением вышеуказанных проблем, обеспечивает полупроводниковое запоминающее устройство. Полупроводниковое запоминающее устройство по первому аспекту настоящего изобретения имеет энергонезависимую матрицу памяти с последовательным доступом, которая имеет адрес ячейки с ограничением записи заранее установленной адресной единицы, где запоминают данные, характеризующиеся возрастанием значения, модуль сохранения данных для записи, который сохраняет данные для записи, подлежащие записи по адресу ячейки с ограничением записи с использованием заранее установленной адресной единицы, модуль записи данных, который записывает сохраненные данные для записи по адресу ячейки с ограничением записи с использованием заранее установленной адресной единицы, модуль считывания, который считывает существующие данные, запомненные по адресу ячейки с ограничением записи в матрице памяти, модуль определения, который определяет, больше или равно либо нет значение сохраненных данных для записи значения считанных существующих данных, и блок управления, который в том случае, когда значение данных для записи больше или равно значению существующих данных, выполняет запись данных для записи по адресу ячейки с ограничением записи матрицы памяти с использованием модуля записи.

В полупроводниковом запоминающем устройстве по первому аспекту настоящего изобретения, когда значение данных для записи меньше значения существующих данных, блок управления может не выполнять запись данных для записи по адресу ячейки с ограничением записи.

Согласно полупроводниковому запоминающему устройству по первому аспекту настоящего изобретения с использованием модуля определения определяется, больше или равно либо нет значение запомненных данных значения считанных существующих данных, и в том случае, когда значение данных для записи больше или равно значения существующих данных, блок управления, используя модуль записи, выполняет запись данных для записи по адресу ячейки с ограничением записи матрицы памяти. Следовательно, можно ограничить запись данных, значение которых противоречит характеристике данных для записи, значение которых возрастает.

Согласно полупроводниковому запоминающему устройству по первому аспекту настоящего изобретения, когда отсчет адресов ячеек с ограничением записи составит n раз (где n - натуральное число) заранее установленной адресной единицы, модуль определения может определить, больше или равно либо нет значение данных для записи значения существующих данных для каждой заранее установленной адресной единицы, и для всех адресов запоминающего устройства с ограничением записи, когда значение существующих данных больше или равно значения данных для записи, блок управления выполняет запись данных для записи с использованием модуля записи по всем адресам ячеек с ограничением записи матрицы памяти.

Согласно полупроводниковому запоминающему устройству по первому аспекту настоящего изобретения для любого из адресов ячеек с ограничением записи, когда значение данных для записи меньше значения существующих данных, блок управления может не выполнять запись данных для записи по всем адресам ячеек с ограничением записи.

В вышеуказанном случае, когда полупроводниковое запоминающее устройство имеет множество адресов ячеек с ограничением записи, можно ограничить запись данных, значения которых противоречат характеристике данных для записи, значение которых возрастает, для всех адресов ячеек с ограничением записи.

Согласно полупроводниковому запоминающему устройству по первому аспекту настоящего изобретения модуль определения может считать для каждого 1 адреса данные для записи из модуля сохранения данных для записи каждый раз, когда модуль считывания считывает существующие данные для каждого 1 адреса, и определяет, больше или равно либо нет значение данных для записи значения считанных существующих данных.

Согласно полупроводниковому запоминающему устройству по первому аспекту настоящего изобретения модуль определения может использовать существующие данные заранее установленной адресной единицы, считанные для каждого 1 адреса модулем считывания, и данные для записи заранее установленной адресной единицы, сохраненные в модуле сохранения данных для записи, и определить, больше или равно либо нет значение данных для записи значения считанных существующих данных. При такой конфигурации можно определить, больше или равно либо нет значение данных для записи значения считанных существующих данных, объединенных заранее установленной адресной единицей.

Согласно полупроводниковому запоминающему устройству по первому аспекту настоящего изобретения данные могут запоминаться в порядке от самого старшего разряда в адресе ячейки с ограничением записи в матрице памяти, и модуль записи данных может выполнять запись данных в матрицу памяти в порядке от самого старшего разряда.

Когда записанные данные характеризуются убыванием значения, полупроводниковое запоминающее устройство по первому аспекту настоящего изобретения может также представлять собой полупроводниковое запоминающее устройство, которое имеет энергонезависимую матрицу памяти с последовательным доступом, которая имеет адрес ячейки с ограничением записи заранее установленной адресной единицы, где хранятся данные, характеризующиеся уменьшением значения, модуль сохранения данных для записи, который сохраняет данные для записи, подлежащие записи по адресу ячейки с ограничением записи с использованием заранее установленной адресной единицы, модуль записи данных, который записывает сохраненные данные для записи по адресу ячейки с ограничением записи с использованием заранее установленной адресной единицы, модуль считывания, который считывает существующие данные, запомненные по адресу ячейки с ограничением записи для каждого 1 адреса в матрице памяти, модуль определения, который определяет, меньше или равно либо нет значение сохраненных данных для записи значения считанных существующих данных, и блок управления, который в том случае, когда значение данных для записи меньше или равно значению существующих данных, выполняет запись данных для записи по адресу ячейки с ограничением записи матрицы памяти с использованием модуля записи.

Когда значение данных для записи больше значения существующих данных, блок управления может не выполнять запись данных для записи по адресу ячейки с ограничением записи.

Когда записанные данные характеризуются убыванием значения, полупроводниковое запоминающее устройство по первому аспекту настоящего изобретения может также представлять собой полупроводниковое запоминающее устройство, в котором модуль определения может определять, меньше или равно либо нет значение сохраненных данных для записи значения считанных существующих данных, и в том случае, когда значение данных для записи меньше или равно значению существующих данных, блок управления может выполнить запись данных для записи по адресу ячейки с ограничением записи матрицы памяти с использованием модуля записи. Также, когда значение данных для записи больше значения существующих данных, запись данных для записи по адресу ячейки с ограничением записи может не выполняться, так что можно ограничить запись данных, значение которых противоречит характеристике данных для записи, значение которых уменьшается.

Второй аспект настоящего изобретения обеспечивает полупроводниковое запоминающее устройство, где в качестве перезаписываемых данных запоминают данные, характеризующиеся возрастанием значения. Полупроводниковое запоминающее устройство по второму аспекту настоящего изобретения имеет энергонезависимую матрицу памяти, которая имеет последовательный доступ и для которой имеется 8 простейших элементов данных, запоминающих один разряд данных на 1 строку, и которая имеет строку с ограничением записи, где запоминают перезаписываемые данные, модуль приема данных, который принимает данные для записи в единицах, кратных 8 разрядам, подлежащих записи в строку с ограничением записи матрицы памяти, модуль сохранения данных для записи, который сохраняет 8 разрядов принятых данных для записи, модуль записи данных, который записывает 8 сохраненных разрядов данных для записи в 8-разрядных единицах в строку с ограничением записи, модуль считывания, который считывает существующие данные, сохраненные в простейшем элементе данных строки с ограничением записи в 1-разрядных единицах в матрице памяти, модуль определения, который определяет для каждой 8-разрядной единицы данных для записи, больше или равно либо нет значение данных для записи значения считанных существующих данных, и блок управления, который в том случае, когда значение данных для записи меньше значения существующих данных для любых из данных для записи в виде 8-разрядных единиц, не выполняет запись данных для записи во все рассматриваемые простейшие элементы данных строки с ограничением записи с использованием модуля записи.

В полупроводниковом запоминающем устройстве по второму аспекту настоящего изобретения, когда значение данных для записи больше или равно значению существующих данных для всех данных для записи в виде 8-разрядных единиц, блок управления может выполнить запись данных для записи во все рассматриваемые простейшие элементы данных строки с ограничением записи.

Согласно полупроводниковому запоминающему устройству по второму аспекту настоящего изобретения определение того, больше или равно либо нет значение данных для записи значения считанных существующих данных с использованием модуля определения для всех данных для записи в виде 8-разрядных единиц, выполняют запись данных для записи во все рассматриваемые простейшие элементы данных строки с ограничением записи с использованием модуля записи. Также, когда значение данных для записи меньше значения существующих данных для любых данных для записи в виде 8-разрядных единиц, блок управления не выполняет запись данных для записи во все рассматриваемые простейшие элементы данных строки с ограничением записи. Следовательно, можно ограничить запись данных, значение которых противоречит характеристике данных для записи, значение которых возрастает.

Согласно полупроводниковому запоминающему устройству по второму аспекту настоящего изобретения модуль определения может считывать данные для записи из модуля сохранения данных для записи для каждого 1 разряда каждый раз, когда модуль считывания считывает существующие данные для каждого 1 разряда, и может определить больше или равно либо нет значение данных для записи значения считанных существующих данных. В этом случае можно определить, больше или равно либо нет значение данных для записи значения считанных существующих данных, без необходимости иметь структуру для запоминания считанных существующих данных.

Согласно полупроводниковому запоминающему устройству по второму аспекту настоящего изобретения модуль определения, используя существующие данные в виде единиц, кратных 8 разрядам, считанных для каждого 1 разряда модулем считывания, и данные для записи в виде единиц, кратных 8 разрядам, сохраненных в модуле сохранения данных для записи, может определить, больше или равно либо нет значение данных для записи значения считанных существующих данных. При такой конфигурации можно определить, больше или равно либо нет значение данных для записи значения считанных существующих данных объединенных в виде 8-разрядных единиц.

Согласно полупроводниковому запоминающему устройству по второму аспекту настоящего изобретения данные могут запоминаться последовательно от самого старшего разряда в простейшем элементе данных строки с ограничением записи, а модуль записи данных может выполнять запись данных в матрицу памяти последовательно с самого старшего разряда.

Когда данные для записи характеризуются убыванием значения, полупроводниковое запоминающее устройство по второму аспекту настоящего изобретения может иметь энергонезависимую матрицу памяти, которая имеет последовательный доступ и для которой имеется 8 простейших элементов данных, где запоминают один разряд данных на 1 строку, и которая имеет строку с ограничением записи, где запоминают перезаписываемые данные, модуль приема данных, который принимает данные для записи в единицах, кратных 8 разрядам, подлежащих записи в строку с ограничением записи матрицы памяти, модуль сохранения данных для записи, который сохраняет 8 разрядов принятых данных для записи, модуль записи данных, который записывает 8 сохраненных разрядов данных для записи в 8-разрядных единицах в строку с ограничением записи, модуль считывания, который считывает существующие данные, запомненные в простейшем элементе данных строки с ограничением записи в 1-разрядных единицах в матрице памяти, модуль определения, который определяет для каждой 8-разрядной единицы данных для записи, меньше или равно либо нет значение данных для записи значения считанных существующих данных, и блок управления, который в том случае, когда значение данных для записи больше значения существующих данных для любых данных для записи в виде 8-разрядных единиц, не выполняет запись данных для записи во все рассматриваемые простейшие элементы данных строки с ограничением записи с использованием модуля записи.

Когда значение данных для записи меньше или равно значения существующих данных для всех данных для записи в виде 8-разрядных единиц, блок управления выполняет запись данных для записи во все рассматриваемые простейшие элементы данных строки с ограничением записи.

Когда данные для записи характеризуются убыванием значения, полупроводниковое запоминающее устройство по второму аспекту настоящего изобретения может использовать модуль определения для определения того, больше или равно либо нет значение данных для записи значения считанных существующих данных, и, когда для каждой 8-разрядной единицы данных для записи определено, что значение данных для записи меньше или равно значению существующих данных для всех данных для записи в виде 8-разрядных единиц, модуль записи выполняет запись данных для записи во все рассматриваемые простейшие элементы данных строки с ограничением записи. Также, когда значение данных для записи больше значения существующих данных для любых данных для записи в виде 8-разрядных единиц, запись данных для записи не выполняют во все рассматриваемые простейшие элементы данных строки с ограничением записи. Следовательно, можно ограничить запись данных, значения которых противоречат характеристике данных для записи, значение которых убывает.

Третий аспект настоящего изобретения обеспечивает способ управления записью данных в полупроводниковое запоминающее устройство, которое имеет энергонезависимую матрицу памяти, имеющую адрес ячейки с ограничением записи заранее установленной адресной единицы, где запоминаются данные, характеризующиеся возрастанием значения, и для которой данные записывают в матрицу памяти в заранее установленных адресных единицах. Способ согласно третьему аспекту настоящего изобретения содержит считывание существующих данных, запомненных по адресу ячейки с ограничением записи для каждого 1-го адреса в матрице памяти, определение того, меньше или равно либо нет значение данных для записи, записанных по адресу ячейки с ограничением записи, значения считанных существующих данных, и не выполнение записи данных для записи по адресу ячейки с ограничением записи в заранее установленных адресных единицах, когда значение данных для записи меньше или равно значению существующих данных.

Когда данные для записи характеризуются убыванием значения, способ по третьему аспекту настоящего изобретения может также включать в себя считывание существующих данных, запомненных по адресу ячейки с ограничением записи для каждого 1 адреса в матрице памяти, определение того, больше или равно либо нет значение данных для записи, записанных по адресу ячейки запоминающего устройства с ограничением записи, значения считанных существующих данных, и не выполнение записи данных для записи по адресу ячейки с ограничением записи в заранее установленных адресных единицах, когда значение данных для записи больше или равно значения существующих данных.

Согласно способу управления записью данных по третьему аспекту настоящего изобретения можно получить такие же результаты, как в полупроводниковом запоминающем устройстве по первому аспекту настоящего изобретения, причем способ управления записью данных по третьему аспекту настоящего изобретения может быть реализован в различных аспектах так же, как при использовании полупроводникового запоминающего устройства по первому аспекту настоящего изобретения.

Четвертый аспект настоящего изобретения обеспечивает способ управления записью данных в полупроводниковое запоминающее устройство, которое имеет энергонезависимую матрицу памяти, имеющую строку с ограничением записи для запоминания перезаписываемых данных, характеризующихся возрастанием значения, причем матрица имеет последовательный доступ и 8 простейших элементов данных, где запоминают 1 разряд данных на 1 строку, и данные записывают в матрицу памяти в 8-разрядных единицах. Способ по четвертому аспекту настоящего изобретения включает в себя прием данных для записи в единицах, кратных 8 разрядам, подлежащих записи в матрицу памяти, сохранение 8 разрядов принятых данных для записи, считывание существующих данных, запомненных в простейшем элементе данных строки с ограничением записи в 1-разрядных единицах в матрице памяти, определение того, меньше или равно либо нет значение данных для записи значения считанных существующих данных для каждых данных для записи в виде 8-разрядных единиц, и когда значение данных для записи меньше или равно значению существующих данных для всех данных для записи в виде 8-разрядных единиц, - не выполнение записи данных для записи во все простейшие элементы данных строки с ограничением записи.

Когда данные для записи характеризуются убыванием значения, способ по четвертому аспекту настоящего изобретения может также включать в себя прием данных для записи в единицах, кратных 8 разрядам, подлежащих записи в матрицу памяти, сохранение 8 разрядов принятых данных для записи, считывание существующих данных, запомненных в простейшем элементе данных строки с ограничением записи в 1-разрядных единицах в матрице памяти, определение того, больше или равно либо нет значение данных для записи значения считанных существующих данных для каждых данных для записи в виде 8-разрядных единиц, и когда значение данных для записи больше или равно значению существующих данных для всех данных для записи в виде 8-разрядных единиц, - запись данных для записи во все простейшие элементы данных строки с ограничением записи.

Согласно способу управления записью данных по четвертому аспекту настоящего изобретения можно получить такой же рабочий эффект, как в полупроводниковом запоминающем устройстве по второму аспекту настоящего изобретения, причем способ управления записью данных по четвертому аспекту настоящего изобретения может быть реализован в различных аспектах таким же путем, как при использовании полупроводникового запоминающего устройства по второму аспекту настоящего изобретения.

Способ по третьему и четвертому аспектам настоящего изобретения кроме того может быть реализован в виде программы и считываемого компьютером носителя, на котором записана эта программа.

Пятый аспект настоящего изобретения обеспечивает полупроводниковое запоминающее устройство. Полупроводниковое запоминающее устройство согласно пятому аспекту настоящего изобретения обеспечено энергонезависимой матрицей памяти, и контроллером считывания/записи, для управления записью данных в матрицу памяти и считыванием данных из матрицы памяти, где контроллер считывания/записи при приеме запроса на запись данных в матрицу памяти сравнивает значение введенных многоразрядных данных для записи со значением многоразрядных запомненных данных, запомненных в многоразрядной области памяти, куда должны быть записаны многоразрядные данные для записи, и для многоразрядных данных для записи, которые удовлетворяют конкретному соотношению по величине, выполняет запись в указанную многоразрядную область памяти, а для многоразрядных данных для записи, которые не удовлетворяют указанному конкретному соотношению по величине, запрещает запись в указанную многоразрядную область памяти.

Согласно полупроводниковому запоминающему устройству по пятому аспекту настоящего изобретения можно запретить запись данных для записи, которые не удовлетворяют конкретному соотношению по величине с запомненными данными.

Полупроводниковое запоминающее устройство по пятому аспекту настоящего изобретения может быть скомпоновано следующим образом. Полупроводниковое запоминающее устройство согласно пятому аспекту настоящего изобретения может быть снабжено энергонезависимой матрицей памяти и контроллером считывания/записи для управления записью данных в матрицу памяти и считывания данных из матрицы памяти, где контроллер считывания/записи при приеме запроса на запись данных в матрицу памяти сравнивает значение введенных многоразрядных данных для записи со значением многоразрядных данных, которые запомнены в многоразрядной области памяти, куда должны быть записаны многоразрядные данные для записи, причем указанное сравнение выполняется последовательно по разрядам, начиная с наибольшего разряда из многоразрядных данных для записи, где, если имеется разряд, для которого определено, что он удовлетворяет конкретному соотношению по величине по отношению к каждому значению разряда в запомненных данных, то выполняется запись для данных для записи от этого разряда вперед, а если имеется разряд, для которого указанное конкретное соотношение по величине не удовлетворяется, то запрещается запись для данных для записи с этого разряда вперед.

Согласно полупроводниковому запоминающему устройству по пятому аспекту настоящего изобретения, снабженному вышеупомянутой структурой, в полупроводниковом запоминающем устройстве, где доступ данных выполняется одноразрядными единицами, можно легко запретить запись данных для записи, которые не удовлетворяют конкретному соотношению по величине относительно запомненных данных.

Заметим, что полупроводниковое запоминающее устройство согласно пятому аспекту настоящего изобретения также можно воплотить в виде способа записи в полупроводниковое запоминающее устройство, компьютерную программу или считываемый компьютером носитель, на котором записана указанная программа.

Шестой аспект настоящего изобретения обеспечивает полупроводниковое запоминающее устройство. Полупроводниковое запоминающее устройство согласно шестому аспекту настоящего изобретения снабжено энергонезависимой матрицей памяти для запоминания данных о количестве потребленного материала, которые являются данными, относящимися к количеству потребленного материала, характеризующимися возрастанием значения, модулем записи данных, который записывает новые данные о количестве потребленного материала, подлежащих запоминанию в матрице памяти, модуль считывания, который считывает существующие данные о количестве потребленного материала, которые уже были запомнены, из матрицы памяти; и блок управления для выполнения записи новых данных о количестве потребленного материала через средство записи данных, когда значение новых данных о количестве потребленного материала больше или равно значения существующих данных о количестве потребленного материала, и не выполнения записи новых данных о количестве потребленного материала с использованием средства записи данных, когда значение новых данных о количестве потребленного материала меньше значения существующих данных о количестве потребленного материала.

Согласно полупроводниковому запоминающему устройству по шестому аспекту настоящего изобретения можно получить такой же рабочий эффект, как для полупроводникового запоминающего устройства по первому и второму аспектам настоящего изобретения.

Полупроводниковое запоминающее устройство, изложенное в первом, втором, пятом и шестом вариантах согласно настоящему изобретению, можно использовать, установив его в контейнере для записывающего материала для печати, предназначенном для хранения записывающего материала для печати, причем этот контейнер является съемным и монтируется на печатающем устройстве для запоминания данных, относящихся к количеству записывающего материала для печати. В этом случае можно повысить надежность информации, относящейся к количеству записывающего материала для печати.

Седьмой аспект настоящего изобретения обеспечивает систему печати, содержащую печатающее устройство и датчик записывающего материала для печати, в котором имеется полупроводниковое запоминающее устройство согласно первому, второму, пятому и шестому аспектам настоящего изобретения, причем этот датчик является съемным и монтируется на печатающем устройстве. В системе печати согласно шестому аспекту настоящего изобретения печатающее устройство включает в себя хост-компьютер, где хост-компьютер подсоединен к полупроводниковому запоминающему устройству датчика записывающего материала для печати через шину сигнала данных, шину тактового сигнала, шину сигнала сброса, положительную шину источника питания и отрицательную шину источника питания, и посылает данные о количестве записывающего материала для печати, потребленного в печатающем устройстве, в полупроводниковое запоминающее устройство; и полупроводниковое запоминающее устройство, прикрепленное к датчику записывающего материала для печати, запоминает в матрице памяти количественные данные, касающиеся записывающего материала для печати, которые были получены. Согласно седьмому аспекту настоящего изобретения имеется возможность повысить надежность записи данных, длина которых больше длины данных, которые можно запомнить в одной строке в матрице памяти, предусмотренной в полупроводниковом запоминающем устройстве, при запоминании информации, касающейся количества записывающего материала для печати, который потребляется во время печати.

Краткое описание чертежей

Фиг. 1 - блок-схема, показывающая внутреннюю функциональную структуру полупроводникового запоминающего устройства по первому варианту осуществления;

Фиг. 2 - пояснительная таблица, отображающая внутреннюю конфигурацию матрицы памяти, предусмотренной в полупроводниковом запоминающем устройстве по первому варианту осуществления;

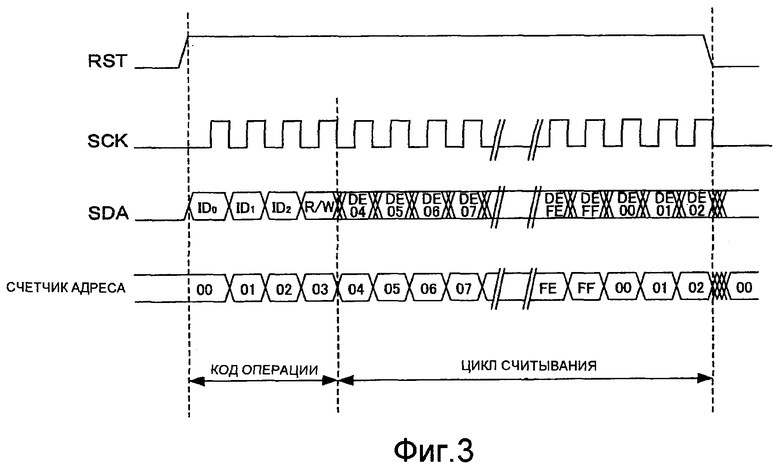

Фиг. 3 - временные диаграммы, показывающие временные соотношения между сигналом RST сброса, внешним тактовым сигналом SCK, сигналом SDA данных и значением счетчика адреса во время выполнения операции считывания;

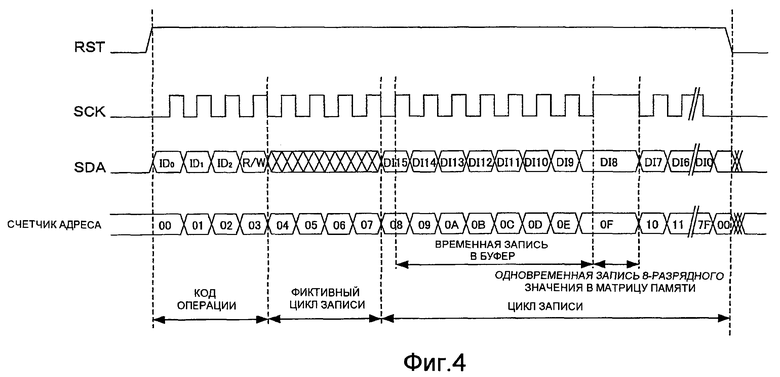

Фиг. 4 - временные диаграммы, показывающие временные соотношения между сигналом RST сброса, внешним тактовым сигналом SCK, сигналом SDA данных и значением счетчика адреса во время выполнения операции записи;

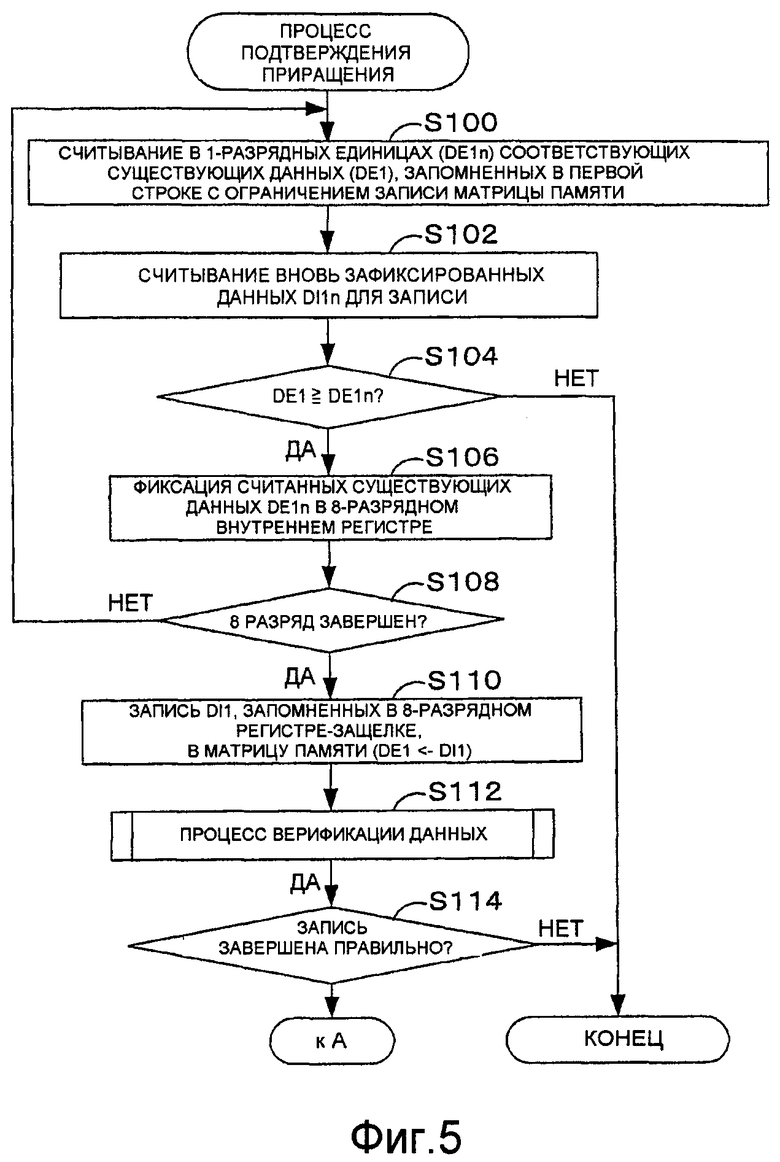

Фиг. 5 - блок-схема алгоритма, показывающая программу обработки для процесса подтверждения приращения в процессе записи, выполняемой полупроводниковым запоминающим устройством по первому варианту осуществления;

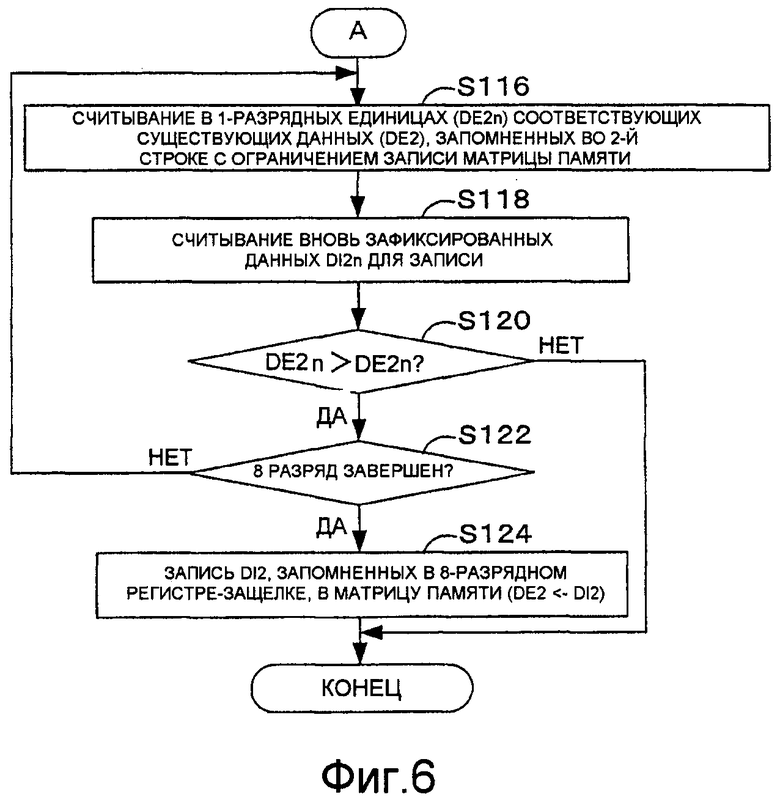

Фиг. 6 - блок-схема алгоритма, показывающая программу обработки для процесса подтверждения приращения в процессе записи, выполняемой полупроводниковым запоминающим устройством по первому варианту осуществления;

Фиг. 7 - блок-схема алгоритма, показывающая программу обработки для процесса верификации данных в процессе записи, выполняемой полупроводниковым запоминающим устройством 10 по первому варианту осуществления;

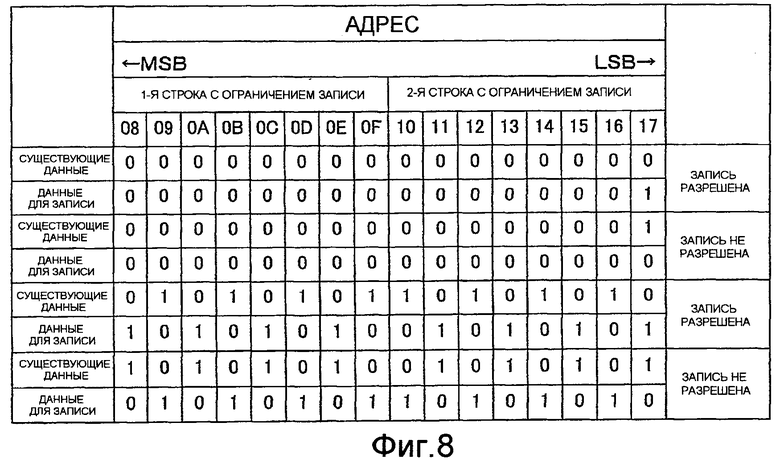

Фиг. 8 - пояснительная таблица, где показаны примерные результаты обработки для процесса подтверждения приращения по первому варианту осуществления;

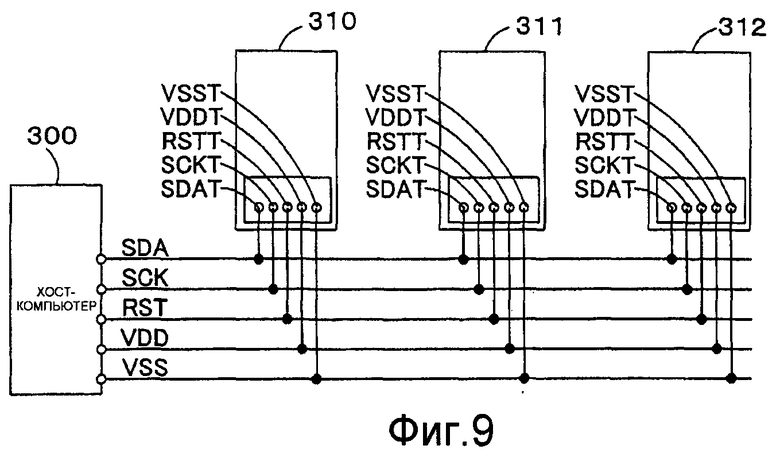

Фиг. 9 - пояснительный чертеж, показывающий прикладной пример полупроводникового запоминающего устройства по первому варианту осуществления;

Фиг. 10 - блок-схема, иллюстрирующая внутреннюю схемную структуру полупроводникового запоминающего устройства согласно второму варианту осуществления;

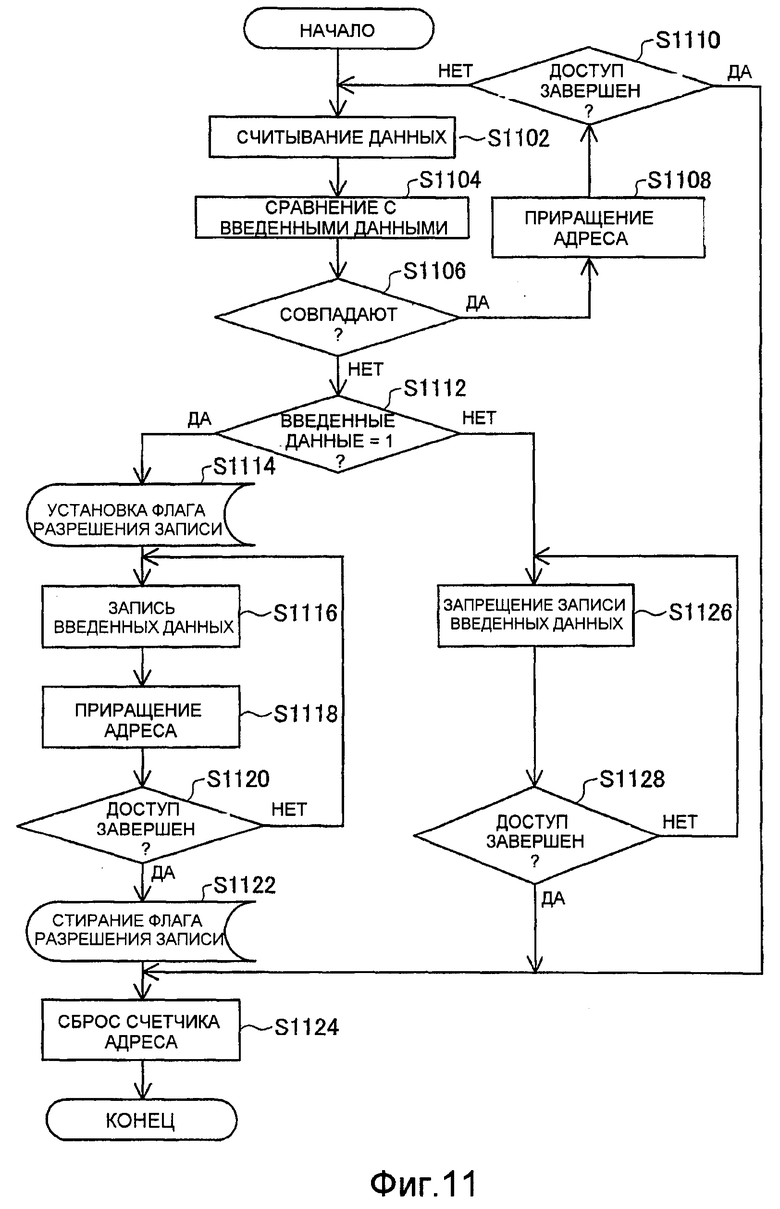

Фиг. 11 - блок-схема алгоритма, иллюстрирующая процедуру выполнения операции записи данных согласно второму варианту осуществления;

Фиг. 12 - блок-схема, иллюстрирующая внутреннюю схемную структуру полупроводникового запоминающего устройства согласно третьему варианту осуществления;

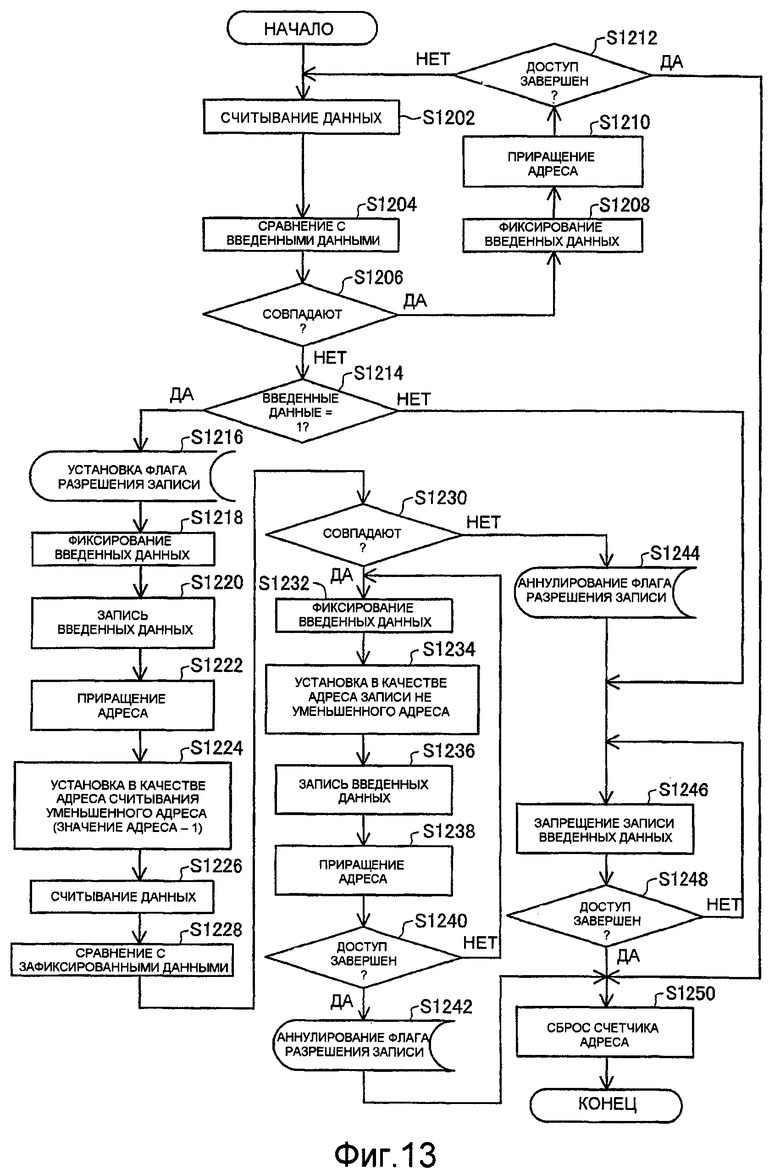

Фиг. 13 - блок-схема алгоритма, иллюстрирующая процедуру выполнения операции записи данных согласно третьему варианту осуществления;

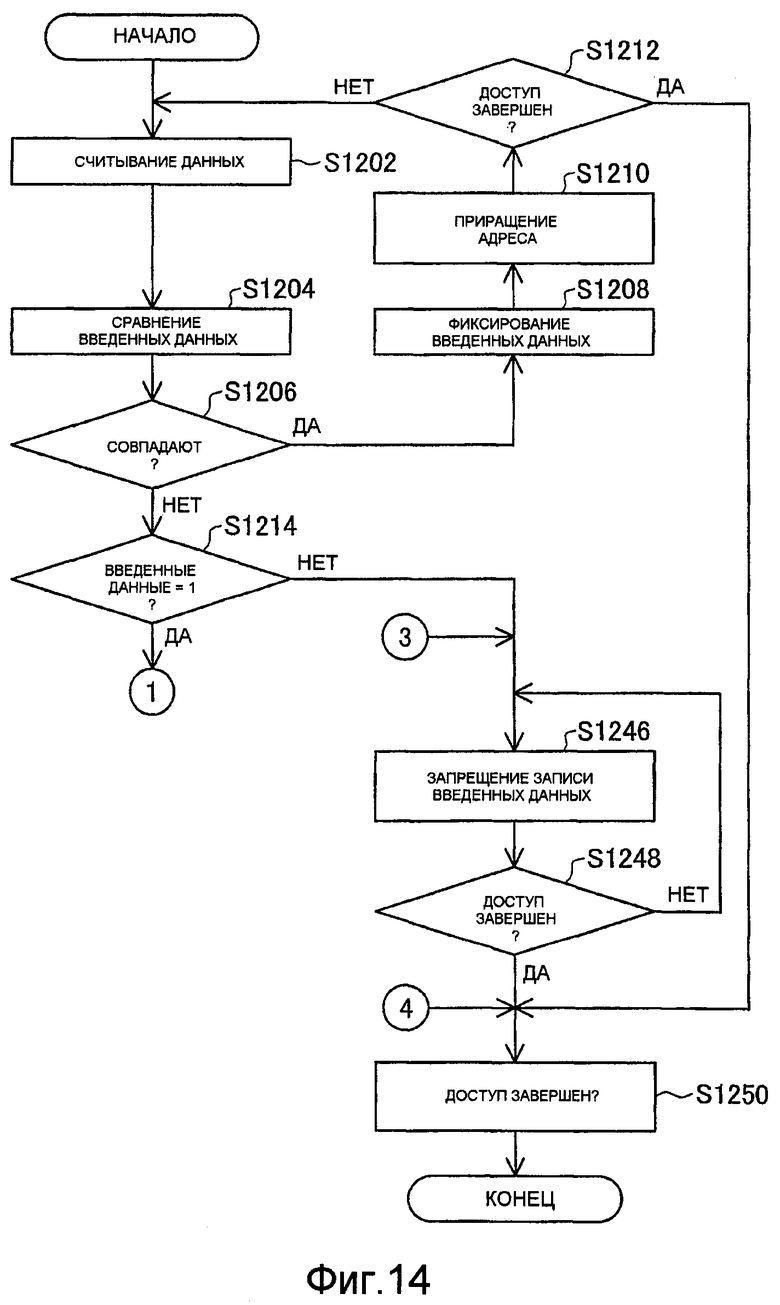

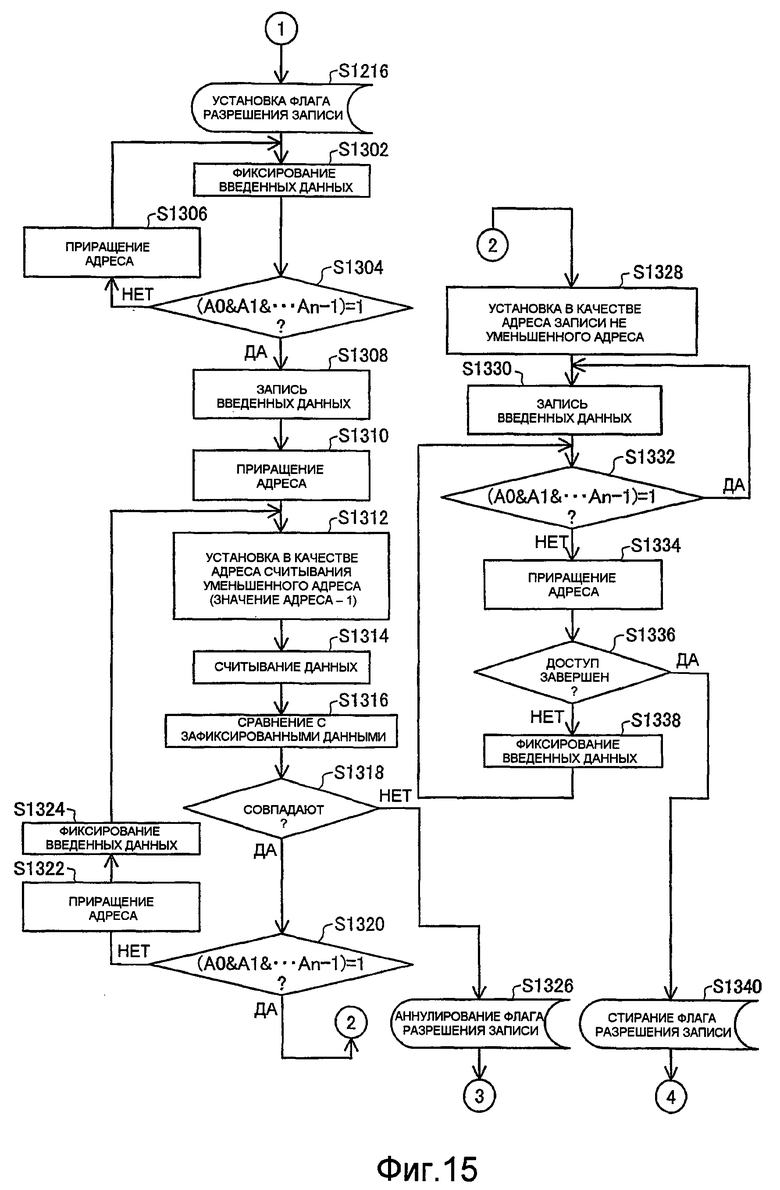

Фиг. 14 - блок-схема алгоритма, иллюстрирующая процедуру выполнения операции записи данных в модифицированном примере третьего варианта осуществления;

Фиг. 15 - блок-схема алгоритма, иллюстрирующая процедуру выполнения операции записи данных в модифицированном примере третьего варианта осуществления.

Осуществление изобретения

Далее со ссылками на чертежи описываются полупроводниковое запоминающее устройство и способ управления записью данных в полупроводниковое устройство по настоящему изобретению на основе нескольких вариантов осуществления изобретения.

Состав полупроводникового запоминающего устройства

Состав полупроводникового запоминающего устройства по первому варианту описывается ниже со ссылками на Фиг. 1 и Фиг. 2. На Фиг. 1 представлена блок-схема, показывающая внутреннюю функциональную структуру полупроводникового запоминающего устройства по первому варианту осуществления. На Фиг. 2 представлена пояснительная таблица, отображающая внутреннюю структуру матрицы памяти для полупроводникового запоминающего устройства по первому варианту.

Полупроводниковое запоминающее устройство по первому варианту осуществления является запоминающим устройством с последовательным доступом, где не требуется ввод извне адресных данных, которые задают адрес назначения доступа. Полупроводниковое запоминающее устройство 10 имеет матрицу 100 памяти, счетчик 110 адреса, контроллер 120 ввода/вывода, компаратор 130 идентификационных данных (ID), контроллер 140 считывания/записи, контроллер 150 приращения, схему 160 подкачки заряда и 8-разрядный регистр-защелку 170. Каждая из этих схем подсоединена к сигнальной линии шинного типа (далее сигнальная шина).

Матрица 100 памяти имеет матрицу 101 EEPROM и матрицу 102 ROM с масочным программированием. Матрица 101 EEPROM является областью запоминания, имеющей EEPROM характеристики, которые в состоянии обеспечить стирание и запись данных электрическим путем, и при записи данных матрица 101 EEPROM, используемая для этого варианта осуществления, может записывать данные прямо, без стирания существующих данных. Матрица 102 ROM с масочным программированием является областью запоминания, которая имеет характеристики ROM с масочным программированием, не позволяющие стирать и перезаписывать данные, записанные во время процесса производства.

В EEPROM матрице и матрице 102 ROM с масочным программированием матрица 100 памяти существует множество простейших элементов данных (ячеек памяти), которые запоминают 1 разряд информации, как типично показано на Фиг. 2.

В варианте осуществления, показанном на Фиг. 2, матрица 100 памяти использует в качестве заранее установленной адресной единицы 8-разрядный адрес на строку (адрес из 8 разрядов данных), и можно разместить, например, 9 простейших элементов данных (8 разрядов) в одной строке и 16 простейших элементов данных (16 слов) в одной строке для запоминания в матрице 101 EEPROM 16 слов × 8 разрядов (128 разрядов) данных. В матрице 102 ROM с масочным программированием можно разместить 8 простейших элементов данных (8 разрядов) в одной строке и 8 простейших элементов данных (8 слов) в одной строке для запоминания 8 слов × 8 разрядов (64 разрядов) данных.

Отображение адресов матрицы 100 памяти описывается со ссылками на Фиг.2. Матрица 100 памяти по этому варианту осуществления включает в себя матрицу 101 EEPROM и матрицу 102 ROM с масочным программированием, как было описано ранее. Идентифицирующая информация (ID информация) для идентификации каждого полупроводникового запоминающего устройства запоминается по первым 3 адресам (столбцы с А0 по А2 первой строки, 3 разряда) матрицы 101 EEPROM. Запись в первую строку, включающую в себя 3 первых адреса, запрещена, и, к примеру, нельзя выполнить перезапись после отгрузки изделия с предприятия-изготовителя.

В примере на Фиг. 2 16 информационных разрядов, которые являются перезаписываемыми при выполнении фиксированных условий, запоминаются по адресам с 9-го (08Н) по 16-й (0FH) и с 17-го (10Н) по 24-й (07Н) матрицы 101 EEPROM. Заметим, что в этом варианте осуществления строку, составленную из указанных адресов с 9-го по 16-й и с 17-го по 24-й иногда называют строкой с ограничением записи, либо каждый из 8-разрядных адресов с 9-го по 16-й и с 17-го по 24-й называют адресом ячейки с ограничением записи заранее установленной адресной единицы. Также фиксированными условиями являются, например, ситуации, когда значение данных для записи больше значения существующих данных в случаях, если запоминаемой информацией является информация, относящаяся к потребленному объему чернил, или когда значение данных для записи меньше значения существующих данных, если запоминаемой информацией является информация, относящаяся к оставшемуся объему чернил.

Область матрицы 101 EEPROM с 25-го адреса и далее является областью только для считывания, запись в которую запрещена; например, запись в нее невозможна после отправки изделия с предприятия-изготовителя.

Матрица 102 ROM с масочным программированием содержит информацию (данные), записанную при изготовлении матрицы памяти, и после ее изготовления запись в нее выполнить невозможно даже до отправки изделия с предприятия-изготовителя.

Матрица 100 памяти по этому варианту осуществления имеет множество строк, где в качестве единицы используется 8 разрядов, как было описано выше, но при этом каждая строка не является независимой строкой из простейших элементов данных, а реализуется одной строкой из простейших элементов данных, устанавливаемой с использованием 8-разрядных единиц. В частности, в описательных целях строку, включающую в себя 9-й разряд, остается назвать вторым байтом, а строку, включающую в себя 17-й разряд, назвать третьим байтом. В результате для доступа к требуемому адресу в матрице 100 памяти необходимо выполнять доступ последовательно с самого начала, чтобы реализовать доступ согласно так называемому «способу последовательного доступа», при этом непосредственный доступ по требуемому адресу, который возможен при использовании способа произвольного доступа, оказывается невозможным.

Числовая шина и разрядная шина (шина данных) подсоединены к каждому простейшему элементу данных в матрице 100 памяти, и данные записывают в простейший элемент данных путем выбора (приложения напряжения выборки) соответствующей числовой шины (строки) и приложения напряжения записи к соответствующей разрядной шине. Также путем выбора соответствующей числовой шины (строки) и подсоединения соответствующей разрядной шины и контроллера 120 ввода/вывода считывают данные (1 или 0) из простейшего элемента данных в соответствии с тем, обнаружен или нет ток. Таким образом можно сказать, что заранее установленной адресной единицей по этому варианту является количество адресов (количество простейших элементов данных) для которых возможна запись путем приложения напряжения записи к одной числовой шине.

Схема 103 выбора столбца имеет столбцы (разрядные шины), подсоединенные к контроллеру 120 ввода/вывода последовательно в соответствии с количеством внешних тактовых импульсов, отсчитанных счетчиком 110 адреса. Схема 104 выбора строки прикладывает напряжение выбора к строкам (числовым шинам) последовательно в соответствии с количеством внешних тактовых импульсов, отсчитанных счетчиком 110 адреса. В частности, при использовании полупроводникового запоминающего устройства 10 по данному варианту осуществления доступ к матрице 110 к требуемому адресу в памяти выполняется не путем использования адресных данных, а в соответствии с количеством тактовых импульсов, отсчитанных эксклюзивным счетчиком 110 адреса.

Счетчик 110 адреса подсоединен к выводу RSTT сигнала сброса, выводу SCKT тактового сигнала, схеме 103 выбора столбцов и схеме 104 выбора строк. Счетчик 110 адреса сбрасывается в начальное значение путем установки в 0 (или низкий уровень) сигнала сброса, который вводится через вывод RSTT сигнала сброса, а после установки сигнала сброса в 1, выполняется синхронизация по заднему фронту тактового импульса, который вводится через вывод SCKT внешнего тактового сигнала, и осуществляется отсчет тактовых импульсов (происходит приращение значения отсчета). В этом варианте осуществления в качестве счетчика 110 адреса используется 8-разрядный счетчик адреса, который запоминает 8 отсчетов тактового импульса, соответствующих числу простейших элементов данных для одной строки (число разрядов) матрицы 100 памяти. Заметим, что начальным значением может быть любое значение, коль скоро оно связано с начальной позицией матрицы 100 памяти, но, как правило, в качестве начального значения используют 0.

Контроллер 120 ввода/вывода представляет собой схему для пересылки данных для записи, которые вводят через вывод SDAT сигнала данных, в матрицу 100 памяти или для приема данных, считываемых из матрицы 100 памяти, и вывода их через вывод SDAT сигнала данных. Контроллер 120 ввода/вывода подсоединен к выводу SDAT сигнала данных, выводу RSTT сигнала сброса, матрице 100 памяти и контроллеру 140 записи/считывания, причем контроллер 120 управляет переключением направления пересылки данных в матрицу 100 памяти и направления пересылки данных (из сигнальной шины, подсоединенной к выводу SDAT сигнала данных) на вывод SDAT сигнала данных в соответствии с запросом от контроллера 140 записи/считывания. 8-разрядный регистр-защелка 170, временно запоминающий данные для записи, которые вводят через вывод SDAT сигнала данных, подсоединен к шине входного сигнала от вывода SDAT сигнала данных к контроллеру 120 ввода/вывода.

Столбец данных (MSB), вводимых через входную сигнальную шину с вывода SDAT сигнала данных в 8-разрядный регистр-защелку 170, сохраняется до тех пор, пока не будет введено 8 разрядов, и, когда 8 разрядов собрано, эти сохраненные 8 разрядов данных будут записаны в матрицу 101 EEPROM. 8-разрядный регистр-защелка 170 относится к регистру сдвига обратного магазинного типа (FIFO), и при фиксировании на 9-м разряде входных данных ранее зафиксированный 1-й разряд данных деблокируется.

Контроллер 120 ввода/вывода запрещает ввод данных через вывод SDAT сигнала данных путем установки направления пересылки данных в матрицу 100 памяти на направление считывания при включении питания и во время сброса, а также путем использования высокого импеданса для входной сигнальной шины между 8-разрядным регистром-защелкой 170 и контроллером 120 ввода/вывода. Это состояние поддерживается до тех пор, пока из контроллера 140 записи/считывания не будет введен запрос на процесс записи. Таким образом, первые 4-разрядные данные столбца данных, введенные через вывод SDAT сигнала данных после ввода сигнала сброса, в матрицу 100 памяти не записываются, а тем временем данные, запомненные в первых 4-х разрядах (тех, где 4-й разряд является безразличным) матрицы 100 памяти, посылаются в компаратор 130 ID. В результате первые 4 разряда матрицы 100 памяти находятся в состоянии «только для считывания».

Компаратор 130 ID подсоединен к выводу SCKT тактового сигнала, выводу SDAT сигнала данных и выводу RSTT сигнала сброса, и с помощью этого компаратора определяется, совпадают ли идентификационные данные, содержащиеся в столбце данных, введенных через вывод SDAT сигнала данных, с идентификационными данными, запомненными в матрице 100 памяти (матрица 101 EEPROM). Если более подробно, то компаратор 100 ID извлекает первые 3 разряда данных кода операции, введенных после ввода сигнала RST сброса, а именно, идентификационные данные. Компаратор 130 ID имеет 3-разрядный регистр (не показан), который запоминает идентификационные данные, содержащиеся во введенном столбце данных, и 3-разрядный регистр (не показан), который запоминает самые старшие 3 разряда идентификационных данных, извлеченных из матрицы 100 памяти через контроллер 120 ввода/вывода, и определяет, совпадают ли эти идентификационные данные, выясняя, совпадают ли значения обоих регистров. Когда указанные идентификационные данные совпадают, компаратор 130 ID посылает сигнал EN разрешения доступа в контроллер 140 записи/считывания. При вводе сигнала RST сброса (RST=0 или низкий уровень) компаратор 130 ID устанавливает регистр в исходное состояние.

Контроллер 140 записи/считывания подсоединен к контроллеру 120 ввода/вывода, компаратору 130 ID, контроллеру 150 приращения, схеме 160 подкачки заряда, выводу SCKT тактового сигнала, выводу SDAT сигнала данных и выводу RSTT сигнала сброса. Контроллер 140 считывания/записи представляет собой схему, которая синхронизируется по 4-му тактовому сигналу после ввода сигнала RST сброса, подтверждает ввод информации управления записью/считыванием (информация от 4-го разряда после 3-разрядной информации ID) через вывод SDAT сигнал данных и переключает внутренний режим работы полупроводникового запоминающего устройства на запись или считывание. В частности, контроллер 140 записи/считывания анализирует извлеченную команду записи/считывания, когда введены сигнал AEN разрешения доступа из компаратора 130 ID и сигнал WEN1 разрешения записи от контроллера WEN1 приращения. Если это команда записи, то контроллер 140 записи/считывания переключает направление пересылки данных по сигнальной шине на направление записи для контроллера 120 ввода/вывода, посылает сигнал WEN2 разрешения записи, который разрешает запись, и выдает запрос на генерацию напряжения записи в схему 160 подкачки заряда.

При этом варианте осуществления, когда данными DI для записи, записываемыми в строку с ограничением записи, являются данные, которые характеризуются возрастанием (приращением) значения, то определяется, больше ли значение данных DI для записи значения существующих данных DE, уже запомненных в строке с ограничением записи, а когда данные DI для записи являются данными, характеризующимися убыванием (уменьшением) значения, то определяется, меньше ли значение данных DI для записи значения существующих данных DE, уже запомненных в строке с ограничением записи, и в результате выполнения этих операций снижаются или предотвращаются изменения данных DI для записи и ввод ошибочных данных. Эта функция обеспечивается в первом случае контроллером приращения, а в последнем случае - контроллером убывания. Далее описывается пример первого случая согласно данному варианту осуществления изобретения.

Контроллер 150 приращения подсоединен к выводу RSTT сигнала сброса, контроллеру 140 записи/считывания и схеме 160 подкачки заряда через сигнальную шину. Контроллер 150 приращения имеет в своем составе 4-разрядный счетчик 151 и 8-разрядные внутренние регистры 152 и 153. Контроллер 150 приращения определяет, больше ли значение данных DI для записи, записываемых в строку с ограничением записи, значения существующих данных DE, уже запомненных в строке с ограничением записи, и, кроме того, определяет (проверяет, подтверждает), правильно ли были записаны данные, ранее записанные в матрицу 101 EEPROM.

Контроллер 150 приращения считывает существующие данные DE из строки с ограничением записи матрицы 101 EEPROM в те моменты времени, когда данные DI для записи фиксируются в 8-разрядном регистре-защелке 170, и запоминает их в 8-разрядном внутреннем регистре 152 для внутреннего хранения. Контроллер 150 приращения сравнивает считанные существующие данные ED с данными DI для записи, введенными в 8-разрядный регистр-защелку 170 в 1-разрядных единицах и определяет, больше ли значение данных DI для записи значения существующих данных DE. Заметим, что для ускорения обработки предпочтительно, чтобы во введенных данных для записи самый старший разряд (MSB) следовал первым.

Контроллер 150 приращения выдает сигнал WEN1 разрешения записи в контроллер 140 записи/считывания, когда значение данных DI для записи больше значения существующих данных DE. Заметим, что, когда строка с ограничением записи распространяется на множество строк, контроллер 150 приращения выдает сигнал WEN1 завершения записи только тогда, когда значение данных DI для записи больше значения существующих данных DE для всех строк с ограничением записи.

После записи данных для записи контроллер 150 приращения проверяет, правильно ли были записаны данные, и, если данные для записи были записаны неправильно, записывает обратно в матрицу 100 памяти существующие данные DE, запомненные в предусмотренном в этом контроллере 8-разрядном внутреннем регистре 152. При проверке данных для записи 4-разрядный счетчик 151, предусмотренный в контроллере 150 приращения, принимает внутренний тактовый сигнал от внутреннего генератора 162, предусмотренного в схеме 160 подкачки заряда, с 8-разрядной задержкой относительно внешнего тактового сигнала из состояния ожидания записи и начинает отсчет в прямом направлении. Значение, отсчитанное 4-разрядным счетчиком 151, вводится в схему 103 выбора столбца и схему 104 выбора строки, после чего выполняется считывание записанных существующих данных DE.

Как было описано ранее, схема 160 подкачки заряда предназначена для подачи через схему 103 выбора столбца в выбранную разрядную шину необходимого напряжения записи при записи данных в матрицу EEPROM на основе сигнала запроса от контроллера 140 записи/считывания.

Схема 160 подкачки заряда оборудована генератором 162, который генерирует сигнал рабочей частоты, необходимый во время повышения напряжения, и путем повышения напряжения, полученного через вывод VDDT положительного электрода источника питания, генерирует необходимое напряжение записи.

Процесс считывания

Далее со ссылками на Фиг. 3 описывается операция считывания в полупроводниковом запоминающем устройстве 10 по данному варианту изобретения. На Фиг. 3 представлена временная диаграмма, показывающая временные соотношения между сигналом RST сброса, внешним тактовым сигналом SCK, сигналом SDA данных и значением счетчика адреса во время выполнения операции считывания.

Здесь описывается подтверждение идентифицирующей информации и процесс подтверждения команды считывания/записи на основе кода операции перед операцией считывания. При отмене хост-компьютером, который не показан, состояния сброса (переход от RST=0, или низкий уровень, в RST=1, или высокий уровень) сигнал SDA данных, который содержит 4-разрядный код операции, синхронизируется с внешним тактовым сигналом и поступает на вывод SDAT сигнала данных. Как показано на Фиг. 3, код операции содержит 3 первых разряда идентифицирующей информации ID0, ID1 и ID2, а в 4-м разряде от начала содержится разряд команды для разрешения записи или считывания. Сравнение идентифицирующей информации выполняется следующим образом.

Компаратор 130 ID извлекает данные, синхронизированные по переднему фронту трех тактовых сигналов SCK, после того как сигнал RST сброса переключился с низкого уровня на высокий, вводит через вывод SDAT сигнала данных 3-разрядную идентифицирующую информацию, и запоминает ее в 1-м 3-разрядном регистре. Одновременно с этим компаратор 130 ID извлекает данные из адресов матрицы 100 памяти, заданных значениями 00, 01 и 02 счетчика 110 адреса, то есть извлекает идентифицирующую информацию, запомненную в матрице 100 памяти, и запоминает ее во 2-м и 3-м 3-разрядных регистрах.

Компаратор 130 ID определяет, совпадает ли идентифицирующая информация, запомненная в 1-м и 2-м регистрах, и в том случае, когда идентифицирующая информация не совпадает, контроллер 120 ввода/вывода поддерживает состояние высокого импеданса для входной сигнальной шины между 8-разрядным регистром-защелкой 170 и контроллером 120 ввода/вывода. Между тем, когда идентифицирующая информация, запомненная в 1-м и 2-м регистрах, совпадает, компаратор 130 ID выдает на контроллер 140 записи/считывания сигнал AEN разрешения доступа. Контроллер 140 записи/считывания, который принял сигнал AEN разрешения доступа, извлекает разряд команды, синхронизированный по переднему фронту 4-го тактового сигнала SCK, после переключения сигнала RST сброса с низкого уровня на высокий и посылки в сигнальную шину, и определяет, является ли эта команда командой записи. Если извлеченный разряд команды не является командой записи, то контроллер 140 записи/считывания выдает в контроллер 120 ввода/вывода команду считывания.

Контроллер 120 ввода/вывода, который принял команду считывания, изменяет направление пересылки данных в отношении матрицы 100 памяти на направление считывания и разрешает пересылку данных. Счетчик 110 адреса синхронизируется по заднему фронту тактового сигнала SCK и выполняет счет в прямом направлении, так что значение счетчика 110 адреса после ввода кода операции равно 04, и выполняется считывание существующих данных DE, запомненных в ячейке 04Н матрицы 100 памяти. Существующие данные DE, запомненные в матрице памяти, синхронизируются по заднему фронту тактового сигнала SCK и выводятся последовательно на вывод SDAT сигнала данных через контроллер 120 ввода/вывода, а выведенные существующие данные DE сохраняются до тех пор, пока не придет следующий задний фронт тактового сигнала SCK. При появлении заднего фронта тактового сигнала SCK значение счетчика 110 адреса увеличивается на 1, в результате чего существующие данные DE, запомненные по следующему адресу (простейший элемент данных) для матрицы 100 памяти, выводятся на вывод SDAT сигнала данных. Эта операция повторяется синхронно с тактовым сигналом SCK, пока не будет достигнут требуемый адрес. В частности, поскольку полупроводниковое запоминающее устройство 10 по данному варианту изобретения относится к типу устройств с последовательным доступом, хост-компьютер должен выдать несколько тактовых импульсов, соответствующих адресу, запрашивая считывание или запись, и увеличивать значение счетчика 110 адреса, пока значение счетчика не будет соответствовать заданному адресу. В результате существующие данные DE синхронизируются по тактовому сигналу SCK и последовательно считываются, начиная с адреса, заданного значением счетчика 110 адреса, которое последовательно увеличивается на единицу.

Матрица 100 памяти полупроводникового запоминающего устройства 10 по данному варианту имеет адреса только с 00Н по BFH, а счетчик 110 адреса выполняет отсчет вплоть до адреса FFH. Область от адреса С0Н по FFH является фиктивной областью, а соответствующие адреса в матрице 100 памяти не существуют, и во время обращения к этой фиктивной области на вывод SDAT сигнала данных выводится значение 0. Когда счетчиком 110 выполнен отсчет адреса до адреса FFH, значение адреса возвращается к 00Н. По окончании операции считывания из хост-компьютера вводится сигнал RST сброса на низком уровне, или «0», и полупроводниковое запоминающее устройство 10 оказывается в состоянии ожидания приема кода операции.

При вводе сигнала RST сброса (=0 или низкий уровень) происходит инициализация счетчика 110 адреса, контроллера 120 ввода/вывода, компаратора 130 ID, контроллера 140 записи/считывания и контроллера 150 приращения.

Процесс записи

Далее со ссылками на Фиг. 4 описывается операция записи для полупроводникового запоминающего устройства 10 по данному варианту осуществления. На Фиг. 4 представлена временная диаграмма, показывающая временные соотношения между сигналом RST сброса, внешним тактовым сигналом SCK, сигналом SDA данных и значением счетчика адреса во время выполнения операции записи. При использовании полупроводникового запоминающего устройства 10 по данному варианту осуществления запись выполняется в строчных единицах (8-разрядные единицы), а именно согласно заранее установленной адресной единице (8 адресных единиц).

После подтверждения компаратором 130 ID совпадения идентифицирующей информации, как было уже описано выше, в случае, когда извлеченный разряд команды является командой записи, и от контроллера 150 приращения принят сигнал WEN1 разрешения записи, контроллер 140 записи/считывания выдает на контроллер 120 ввода/вывода сигнал WEN2 разрешения записи.

Как показано на Фиг. 4, после ввода кода операции через вывод SCKT тактового сигнала в качестве фиктивных тактовых сигналов записи вводятся 4 тактовых сигнала, в результате чего возникает состояние ожидания записи. Счетчик 110 адреса выполняет отсчет в прямом направлении синхронно с задним фронтом тактового сигнала SCK, так что значение счетчика 110 адреса после состояния ожидания записи составит 08, и данные будут записываться, начиная с адреса 08Н матрицы 100 памяти.

При использовании данного варианта осуществления в одну строку (8-разрядную матрицу 100 памяти) записываются данные для записи длиной 16 разрядов. Во время процесса записи сначала 8 разрядов данных с самого старшего разряда (MSB) данных DI для записи синхронизируются по переднему фронту тактового сигнала SCK и фиксируются последовательно в 8-разрядном регистре-защелке 170. Также, пока в контроллер 120 ввода/вывода не будет выведен сигнал WEN2 разрешения записи, существующие данные, синхронизированные по заднему фронту тактового сигнала SCK после 8-го адреса матрицы 100 памяти, последовательно выводятся по сигнальной шине вывода данных (вывод SDA сигнала данных). Существующие данные, выведенные по сигнальной шине вывода данных, вводятся в контроллер 150 приращения и вместе с данными DI для записи, зафиксированными в 8-разрядном регистре-защелке 170, как было описано выше, используются для определения того, больше ли значение данных DI для записи в контроллере 150 приращения, чем значение существующих данных DE. Этот процесс определения выполняется по прошествии переднего фронта тактового сигнала SCK (=1 или высокий уровень) 8-го цикла после состояния ожидания записи.

Контроллер 120 ввода/вывода, который получил сигнал WEN2 разрешения записи, изменяет направление пересылки данных в отношении матрицы 100 памяти на направление записи, снимает установку высокого импеданса для сигнальной шины между 8-разрядым регистром-защелкой 170 и контроллером ввода/вывода и разрешает пересылку данных. В результате на каждую разрядную шину матрицы 100 памяти передается значение (0 или 1) данных DI для записи. Контроллер 140 записи/считывания запрашивает генерацию напряжения записи у схемы 160 подкачки заряда по прошествии заднего фронта тактового сигнала SCK после 8-го цикла после состояния ожидания записи, созданное напряжение записи подается на разрядную шину, выбранную схемой 103 выбора столбца (в этом варианте все разрядные шины), и в результате в одну строку с ограничением записи разом записывается 8 разрядов данных 1 и 0, запомненных в 8-разрядном регистре-защелке 170.

Когда тактовый сигнал SCK 8-го цикла переходит на низкий уровень, значение счетчика 110 адреса возрастает на единицу, и выполняется выборка данных DI для записи (2-й байт данных), подлежащих записи по следующему адресу (8 адресов). Также на интервале низкого уровня тактового импульса после заднего фронта тактового сигнала SCK 8-го цикла выполняется процесс проверки того, совпадают ли записанные существующие данные DE и данные DI, используемые для записи. В частности, на интервале, когда тактовый сигнал находится на низком уровне, в схему 103 выбора столбца и в схему 104 выбора строки вводится значение счетчика для задания адреса 8-и разрядов существующих данных DE, записанных 4-разрядным счетчиком 151, которым оборудован внутренний контроллер 150. В результате записанные 8 разрядов существующих данных DE выводятся из контроллера 120 ввода/вывода и запоминаются в 8-разрядном внутреннем регистре 153, предусмотренном в контроллере 150 приращения, через контроллер 120 ввода/вывода. Контроллер 150 приращения проверяет, совпадают ли 8 разрядов существующих данных DE, запомненных в 8-разрядном внутреннем регистре 153, с 8 разрядами данных DI для записи, запомненных в 8-разрядном регистре-защелке 170.

При использовании данного варианта осуществления данные DI для записи имеют длину в 16 разрядов, и, поскольку имеется две строки из числа строк с ограничением записи (8 адресов х 2), то запись данных DI для записи завершается при двухкратном выполнении вышеописанного процесса. После завершения записи данных DI для записи из хост-компьютера через вывод RSTT сигнала сброса вводится сигнал RST сброса (=0 или низкий уровень).

Заметим, что данные для записи, посылаемые из хост-компьютера, за исключением данных, соответствующих адресу, запрашивающему перезапись, имеют то же значение (0 или 1), которое хранится в данный момент в матрице 100 памяти. То есть, поверх данных адреса в матрице 100 памяти, которые нельзя перезаписывать, записывается то же самое значение.

При вводе сигнала RST сброса (=0 или низкий уровень) происходит инициализация счетчика 110 адреса, контроллера 120 ввода/вывода, компаратора 130 ID, контроллера 140 записи/считывания и контроллера 150 приращения.

Процесс подтверждения приращения

Далее со ссылками на Фиг. 5-8 описывается процесс подтверждения приращения и процесс проверки данных для процесса записи, выполняемого полупроводниковым запоминающим устройством 10 по данному варианту осуществления. На Фиг. 5 и на Фиг. 6 представлены блок-схемы алгоритма, показывающие программу обработки для процесса подтверждения приращения применительно к процессу записи, выполняемому полупроводниковым запоминающим устройством по первому варианту осуществления. На Фиг. 7 представлена блок-схема алгоритма, показывающая программу обработки для процесса проверки данных применительно к процессу записи, выполняемому полупроводниковым запоминающим устройством по первому варианту осуществления. На Фиг. 8 представлена пояснительная таблица, демонстрирующая приведенные в качестве примера результаты процесса подтверждения приращения для первого варианта осуществления.

В начале процесса записи данных DI для записи длиной 16 разрядов (2 байта), когда 1-й байт данных DI1 для записи фиксируется в 8-разрядном регистре-защелке 170, контроллер 150 приращения считывает в 1-разрядных единицах соответствующие существующие данные DE1, запомненные в первой строке с ограничением записи матрицы 100 памяти (этап S100). Затем каждый 1 разряд существующих данных DE1, которые образуют 8 разрядов существующих данных DE1, запомненных в первой строке с ограничением записи, рассматривается в качестве существующих данных DE1n (n = от 1 до 8). Также каждый 1 разряд данных DI1 для записи, который образует 8 разрядов данных DI1 для записи, рассматривается как данные DI1n для записи (n = от 1 до 8).

В частности, контроллер 150 приращения считывает в 1-разрядных единицах соответствующие существующие данные DE1, запомненные в первой строке с ограничением записи матрицы 100 памяти, которые выводятся из контроллера 120 ввода/вывода синхронно с задним фронтом тактового сигнала SCK, используемого при фиксации каждого набора из 2-байтовых данных DI2n для записи в 8-разрядном регистре-защелке 170. Заметим, что адреса матрицы 100 памяти, по которым должен быть записан 1-й байт данных для записи, представляют собой 8 адресов, соответствующих 1-й строке с ограничением записи, и эти 8 адресов являются адресами установленной единицы.

Контроллер 150 приращения считывает 1 разряд данных DI1 для записи, зафиксированных в 8-разрядном регистре-защелке 170, в текущий момент времени (этап S102). Заметим, что при использовании данного варианта осуществления данные DI для записи вводятся в полупроводниковое запоминающее устройство 10 последовательно, начиная с самого старшего разряда (MSB), а данные DI1 для записи фиксируются последовательно с использованием MSB в 8-разрядном регистре-защелке 170.

Контроллер 150 приращения определяет, больше или равно либо нет значение данных DI1n для записи, считанных из 8-разрядного регистра-защелки 170, чем значение существующих данных DE1n, считанных из строки с ограничением записи в матрице 100 памяти, то есть определяет, выполняется ли неравенство DI1n≥DE1n (этап S104). Эта программа обработки заканчивается, когда контроллер 150 приращения определит, что DI1n<DE1n (этап S104: Нет). То есть, запись данных DI1 для записи не выполняется.

Если контроллер 150 приращения определяет, что DI1n ≥ DE1n (этап S106: Да), то существующие данные DE1n, считанные из 1-й строки с ограничением записи, запоминаются в 8-разрядном внутреннем регистре 152, предусмотренном внутри указанного контроллера (этап S106).

Когда контроллер 150 приращения определяет, завершено ли сравнение 8-разрядных существующих данных DE1n, запомненных в 1-ой строке с ограничением записи, с 8 разрядами данных DI1n для записи, запомненных в 8-разрядном регистре-защелке 170 (этап S108), и в результате определено, что сравнение не завершено (этап S108: Нет), то выполнение этапов с S100 по S106 повторяется.

Когда контроллер 150 приращения определяет, что сравнение 8 разрядов существующих данных DE1n, запомненных в 1-й строке с ограничением записи, и 8 разрядов данных DI1n для записи, запомненных в 8-разрядном регистре-защелке 170, завершено (этап S108: Да), он записывает данные DI1 для записи, запомненные в 8-разрядном регистре-защелке 170, в 1-ю строку с ограничением записи матрицы 100 памяти (этап S112). В частности, в результате получится, что DE1 <- DI1, и данные DI1 для записи станут новыми существующими данными DE1. Если более подробно, то, как было описано ранее, контроллер 150 приращения не выполняет непосредственную запись данных DI1 для записи в матрицу 100 памяти, а просто выводит в контроллер 140 записи/считывания сигнал WEN1 разрешения записи, который разрешает запись данных DI1 для записи, запомненных в 8-разрядном регистре-защелке 170, в 1-ю строку с ограничением записи матрицы 100 памяти, причем запись выполняется контроллером 140 записи/считывания, который получил сигнал WEN1 разрешения записи.

Контроллер 150 приращения выполняет процесс верификации данных (этап S112), и при правильном завершении записи (этап S114: Да) выполняются этап и после блока А на Фиг. 6. Между тем, контроллер 150 приращения выполняет процесс верификации данных (этап S112), и, когда запись нормально не завершается (этап S114: Нет), процесс записи заканчивается.

Процесс верификации данных описывается ниже со ссылками на Фиг. 7. Контроллер 150 приращения считывает записанные существующие данные DE1 из 1-й строки с ограничением записи матрицы 100 памяти (этап S200) и сравнивает их с данными DI1 для записи, запомненными в 8-разрядном регистре-защелке 170 (этап S202). Если более конкретно, то контроллер 150 приращения имеет 4-разрядный счетчик 151, который ведет отсчет в прямом направлении, используя внутренний тактовый сигнал, генерируемый внутренним генератором 162 схемы 160 подкачки заряда, на интервале, когда тактовый сигнал находится на низком уровне, после того, как закончена запись первого байта. Контроллер 150 приращения выводит значение 4-разрядного счетчика 151 в схему 103 выбора столбца и схему 104 выбора строки, считывает только что записанные 8 разрядов существующих данных DE1 в адресной последовательности от 1-й строки с ограничением записи матрицы 100 памяти через контроллер 120 ввода/вывода и фиксирует их в 8-разрядном внутреннем регистре 153. В частности, внутренний тактовый сигнал выводится с задержкой в 8 разрядов (8 тактовых сигналов) относительно состояния ожидания записи.

Контроллер 150 приращения определяет, совпадают ли существующие данные DE1, зафиксированные в 8-разрядном внутреннем регистре 153, и данные DI1 для записи, используемые для записи в 1-ю строку с ограничением записи, зафиксированные в 8-разрядном регистре-защелке 170 (этап S204). Когда существующие данные DE1, запомненные во 8-разрядном внутреннем регистре 153 и считанные из 1-й строки с ограничением записи, совпадают с данными DI1 для записи, запомненными в 8-разрядном регистре-защелке 170 (этап S204: Да), контроллер 150 приращения определяет, что запись завершена правильно (этап S206), и эта программа обработки заканчивается.

Когда существующие данные DE1, запомненные в 8-разрядном внутреннем регистре 153, считанные из 1-й строки с ограничением записи, не совпадают с данными DI1 для записи, зафиксированными в 8-разрядном регистре-защелке 170 (этап S204: Нет), контроллер 150 приращения определяет, что запись завершена неправильно, то есть запись была ненормальной (этап S208). Контроллер 150 приращений определяет, совпадают ли существующие данные DE1, зафиксированные в 8-разрядном внутреннем регистре 153, которые были считаны из 1-й строки с ограничением записи, с существующими данными DE1old, запомненными перед записью в 8-разрядном внутреннем регистре 152 (этап 210), и, если определено, что DE1=DE1old (этап S210: Да), заканчивает эту программу обработки. Между тем, когда контроллер 150 приращения определяет, что DE1≠DE1old (этап 210: Нет), он записывает существующие данные DE1old, запомненные перед записью в 8-разрядном внутреннем регистре 152, обратно в 1-ю строку с ограничением записи матрицы 100 памяти (этап S212) и заканчивает эту программу обработки. Если определено, что запись ненормальна, то процесс записи оставшихся данных DI2 для записи во 2-ю строку с ограничением записи не выполняется.

Процесс обратной записи выполняется в циклах обработки записи в 2-ю строку с ограничением записи. В частности, во время цикла записи 2-го байта данных DI2 для записи существующие данные DE1old, запомненные в 8-разрядном регистре-защелке, вводятся в контроллер 120 ввода/вывода, и так же, как с данными, введенными через вывод SDAT сигнала данных, выполняется процесс записи в 1-ю строку с ограничением записи матрицы 100 памяти. В результате 1-й и 2-й строкам с ограничением записи матрицы 100 памяти возвращается значение, которое было до выполнения процесса записи.

Для описания процесса подтверждения приращения вновь обратимся к Фиг.6. Когда запись 1-го байта данных DI1 для записи из данных DI для записи длиной 16 разрядов выполнена правильно, в момент, когда в 8-разрядном регистре-защелке 170 фиксируется оставшийся 2-й байт данных DI2 для записи, контроллер 150 приращения считывает в 1-разрядных единицах соответствующие существующие данные DE2, запомненные во 2-й строке с ограничением записи в матрице 100 памяти (этап S116). Затем каждый 1 разряд существующих данных DE2, которые образуют 8 разрядов существующих данных DE2, запомненных во 2-й строке с ограничением записи, рассматриваются как существующие данные DE2n (n= от 1 до 8).

В частности, контроллер 150 приращения считывает соответствующие существующие данные DE2n, запомненные во 2-й строке с ограничением записи матрицы 100 памяти, которые являются выходом контроллера 120 ввода/вывода, синхронно с задним фронтом тактового сигнала SCK, используемого при фиксации каждых 2-х байт данных DI2n для записи в 8-разрядном регистре-защелке 170. Заметим, что адреса матрицы 100 памяти, по которым должен быть записан 1-й байт данных для записи, являются 8 адресами, соответствующими 2-й строке с ограничением записи, причем эти 8 адресов являются адресами для установленной единицы.

Контроллер 150 приращения считывает данные DI2n для записи, заново зафиксированные в 8-разрядном регистре-защелке 170 (этап S118). Заметим, что в этом варианте изобретения данные DI для записи вводятся в полупроводниковое запоминающее устройство 10 последовательно, начиная с самого старшего разряда (MSB), а данные DI2n для записи последовательно фиксируются с использованием MSB в 8-разрядном регистре-защелке 170.

Контроллер 150 приращения определяет, больше ли значение данных DI2n для записи, считанных из 8-разрядного регистра-защелки 170, чем значение существующих данных DE2n, считанных из 1-й строки с ограничением записи матрицы 100 памяти, то есть выполняется ли неравенство DI2n>DE2n (этап S120). Когда контроллер 150 приращения определяет, что DI2n≤DE2n (этап S120: Нет), он заканчивает эту программу обработки. В частности запись данных DI2 для записи не выполняется.

Когда контроллер 150 приращения определяет, что DI2n > DE2n (этап S120: Да), он определяет, завершено ли сравнение 8 разрядов существующих данных DE2n, запомненных во 2-й строке с ограничением записи, с 8 разрядами данных для DI2n, запомненными в 8-разрядном регистре-защелке 170 (этап S122), и когда определяется, что это сравнение не завершено (этап S122: Нет), повторно выполняются этапы с S116 по S120.

Когда контроллер 150 приращения определяет, что сравнение 8 разрядов существующих данных DE2n, запомненных во 2-й строке с ограничением записи, и 8 разрядов данных DI2n для записи, запомненных в 8-разрядном регистре-защелке 170, завершено (этап S122: Да), он записывает данные DI2 для записи, запомненные в 8-разрядном регистре-защелке 170, во 2-ю строку с ограничением записи матрицы 100 памяти (этап S124) и заканчивает эту программу обработки. В частности, в результате получится, что DE2 <- DI2, и данные DI2 для записи станут новыми существующими данными DE2. Если более подробно, то, как было описано ранее, контроллер 150 приращения не выполняет непосредственную запись данных DI2 для записи в матрицу 100 памяти, а просто разрешает запись данных DI2 для записи, запомненных в 8-разрядном регистре-защелке 170, во 2-ю строку с ограничением записи матрицы 100 памяти, выводит сигнал WEN1 разрешения записи в контроллер 140 записи/считывания, а запись выполняется контроллером 140 записи/считывания, который получил сигнал WEN1 разрешения записи.

Далее со ссылками на Фиг. 8 описываются примеры для случая разрешения записи в матрицу 100 памяти и случая, когда такая запись не разрешена. На Фиг. 8 горизонтальная ось используется для адресов матрицы 100 памяти, причем слева находится самый старший разряд (MSB), а справа самый младший разряд (LSB). Адреса с 08 по 0F соответствуют 1-й строке с ограниченной записью, а адреса с 10 по 17 соответствуют 2-й строке с ограничением записи.

В первом примере данные DI1 для записи, соответствующие 1-й строке с ограничением записи, и существующие данные DE1 совпадают, а значение данных DI2 для записи, соответствующих 2-й строке с ограничением записи, больше значения существующих данных DE2, так что запись разрешается.

Во втором примере данные DI1 для записи, соответствующие 1-й строке с ограничением записи, и существующие данные DE1 совпадают, а значение данных DI2 для записи, соответствующих 2-й строке с ограничением записи, меньше значения существующих данных DE1, так что запись не разрешается.

В третьем примере данные DI1 для записи, соответствующие 1-й строке с ограничением записи, больше существующих данных DE1, а значение данных DI2 для записи, соответствующих 2-й строке с ограничением записи, меньше значения существующих данных DE2, так что запись не разрешается.

В четвертом примере данные DI1 для записи, соответствующие 1-й строке с ограничением записи, меньше существующих данных DE1, так что независимо от соотношения между значением данных DI2 для записи, соответствующим 2-й строке с ограничением записи, и значением существующих данных DE2, запись не разрешается.

Далее со ссылками на Фиг. 9 описывается прикладной пример полупроводникового запоминающего устройства 10 по данному варианту осуществления. На Фиг. 10 представлен пояснительный чертеж, иллюстрирующий прикладной пример полупроводникового запоминающего устройства по данному варианту осуществления. Полупроводниковое запоминающее устройство 10 по этому варианту включает в себя контейнеры, где хранятся потребительские товары, например, картриджи 310, 311 и 312, в которых находятся чернила используемые в качестве записывающего материала для печати. При установке каждого картриджа 310, 3111 и 312 с чернилами на печатающем устройстве, возникает шинное соединение с хост-компьютером 300, предусмотренном в печатающем устройстве. В частности, с полупроводниковым запоминающим устройством 10, оборудованным картриджами 310, 311 и 312 с чернилами, соединены сигнальная шина SDA данных, шина SCK тактового сигнала, шина RST сигнала сброса, шина VDD положительного электрода источника питания и шина VSS отрицательного электрода источника питания, идущие от хост-компьютера 300.

Как было описано выше, при использовании полупроводникового запоминающего устройства 10 по этому варианту осуществления в полупроводниковое запоминающее устройство 10 записываются только данные DI для записи, значение которых больше значения существующих данных DE. Следовательно, можно повысить точность обновления данных, характеризующихся увеличением значения. В частности, в случаях, когда данные DI для записи, посланные от хост-компьютера, изменяют из-за шума свое значение в сторону уменьшения по отношению к предыдущему значению, или когда из хост-компьютера ошибочно послано значение, меньшее предыдущего, запись в полупроводниковое запоминающее устройство 10 не выполняется. Таким образом, при выполнении управления устройством с использованием потребленного объема потребительских товаров, например, когда непрерывно контролируется струйный принтер с целью предотвращения опустошения печатающей головки с использованием данных о потребленном объеме чернил, можно уменьшить или предотвратить повреждение печатающей головки из-за пересыхания, посредством повышения точности обновления данных.

Другие версии выполнения первого варианта осуществления

(1) В вышеописанном варианте осуществления, когда значение данных DI2 для записи больше значения существующих данных DE2, запись в 2-ю строку с ограничением записи разрешается, но также имеется возможность разрешения записи, когда значения данных DI2 для записи и существующих данных DE2 равны. В этом случае можно по меньшей мере уменьшить или предотвратить проблемы, которые возникают при уменьшении значения данных, не уменьшая значения данных, относящихся к потребленному объему потребительских товаров, запомненных в матрице 100 памяти. В этом случае существующие данные DE2 перезаписываются на аналогичное значение для данных DI2.

(2) В связи с вышеупомянутым вариантом осуществления был описан случай запоминания в полупроводниковом запоминающем устройстве данных, характеризующихся увеличением значения, в частности, случай записи потребленного объема потребительских товаров; однако также можно получить аналогичную выгоду в случае запоминания данных, характеризующихся уменьшением значения, в частности, в случае, когда записывается оставшийся объем потребительских товаров. В этом случае вместо контроллера 150 приращения можно предусмотреть контроллер убывания, который определяет, меньше ли значение данных DI для записи, чем значение существующих данных DE.

(3) В вышеописанном варианте осуществления в качестве прикладного примера был использован картридж с чернилами, но в дополнение к этому можно получить те же результаты при использовании картриджа с тонером. Тот же результат также можно получить при использовании носителя, на котором запоминается информация, эквивалентная деньгам, например карта предоплаты или т.п.