1

Изобретение относится к вычислительной технике и может быть использовано при конструировании мулыиш:сксных каналов вводавывода.

Известны мультиплексные каналы автономного либо встроенного типа, содержащие больщое число подканалов. Такой канал способен выполнять одновременно несколько операций ввода-вывода. Работающие внещние устройства (ВУ) периодически устанавливают связь с каналом для приема либо выдачи данных (обычно байта). В каждом сеансе связи канал считывает из памяти подканалов управляюидее слово (УС), связанное с данным ВУ и указывающее вид операции (запись либо чтение), текущий адрес данных в оперативной памяти и светчик байтов. Затем производится передача байта между ВУ и оперативной памятью, модификация адреса и счета в УС и запись УС в память подканалов.

Известно устройство, содержащее регистр данных и регистр управляющего слова, соединенные по входу и выходу с информационной магистралью оперативной памяти. К входу и

выходу регистра данных подключена также информационная щина интерфейса ввода-вывода. В этом устройстве память подканалов является частью оперативной памяти 1.

Недостаток его заключается в уменьщении пропускной способности канала и производительности вычислительной системы, обусловленном больщими затратами времени на считывание и запись управляющих слов.

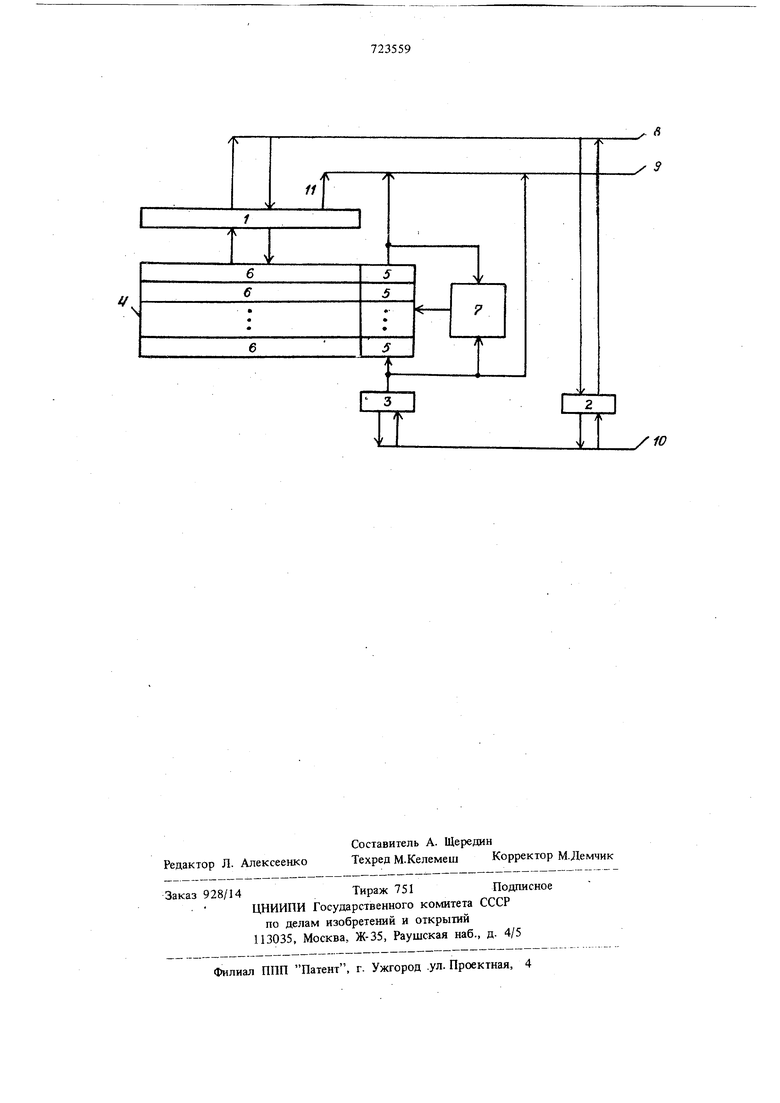

Наиболее близким к предлагаемому является устройство f, содержащее регистр адреса, первый выход которого соединен с адресной шиной оперативной памяти, а второй выход и первый вход соединегы с информационной шиной интерфейса и с первыми входом и выходом регистра данных, вторые вход и выход которого подключены к информационной шине оперативной памяти и к первым входу и выходу регистра управляющего слова, второй выход которого соединен с адресной шиной оперативной памяти. Устройство содержит местную память, предназначенную для хранения управляющих слов. Объем этой памяти значителен, поскольку устройство имеет Много под3каналов (обычно от 32 до 256). В каждый период времени операции ввода-вывода выполняются только на нескольких внешних устрой ствах, следовательно лишь несколько управляющих слов являются активными, а остальная часть местной памяти в каждый период времени не используется 2. Недостатком данного устройства является расход оборудования на построение местной памяти подканалов значительного объема. Цель изобретения - упропдение устрюйства. Поставленная цель достигается тем, что -в мультиплексный канал, содержащий регистр адреса, первый выход которого соединен с адрес ной ишной оперативной памяти, а второй выхо и первый вход соединены с информационной шиной интерфейса и с первыми входом и выходом регистра данных, вторые вход и вы ход которого подключены к информационной шине оперативной памяти и к первым входу и выходу регистра управляющего слова, второй выход которого соединен с адресной шиной оперативной памяти, введены блок ассоциативных регистров и блок сравнения, первый вход i которого соединен с первым выходом регистра адреса и с первым входом блока ассоциативных регистров, первый выход которого подклю чен ко второму выходу регистра управляющего слова и ко второму входу блока сравнения, выход которого соединен со вторым входом блока ассоциативных регистров, второй выход и третий вход которого соединены соответственно со вторым входом и с третьим выходом регистра управляющего слова. На чертеже представлена блок-схема устройства. Устройство содержит регистр 1 управляющего слова, регистр 2 дaннь XJ регистр 3 адреса, блок 4 ассоциативных регистров с признаковой 5 и информационной 6 частями, блок сравнения, информационную 8 и адресную 9 шины оперативной памяти, информационную шину 10 интерфейса ввода-вывода. Устройство работает следующим образом. Процессор,инйциируя операцию ввода-вывода посылает в канал адрес внешнего устройства и управ.11яющее слово,которые помещаются в регистры 3 и 1 соответственно. Канал производит вы борку внешнего устройства и настраивает его на выполнение операи.ии. Затем для обслуживания данной операции выбирается любой незаня тый из числа ассоциативных регистров блока 4. Занятость регистра указывается специ альным разрядом-указателем в признаковой части 5. В признаковую часть 5 выбранного ре гистра помещается адрес внешнего устройства из регистра 3, а в информащюнную часть 6 - управляющее слово из регистра 1. Управление регистрами и узлами устройства производится узлом местного управления, если канал автономный, или центральным управлением прюцессора, есди канал встроенного типа (эти узлы управления на чертеже не показаны). Когда внешнее устройство подготовится к выдаче или приему данных, оно устанавливает связь с каналом и по шине 10 посылает свой адрес, который записывается в регистр 3. Блок 7 отыскивает ассоциативный регистр, связанный с данной операцией, для чего содержимое признаковых частей 5 всех ассоциативных регистров анализируется на равенство с кодом , в регистре 3. Выбирается тот регистр, для которого имеет место совпадение. Потенциалами на выходе блока 7 информационная часть 6 этого регистра подключается по выходу и входу к регистру 1. Из ассоциативного регистра в регистр 1 переписывается управляющее слово, указывающее направление передачи данных, связанный с этой передачей участок оперативной памяти и так далее. Производится передача байта,данных из внешнего устройства через шину 10, регистр 2 и шину 8 в оперативную память, либо в противоположном направлении. Адрес обращения к оперативной памяти устанавливается на шине 9 с выхода 11 адресной части регистра 1. Затем в этом регистре корректируется на единицу адрес данных и счетчик байтов. После передачи байта или группы байтов внешнее устройство отсоединяется от канала, скорректированное управляющее слово возвращается из регистра 1 в ассоциативный регистр. При каждом очередном подключении внешнего устройства для передачи данных описанные действия повторяются. Канал может обращаться в оперативную память не побайтно, а словами, Он формирует слово из- байтов (в операции чтения) или распределяет слово на байты (в операции записи) и хранит обрабатываемое слово в ассоциативном регистре вместе с управляюшим словом. Средства реализации обмена с памятью словами на чертеже не показаны. После окончания операции связанный с нею ассоциативный регистр освобождается и может использоваться для вьшолнения другой операции ввода-вывода с любым внешним устройством. Параллельно с рассмотренной операцией и подобно ей могут выполняться еще несколько операций; ввода-вывода, каждая из которых обслуживается одним из ассоциативных регистров блока 4. Если процессор пытается начать очередную операцию ввода-вывода в момент времени, когда все ассоциативные регистры заняты, канал может отказаться от ее вьшолнения до окончания одной из текущих операций. В эточ случае каналу не требуется память помимо ассоциативных регистров для хранения Т1равляющих слов, однако количество выполняемых операций ввода-вывода ограничивается числом ассоциативных регистров. Для избежания этого ограничения предлагаемый канал содержит память подканалов, расположенную в оперативной памяти. ЕС.ЛИ во время инициирования очередной операции ввода-вывода все ассоциативные регистры блока 4 заняты, канал производит запуск внешнего устройства и затем передает управляющее слово из регистра 1 по шине 8 в память подканалов для записи. Адрес обращения к памяти подканалов определяется адресом внещнего устройства, который посылается на шину 9 с выхода регистра 3. Когда зто внешнее устройство устанавливает связь с каналом для передачи данных, блок 7 по несовпадению содержимого регистра 3 и признаковых частей 5 определяет отсутствие ассоци ативного регистра, связанного с данной операцией. Затем блок 7 отыскивает свободный регистр или, если свободных, нет, ассоциативный регистр, используемый реже остальных. Потенциалами на выходе блока 7 производится выборка наименее активного регистра, и содержи мое его информационной части 6 посылается через регистр 1 и шину 8 в память подканало для записи. Адрес записи устанавливается на ш не 9 с выхода признаковой части 5 этого реги тра. Затем из памяти подканалов считывает ся управляющее слово устройства, подключенного в данный момент к каналу. Это управля ющее слово помещается в регистр 1 j после пе редачи данных корректируется и записывается в информационную час:ь 6 только что освобож- 35 денного регистра. В признаковую часть 5 записывается адрес внешнего устройства из регистра 3. Если имеется свободный ассоциативный регистр, канал работает таким же образом, но выгрузка содержимого регистра в память подканалов не производится. Обращение в память подканалов происходи лишь в случае, если число параллельно выполняемых операций превышает количество ассоциативных регистров. Поскольку выгрузке-загрузке подвергаются наименее активные регистры, эти обращения имеют место в сеансах связи с наиболее медленными из одновременно работающих внещних устройств. Следовательно, обращения в память подканалов редки и практи чески не снижают. гЕропускную способность канала, если он, например, располагает двумя ассоциативными регистрами и выполняет операции с устройствами А, В и С, имеющими быстродействие 1000, 100 и 10 байтов в секунду соответственно. Обращение в памяти подканалов происходит во всех сеансах связи с устройствами С и в десяти из каждых ста сеансов связи с устройством В, т.е. в двадцати сеансах из 1110. 1110. Изобретение создает экономию оборудования . за счет уменьшения объема местной памяти, так как предлагаемый канал, имея те же характеристики, содержит лишь несколько регистров, дополненных признаковой частью (размером 1 байт) и общих для всех подканалов. Особенность канала, связанная с работой словами, не снижает эффективности изображения. Формула изобретения Мультиплексный канал, содержащий регистр адреса, первый -выход которого соединен с адресной щиной оперативной памяти, а второй выход и первый вход coeAiiHCHbi с информа- ционной щиной интерфейса и с первыми входом и выходом регистра данных, вторые вход и выход которого подключены к информационной щине оперативной памяти и к первым входу и выходу регастра управляющего слова, второй выход которого соединен с адресной шиной оперативной памяти, отличающийся тем, что, с целью упрощения устройства, он содержит блок ассоциативных регистров и блок сравнения, первый вход которого соединен с первым выходом регистра адреса и с первым входом блока ассоциативных регистров, первый выход которого подключен ко второму выходу регистра управляющего слова и ко второму входу блока сравне1шя, выход которого соединен со вторым входом блока ассоциативных регистров, второй выход и третий вход которого соед11нены соответственно с вторым входом и с третьим выходом регистра управляющего слова. Источники информации, принятые во внимание при экспертизе 1.Патент США N 3504345, кл. 342-172.5, опублик. 1970. 2.Патент США № 3432813, кл. 342-172.5, опублик. 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство ввода-вывода | 1976 |

|

SU781803A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Селекторный канал | 1973 |

|

SU491951A1 |

| Мультиплексный канал | 1973 |

|

SU517022A1 |

| Встроенный мультиплексный канал | 1977 |

|

SU734649A1 |

| Мультиплексный канал | 1973 |

|

SU525079A1 |

Авторы

Даты

1980-03-25—Публикация

1978-01-09—Подача