Изобретение относится к вычислительной технике и может быть использовано для построения систем обмена данными.

Цель изобретения - повышение быстродействия устройства.

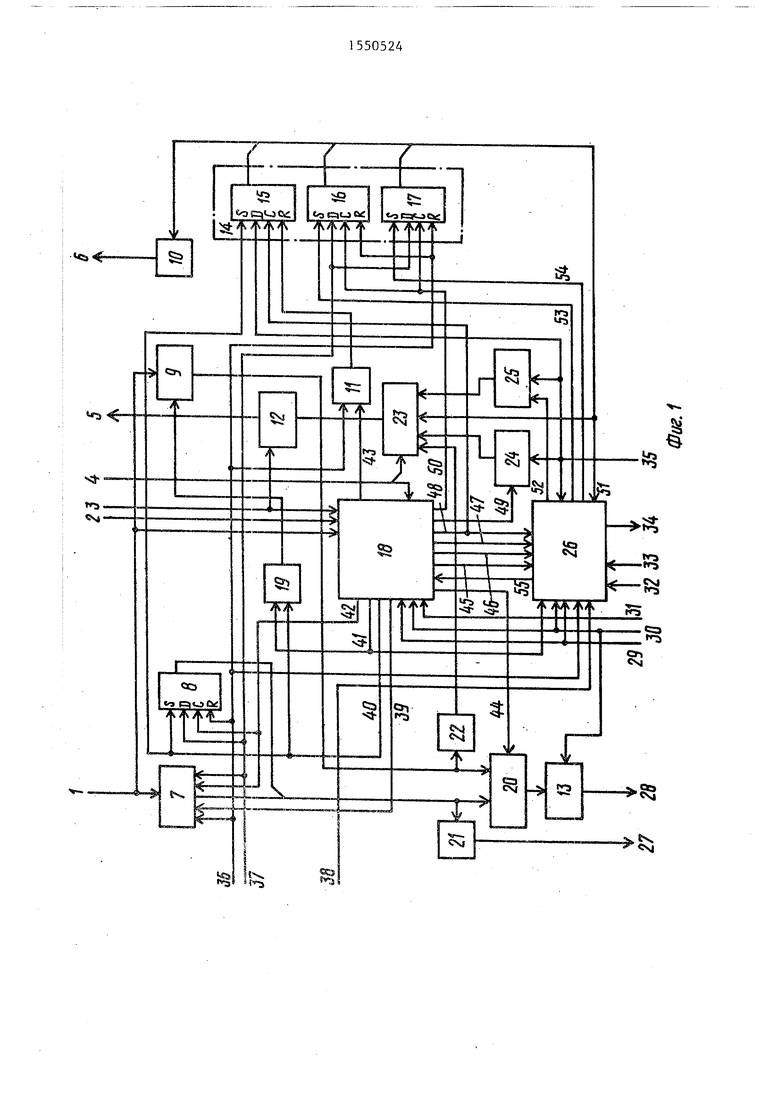

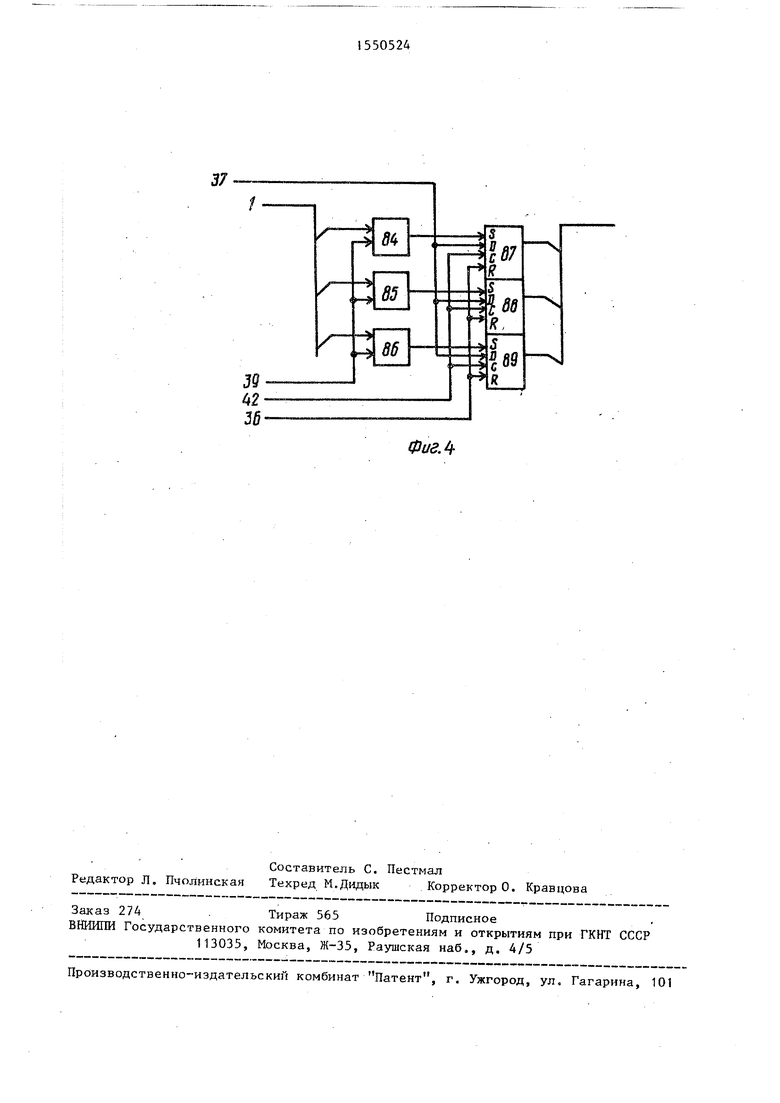

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - 4 - схемы узла управления, узла фиксации режима работы и регистра режима.

Устройство содержит выходную информационную шину 1 процессора, шину 2 Запись процессора, шину 3 Чте- ние процессора, адресную шину 4 процессора, входную информационную шину 5 процессора, входную шину 6 Прерывание процессора, регистр 7 режимов, триггер 8, регистр 9 выходной информации, формирователь 10 сигнала прерывания, элемент ИЛИ 11, шинный формирователь 12, шинный формирователь 13, регистр 14 признаков, состоящий , из триггеров 15, 16 и 17, узел 18

.управления, элемент ИЛИ 19, мультиплексор 20, формирователь 21 сигнала прерывания, шифратор 22, мультиплексор 23, регистр 24 байта текущего состояния, регистр 25 входной информации, узел 26 фиксации режима работы, входную шину 27 прерывания внешнего устройства, входную информационную шину 28 внешнего устройства, шину 29 Запись внешнего устройства, шину 30 Чтение внешнего устройства, адресную шину 31 внешнего устройства, шину 32 Конец блока, шину 33 Разрешение прямого доступа, шину 34 Запрос прямого доступа, выходную информационную гаину 35 внешнего устройства, шину 36 начальной установки, шину 37 нулевого потенциала, шину 38 единичного потенциала.

На фиг. 1 показаны выходы 39 - 50 узла 18 управления, вход 51 и выходы 52 - 55 узла 26 фиксации режима работ.

(Л С

Узел 18 управления содержит фиг. 2) элементы И 56 - 67, первый 68 и второй 69 дешифраторы и элемент ИЛИ 70,

Узел 26 фиксации режима работы содержит (фиг. 3) три триггера 71 - 73, шесть элементов ИЛИ 74 - 79 и четыре элемента И 80 - 83.

Регистр 7 режимов содержит (фиг. 4) три элемента И 84 - 86 и три триггера 87-89.

Выходная информационная шина 1 процессора служит для выдачи управляющей информации в регистр 7 режимов, а также для выдачи байта команды или данных в регистр 9 выходной информации.

Шина 2 Запись процессора служит для выдачи процессором сигнала управ- ления записью в регистр 7 режима, регистр 9 выходной информации.

Шина 3 Чтение процессора служит для выдачи процессором сигнала управления чтением из регистра 14 призна- ков, шифратора 22, регистра 24 байта текущего состояния, регистра 25 входной информации.

Адресная шина 4 процессора служит для выдачи процессором адресов адре- суемых элементов памяти: регистра 7 режимов, регистра 9 выходной информации, регистра 14 признаков, шифратора 22, регистра 24 байта текущего состояния, регистра 25 входной информации. Входная информационная шина 5 про- цессо ра служит для передачи процессору значений регистра 14 признаков, шифратора 22, регистра 24 байта текущего состояния, регистра 25 входной информации.

Входная шина 6 прерывания процессора служит для выдачи в процессор запросов на микропрограммное прерывание для инициирования процедур чтения бай тов начального и конечного состояний, а также чтения или записи байта данных.

Регистр 7 режимов служит для записи и хранения информации от процессора, представляющей указания типа При ем, Цепочка команд, Конец передачи данных.

Триггер 8 служит для идентификации информации, записанной в регистр 9 выходной информации, как команды.

Регистр 9 выходной информации служит для записи и хранения команд и данных от процессора.

«о

5

0

5

Формирователь 10 сигнала прерывания служит для формирования и выдачи сигнала прерывания в процессор. На вход формирователя поступают значения разрядов регистра 14 признаков, единичное значение каждого из которых вызывает формирование сигнала прерывания, формирователь 10 выполнен на элементе ИЛИ.

Шинный формирователь 12 служит для управления выдачей информации на входную информационную шину 5 процессора. Выполнен на элементах с третьим состоянием.

Шинный формирователь 13 служит для управления выдачей информации на входную информационную шину 28 внешнего устройства. Выполнен на элементах с третьим состоянием.

Регистр 14 признаков служит для хранения и выдачи в процессор признаков , идентифицирующих информацию в регистре 25 входной информации как данные или байт состояния. Единичное значение каждого из разрядов регистра 14 признаков вызывает формирование сигнала прерывания в процессор. Регистр 14 признаков состоит из триггеров 15-17.

Триггер 15 служит для записи и хранения признака Байт состояния для идентификации информации, хранящейся в регистре 25 входной информации, как байт состояния. При записи в регистр 14 признаков со стороны внешнего устройства триггер 15 имеет отдельный адрес, по которому также осуществляется запись в триггер 72 в узле 26 фиксации режима работы. Триггер 16 служит для записи и хранения признака Требуются данные требования байта данных от процессора. При записи в триггер 16 со стороны внешнего устройства он имеет отдельный адрес. Триггер 17 служит для хранения признака Данные для идентификации информации, хранящейся в регистре 25 входной информации, как данных. Установка триггера 17 осуществляется при записи в регистр 25 входной информации байта данных от внешнего устройства .

Узел 18 управления служит для приема управляющих сигналов от процессора и внешнего устройства и, на основе их анализа, формирования сигналов управления устройством.

51550

Мультиплексор 20 служит для управления выдачей информации во внешнее устройство из регистра 7 режимов и триггера 8, или из регистра 9 выходной информации.

Формирователь 21 сигнала прерывания служит для формирова шя и выдачи сигнала прерывания во внешнее устройство. На вход формирователя 21 по- ступают значения разрядов регистра 7 режимов и триггера 8. Формирователь 21 выполнен, например, на элементе ИЛИ.

Шифратор 22 служит для хранения начальных байтов состояния для выдачи их в процессор в процедуре начальной выборки для всех кодов команд. Выполнен, например, на ПЗУ, на адресные входы которого поступают ко- ды команд, а с выхода считываются байты начального состояния.

Мультиплексор 23 служит для управления выдачей информации в процессор из шифратора 22, регистра 14 призна- ков, регистра 24 байта текущего состояния или регистра 25 входной информации .

Регистр 24 байта текущего состояния служит для хранения состояний внешнего устройства: Доступно, Недоступно, Занято.

Регистр 25 входной информации служит для записи и хранения байтов данных и байтов состояния от внешнего устройства.

Узел 26 фиксации режима работы служит для управления режимами обмена данными с внешним устройством в режиме прямого доступа к оперативной памяти внешнего устройства.

Входная шина 27 прерывания внешнего устройства служит для выдачи во внешнее устройство запросов на микропрограммное прерывание для иницииро- вания процедур передачи команды, обмена данными, завершения операции.

Входная информационная шина 28 внешнего устройства служит для передачи внешнему устройству значений ре- гистра 7 режимов, триггера 8, а также значений регистра 9 выходной информации.

Шина 29 Запись внешнего устройства служит для приема от внешнего устройства сигнала управления записью в регистр 14 признаков, в регистр 24 байта текущего состояния, в регистр 25 входной информации.

Шина 30 Чтение внешнего устройства служит для приема от внешнего устройства сигнала управления чтением регистра 7 режимов, триггера 8, а также регистра 9 выходной информации. Адресная шина 31 внешнего устройства служит для приема от внутреннего устройства адресов адресуемых элементов памяти: регистра 7 режимов, триггера 8, регистра 14 признаков, регистра 7 режимов, триггера 8, регистра 14 признаков, регистра 24 байта текущего состояния, регистра 25 входной информации.

Шипа 32 Конец блока служит для приема от внешнего устройства сигнала завершения процедуры обмена данными в режиме прямого доступа к оперативной памяти внешнего устройства.

Шина 33 Разрешение прямого доступа служит для выдачи внешним устройством сигнала обратной связи на сигнал Запрос прямого доступа от устройства и служит для управления приемом или выдачей байтов данных.

Шина 34 Запрос прямого доступа служит для инициирования во внешнем устройстве процедуры приема или выдачи байта данных в режиме прямого доступа к оперативной памяти внешнего устройства.

Выходная информационная шина 35 внешнего устройства служит для выдачи информации от внешнего устройства в регистры 14 признаков, 24 байта текущего состояния и 25 входной информации.

Устройство работает следующим образом.

Перед началом работы сигналом на шине 36 начальной установки все элементы памяти устройства приводятся в исходное состояние. Инициация работы устройства производится как от процессора, так и от внешнего устройства.

Процессор может обращаться по записи в регистр 7 режима и регистр 9 выходной информации, при этом в устройство по выходной информационной шине 1 процессора поступает байт информации для записи, а на адресную шину 4 процессора и шину 2 Запись процессора - адрес элемента памяти и сигнал управления записью. Адрес „ элемента памяти и сигнал управления записью поступают в узел 18 управления, где вырабатывается сигнал управ

ления записью в адресованный элемент памяти.

Процессор может обращаться по чте-1 нию в регистр 14 признаков, шифратор 22, регистр 24 байта текущего состоя- ния и регистр 25 входной информации, при этом в устройство по адресной шине 4 процессора и шине 3 Чтение процессора поступают адрес элемента памяти и сигнал управления чтением. Адрес элемента памяти и сигнал управления чтением поступают в узел 18 управления, где вырабатывается сигнал управления чтением адресованного эле- мента памяти. Под управлением этого сигнала производится чтение значения адресованного элемента памяти на входную информационную шину 5 процессора. Внешнее устройство может обращаться по записи в триггер 15 регистра 14 признаков, регистр 24 байта текущего состояния, регистр 25 входной информации, триггер 72 узла 26 фиксации режима работы, при этом в устрой- ство по выходной информационной шине 35 внешнего устройства поступает байт информации для записи, а по адресной шине 31 внешнего устройства и шине 29 Запись внешнего устройства - ад- pec и сигнал управления записью. Ад рее элемента памяти и сигнал управления записью поступают в узел 18 управления, где вырабатывается сигнал управления записью в адресованный элемент памяти.

Внешнее устройство может обращаться по чтению в регистр 7 режимов, триггер 8 и регистр 9 выходной информации, при этом в устройство по ад- ресной шине 31 внешнего устройства и шине 30 Чтение внешнего устройства поступают адрес и сигнал управления чтением. Адрес элемента памяти и сигнал управления чтением поступают в узел 18 управления, где вырабатываетс сигнал управления чтением адресован- ного элемента памяти. Под управлением этого сигнала производится чтение значения адресованного элемента памяти на входную информационную шину 28 внешнего устройства. Выходы регистра 7 режимов и триггера 8 объединены в шину, при обращении по чтению эти элементы памяти имеют единый адрес и значения их читаются заодно обращение.

В процедурах обмена байтами данных между устройством и внешним устройством взаимодействие их осуществляется

0

- 5 п

.,- 5

50

в режиме прямого доступа к оперативной памяти внешнего устройства. В режиме передачи данных от процессора во внешнее устройство чтение байта данных на входную информационную шину 28 внешнего устройства из регистра 9 выходной информации производится под управлением сигналов на шине 34 Запрос прямого доступа, шине 30 Чтение внешнего устройства, шине 33 Разрешение прямого доступа. В режиме передачи данных от внешнего устройства в процессор запись байта данных с выходной информационной шины 35 внешнего устройства в регистр 25 входной информации производится под управлением сигналов на шине 34 Запрос прямого доступа, на шине 29 Запись, на шине 33 Разрешение прямого доступа, на шине 32 Конец блока.

Устройство осуществляет часть функций управления внешним устройством в операциях ввода-вывода, которые состоят из процедур:

-начальной выборки, которая включает в себя прием команды от процессора и выдачу начального байта состояния,

-передачи данных от процессора во внешнее устройство,

-передачи данных от внешнего устройства в процессор,

-передачи байта состояния в процессор.

Процедура начальной выборки в устройствах ввода-вывода обычно выполняется следующим образом.

Устройства ввода-вывода, получив код команды от процессора, анализиру- ют состояние устройства, которое может иметь значение Доступно, Занято или Недоступно. Если состояние устройства ввода - вывода Занято или Недоступно, оно выдается как начальный байт состояния устройства; если состояние устройства Доступно, анализируется код поступившей команды. Код команды может иметь значения, приемлемые или неприемльмые для данного устройства ввода-вывода. Если код команды неприемлем, в процессор выдается байт начального состояния Сбой в устройстве. Если код команды приемлемый, выдается байт начального состояния, определенный для каждого кода команды, например: нулевой, Канал кончил, Канал кончил, внешнее устройство кончило. Выполнение процедуры начальной выборки по такому алгоритму занимает достаточно много времени, особенно, если устройство ввода-вывода представляет собой пульт системы и на момент поступления команды от процессора микропрограмма управления пультом системы отрабатывает другие процедуры и сигнал прерывания от процессора по отработке кода поступившей команды не может быть сразу отработан.

В данном устройстве процедура на

байта состояния из шиЛратора 22. Шифу ратор 22 представляет собой ПЗУ, на адресные входы которого поступает код команды. В ПЗУ хранятся байты начального -состояния на все коды существующих команд для данного устройства ввода-вывода, а также значения Сбой устройства для всех несушест- вующих кодов команд. Эти значения считываются микропрограммой процессора и принимаются за байты начального состояния. После считывания байта начального состояния микропрограммой

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1987 |

|

SU1442996A1 |

| Устройство для сопряжения процессора с устройствами ввода-вывода | 1983 |

|

SU1129602A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения систем обмена информацией. Целью изобретения является повышение быстродействия. Устройство содержит узел управления, узел фиксации режима работы, два мультиплексора, два шинных формирователя, два формирователя сигнала прерывания, регистр режимов, регистр признаков, регистр выходной информации, регистр входной информации, регистр байта текущего состояния, шифратор, триггер, два элемента ИЛИ. 2 з.п. ф-лы. 4 ил.

чальной выборки выполняется следующим,,- процессора осуществляется запись в

,.,I ..

30

35

образом. Инициация процедуры осуществляется со стороны процессора. Перед записью кода команды микропрограмма процессора считывает регистр 24 байта текущего состояния и анализирует его значение. В регистре 24 байта текущего состояния всегда хранится состояние внешнего устройства Доступно, Занято или Недоступно, которое записывается микропрограммой внешнего 25 устройства и изменяется при изменении состояния внешнего устройства. Состояние внешнего устройства анализируется микропрограммой процессора и, если оно имеет значение Занято или Недоступно, то принимается за значение начального байта состояния в ответ на команду, которая в этом случае не записывается в устройство. Если значение регистра 24 байта текуше- го состояния Доступно, то код команды записывается в регистр 9 выходкой информации, при этом устанавливается триггер 8 и триггер 15 регистра 14 признаков. На входной шине 6 пре- iрывания процессора появляется сигнал прерывания микропрограммы процессора. По сигналу прерывания процессор считывает значение регистра 14 признаков и анализирует его значение. Единичное значение триггера 15 регистра 14 признаков идентифицирует сигнал прерывания как запрос на передачу байта состояния, который может быть начальным байтом состояния, конечным или асинхронным байтом состояния. Значение конечного или асинхронного начального байта состояния хранится в регистре 25 входной информации. Значение начального байта состояния на код поступившей команды хранится в шифраторе 22. В процедуре начальной выборки микропрограмма процессора считывает значение начального

40

45

50

55

регистр 7 режима значения Прием. На входной шине 27 прерывания внешн го устройства появляется сигнал пр рывания микропрограммы внешнего уст ройства, по которому микропрограмма внешнего устройства считывает значе ния регистра 7 режима и триггера 8 и анализирует их. Единичное значени триггера 8 идентифицирует информаци в регистре 9 выходной информации ка команду, а значение Прием регистр 7 режимов указывает на завершение п ема байта начального состояния проц сором. Микропрограмма внешнего устройства считывает значение регистра выходной информации, где хранится к команды. Таким образом, в устройств процедура начальной выборки заверша ется на уровне процессор-устройство Обращение к внешнему устройству осу ществляется только для передачи код команды для выполнения процедур, сл дующих за процедурой начальной выборки.

Перед выполнением этих процедур микропрограммой внешнего устройства в регистр 24 байта текущего состоян записывается значение Занято, кот рое блокирует устройство для записи новых команд, пока выполнение преды дущей команды не будет завершено. П сле завершения команды в регистр 24 байта текущего состояния записывает значение Доступно.

Запись в регистр 24 байта текуще состояния осуществляется следующим разом. По выходной информационной ш не 35 внешнего устройства на вход р гистра 24 байта текущего состояния поступает значение банта состояния внешнего устройства. Адрес регистра 24 байта текущего состояния по адрес ной шине 31 внешнего устройства поступает на вход дешифратора 69 адреI ..

30

35

25

40

45

50

5

регистр 7 режима значения Прием. На входной шине 27 прерывания внешнего устройства появляется сигнал прерывания микропрограммы внешнего устройства, по которому микропрограмма внешнего устройства считывает значения регистра 7 режима и триггера 8 и анализирует их. Единичное значение триггера 8 идентифицирует информацию в регистре 9 выходной информации как команду, а значение Прием регистра 7 режимов указывает на завершение приема байта начального состояния процессором. Микропрограмма внешнего устройства считывает значение регистра 9 выходной информации, где хранится код команды. Таким образом, в устройстве процедура начальной выборки завершается на уровне процессор-устройство. Обращение к внешнему устройству осуществляется только для передачи кода команды для выполнения процедур, следующих за процедурой начальной выборки.

Перед выполнением этих процедур микропрограммой внешнего устройства в регистр 24 байта текущего состояния записывается значение Занято, кото-, рое блокирует устройство для записи новых команд, пока выполнение предыдущей команды не будет завершено. После завершения команды в регистр 24 байта текущего состояния записывается значение Доступно.

Запись в регистр 24 байта текущего состояния осуществляется следующим образом. По выходной информационной шине 35 внешнего устройства на вход регистра 24 байта текущего состояния поступает значение банта состояния внешнего устройства. Адрес регистра 24 байта текущего состояния по адресной шине 31 внешнего устройства поступает на вход дешифратора 69 адреса узла 18 управления, на выходе которого появляется сигнал, который поступает на вход элемента И 62. На другой вход элемента И 62 по шине 29 Запись внешнего устройства поступает сигнал управления записью. Сигналом с выхода элемента И 62, который с выхода 49 поступает на управляющий вход регистра 24 байта текущего состояния, осуществляется запись байта текущего состояния.

При чтении значения регистра 24 байта текущего состояния по адресной шине 4 процессора на управляющий вход мультиплексора 23 поступает двух разрядный адрес регистра 24 байта текущего состояния, а по 3 Чтение процессора на управляющий вход шинного формирователя 12 поступает сигнал управления чтением. Наличие адреса на входе мультиплексора 23 и сигнала управления чтением на управляющем входе шинного формирователя 12

обеспечивает выдачу на входную инфор- 25 нием. Адрес шифратора 22, определяемационную шину 5 процессора значения регистра 24 байта текущего состояния.

При записи команды в устройство

по выходной информационной шине 1 Сигнал управления чтением управляет

цессора на вход регистра 9 выходной информации поступает код команды, по адресной шине 4 процессора - разряд адреса записи команды в регистр 9 выходной информации, а по шине 2 Запись процессора - сигнал управления записью. Разряд адреса и сигнал управления записью поступают в узел 18 управления на входы элемента И 59, на выходе которого формируется сигнал и поступает через элемент ИЛИ 19 на вход записи регистра 9 выходной информации и на установочные входы триггеров 8, 15. В регистр 9 выходной ин- , формации записывается код команды,

а триггера 8, 15 устанавливаются в единичное значение. Единичное значение триггера 8 поступает на первый информационный йход мультиплексора 20, а значение кода команды из регистра 9 выходной информации поступает на второй информационный вход мультиплексора 20 и вход шифратора 22, Единичное значение триггера 15 регистра 14 признаков поступает на вход мультиплексора 23 и вход формирователя 10 сигнала прерывания. На выходе формирователя 10 сигнала прерывания по- являе тся сигнал прерывания, который

35

40

прохождением этого значения через шинный формирователь 12 на входную информационную шину 5 процессора.

При записи значения Прием в регистр 7 режимов по выходной информационной шине 1 процессора на входы регистра 7 режимов и узла 18 управле ния поступает разряд информации, по адресной шине 4 процессора - разряд адреса регистра 7 режимов, а по шине 2 Запись процессора - сигнал уп равления записью. В узле 18 управления на элементе И 58 вырабатывается сигнал управления записью и по шине &е 39 поступает на вход регистра 7 режи мов , где на элементе И 86 Формируется сигнал записи значения Прием в триггер 89. Единичное значение триггера 89 поступает на вход второго формирователя 21 сигнала прерывания и вызывает возникновение сигнала на входной шине 27 прерывания внешнего устройства. В узле 18 управления на элементе И 56 Нормируется сигнал, которьй через элемент ИЛИ 11 поступа ет на вход сброса триггера 15 и сбра сывает его.

При чтении значений регистра 7 ре жимов и триггера 8 по адресной шине

50

55

5

0

по входной шине 6 прерывания процессора поступает в процессор.

При чтении значения триггера 15 регистра 14 признаков по адресной шине 4 процессора и шине 3 Чтение процессора поступают адрес регистра 14 признаков и сигнал управления чтением. Адрес регистра 14 признаков, определяемый двумя разрядами, поступает на управляющий вход мультиплексора 23 и управляет прохождением значения регистра 14 признаков через мультиплексор 23. Сигнал управления чтением поступает на управляющий вход шинного формирователя 2 для управления прохождением значения регистра 14 признаков на входную информационную шину 5 процессора.

При чтении значения начального байта состояния из шифратора 22 по адресной шине 4 процессора и шине 3 Чтение процессора поступает адрес шифратора 22 и сигнал управления чтемый двумя разрядами, поступает на управляющий вход мультиплексора 23 и управляет прохождением значения шифратора 22 через мультиплексор 23,

5

0

прохождением этого значения через шинный формирователь 12 на входную информационную шину 5 процессора.

При записи значения Прием в регистр 7 режимов по выходной информационной шине 1 процессора на входы регистра 7 режимов и узла 18 управления поступает разряд информации, по адресной шине 4 процессора - разряд адреса регистра 7 режимов, а по шине 2 Запись процессора - сигнал управления записью. В узле 18 управления на элементе И 58 вырабатывается сигнал управления записью и по шине е 39 поступает на вход регистра 7 режимов , где на элементе И 86 Формируется сигнал записи значения Прием в триггер 89. Единичное значение триггера 89 поступает на вход второго формирователя 21 сигнала прерывания и вызывает возникновение сигнала на входной шине 27 прерывания внешнего устройства. В узле 18 управления на элементе И 56 Нормируется сигнал, которьй через элемент ИЛИ 11 поступает на вход сброса триггера 15 и сбрасывает его.

При чтении значений регистра 7 режимов и триггера 8 по адресной шине

0

5

315505

31 внешнего устройства и по шине 30 Чтение внешнего устройства поступают: адрес, общий для регистра 7 режима и триггера 8, и сигнал управления чтением. Так как в отсутствие сигнала управления чтением регкс гра 9 выходной информации на управляющем входе мультиплексора 20 он всегда настроен на прохождение информации с выхода реги- )0 стра 7 режима и триггера 8, а шинный формирователь 13 управляется сигналом на шине 30 Чтение внешнего устройства - с появлением сигнала управления

чтением на шине 30 Чтение внешнего

устройства единичное значение триггера считывается на входную информационную шину 28 внешнего устройства. В узле 18 управления адрес поступает на вход дешифратора 69 и с его выхода JQ на вход элемента И 66, на второй вход которого поступает сигнал управления чтением. Сигнал с выхода элемента И 66 поступает на синхровходы тригге-

ров 87 - 89 регистра 7 режима и триг- 25 нее). Байт данных из регистра 9 счигера 8, которые по заднему фронту сигнала управления чтением сбрасываются в исходное состояние.

При чтении кода команды из регистра 9 выходной информации по адресной шине 31 внешнего устройства и по шине 30 Чтение внешнего устройства в узел 18 управления поступают адрес регистра 9 выходной информации и сигнал управления чтением. Адрес поступает на вход дешифратора 69 и с его выхода на вход элемента И 67. На элемент И 67 также поступает сигнал управления чтением. Сигнал, сформированный на элементе И 67, через элемент ИЛИ 70 поступает на управляющий вход мультиплексора 20, настраивая его на прохождение информации с выхода регистра 9 выходной информации.

50

Сигнал по шине Чтение внешнего уст-дд цедуру, дальнейшее чтение регистра 9 ройства разрешает прохождение инфор- выходной информации не производится, мации с выхода мультиплексора 20 на входную информационную шину внешнего устройства. Таким образом, код команды из регистра 9 выходной информации, проходя через мультиплексор 20 и шинный формирователь 13, считывается на входную информационную шину 28 внешнего устройства.

Процедура передачи данных от процессора во внешнее устройство осуществляется при выполнении команды записи и инициируется микропрограммой

55

При первоначальной записи в триггер 16 регистра 14 признаков на адресную шину 31 внешнего устройства и на шину 29 Запись внешнего устройства поступает адрес триггера 16 и сигнал управления записью, из которых в узле 18 управления на выходе элемента И 63 появляется сигнал управления записью в триггер 16, который поступает в узел 26 фиксации режима работы, через .элемент ИЛИ 77, на установочный вход триггера 16.

внешнего устройства. После анализа

14

кода команды записи и приема значения Прием регистра 7 режимов, микропрограмма внешнего устройства записывает значение Занято в регистр 24 байта

0

5

Q

текущего состояния и признак Требуются данные в триггер 16 регистра 14 признаков. Единичное значение триггера I6 вызывает появление сигнала прерывания микропрограммы процессора на входной шине 6 прерывания процессора. По сигналу прерывания микропрограммой процессора осуществляется чтение значения регистра 14 признаков и его анализ. После считывания регистра 14 признаков он приводится в исходное состояние. По признаку Требуются данные микропрограмма процессора записывает байт данных в регистр 9 выходной информации. При записи байта данных устанавливается триггер 73 и на его выходе появляется сигнал, который по шине 34 Запрос прямого доступа поступает в устройство (внеш0

5

0

тывается во внешнее устройство. При чтении регистра 9 выходной информации вновь устанавливается триггер 16 Требуются данные регистра 14 признаков. По единичному значению триггера 16 вновь появляется сигнал на выходной шине 6 прерывания процессора. Организуется следующий цикл передачи байта данных от процессора внешнему устройству. Цикл повторяется до тех пор, пока не исчерпается блок данных в процессоре. Для завершения процедуры процессор на признак Требуются данные отвечает записью в регистр 7 режимов указания Конец передачи данных. Микропрограмма внешнего устройства, считав значение регистра 7 режимов с указателем Конец передачи данных, завершает про

цедуру, дальнейшее чтение регистра 9 выходной информации не производится,

При первоначальной записи в триггер 16 регистра 14 признаков на адресную шину 31 внешнего устройства и на шину 29 Запись внешнего устройства поступает адрес триггера 16 и сигнал управления записью, из которых в узле 18 управления на выходе элемента И 63 появляется сигнал управления записью в триггер 16, который поступает в узел 26 фиксации режима работы, через .элемент ИЛИ 77, на установочный вход триггера 16.

15155

При считывании значения регистра 14 признаков по адресной шине 4 процессора и мине Чтение процессора поступают адрес и сигнал управления чтением. В узле 18 управления значение адреса поступает на входы дешифратора 68, на выходе которого появляется сигнал, который поступает на $ход элемента И 60« На другой вход Элемента И 60 поступает сигнал управ- ,|1ения чтением. На выходе элемента |4 60 формируется сигнал управления чтением регистра 14 признаков, который поступает на сихровходы триггеров 6 и 17 и по заднему фронту сигнала Ьбрасывает их в исходное состояние.

При записи байта данных в регистр 0 выходной информации на адресную ши- йу 4 процессора и на шину 2 Запись Процессора поступают разряд адреса Записи байта данных в регистр 9 выходной информации и сигнал управления Записью. В узле 18 управления и на выходе элемента И 57 появляется сиг- Нал управления записью данных в регистр 9 выходной информации. Этот сигнал через элемент ИЛИ 19 поступает на Јход записи регистра 9 выходной информации и в узел 26 фиксации режима работы. В регистр 9 выходной информации записывается байт данных, в узле Й6 фиксации режима работы через элемент ИЛИ 75 сигнал поступает на уста- Йовочный вход триггера 73 и устанавливает его в единичное значение. На выходе триггера 73 появляется сигнал, Который по шине 34 Запрос прямого Доступа поступает во внешнее устройство.

При чтении байта данных из регистра 9 выходной информации по шине 33 Разрешение прямого доступа и шине 30 Чтение внешнего устройства поступают на вход элемента И 80 узла 26 фиксации режима работы сигнал обратной связи от внешнего устройства и сигнал управления чтением. На выходе элемента И 80 появляется сигнал, который поступает через элемент ИЛИ 76 на Вход сброса триггера 73 и сбрасывает его, через элемент ИЛИ 77 поступает на установочный вход триггера 16 регистра 14 признаков и устанавливает его в единичное значение, а также через элемент ИЛИ 70 узла 18 управления поступает на управляющий вход культиплексора 20 и управляет прохождением информации регистра 9 выходной

16

o

5

0

25

30

35

40

45

50

55

информации через мультиплексор 20. В этот момент времени шинный формирователь 13 открыт сигналом на шине 30 Чтение внешнего устройства, и информация-регистра 9 выходной информации появляется на входной информационной шине 28 внешнего устройства.

Процедура передачи данных от внешнего устройства в процессор инициируется микропрограммой внешнего устройства. После анализа кода команды чтения и приема значения Прием регистра 7 режимов, микропрограмма внешнего , устройства записывает значение Занято в регистр 24 байта текущего состояния, настраивает внешнее устройство на чтение данных в режиме прямого доступа из оперативной памяти внешнего устройства и для инициирования режима прямого доступа осуществляет запись в триггер 72 режима чтения узла фиксации режима выдача - прием. По единичному значению триггера 72 устанавливается триггер 73. На шине 34 Запрос прямого доступа11 появляется сигнал, в ответ на который внешнее устройство на выходную информационную шину 35 помешает байт информации, на шину 33 Разрешение прямого доступа сигнал обратной связи, а на шину 29 Запись внешнего устройства - сигнал управления записью, по которым осуществляется запись байта данных в регистр 25 входной информации. При этом устанавливается триггер 17 в регистре 14 признаков. Установка триггера 17 вызывает появление сигнала прерывания на входной шине 6 прерывания процессора. Микропрограмма процессора организует чтение байта данных из регистра 25 входной информации. При чтении регистра 25 выходной информации вновь устанавливается триггер 73 и возникает сигнал на шине 34 Запрос прямого доступа, в ответ на который появляется байт информации на выходной информационной шине 35, сигнал на шине 29 Запись внешнего устройства и шине 33 Разрешение прямого доступа. Цикл передачи байта данных в процессор повторяется. При передаче последнего байта данных, кроме сигнала на шине 29 Запись внешнего устройства и шине 33 Разрешение прямого доступа, присутствует сигнал на шине 32 Конец блока. При наличии этого сигнала триггер 73 не устанавливается и последу

17

ющая передача данных из внешнего устройства в процессор не осуществляет- ся.

При записи в триггер 72 по выходной информационной шине 35 внешнего устройства на информационный вход триггера 7,2 поступает единичное значение, на адресную шину 31 внешнего устройства поступает адрес триггера 72, общий с адресом триггера 15, а на шину 29 Запись внешнего устройства - сигнал управления записью. В узле 18 управления на элементе И 64 Формируется сигнал управления записью в триггер 72, который с выхода 48 поступает на синхровход триггера 72. Триггер 72 устанавливается в единичное значение. Сигнал с выхода триггера 72 поступает на скнхровход тригге- ра 73, на информационном входе которого присутствует единичное значение шины 38 единичного потенциала. Триггер 73 устанавливается в единичное значение и на шине 34 Запрос прямого доступа появляется сигнал. Триггер 73 устанавливается по фронту сигнала с триггера 72.

При записи байта данных в регистр 25 входной информации по выходной информационной шине внешнего устройства поступает байт данных, а по шине 33 Разрешение прямого доступа и шине 29 Запись внешнего устройства поступают сигналы обратной связи и управления записью. На элементе И 81 формируется сигнал, который через элемент ИЛИ 76 поступает на вход сброса триггера 73 и приводит его в исходное состояние, через элемент ИЛИ 78 поступает на вход записи регистра 25 входной информации, а также на вход элемента И 82. В регистр 25 входной информации записывается байт данных, а триггер 17 устанавливается в единичное значение. Единичное значение триггера 17 вызывает появление сигнала прерывания на входной шине 6 прерывания процессора.

При чтении байта данных регистра 25 входной информации по адресной шине 4 процессора и по шине 3 Чтение процессора поступают адрес регистра 25 входной информации и сигнал управления чтением. Адрес регистра 25 входной информации, задаваемый двумя раз- рядами, поступает на вход мультиплексора 23 и на входы дешифратора 68 узла 18 управления. Значение регистра

155

10

jcJQ25

0524-18

25 входной информации проходит через мультиплексор 23 и шинный формирователь 12 на входную информационную тину 5 процессора. На элемент И 61 узла 18 управления поступают сигналы с выхода дешифратора 68 и с шины 3 Чтение процессора. На выходе элемента И 61 возникает сигнал, который- поступает в ,узел 26 фиксации режима работы на вход элемента И 83. На входы элемента И 83 также поступают сигналы с инверсного плеча триггера 71, который к этому моменту находится в сброшенном состоянии, а также с прямого плеча триггера 72, который находится в установленном состоянии. На выходе элемента И 83 возникает сигнал, который через элемент ИЛИ 75 поступает на установочный вход триггера 73, устанавливая его в единичное состояние. На шине 34 Запрос прямого доступа возникает сигнал запроса следующего байта данных.

При записи последнего байта данных в регистр 25 входной информации Б узел 26 фиксации режима работы по шинам 33 Разрешение прямого доступа и 29 Запись внешнего устройства поступают сигнал обратной связи и сигнал управления записью, кроме того, по шине 32 Конец блока поступает сигнал сопровождения последнего байта данных. На элементе И 82 Формиру-1 ется сигнал, который поступает на установочный вход триггера 71 и устанавливает его в единичное состояние, а также, через элемент ИЛИ 78, поступает на вход записи регистра 25 входной информации. В регистр 25 входной информации записывается байт данных. Триггер 17 устанавливается в единичное значение. Единичное значение триггера 17 вызывает появление сигнала прерывания на входной шине 6 прерывания процессора.

При чтении последнего байта дан- ных из регистра 25 входной информации не происходит установки триггера 73, так как инверсный выход триггера 71 в этом случае имеет нулевое значение и на элементе 83 не формируется сигнал установки триггера 73.

Процедура передачи байта состояния в процессор инициируется микропрограммой внешнего устройства. Микропрограмма внешнего устройства записывает байт состояния в регистр 25 входной информации и единичное значе30

35

40

45

50

ние в триггер 15 регистра 14 признаков. Единичное значение триггера 15 вызывает возникновение сигнала прерывания на входной шине 6 прерывания процессора. По сигналу прерывания микропрограмма процессора считывает значение регистра 14 признаков и анализирует его. По единичному значению триггера 159 идентифицирующему сигнал Q прерывания как запрос на передачу байта состояния, а информацию в регистре 25 входной информации как байт состояния, значение банта состояния микропрограммно считывается в процес- сор из регистра 25 входной информации. Микропрограмма процессора осушествля- ет запись в регистр 7 режимов признака Прием, который вызывает появление сигнала прерывания на входной ши 2Q не 27 прерывания внешнего устройства, а также сброс триггера 15. По сигналу прерывания микропрограмма внешнего устройства осуществляет чтение реги- стра 7 режимов и его анализ. После 25 чтения регистра 7 он сбрасывается в нулевое значение. Процедура передачи байта состояния завершается.

При записи байта состояния в регистр 25 входной информации по выход- JQ ной информационной щине 35 поступает байт состояния, по адресной шине 31 внешнего устройства и шине 29 Запись адрес регистра 25 входной информации и сигнал управления записью поступают .,, в узел 18 управления, где на элементе И 65 Формируется сигнал управления записью в регистр 25 входной информации, который поступает в узел 26 фиксации режима работы и, через эле- лп мент ИЛИ 79, на вход записи регистра 25 входной информации, В регистр 25 входной информации записывается байт состояния.

При записи в триггер 15 регистра 14 признаков признака байта состояния на информационный вход триггера 15 по входной информационной шине 35 внешнего устройства поступает единичное значение разряда записи в триггер 15, по адресной шине 31 внешнего устройства и по шине 29 Запись поступают адрес триггера 15 и сигнал управления записью. В узле 18 упоавления на элементе И 64 формируется сигнал управления записью в триггер 15 и устанав1 ливает его в единичное значение, а также поступает в узел 26 фиксации режима работы на информационный вход

50

55

,

0

5

триггера 72 для записи в него нулевого значения. Таким образом, при записи в триггер 15 единичного значения в триггер 72 записывается нулевое значение. Единичное значение триггера 15 поступает на вход формирователя сигналов прерывания 10, вызывая появление сигнала прерывания на входной шине 6 прерывания процессора, а также в блок 26 фиксации режима работы, где, проходя через элемент ИЛИ 74, поступает на вход сброса триггера 71 и сбрасывает его в исходное состоя- . ние.

Считывание значения триггера 15 производится так же, как и при выполнении процедуры начальной выборки.

Чтение байта состояния из регистра 25 входной информации отличается от чтения байта данных тем, что к моменту чтения байта состояния триггер 72 узла 26 режима работы находится в сброшенном состоянии и на элементе И 83 не формируется сигнал установки триггера 73. Запись признака Прием в регистр 7 режимов осуществляется так же, как в процедуре начальной выборки.

При записи в триггер 89 регистра 7 режимов на элементе И 56 узла 18 управления формируется сигнал сброса триггера 15, которым триггер 15 приводится в исходное состояние. Единичное значение триггера 89 вызывает появление сигнала прерывания на входной шине 27 прерывания внешнего устройства,

Чтение регистра 7 режимов производится так же, как в процедуре начальной выборки.

Таким образом, устройство, по сравнению с прототипом, обладает расширенными функциональными возможностями, позволяющими идентифицировать информацию как команду или байт состояния, хранить байт текущего состояния, хранить байты начального состояния, формировать сигнал прерывания во внешнее устройство. Расширение функциональных возможностей в устройстве позволяет, кроме процедуры передачи данных, выполнять процедуры начальной выборки и передачи байта состояния,, т.е. весь набор процедур., ввода - вывода по логике интерфейса ЕС ЭВМ.

Хранение байта текущего состояния и байтов начального состояния в устройстве сокращает время выполнения процедуры начальной выборки. В известных устройствах для выполнения начальной выборки осуществляется передача кода команды на внешнее устройство, где микропрограммно производится анализ байта текущего состояния, формирование и передача в процессор байта начального состояния. Так как

в данном устройстве процедура начальной выборки выполняется аппаратно на уровне процессор - устройство сопряжения, время ее выполнения значительно меньше, чем в известных условиях, Например, для выполнения начальной выборки в ЭВМ ЕС1007 программным путем требуется около 370 мсек, которые складываются, в среднем, из времени выполнения 100 команд обработки пре- рывания (с временем выполнения одной команды 7,5 мксек), 30 команд опроса устройства, 350 мсек на ожидание ответа от устройства и времени выполнения 100 команд анализа поступившей команды и выдачи начального байта . состояния. При использовании данного устройства время выполнения начальной выборки не превышает 7 мксек. За счет повышения быстродействия при выполне- нии процедуры начальной выборки повышается быстродействие при выполнении процедуры ввода - вывода в целом.

Формула изобретения

0

j 0 5 о

5

о

0

внешнего устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены регистр признаков, два мультиплексора и два шинных формирователя, регистр байта текущего состояния, шифратор, второй формирователь сигнала прерывания, два элемента ИЛИ, триггер причем второй вход логического состояния узла управления является входом устройства для подключения к выходу записи процессора, третий вход логического условия узла управления соединен с управляющим входом первого шинного формирователя и является входом устройства для подключения к выходу чтения процессора, первая группа входов логического условия узла управления и группа управляющих входов первого мультиплексора образуют группу входов устройства для подключения к группе адресных выходов процессора, группа информационных выходов первого шинного преобразователя образует группу выходов устройства для подклю- i чения к группе информационных входов процессора, выход прерывателя второго формирователя сигналов прерывания является выходом устройства для подключения к входу прерывания внешнего устройства, группа информационных выходов второго шинного формирователя образует группу выходов устройства для подключения к группе информационных входов внешнего устройства, группы информационных входов регистра байта текущего состояния и регистра входной информации, первые инфорационные входы узла фиксации режима работы и регистра признаков образуют группу входов устройства для подключения к группе информационных выходов внешнего устройства, второй стробирующий вход узла фиксации режима работы является входом устройства для подключения к выходу конца блока внешнего устройства, вторая группа входов логического условия узла управления образует группу входов устройства для подключения к группе адресных выходов внешнего устройства, четвертый вход логического условия узла управления соединен с третьим стробирующим входом узла фиксации режима работы и является входом устройства для подключения и выходу записи внешнего устройства, пятый вход логического условия узла управления соединен с четвертым

23155

стробирующим входом узла фиксации режима работы, с управляющим входом второго шинного формирователя и является входом устройства для подключения к выходу чтения внешнего устройства, установочный вход регистра режимов соединен с нулевым входом триггера, с первым, вторым, нулевыми входами регистра признаков, с первым входом первого элемента ИЛИ, с первым установочным входом регистра Фиксации режима работы и является установочным входом устройства, информационные входы регистра режимов, триг- гера, первый, второй информационные входы регистра признаков подключены к шине нулевого потенциала устройства, второй информационный вход узла фиксации режима работы подключен к Јиине единичного потенциала устройства, при этом первый выход узла управ

пения соединен с входом записи регистра режимов, вход чтения которого соединен с вторым выходом узла управ- ления и с синхровходом триггера, выход которого и группа информационных выходов регистра режимов соединены с группой входов требования прерывания второго формирователя сигналов Прерывания и с первой группой информационных входов второго мультиплексора, вторая группа информационных входов которого соединена с группой Информационных выходов регистра выходной информации и с группой информационных входов шифратора, группа Выходов которого соединена с первой Группой информационных входов первог мультиплексора, вторая группа информационных входов которого соединена с группой входов требования прерывания первого Формирователя сигналов прерывания, с третьим информационным входом узла фиксации режима работы и с группой информационных выходов регистра признаков, первый и второй единичные входы которого соединены соответственно с петэьым и вторым установочными выходами узла фиксации режима работы, выход записи которого соединен с входом записи регистра входной информации, группа информационных выходов которого соединена с третьей группой информационных входо первого мультиплексора, четвертая группа информационных входов которого соединена с группой информационны выходов регистра байга текущего со

24

0

0

5

0

5

5

5

стояния, вход записи которого соединен с третьим выходом узла управле- ния, четвертый, пятый, шестой выходы и шестой вход логического условия которого соединены соответственно с первым, вторым, третьим входами логического условия и с выходом чтения узла фиксации режима работы, синхровход которого соединен с седьмым выходом узла управления и- с первым синхровходом регистра признаков, второй и третий синхровходы которого соединены с восьмым выходом узла управления, девятый выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с третьим нулевым входом регистра признаков, третий единичный вход которого соединен с единичным входом триггера, с первым входом второго элемента ИЛИ и с десятым выходом узла-управления, одиннадцатый выход которого соединен с вторым установочным входом узла Фиксации ежима работы и с вторым входом элемента ИЛИ, выход которого соединен с входом записи регистра выходной информации, группа информационных входов первого шинного формирователя соединена с группой информационных выходов первого мультиплексора, группа информационных входов второго шинного формирователя соединена с группой информационных выходов второго мультиплексора, управляющий вход которого соединен с двенадцатым выходом узла управления ,

2 „ Устройство по п. I , отличающееся тем, что узел управления содержит два дешифратора, двенадцать элементов И и элемент ИЛИ, причем первьй вход первого элемента И является первым входом логического условия узла, первьй вход второго элемента И соединен с первыми входами третьего, четвертого элементов И и является вторым входом логического условия узла, первьй вход пятого элемента И соединен с первым входом шестого элемента И и является третьим входом логического условия узла, первьй вход седьмого элемента И соединен с первыми входами восьмого, девятого, десятого элементов И и является четвертым входом логического условия узла, первьй вход одиннадцатого элемента И соединен с первым входом двенадцатого элемента И и являемся пятым входом логического условия узла, пер

2515

вый вход элемента ИЛИ является шестым входом логического условия узла вторые входы второго, третьего, четвертого элементов И и группа информационных входов первого дешифратора образуют первую группу входов логического условия узла, группа информационных входов второго дешифратора образует вторую группу входов логического условия узла, выход третьего элемента И соединен с вторым входом первого элемента И и является первы выходом узла, выходы одиннадцатого, седьмого, восьмого, шестого, десятого, девятого, пятого, первого, четвертого, второго элементов И и выход элемента ИЛИ являются соответственно вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым, десятым, одиннадцать и двенадцатым выходами узла, при этом в узле управления первый и второй выходы первого дешифратора соединены соответственно с вторыми входами пятого и шестого элементов И, второй вход элемента ИЛИ соединен с выходом двенадцатого элемента И, второй вход которого соединен с вторым входом седьмого элемента И и с первым выходом второго дешифратора, второй выход которого соединен с вторым входом восьмого элемента И; второй вход девятого элемента И соединен с вторым входом одиннадцатого элемента И и с третьим выходом второго дешифратора, четвертый выход которого соединен с вторым входом десятого элемента И.

40

26

0

триггера и с первым входом DTODOIо элемента ИЛИ, и первый вход третьего элемента ИЛИ являются соответственно первым и вторым установочными входагш узла, синхровход первого триггера лз- ляется синхровходом узла, первый вход первого элемента И, соединенный с первым входом второго элемента И, первый вход третьего элемента И, вторые входы второго и первого элементов Я являются соответственно первым, вторым, третьим и четвертым стробирую- шими входами узла, первый вход четвертого элемента ИЛИ, первый вход четвертого элемента И и первый вход пятого

0

25

0

5

0

элемента ИЛИ являются соответственно первым, вторым и третьим входами логического условия узла, выход второго триггера является выходом запроса прямого доступа узла, выход четвертого элемента ИЛИ и выход шестого элемента ИЛИ, соединенный с вторым входом пятого элемента ИЛИ, являются соответственно первым и вторым установочными выходами узла, выход первого элемента И, соединенный с вторыми входами второго и четвертого элементов ИЛИ, и выход пятого элемента ИЛИ являются соответственно выходами чтения и записи узла, при этом в узле фиксации режима работы выход первого элемента ИЛИ соединен с нулевым входом третьего триггера, единичный вход которого соединен с первым входом шестого элемента ИЛИ и с выходом третьего элемента И, второй вход которого соединен с выходом второго элемента И, с вторым входом шестого элемента ИЛИ и с третьим входом второго элемента ИЛИ, выход которого соединен с нулевым входом второго триггера, синхровход которого соединен с выходом первого триггера и с вторым входом четвертого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с единичным входом второго триггера, выход третьего триггера соединен с третьим входом четвертого элемента И.

Фиг А

| Устройство для сопряжения двух магистралей | 1982 |

|

SU1111147A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1982 |

|

SU1132282A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (прототип). | |||

Авторы

Даты

1990-03-15—Публикация

1988-06-27—Подача